Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, фиг.1 в описании изобретения к патенту РФ 2276399, кл. G06F 7/00, 2006 г.), которые реализуют параллельный набор n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация последовательного набора n простых симметричных булевых функций, зависящих от параллельного набора n аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (фиг.1 в описании изобретения к патенту РФ 2282234, кл. G06F 7/57, 2006 г.), который содержит n замыкающих, n размыкающих ключей, n элементов И, n элементов ИЛИ, n D-триггеров и реализует последовательный набор n простых симметричных булевых функций, зависящих от параллельного набора n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация параллельного набора n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации параллельного набора n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов либо последовательного набора этих функций, зависящих от параллельного набора указанных аргументов.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n замыкающих, n размыкающих ключей, n элементов И, n элементов ИЛИ и n D-триггеров, первый и второй входы i-го  элемента И соединены соответственно с вторым и первым входами i-го элемента ИЛИ, выход i-го замыкающего и выход i-го размыкающего ключей объединены, а их вход управления соединен с первым управляющим входом логического вычислителя, подсоединенного вторым управляющим входом к тактовому входу i-го D-триггера, особенность заключается в том, что выход k-го

элемента И соединены соответственно с вторым и первым входами i-го элемента ИЛИ, выход i-го замыкающего и выход i-го размыкающего ключей объединены, а их вход управления соединен с первым управляющим входом логического вычислителя, подсоединенного вторым управляющим входом к тактовому входу i-го D-триггера, особенность заключается в том, что выход k-го

элемента И и выход i-го элемента ИЛИ подключены соответственно к первому входу (k+1)-го элемента И и входу данных i-го D-триггера, неинвертирующий выход которого соединен с входом i-го размыкающего ключа, подсоединенного выходом к первому входу i-го элемента ИЛИ, выход которого соединен с i-ым параллельным выходом логического вычислителя, подключенного i-ым параллельным входом, последовательным входом и последовательным выходом соответственно к входу i-го замыкающего ключа, первому входу первого и выходу n-го элементов И.

элемента И и выход i-го элемента ИЛИ подключены соответственно к первому входу (k+1)-го элемента И и входу данных i-го D-триггера, неинвертирующий выход которого соединен с входом i-го размыкающего ключа, подсоединенного выходом к первому входу i-го элемента ИЛИ, выход которого соединен с i-ым параллельным выходом логического вычислителя, подключенного i-ым параллельным входом, последовательным входом и последовательным выходом соответственно к входу i-го замыкающего ключа, первому входу первого и выходу n-го элементов И.

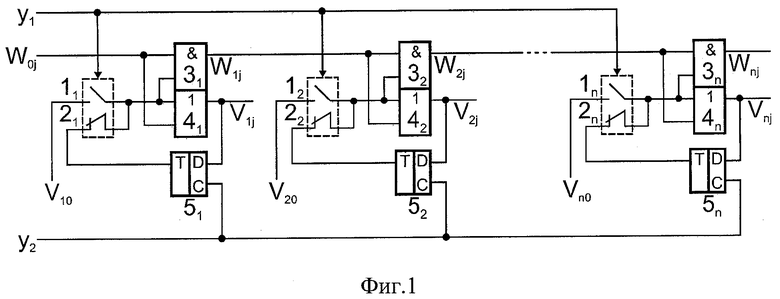

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы, поясняющие принцип его работы.

Логический вычислитель содержит n замыкающих ключей 11,…,1n, n размыкающих ключей 21,…,2n, n элементов И 31,…,3n, n элементов ИЛИ 41,…,4n и n D-триггеров 51,…,5n, причем выход элемента  первый и второй входы элемента

первый и второй входы элемента  соединены соответственно с первым входом элемента 3k+1, вторым и первым входами элемента 4i, выход которого подключен к входу данных D-триггера 5i, подсоединенного неинвертирующим выходом к входу ключа 2i, выход которого соединен с выходом ключа 1i и первым входом элемента 4i, подсоединенного выходом к i-му параллельному выходу логического вычислителя, i-й параллельный вход, последовательный вход, последовательный выход, первый и второй управляющие входы которого соединены соответственно с входом ключа 1i, первым входом элемента 3i, выходом элемента 3n, входом управления ключей 1i, 2i и тактовым входом D-триггера 5i.

соединены соответственно с первым входом элемента 3k+1, вторым и первым входами элемента 4i, выход которого подключен к входу данных D-триггера 5i, подсоединенного неинвертирующим выходом к входу ключа 2i, выход которого соединен с выходом ключа 1i и первым входом элемента 4i, подсоединенного выходом к i-му параллельному выходу логического вычислителя, i-й параллельный вход, последовательный вход, последовательный выход, первый и второй управляющие входы которого соединены соответственно с входом ключа 1i, первым входом элемента 3i, выходом элемента 3n, входом управления ключей 1i, 2i и тактовым входом D-триггера 5i.

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, второй управляющие входы подаются соответственно импульсные сигналы у1, у2∈{0,1} (фиг.2), причем длительность Т* высокого уровня сигнала у1 и период Т сигнала у2 должны удовлетворять условиям Т*>Δt* и Т>Δt, где

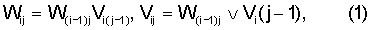

Δt*=nΔtИ, Δt=ΔtTp+nΔtИ, a ΔtТр и ΔtИ есть длительности задержек, вносимых D-триггером и элементом И. Аргументы реализуемых функций - входные двоичные сигналы х1,…,хn∈{0,l} либо последовательно подаются согласно фиг.2 на последовательный вход логического вычислителя (при этом на его первом,…, n-ом параллельных входах фиксируется логический «0»), либо параллельно подаются соответственно на первый,…, n-й параллельные входы логического вычислителя (при этом на его последовательном входе фиксируется логическая «1»). Если у1=1 (y1=0), то ключ  замкнут (разомкнут), а ключ 2i разомкнут (замкнут). Тогда сигналы на выходах элементов 3i, 4i будут определяться рекуррентными выражениями

замкнут (разомкнут), а ключ 2i разомкнут (замкнут). Тогда сигналы на выходах элементов 3i, 4i будут определяться рекуррентными выражениями

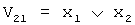

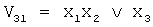

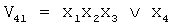

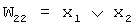

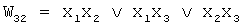

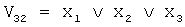

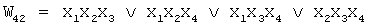

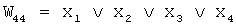

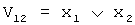

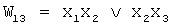

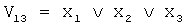

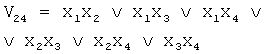

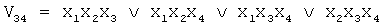

где  есть номер момента времени tj (фиг.2); Vi0=xi, W0j=1 либо Vi0=0, W0j=xj. В представленных ниже табл.1 и табл.2 приведены значения выражений (1) при n=4, если соответственно Vi0=хi, W0j=1 и Vi0=0, W0j=xj.

есть номер момента времени tj (фиг.2); Vi0=xi, W0j=1 либо Vi0=0, W0j=xj. В представленных ниже табл.1 и табл.2 приведены значения выражений (1) при n=4, если соответственно Vi0=хi, W0j=1 и Vi0=0, W0j=xj.

V11=1

V12=1

V22=1

V13=1

V23=1 V33=1

V33=1

V14=1

V24=1

V34=1

V44=1

V11=x1

V21=0

V22=x1x2

V31=0

V32=0

V33=x1x2x3

V41=0

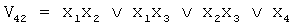

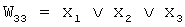

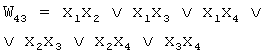

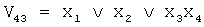

V42=0

V43=0

V44=x1x2x3x4

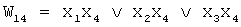

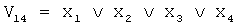

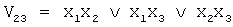

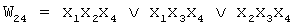

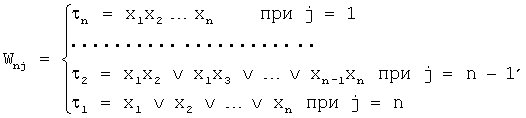

Таким образом, при Vi0=xi и W0j=1 на последовательном выходе предлагаемого логического вычислителя имеем

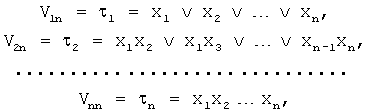

а при Vi0=0, W0j=хj и j=n на его первом, втором,…, n-ом параллельных выходах соответственно имеем

где τ1,…, τn есть простые симметричные булевы функции (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию параллельного набора n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов, либо последовательного набора этих функций, зависящих от параллельного набора указанных аргументов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2383052C2 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2324219C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2003 |

|

RU2248036C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2002 |

|

RU2227931C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2012 |

|

RU2504826C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2262734C1 |

Логический вычислитель предназначен для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, и может быть использован в системах цифровой вычислительной техники как средство преобразования кодов. Техническим результатом является расширение функциональных возможностей устройства за счет реализации параллельного либо последовательного набора булевых функций, зависящих соответственно от последовательного либо параллельного набора указанных аргументов. Устройство содержит n замыкающих ключей, n размыкающих ключей, n элементов И, n элементов ИЛИ и n D-триггеров. 2 ил., 2 табл.

Логический вычислитель, предназначенный для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержащий n замыкающих, n размыкающих ключей, n элементов И, n элементов ИЛИ и n D-триггеров, причем первый и второй входы i-го  элемента И соединены соответственно с вторым и первым входами n-го элемента ИЛИ, выход i-го замыкающего и выход i-го размыкающего ключей объединены, а их вход управления соединен с первым управляющим входом логического вычислителя, подсоединенного вторым управляющим входом к тактовому входу i-го D-триггера, отличающийся тем, что выход k-го

элемента И соединены соответственно с вторым и первым входами n-го элемента ИЛИ, выход i-го замыкающего и выход i-го размыкающего ключей объединены, а их вход управления соединен с первым управляющим входом логического вычислителя, подсоединенного вторым управляющим входом к тактовому входу i-го D-триггера, отличающийся тем, что выход k-го

элемента И и выход i-го элемента ИЛИ подключены соответственно к первому входу (k+1)-го элемента И и входу данных i-го D-триггера, неинвертирующий выход которого соединен с входом i-го размыкающего ключа, подсоединенного выходом к первому входу i-го элемента ИЛИ, выход которого соединен с i-м параллельным выходом логического вычислителя, подключенного i-м параллельным входом, последовательным входом и последовательным выходом соответственно к входу i-го замыкающего ключа, первому входу первого и выходу n-го элементов И.

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1990 |

|

SU1730616A1 |

| МЕТАЛЛОПОРИСТЫЙ ПРОПИТАННЫЙ КАТОД ДЛЯ МАГНЕТРОНА | 2007 |

|

RU2342732C1 |

Авторы

Даты

2009-04-27—Публикация

2007-10-26—Подача