рования 24 микроопераций, декодер 25 команд, триггер 26. элемент ИЛИ 27,.триггер 28, р ультиплексор 29 и одноразрядный шинный формирователь 30.

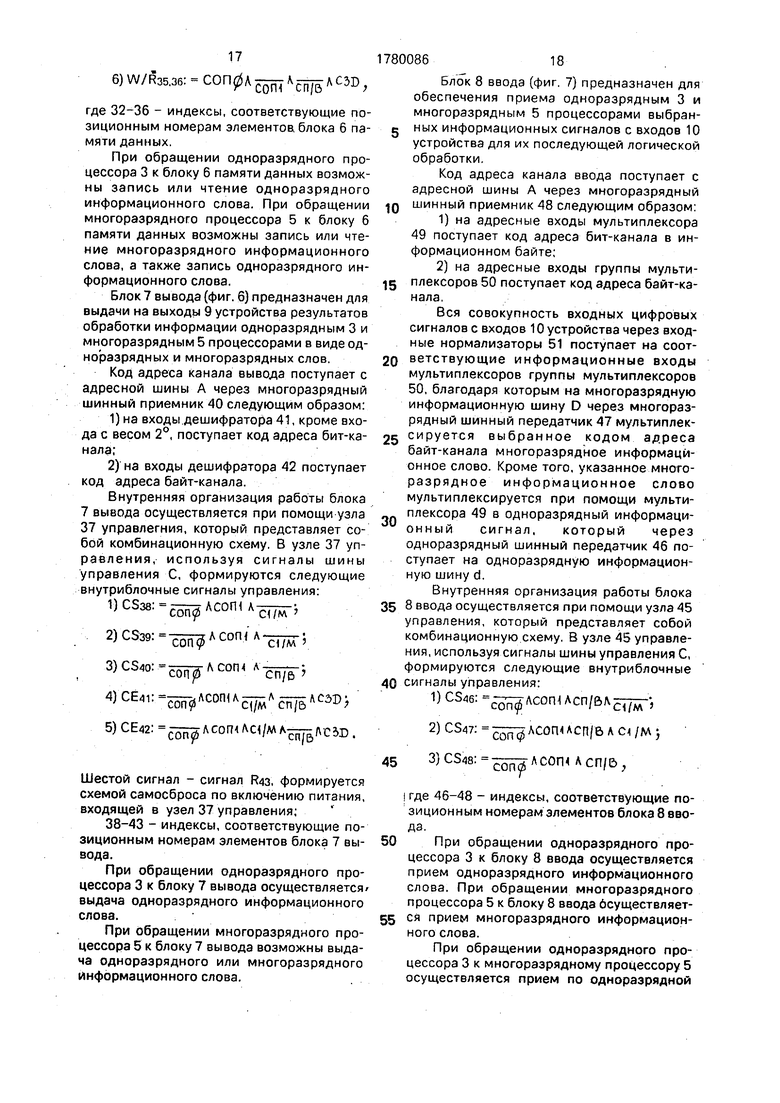

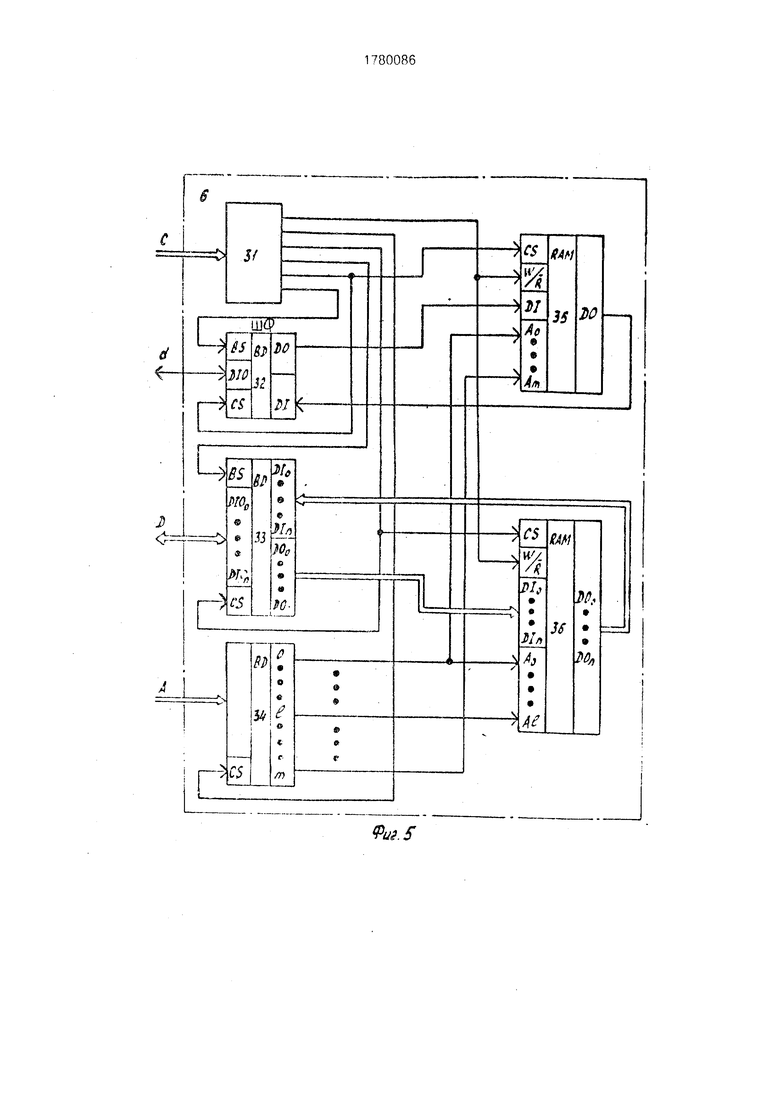

Блок 6 памяти данных (фиг. 5) содержит узел 31 управления, одноразрядный шинный формирователь 32. многоразрядный шинный формирователь 33, многоразрядный шинный приемник 34, одноразрядный оперативный накопитель 35 и многоразрядный оперэтивный накопитель 36,

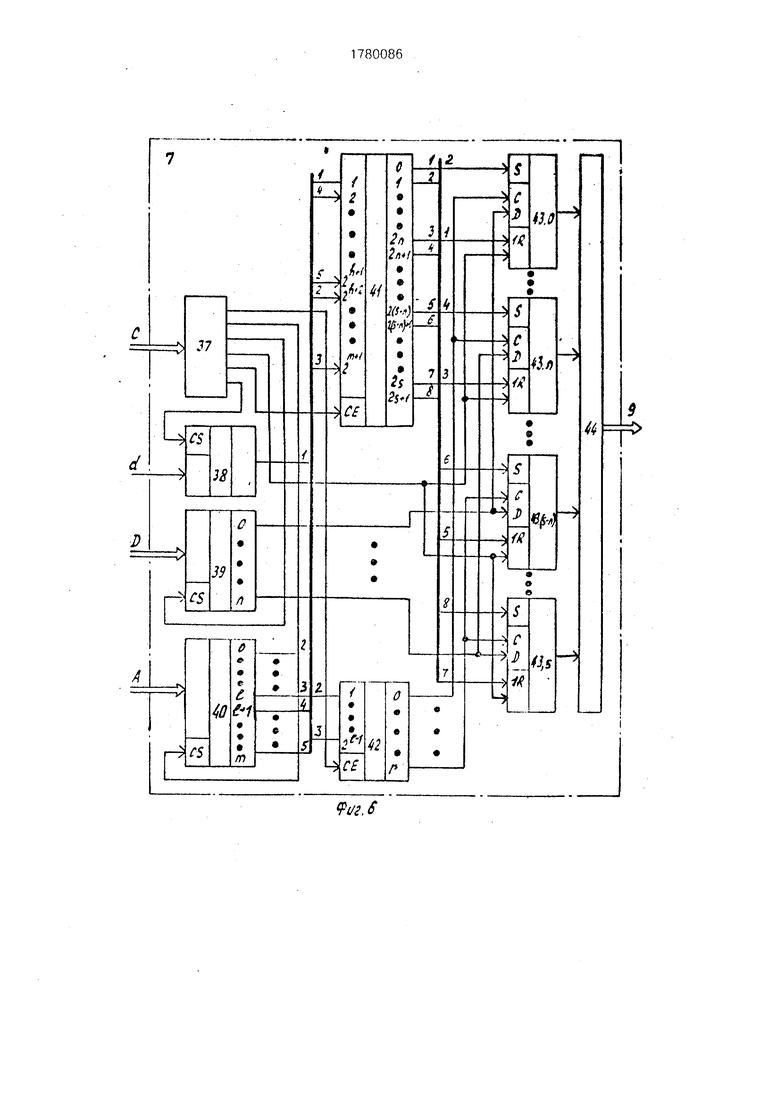

Блок 7 вывода (фиг. 6) содержит узел 37 управления, одноразрядный шинный приемник 38, многоразрядные шинные приемники 39 и 40, дешифратор 41, дешифратор 42, группу TpiirrepOB 43 si выходные усилители 44.

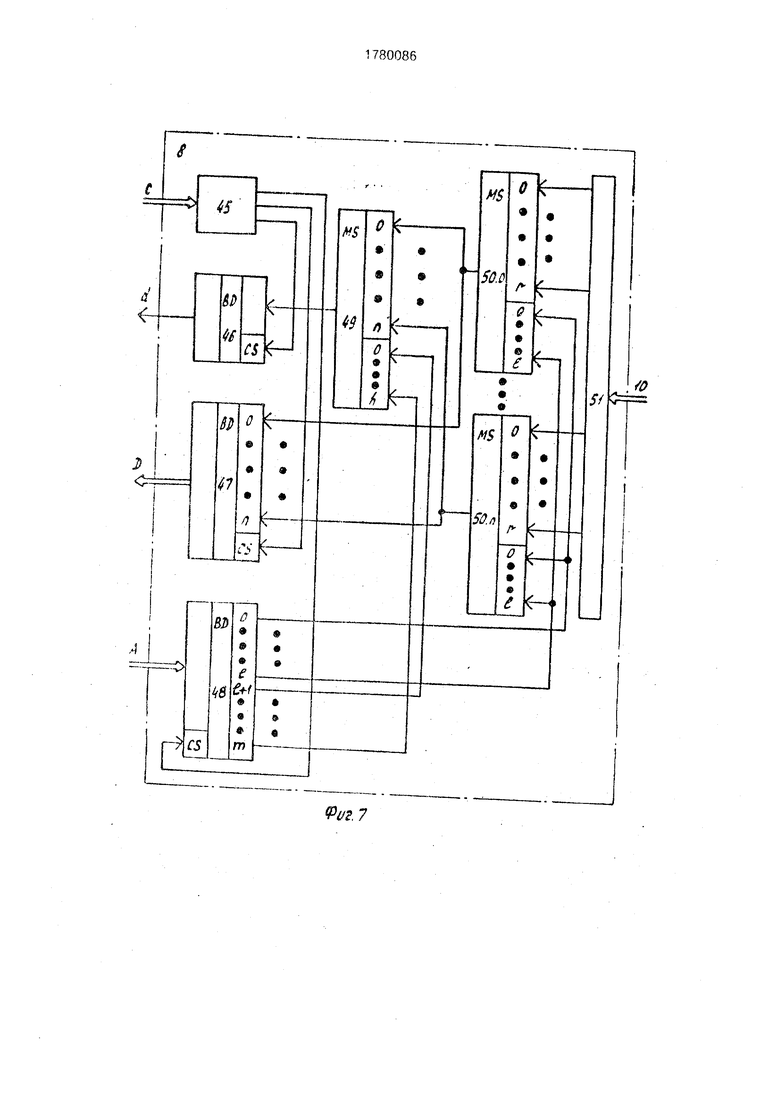

Блок ввода (фиг. 7) содержит узел 45 управления, одноразрядный шинный передатчик 46, многоразрядный шинный передатчик 47, многоразрядный шинный приемник 48, мультиплексор 49, группу мультиплексоров 50 и входные нормализаторы 51,

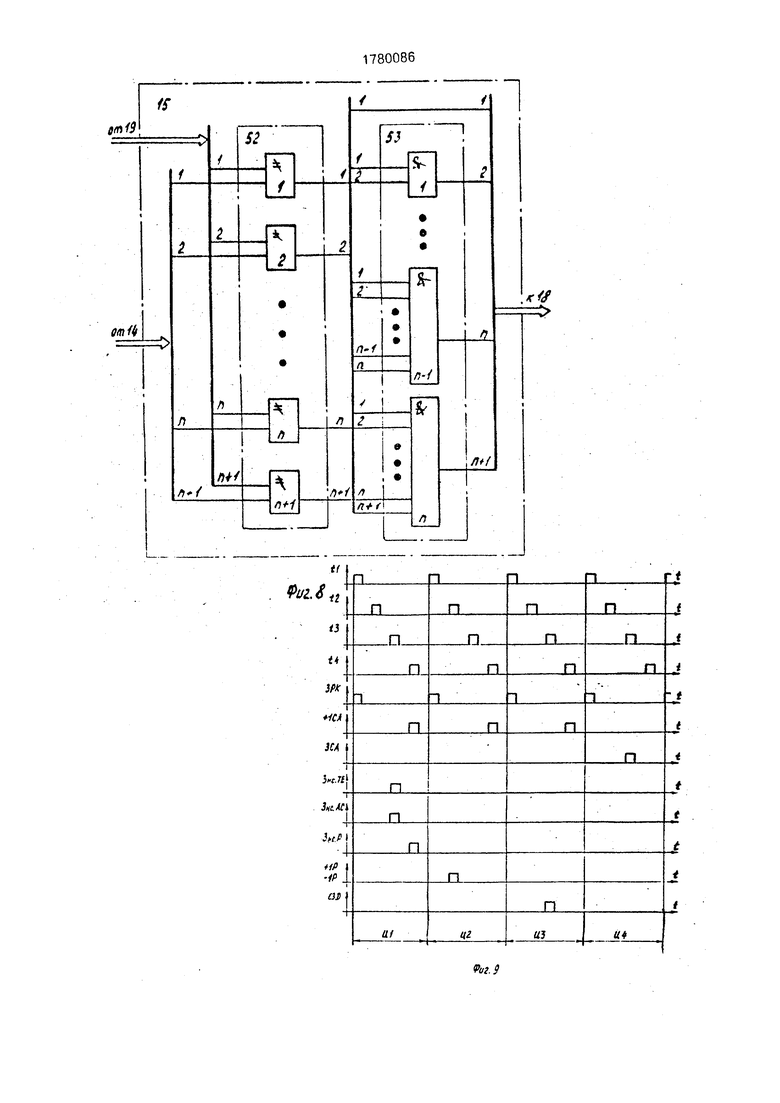

Схема 15 сравнения (фиг. 8) содержит группу (л + 1} элементов РАВНОЗНАЧНОСТЬ 52 и группу п элементов И-53 с копичеством входов от 2 до (п + 1).

Устройство, работает следующим обраоОМ.

В исходном состоянии синхронизатор 1, счетчик 21 адресов и perujcTp 22 команд блока 2 (см. фиг. 3) и группа триггеров 43 блока 7 вывода (см. фиг. 6) сброшены сигналом узла самосброса по включению питания нажатия кнопки Сброс, которые в графических материалах не изображены..

Нажатием кнопки Пуск (на чертежах не показана) осуществляется запуск синхронизатора 1, который начинает выдавать последозательности тактовых импульсов tr-Vi, которыми осуществляется синхронизация работы всего устройства.

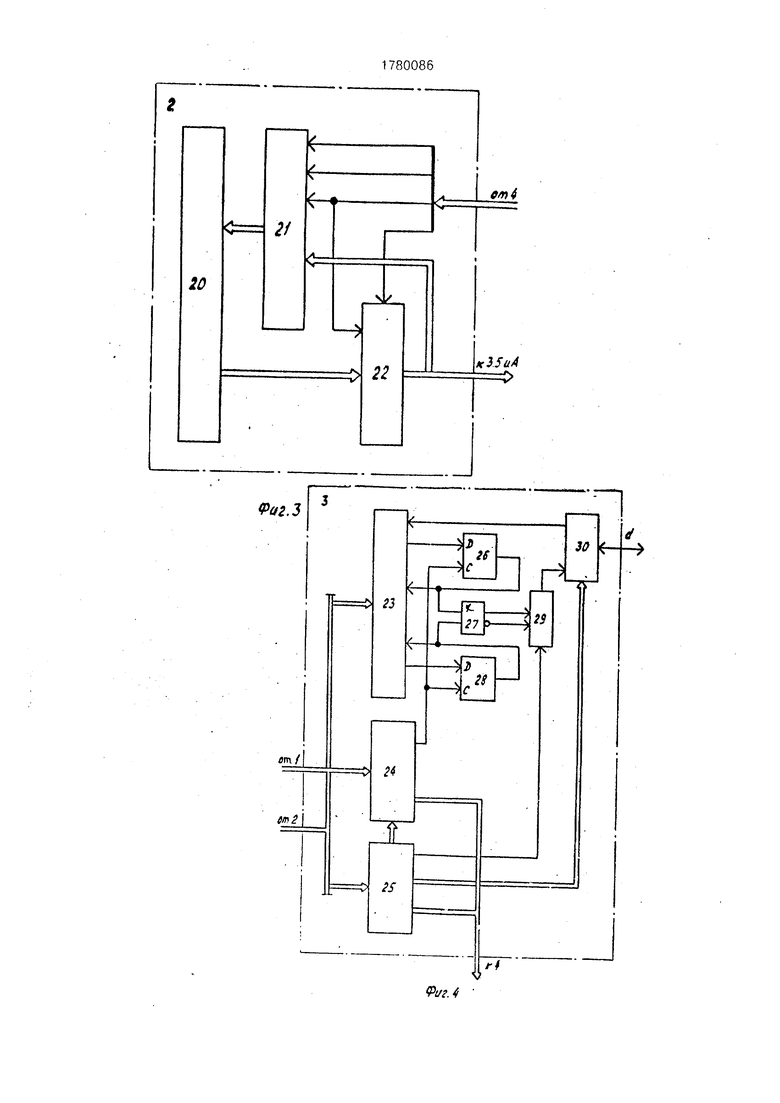

Коды команд хранятся и выдаются блоком 2 (см. фиг. 3). Выбор командного слова в накопителе 20 осуществляется кодом адреса команды, поступающем из счетчика 21 адресов. Запись выбранного командного слова в регистр 22 команд осуществляется игналом ЗРК, поступающим изблока4формирован11я управляющих сигналов. Формирование кодов адресов команд осуществляется двумя способами:

1)последовательным, путем инкрементирования 1 в счетчик 21 адресов сигналом+1СА, поступающим из блока 4;

2)параллельным, при выполнении команд перехода, при этом запись кода адреса из регистра 22 команд в счетчик 21

адресов осуществляется сигналом ЗСА.

Коды команд с выходов блока 2 подаются дальше следующим образом: код призна0ка процессора и код операции поступают на входы одноразрядного 3 и многоразрядного 5 процессоров, коды адресов операндов адресных команд - на адресную шину А. В зависимости от кода признака процессора и кода операции команды выполняются:

1)одноразрядным процессором 3 без участия многоразрядного процессора Б;

2)одноразрядным процессором 3 с участием многоразрядного процессора 5, при

0 этом триггер 17 результата сравнения является операндом при выполнении одноразрядным процессором 3 некоторой части

.команд приема и логической обработки;

3)многоразрядным процессором 5 без

5 участия одноразрядного процессора 3;

4)многоразрядным процессором 5 с участием одноразрядного процессора 3, при этом значение сигнала с информационного выхода одноразрядного процессора 3

0 является условием выполнения многоразряднь1м процессором 5. некоторой части условных команд.

Ввод двоичной информации с входов 10 устройства для ее обработки одноразрядным 3 и многоразрядным 5 процессорами

5 обеспечивается блоком В ввода.

Промежутсмное хранение результатов обработки одноразрядной и многоразрядной информации обеспечивается одноразрядным и многоразрядным оперативным

0 запоминающими устройствами блока 6 памяти данных.

Вывод результатов обработки информации на выходы 9 устройства в виде одноразрядных и многоразрядных двоичных

5 слов обеспечивается блоком 7 вывода,

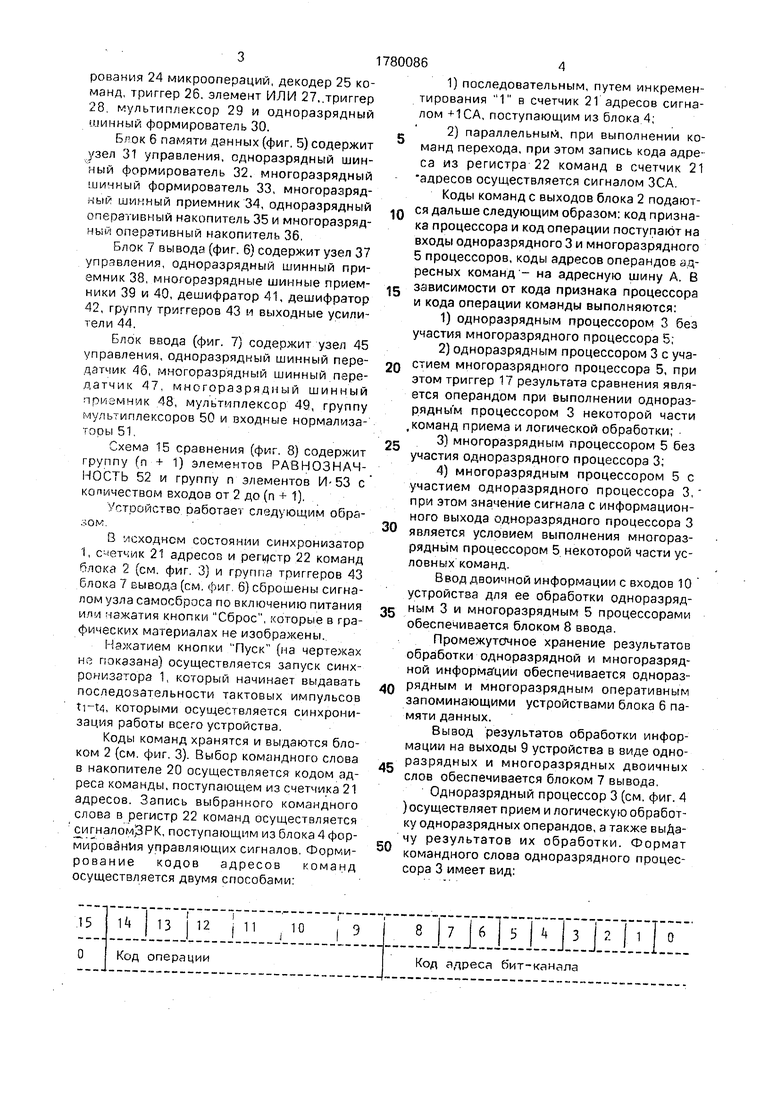

Одноразрядный процессор 3 (см. фиг. 4 )осуществляет прием и логическую обработку одноразрядных операндов, а также выДачу результатов их обработки. Формат

0 командного слова одноразрядного процессора 3 имеет вид:

где 0-15 - разряды регистра 22 команд PKU - РК15.

В РК15 кодируется признак процессора ПП.

ПП: О - признак одноразрядного процессора.

Адресное пространство каждого периферийного блока составляет 512 бит.

В одноразрядном процессоре 3 код признака процессора и код операции поступают на входы декодера 25 команд и операционного узла 23. Декодер 25 команд осуществляет декодирование кода операции и вырабатывает потенциальные (в пределах; длительности цикла команды) сигналы управления.

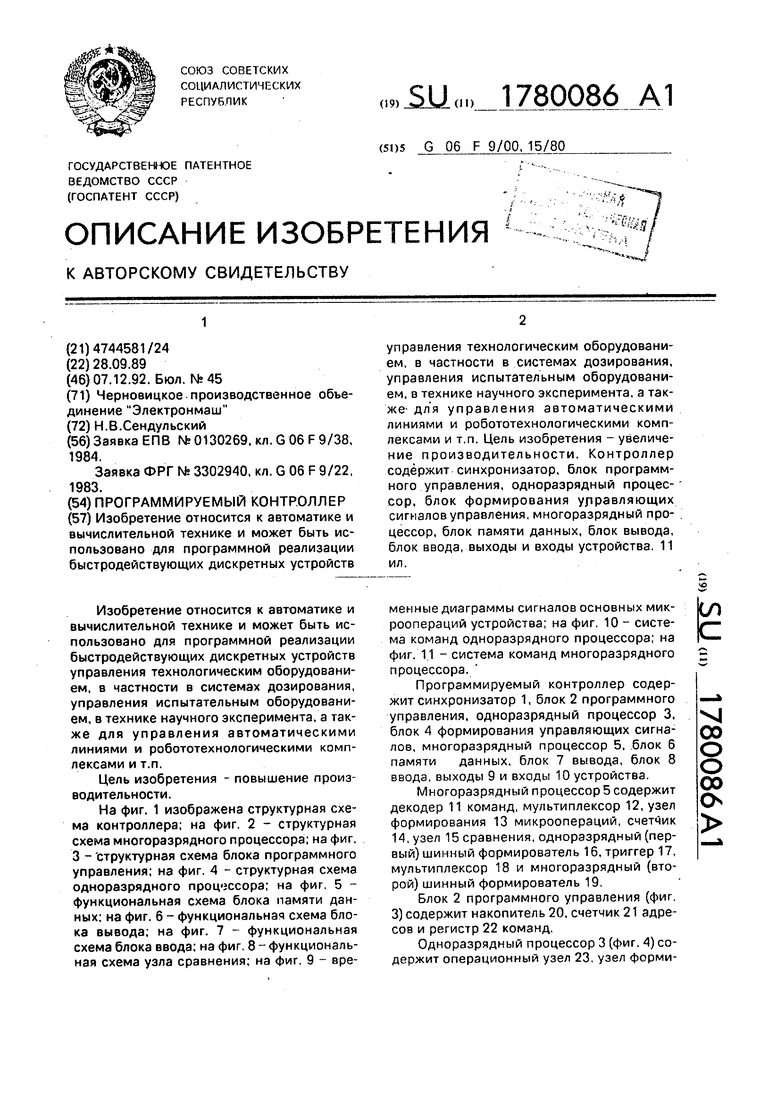

Таблица программы логической матрицы ПЛМ, реализующей декодер 25 команд, имеет вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

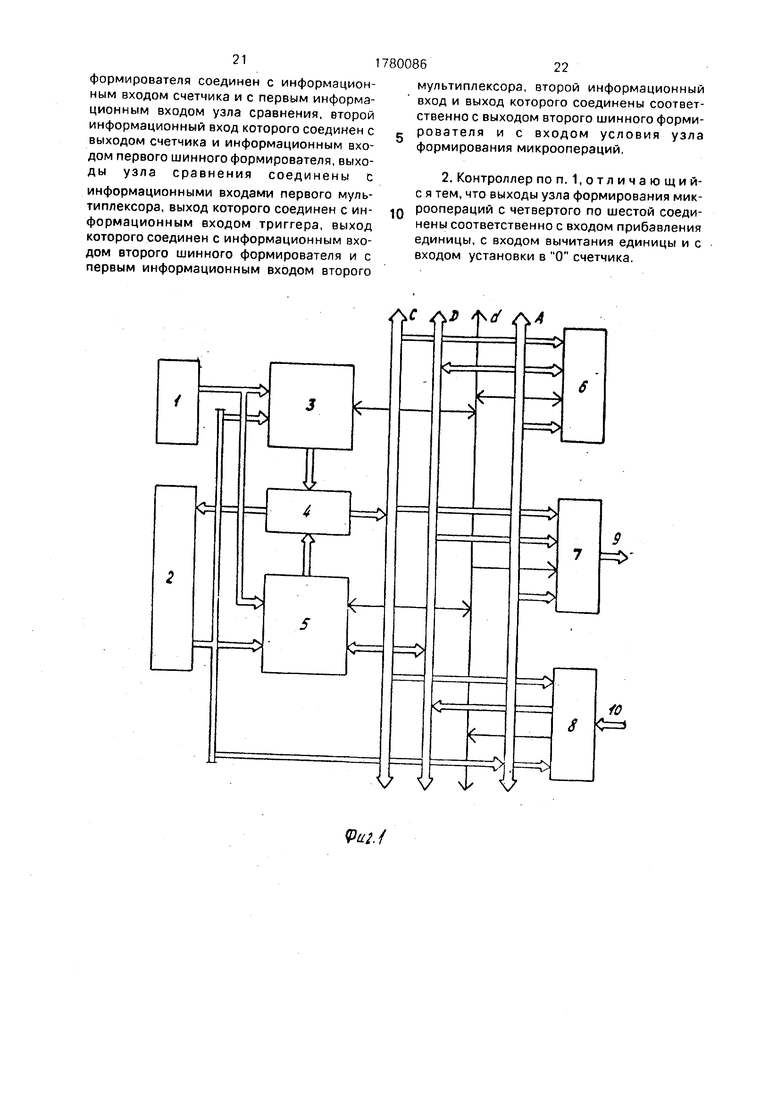

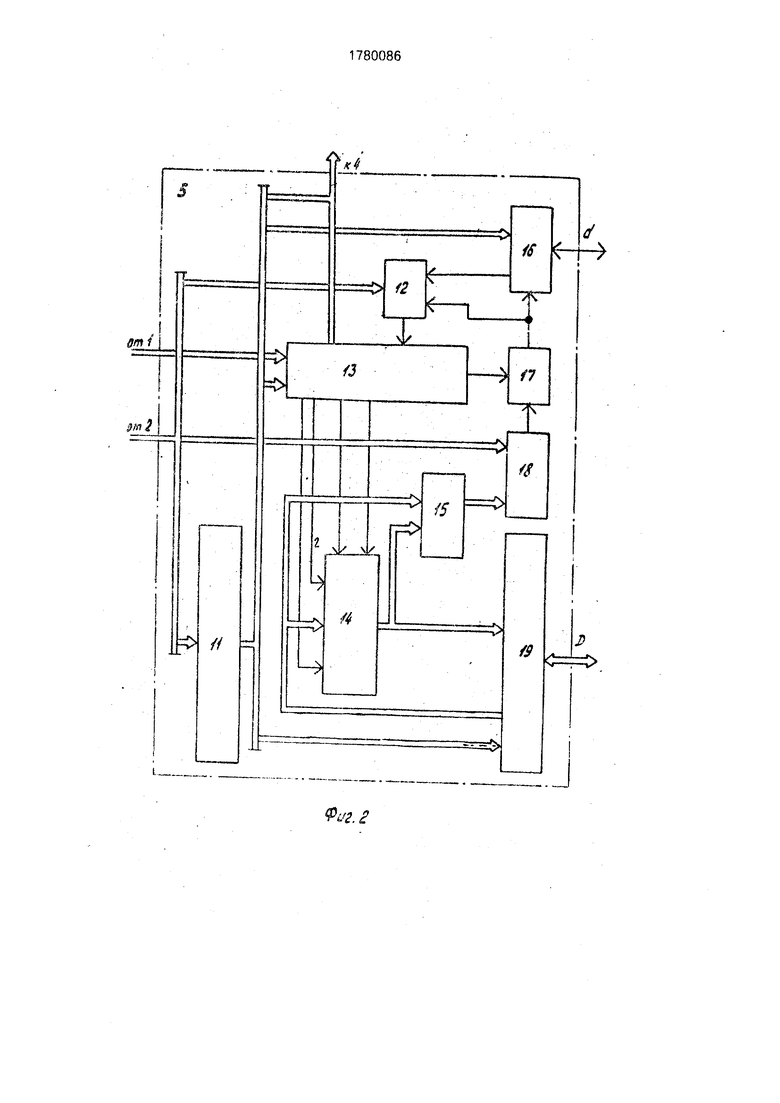

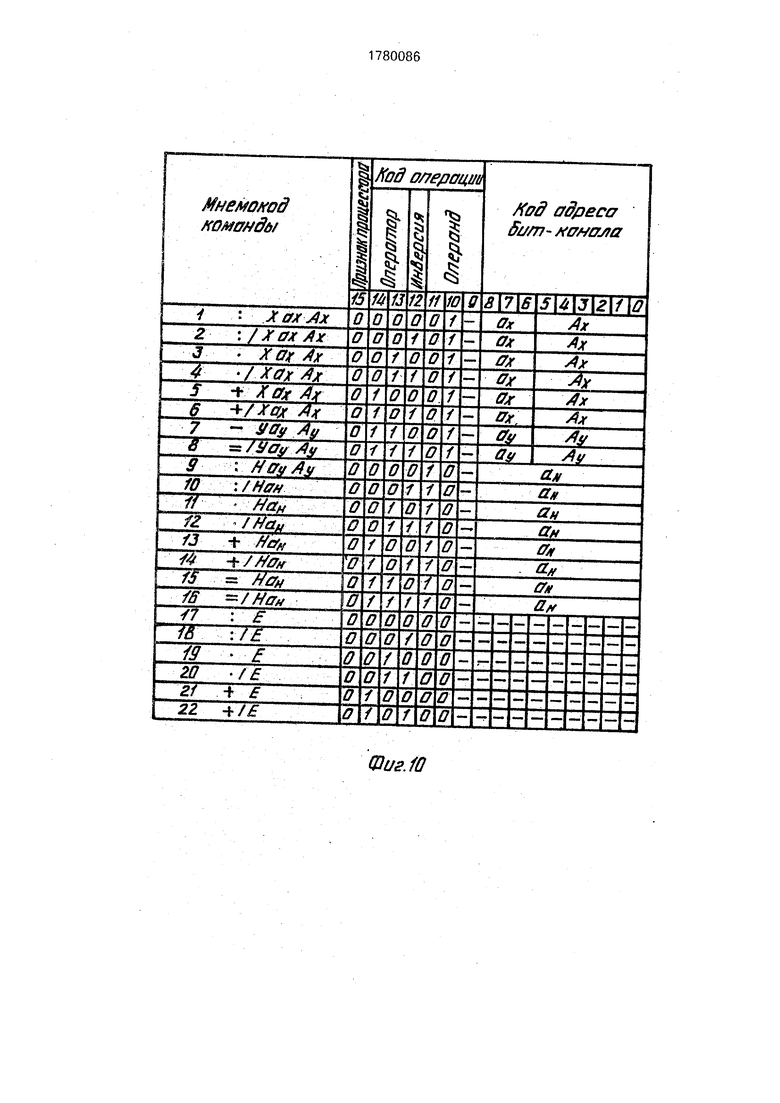

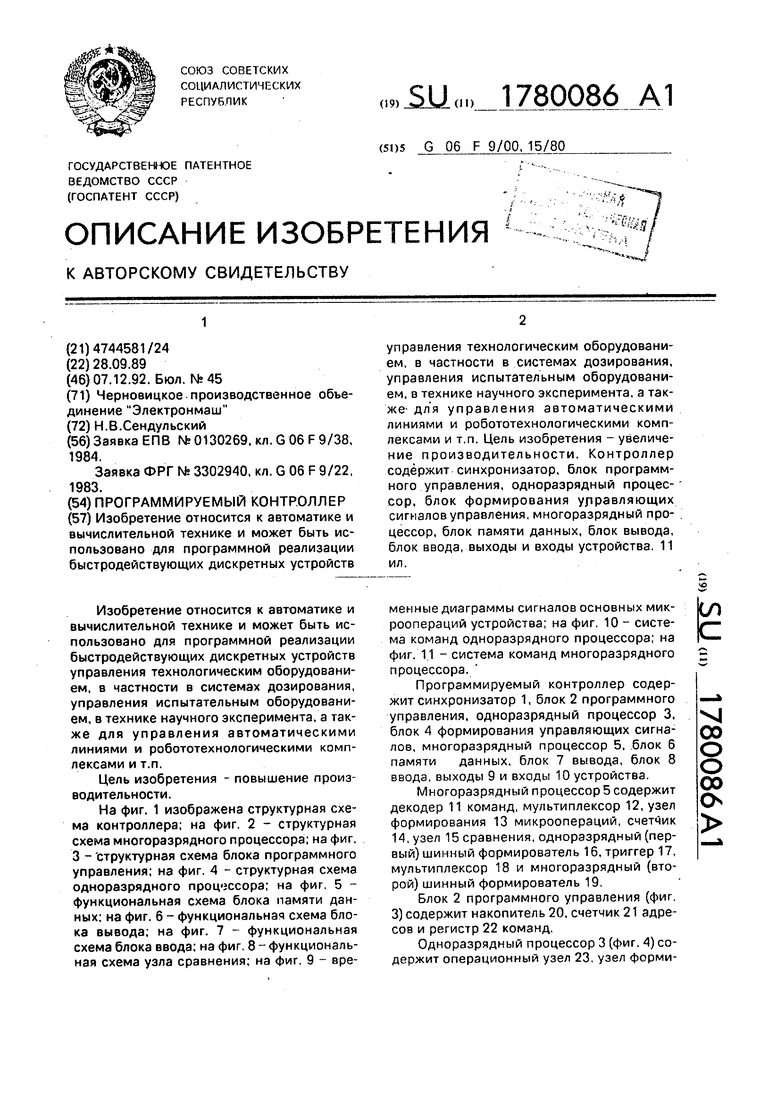

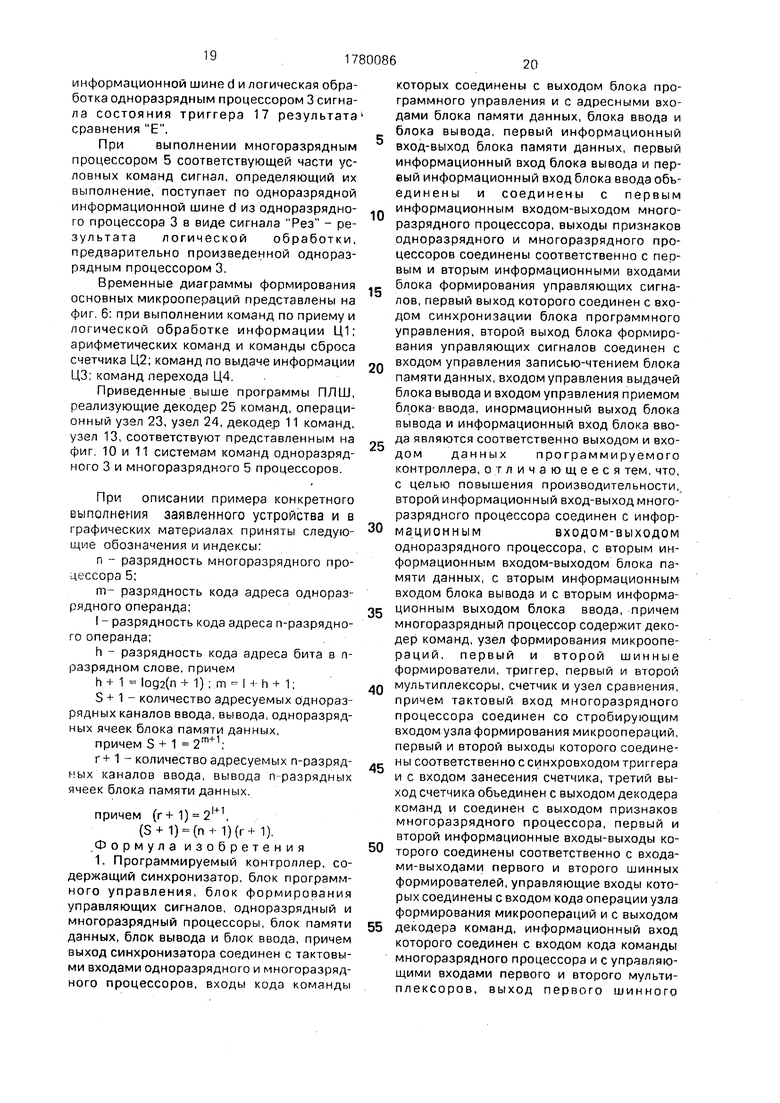

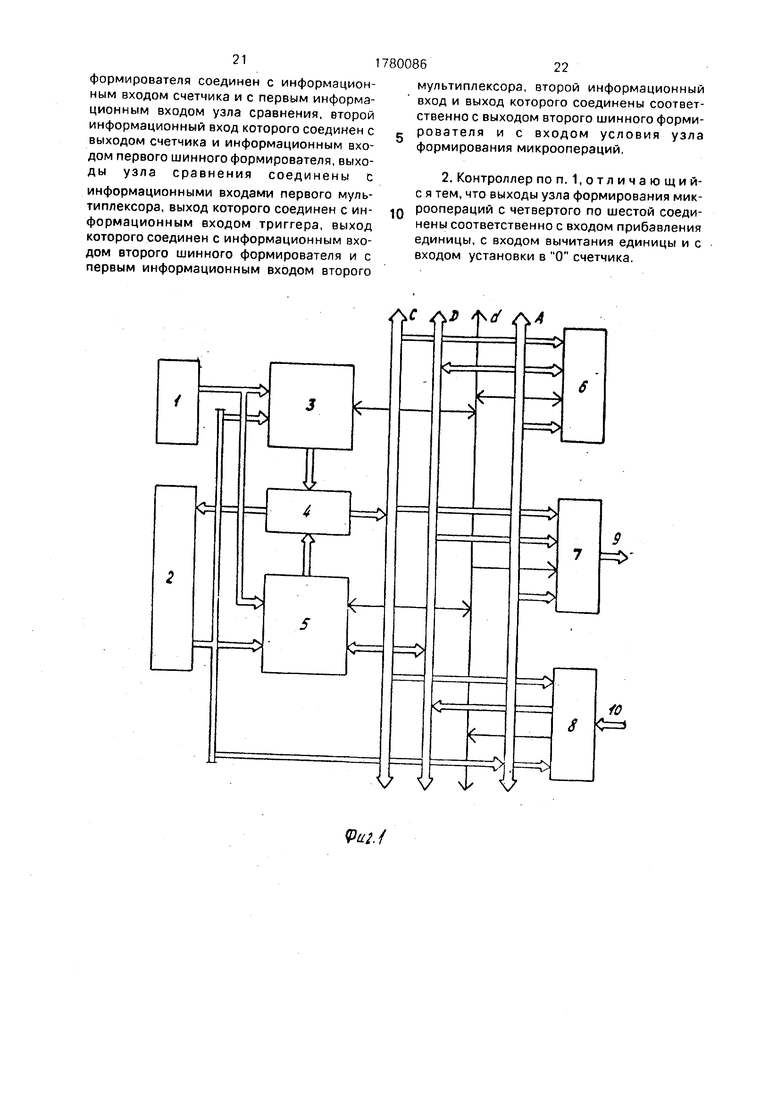

Изобретение относится к автоматике и вычислительной технике и может быть использовано для программной реализации быстродействующих дискретных устройствуправления технологическим оборудованием, в частности в системах дозирования, управления испытательным оборудованием, в технике научного эксперимента, а также- для управления автоматическими линиями и робототехнологическими комплексами и т.п. Цель изобретения - увеличение производительности. Контроллер содержит синхронизатор, блок программного управления, одноразрядный процессор, блок формирования урравляющих сигналов управления, многоразрядный процессор, блок памяти данных, блок вывода, блок ввода, выходы и входы устройства. 11 ил.Изобретение относится к автоматике и вычислительной технике и можцт быть использовано для программной реализации быстродействующих дискретных устройств управления технологическим оборудованием, в частности в системах дозирования, управления испытательным оборудованием, в технике научного эксперимента, а также для управления автоматическими линиями и робототехнологическими комплексами и т.п.Цель изобретения - повышение производительности.На фиг. 1 изображена структурная схема контроллера; на фиг. 2 - структурная схема многоразрядного процессора; на фиг. 3 - 'структурная схема блока программного управления; на фиг. 4 - структурная схема одноразрядного процессора; на фиг. 5 - функциональная схема блока памяти данных; на фиг. 6 - функциональная схема блока вывода; на фиг. 1 - функциональная схема блока ввода; на фиг. 8 - функциональная схема узла сравнения; на Фиг. 9 - временные диаграммы сигналов основных микроопераций устройства; на фиг. 10 - система команд одноразрядного процессора; на фиг. 1.1 -система команд многоразрядного процессора. 'Программируемый контроллер содержит синхронизатор 1, блок 2 программного управления, одноразрядный процессор 3, блок 4 формирования управляющих сигналов, многоразрядный процессор 5, .блок 6 памяти данных, блок 7 вывода, блок 8 ввода, выходы 9 и входы 10 устройства.Многоразрядный процессор5 содержит декодер 11 команд, мультиплексор 12, узел формирования 13 микроопераций, счетчик 14, узел 15 сравнения, одноразрядный (первый) шинный формирователь 16, триггер 17, мультиплексор 18 и многоразрядный (второй) шинный формирователь 19.Блок 2 программного управления (фиг. 3) содержит накопитель 20, счетчик 21 адресов и регистр 22 команд.Одноразрядный процессор 3 (фиг. 4) содержит операционный узел 23, узел форми-слсVI00о оСХ)ON>&

Цифрами 1 и О обозначено соответственно прямое и инверсное вхождение входной переменной в конъюнкцию.

- - входная переменная в данную конъюнкцию не входит.

Т - конъюнкция входит в выходную функцию.

/ - конъюнкция в выходную функцию не входит.

Входные сигналы второго декодер,а 25 команд - разряды регистра 22 команд РК10 -РК15.

Выходные сигналы декодера 25 команд;

1)AMS адресный сигнал мультиплексора 29:

2)CS и BS - сигнал выборки и сигнал управления одноразрядного шинного формирователя 30, причем BS: 1 - выдача информации, BS: О - прием информации;

3) - прием и логическая обработка одноразрядной информации;

4) - выдача результата обработки одноразрядной информации;

5)ОП Oi, ОП11 - разряды кода операнда:

6)1 /MI - признак разрядности обрабатываемой информации, причем 1/Mi: О соответствует одноразрядной информации:

7)n/Bi - прием или выдача информации, причем n/Bi; 0 - выдача, П/Bi; 1 - прием.

При выполнении команд по приему и обработке одноразрядной информации информационный сигнал d1 от выбранного периферийного блока поступает через

одноразрядный шинный формирователь 30 в операционный узел 23. в котором осуществляется обработка принимаемой информации d1. Операционный узел 23 представляет собой комбинированную схему. Таблица программы ПЛМ, реализующей операционный узел 23, имеет вид:

Входные сигналы операционного узла 23:

1)d1 -значение вводимого одноразрядного информационного слова;

2)АСО и ACI- предыдущие состояния триггеров 26 и 28;

3)РК12 - РК14 - разряды регистра 22 команд..

Выходные сигналы операционного узла 23 - входные информационные сигналы триггероа 26 и 28 DACO и DAC1.

Операндами при приеме и логической обработке одноразрядной информации служат информационные сигналы блока 6 памяти данных, /блока 8 ввода и триггера 17 результата сравнения многоразрядного процессора 5. Операционный узел 23 обеспечивает прием и логическую обработку прямых и инверсных значений вводимой информации следующим образом;

Входными импульсами узла 24 являются тактовые импульсы ti, +t3 и t4 синхронизатора 1 и сигналы управления декодера 25 команд.

Выходные сигналы узла 24 м;

1) 3PKi - занесение в регистр 22 команд;

1)прием (АСО) ; (d1) (АСО) ; (АС1); 0 (АС1) 0;(d,)

2)конъюнктивныйприем (АСО); (АСО) (d1) (АСО); (АСО)Л (-)

(АС1); (АС1) (АС1); (АС1)

3)дизъюнктивныйприем (АСО);

(ACOyv (d1) (АСО); (ACO)v (---

а{

(АС1); (ACO)V (АС1) (АС1); (ACO)v (AC1)

Фиксация результатов приема и логической обработки вводимой информации осуществляется микрооперацией 3 не.АС, сигнал которой выдается узлом формирования 24 микроопераций. Таблица программы ПЛМ, реализующей узел 24, имеет вид;

2)Знс.АС - занесение информации в триггеры 26 и 28 при выполнении команд

55 приема и логической обработки;

3)3Di - фиксация информационного слова блоком 7 вывода или блоком б памяти

данных при выдаче информации;

4) +CAi -инкремент счетчика 21 адресов.

Результат логической обработки Рез формируется при помощи элемента ИЛИ 27 следующим образом:

(Рез): (АСО) у (АС1).

При выполнении команд по выдаче одноразрядной информации выдаваемой одноразрядный информационный сигнал dO формируется при помощи мультиплексора 29 следующим образом;

(dO)) A(PK12)v (Рез)лРК12.

Выдаваемый информационный сигнал dO может адресоваться в блок 6 памяти данных, в блок 7 вывода, восприниматься многоразрядным процессором 5.

Связь одноразрядного процессора 3 с интерфейсной одноразрядной информационкой шиной d осуществляется посредствомдвунаправленнойшиныодноразрядного шинного формирователя 30.

Сигналы ОПй}1, ОП11,1/Mi, П/Bi. 3PKi, +1CAi. 3Di образуют выход признаков одноразрядного процессора 3.

Многоразрядный процессор 5 (фиг. 2) выполняет команды приема и логической где - - незначимые разряды командного слова;

78008610

обработки многоразрядных операндов, выдачи многоразрядных и одноразрядных информационных слов. а также арифметические команды и команды перехода. При выполнении команд приема информации выполняется также операция сравнения принимаемого информационного слова с содержимым счетчика 14 и вырабатывается логический признак Е, который фиксируется триггером 17. При этом число сравниваемых разрядов выбирается кодом формата сравнения, содержащимся в командном слове. Команды переходов, выдачи многоразрядной информации, инкремент 1, декремент 1 разделяются на безусловные и условные. Условиями выполнения условных команд могут быть следующие сигналы: Рез, Рез, Е, Е,

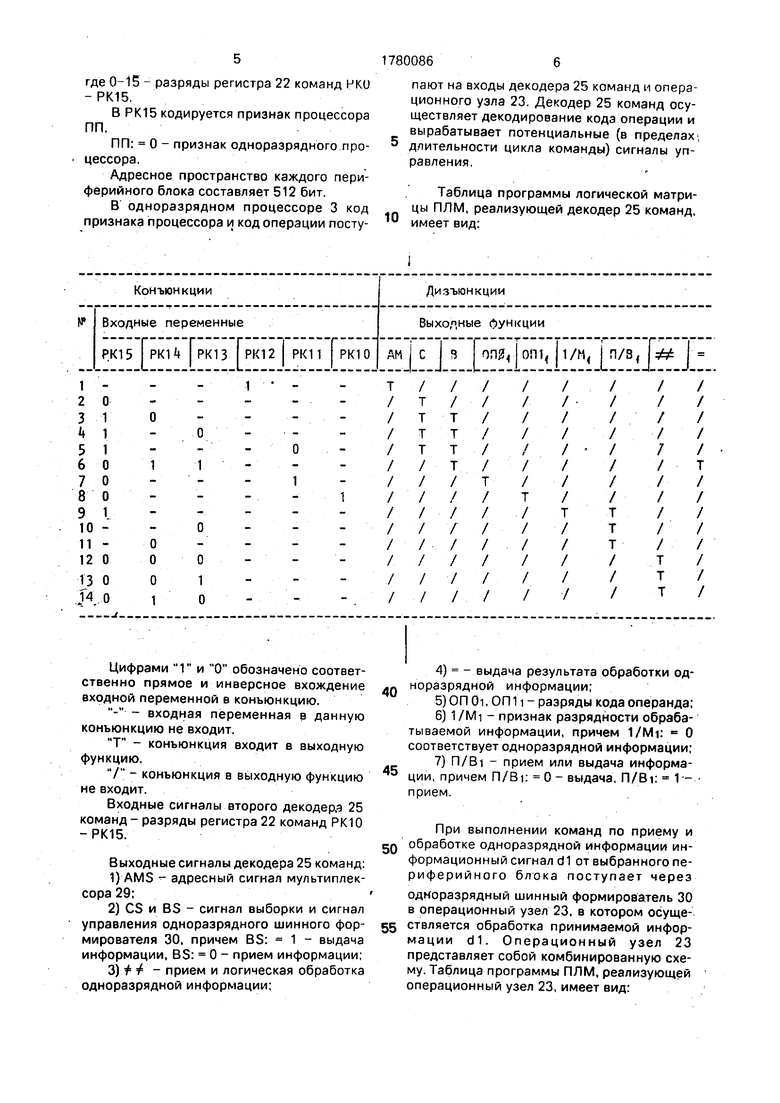

При работе многоразрядным процессором 5 выполняются команды с признаком процессора ПП: 1, Команды, выполняемые многоразрядным процессором 5, образуют группы, имеющие следующие форматы командных слов:

1) команды приема информации со сравнением, команды инкрементирование со сравнением: 15 ft 13 1 12 I 11 Гю 1 9 8 7Jh 5j 4j3r2 ljo 1 Код операцииКод формата Код адреса 2) команды безусловного и условного перехода tI., Ъ 14J13 12|n|lO|9JS 7 б 5 1зГ211|0 1 Код операции:Код адреса перехода 3) арифметические команды (инкрементдекремент безусловный, декремент 1 ус безусловный, инкремент 1 условный,ловный); 15 14 il3 J 12 I П 10 Гэ I 8 j 7 6 5 И 3 211 О 1 Код операции I сравнения блйт-клнала 45 , команда сброса операционного регистра:4) команды безусловной и условной выдачи многоразрядной информации:

5) команды выдачи одноразрядной

информации:

При з-:ом информационный объем блока 2 составляет 2К{2048) 16-разрядных слов и ограничивается в данном случае разрядностью кода адреса перехода команд перехода. Адресное пространство каждого из периферийных блоков (блока 6 памяти данлых, блока 7 вывода, блока 8 ввода) составляет 512 бит и(или) 64байта.

В многоразрядном процессоре 5 код признака и код операции декодируется декодером 11 команд, который представляет собой комбинационную схему и формирует на своих выходах потенциальные (в течение цикла команды) сигналы управления,

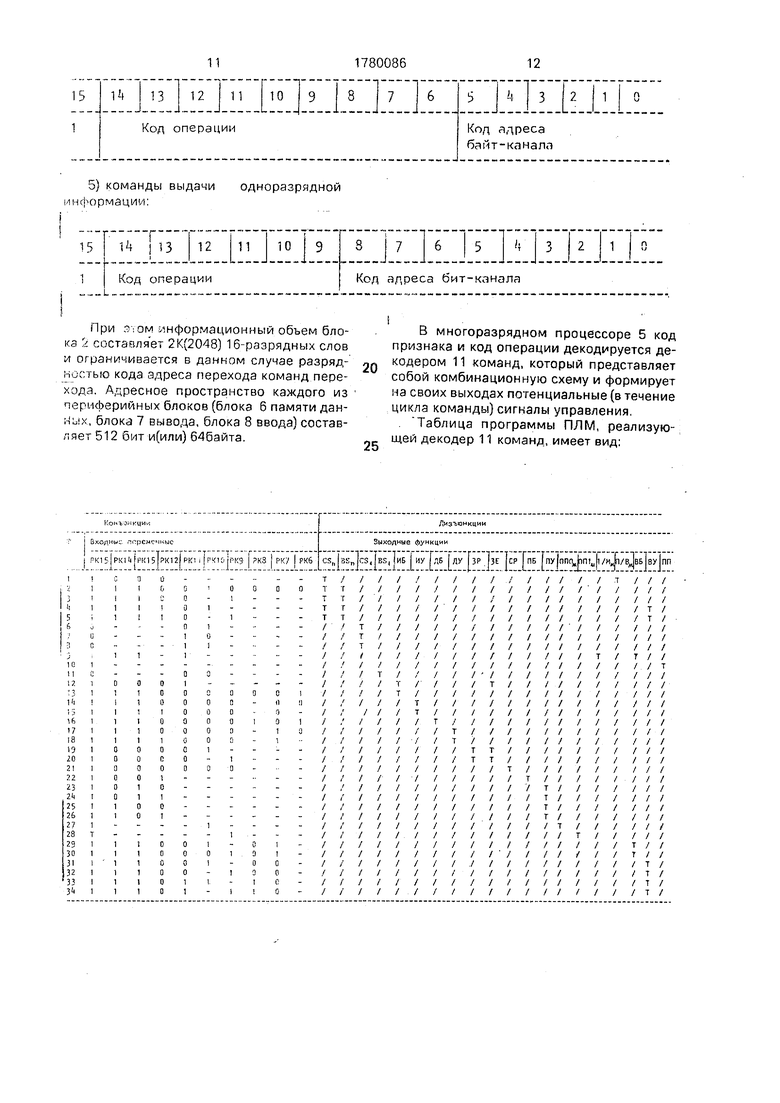

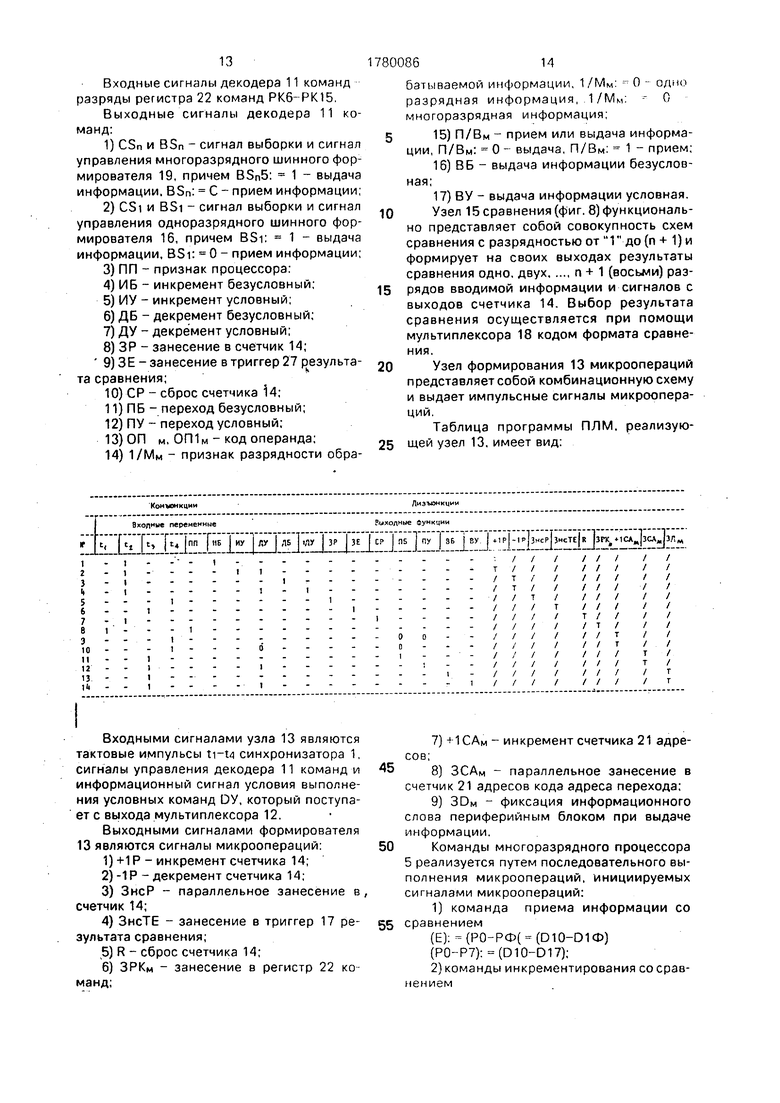

Таблица программы ПЛМ, реализующей декодер 11 команд, имеет вид:

13

Входные сигналы декодера 11 команд разряды регистра 22 команд РК6- РК15,

Выходные сигналы декодера 11 команд:

1)CSn и BSn - сигнал выборки и сигнал управления многоразрядного шинного формирователя 19, причем BSn5: 1 - выдача информации. BSn: С - прием информации:

2)CSi и BSi - сигнал выборки и сигнал управления одноразрядного шинного формирователя 16, причем BSi: 1 - выдача информации, BSi: О - прием информации:

3)ПП - признак процессора:

4)ИБ - инкремент безусловный:

5)ИУ - инкремент условный:

6)ДБ - декремент безусловный:

7)ДУ - декремент условный:

8)ЗР - занесение в счетчик 14;

9) ЗЕ - занесение в триггер 27 результата сравнения:

10)СР - сброс счетчика 14:

11)ПБ-переход безусловный:

12)ПУ переход условный:

13)ОП м, ОП1м - код операнда:

14)1/Мм - признак разрядности обраВходными сигналами узла 13 являются тактовые импульсы ti-u синхронизатора 1, сигналы управления декодера 11 команд и информационный сигнал условия выполнения условных команд ОУ, который поступает с вь1хода мультиплексора 12.

Выходными сигналами формирователя 13 являются сигналы микроопераций:

1)+1Р - инкремент счетчика 14:

2)-IP-декремент счетчика 14:

3)ЗнсР - параллельное занесение в счетчик 14;

4)ЗнсТЕ - занесение в триггер 17 результата сравнения;

5)R - сброс счетчика 14:

6)ЗРКм - занесение в регистр 22 команд:

78008614

бзтываемой информации, 1/Мм: О - одно разрядная информация, 1/Мм: - О многоразрядная информация:

515) П/Вм - прием или выдача информации, П/Вм: О - выдача, П/Вм: 1 прием:

16)ВБ - выдача информации безусловная:

17)ВУ - выдача информации условная. 10 Узел 15 сравнения (фиг, 8) функционально представляет собой совокупность схем сравнения с разрядностью от 1 до(п -ь 1)и формирует на своих выходах результаты сравнения одно, двухп + 1 (восьми) разрядов вводимой информации и сигналов с выходов счетчика 14. Выбор результата сравнения осуществляется при помощи мультиплексора 18 кодом формата сравнения,

20Узел формирования 13 микроопераций

представляет собой комбинационную схему и выдает импульсные сигналы микроопераций.

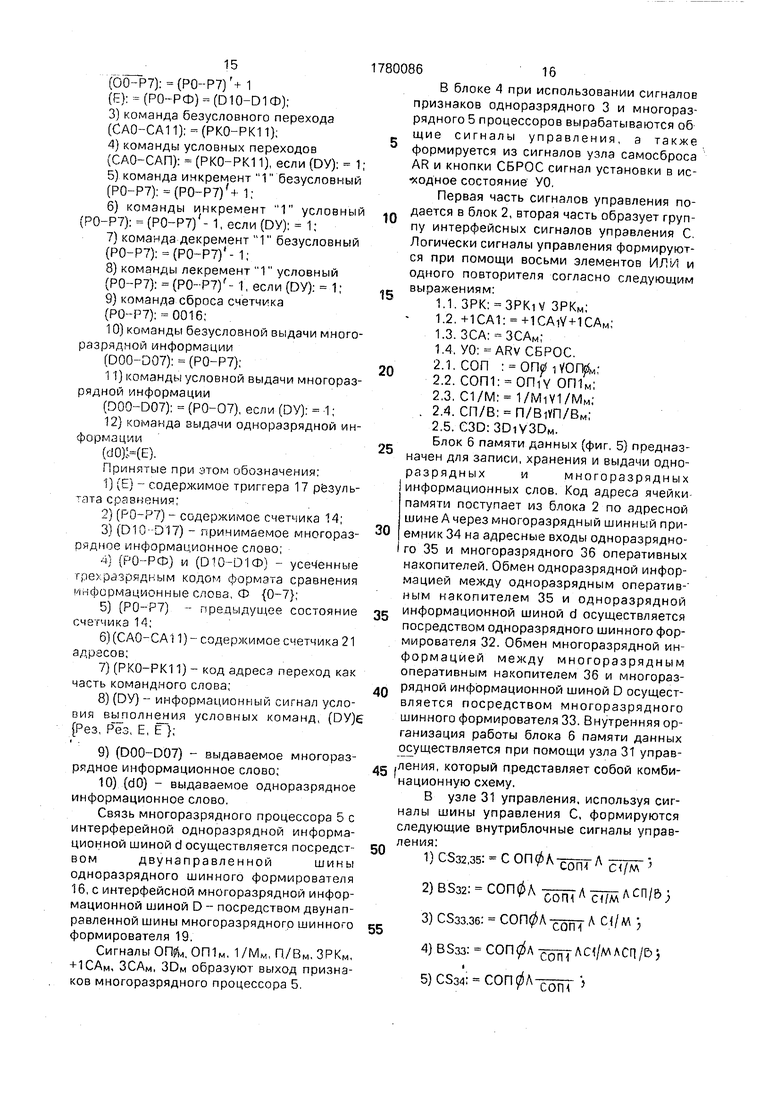

Таблица программы ПЛМ, реализую25 идей узел 13, имеет вид:

7)+1САм - инкремент счетчика 21 адресов:

8)ЗСАм параллельное занесение в счетчик 21 адресов кода адреса перехода:

9)ЗОм - фиксация информационного слова периферийным блоком при выдаче информации.

Команды многоразрядного процессора 5 реализуется путем последовательного выполнения микроопераций, инициируемых сигналами микроопераций:

1)команда приема информации со сравнением

(Е): (РО-РФ( (О10-О1Ф) (PO-P7): (D10-D17):

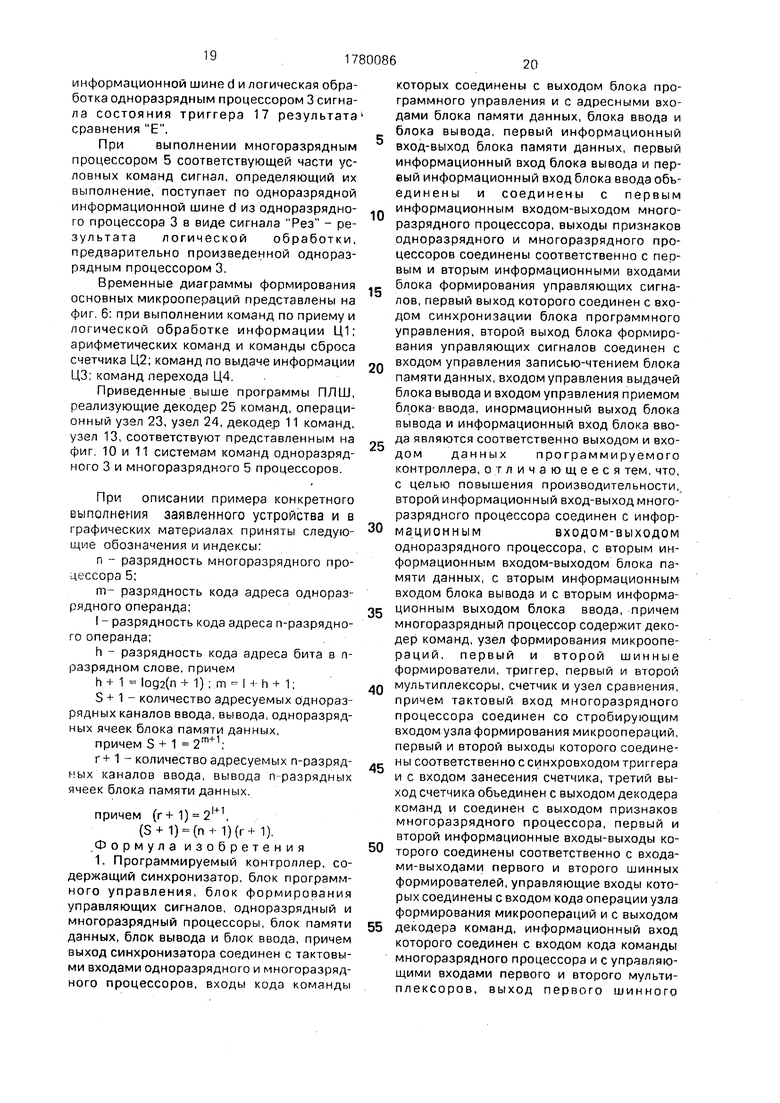

2)команды инкрементирования со сравнением15 ();(РО-Р7)+ 1 (Е): (РО-РФ) (010-01Ф); 3)команда безусловного перехода (САО-СА11): (РКО-РК11); 4)команды условных переходов (САО-САП): (РКО-РК11), если (ОУ): 1; 5)команда инкремент 1 безусловный (РО-Р7): (РО-Р7)+ 1; 6)команды инкремент 1 условный (РО-Р7): (РО-Р7) - 1, если (ОУ); 1 ; 7)команда декремент 1 безусловный {РО-Р7): (РО-Р7)- 1; 8)команды лекремент 1 условный (РО-Р7): (РО-Р7)- 1, если (ОУ): 1; 9)команда сброса счетчика (РО-Р7): 0016; 10)команды безусловной выдачи многоразрядной информации (000-007): (РО-Р7): 11)команды условной выдачи многоразрядной информации (000-007): (РО-07), если (ОУ): -1: 12)команда выдачи одноразрядной информации (dO)HE). Принятые при этом обозначения: 1)(Е) - содержимое триггера 17 результата сравнения: 2)(РО-Р7) - содержимое счетчика 14; 3)(010-D17) - гфинимаемое многоразрядное информационное слово: 4)(РО-РФ) и (010-01Ф) - усе- енные трехразрядным кодом формата сравнения информационные слова, Ф {0-7}: 5)(РО-Р7) - предыдущее состояние счетчика 14: 6)(САО-СА11)-содержимое счетчика 21 адресов: 7)(РКО-РК11) - код адреса переход как часть командного слова: 8)(ОУ) - информационный сигнал условия вьтолнения условных команд, (ОУ) Рез, Рёз, Е, 9)(DOO-007) - выдаваемое многоразрядное информационное слово: 10)(dO) - выдаваемое одноразрядное информационное слово. Связь многоразрядного процессора 5 с интерферейной одноразрядной информационной шиной d осуществляется посредствомдвунаправленнойщиныодноразрядного шинного формирователя 16, с интерфейсной многоразрядной информационной шиной О - посредством двунаправленной шины многоразрядногр шинного формирователя 19. Сигналы ОПИИ, ОП1м, 1/Мм, П./Вм,ЗРКм, + 1САм, ЗСАм, 30м образуют выход признаков многоразрядного процессора 5. 6 В блоке 4 при использовании сигналов признаков одноразрядного 3 и многоразрядного 5 процессоров вырабатываются об щие сигналы управления, а также формируется из сигналов узла самосброса AR и кнопки СБРОС сигнал установки в исходное состояние УО. Первая часть сигналов управления подается в блок 2, вторая часть образует группу интерфейсных сигналов управления С. Логически сигналы управления формируются при помощи восьми элементов и одного повторителя согласно следующим выражениям: 1.1.3PK: 3PKiV ЗРКм; 1.2.+1СА1: +1СА1У+1САм: 1.3.ЗСА:-- ЗСАм; 1.4.yO: ARV СБРОС. 2.1.СОП : ОП( 2.2.COni: OniY ОП1м: 2.3,С1/М: 1/М1У1/Мм; . 2.4. СП/В: П/В1УП/Вм; 2.5.СЗО:301УЗОм. Блок 6 памяти данных (фиг, 5) предназначен для записи, хранения и выдачи одноразрядных и многоразрядных информационных слов. Код адреса ячейкипамяти поступает из блока 2 по адресной шине А через многоразрядный шинный приемник 34 на адресные входы одноразрядного 35 и многоразрядного 36 оперативных накопителей. Обмен одноразрядной информацией между одноразрядным оперативиым накопителем 35 и одноразрядной информационной шиной d осуществляется посредством одноразрядного шинного формирователя 32. Обмен многоразрядной информацией между многоразрядным оперативным накопителем 36 и многоразрядной информационной шиной О осуществляется посредством многоразрядного шинного формирователя 33. Внутренняя организация работы блока 6 памяти данных осуществляется при помощи узла 31 управления, который представляет собой комбинационную схему. В узле 31 управления, используя сигналы шины управления С, формируются следующие внутриблочные сигналы управления:1)С5з2,35: СОП0Л- опТАс 7м- 2)В5з2: СОП0Л-ЗогйЛсТ7мЛ П/&3 3) СЗзз.зе: ; 4} В5зз: СОП0Л - рр ЛС /МЛСП/Ь J 5)С5з4: СОП0А- оЩ- j 17 6)W/R35.36: COn0A 5njQAC3D, где 32-36 - индексы, соответствующие позиционным номерам элементов блока 6 памяти данных. При обращении одноразрядного процессора 3 к блоку 6 памяти данных возможны запись или чтение одноразрядного информационного слова. При обращении многоразрядного процессора 5 к блоку 6 памяти данных возможны запись или чтение многоразрядного информационного слова, а также запись одноразрядного информационного слова. Блок 7 вывода (фиг. 6) предназначен для выдачи на выходы 9 устройства результатов обработки информации одноразрядным 3 и многоразрядным 5 процессорами в виде одноразрядных и многоразрядных слов. Код адреса канала вывода поступает с адресной шины А через многоразрядный шинный приемник 40 следующим образом: 1)на входы.дещифратора 41, кроме входа с весом 2°, поступает код адреса бит-канала:2)на входы дешифратора 42 поступает код адреса байт-канала. Внутренняя организация работы блока 7 вывода осуществляется при помощи узла 37 управлегния, который представляет собой комбинационную схему. В узле 37 управления, используя сигналы шины управления С, формируются следующие внутриблочные сигналы управления: 1)СЗзе: ЛСОП1А 2)CS39: лсоп л сопф 3)С54о: сопр с° Сп/К ) CE-I- ШГ/СОПи А сН/5 2.- 53Н ЛСОШЛа/МА Л-С51) . Шестой сигнал - сигнал R43, формируется схемой самосброса по включению питания, входящей в узел 37 управления; 38-43 - индексы, соответствующие позиционным номерам элементов блока 7 вывода. При обращении одноразрядного процессора 3 к блоку 7 вывода осуществляется выдача одноразрядного информационного слова. При обращении многоразрядного процессора 5 к блоку 7 вывода возможны выдача одноразрядного или многоразрядного информационного слова. 86 блок 8 ввода (фиг. 7) предназначен для обеспечения приема одноразрядным 3 и многоразрядным 5 процессорами выбранных информационных сигналов с входов 10 устройства для их последующей логической обработки. Код адреса канала ввода поступает с адресной шины А через многоразрядный шинный приемник 48 следующим образом: 1)на адресные входы мультиплексора 49 поступает код адреса бит-канала в информационном байте: 2)на адресные входы группы мультиплексоров 50 поступает код адреса байт-канала. Вся совокупность входных цифровых сигналов с входов 10 устройства через входные нормализаторы 51 поступает на соответствующие информационные входы мультиплексоров группы мультиплексоров 50, благодаря которым на многоразрядную информационную шину D через многоразрядный шинный передатчик 47 мультиплексируется выбранное кодом адреса байт-канала многоразрядное информационное слово. Кроме того, указанное многоразрядное информационное слово мультиплексируется при помощи мультиплексора 49 в одноразрядный информационный сигнал, который через одноразрядный шинный передатчик 46 поступает на одноразрядную информационную шину d. Внутренняя организация работы блока 8 ввода осуществляется при помощи узла 45 управления, который представляет собой комбинационную схему. В узле 45 управления, используя сигналы шины управления С, формируются следующие внутриблочные сигналы управления: ) 46 с7 лсописп/вл щ-, 2) CS47: ; ЛСОП4 АСП|В л Сч/М J 3)С548: --р ЛСОП4Асп/&/ I где 46-48 - индексы, соответствующие позиционным номерам элементов блока 8 ввода. При обращении одноразрядного процессора 3 к блоку 8 ввода осуществляется прием одноразрядного информационного слова. При обращении многоразрядного процессора 5 к блоку 8 ввода бсуществляется прием многоразрядного информационного слова. При обращении одноразрядного процессора 3 к многоразрядному процессору 5 осуществляется прием по одноразрядной 178 информационной шине d и логическая обработка одноразрядным процессором 3 сигнала состояния триггера 17 результата сравнения Е. При выполнении многоразрядным процессором 5 соответствующей части условных команд сигнал, определяющий их выполнение, поступает по одноразрядной информационной шине d из одноразрядного процессора 3 в виде сигнала Рез - результата логической обработки, предварительно произведенной одноразрядным процессором 3. Временные диаграммы формирования основных микроопераций представлены на фиг. 6: при выполнении команд по приему и логической обработке информации Ц1; арифметических команд и команды сброса счетчика Ц2; команд по выдаче информации ЦЗ: команд перехода Ц4. Приведенные выше программы ПЛШ, реализующие декодер 25 команд, операционный узел 23, узел 24, декодер 11 команд, узел 13, соответствуют представленным на фиг. 10 и 11 системам команд одноразрядного 3 и многоразрядного 5 процессоров. При описании примера конкретного выполнения заявленного устройства и в графических материалах приняты следующие обозначения и индексы: п - разрядность многоразрядного процессора 5; т- разрядность кода адреса одноразрядного операнда: I - разрядность кода адреса п-разрядного операнда; h - разрядность кода адреса бита в празрядном слове, причем h + 1 Iog2(n + 1): m I + h + 1; S + 1 - количество адресуемых одноразрядных каналов ввода,вывода,одноразрядных ячеек блока памяти данных, причем S + 1 + 1 - количество адресуемых п-разрядных каналов ввода, вывода п-разрядных ячеек блока памяти данных. причем (г+ 1) 2 (S + 1) (n + 1){r+1). Формула изобретения 1. Программируемый контроллер, содержащий синхронизатор, блок программного управления, блок формирования управляющих сигналов, одноразрядный и многоразрядный процессоры, блок памяти данных, блок вывода и блок ввода, причем выход синхронизатора соединен с тактовыми входами одноразрядного и многоразрядного процессоров, входы кода команды 20 которых соединены с выходом блока программного управления и с адресными входами блока памяти данных, блока ввода и блока вывода, первый информационный вход-выход блока памяти данных, первый информационный вход блока вывода и первый информационный вход блока ввода объединены и соединены с первым информационным входом-выходом многоразрядного процессора, выходы признаков одноразрядного и многоразрядного процессоров соединены соответственно с первым и вторым информационными входами блока формирования управляющих сигналов, первый выход которого соединен с входом синхронизации блока программного управления, второй выход блока формирования управляющих сигналов соединен с входом управления записью-чтением блока памяти данных, входом управления выдачей блока вывода и входом управления приемом блока-ввода, инормационный выход блока вывода и информационный вход блока ввода являются соответственно выходом и входом данных программируемого контроллера, отличающееся тем, что, с целью повышения производительности, второй информационный вход-выход многоразрядного процессора соединен с информационнымвходом-выходомодноразрядного процессора, с вторым информационным входом-выходом блока памяти данных, с вторым информационным входом блока вывода и с вторым информационным выходом блока ввода, причем многоразрядный процессор содержит декодер команд, узел формирования микроопераций, первый и второй шинные формирователи, триггер, первый и второй мультиплексоры, счетчик и узел сравнения, причем тактовый вход многоразрядного процессора соединен со стробирующим входом узла формирования микроопераций, первый и второй выходы которого соединены соответственно с синхровходом триггера и с входом занесения счетчика, третий выход счетчика объединен с выходом декодера команд и соединен с выходом признаков многоразрядного процессора, первый и второй информационные входы-выходы которого соединены соответственно с входами-выходами первого и второго шинных формирователей, управляющие входы которых соединены с входом кода операции узла формирования микроопераций и с выходом декодера команд, информационный вход которого соединен с входом кода команды многоразрядного процессора и с управляющими входами первого и второго мультиплексоров, выход первого шинного

21

формирователя соединен с информационным входом счетчика и с первым информационным входом узла сравнения, второй информационный вход которого соединен с выходом счетчика и информационным входом первого шинного формирователя, выходы узла сравнения соединены с информационными входами первого мультиплексора, выход которого соединен с информационным входом триггера, выход которого соединен с информационным входом второго шинного формирователя и с первым информационным входом второго

22

1780086

мультиплексора, второй информационный вход и выход которого соединены соответственно с выходом второго шинного формирователя и с входом условия узла формирования микроопераций,

9а2.

Раг.З

Фиг. 4

fPus.S

ffi/s.S

Pi/t7

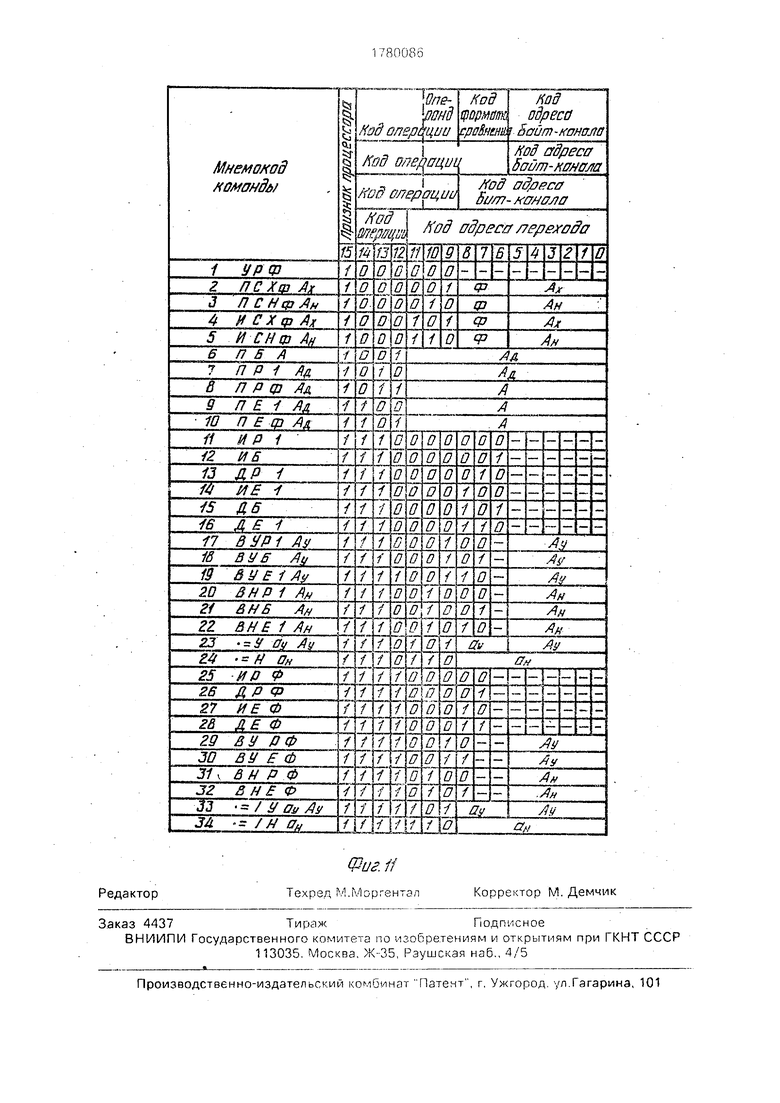

Фиг. 10

| Фронтальная навесная жатка-вязалка | 1959 |

|

SU130269A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-07—Публикация

1989-09-28—Подача