Изобретение относится к области радиотехники, в частности к способам и устройствам временной синхронизации для систем связи, в том числе с широкополосными сигналами. Изобретение также относится, но не ограничивается этим, к сотовым системам радиосвязи множественного доступа с кодовым разделением каналов (СDМА), базовым и мобильным станциям, использующим методы временной синхронизации.

Система слежения за временной задержкой сигнала используется для любой цифровой системы связи. Осуществление постоянной временной подстройки приемника необходимо в силу неидеальности часов приемника и передатчика. Кроме того, в системах подвижной связи расстояние между приемником и передатчиком, а следовательно, задержка сигнала изменяется в силу перемещения мобильной станции.

Временное слежение в системах цифровой радиосвязи строится на основе формирования оценки временной ошибки синхронизации и последующей ее коррекции. Для формирования оценки временной ошибки обычно используется временной дискриминатор, оценивающий производную корреляционной функции полезного сигнала.

При практической реализации системы слежения за задержкой возникает ряд проблем, решение которых связано с поиском компромисса между сложностью технической реализации и точностью слежения за задержкой. Кроме того, система слежения за задержкой является системой с обратной связью, следовательно, необходимо решать проблему устойчивости. Система начального поиска не обеспечивает точной синхронизации приемника и передатчика, следовательно, в начальный период работы система слежения за задержкой должна быстро устранить начальное временное рассогласование.

Решению проблемы временной синхронизации уделяется достаточно большое внимание в работе [1, Дж. Спилкер. Цифровая спутниковая связь. М. "Связь". 1979, с. 387 - 404].

Типичный вариант выполнения цифрового устройства слежения за задержкой сигнала и алгоритм его реализации рассмотрен в монографии Витерби [2, Принципы широкополосной связи. Andrew J. Viterbi. "CDMA. Principles of Spread Spectrum Communication". Addison-Wesley Wireless Communications Series, p. 60, fig. 3.6, 1995]. В данном устройстве используется слежение за задержкой типа "опережение-запаздывание", которое работает недостаточно эффективно, вследствие постоянного колебания временной позиции демодулятора вокруг истинной временной позиции принимаемого сигнала, кроме того, недостатком такого способа является медленное вхождение в синхронизм.

Известно также устройство и алгоритм его реализации, описанный [3, Дж. Дж. Олмос, Р. Агусти "Анализ и проектирование схемы слежения за задержкой второго порядка в системе CDMA", J. J. Olmos, R. Agusti. Analysis and design of the second order delay-lock loop in a CDMA system. IEEE 0-7803-0673- 2/92, 1992, стр. 221 - 224]. Это устройство содержит три параллельные ветви обработки, вторая и третья из которых содержат последовательно соединенные перемножитель, фильтр и квадратор в каждой ветви обработки, при этом перемножитель и фильтр в каждой ветви обработки выполняют функцию корреляторов, на выходе которых формируются значения корреляционных функций входного сигнала и его запаздывающей и опережающей копий, а первая ветвь обработки содержит перемножитель, на выходе которого появляется информационный сигнал, который содержится во входном широкополосном сигнале, а также это устройство содержит генератор псевдослучайных последовательностей, сумматор, фильтр низкой частоты в кольце обратной связи и управляемый генератор.

Недостатками этого устройства и алгоритма его реализации является длительный переходный процесс компенсации начальных расстроек по задержке и низкая устойчивость цифровой реализации алгоритма.

Наиболее близким техническим решением к заявляемому изобретению является устройство и алгоритм его реализации, описанные в статье А.Гонзалес, В.Руис, М. И.Лопес, С.Валдеолмиллос [4, "Моделирование устройства слежения за задержкой второго порядка в условиях многолучевого распространения". А. Gonzalez, В. Ruiz, M. I. Lopez, С. Valdeolmillos. Simulation of a second order delay locked loop ib multipath environment. IEEE 0-7803-1266-X/93].

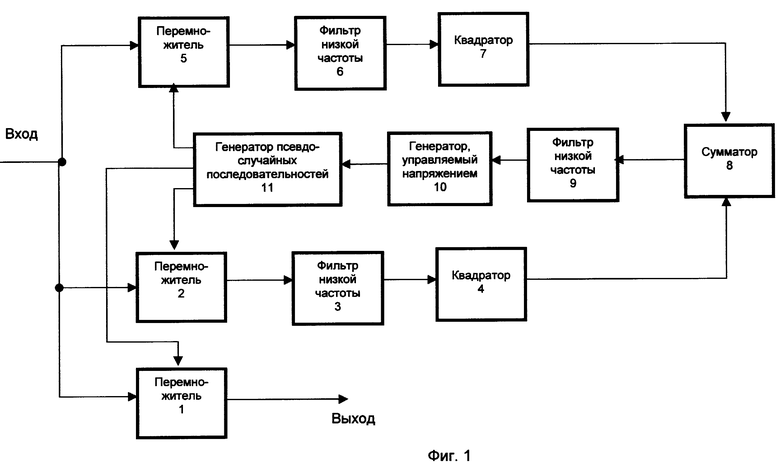

Это устройство содержит (фиг. 1) три параллельные ветви обработки, первая из которых содержит перемножитель, на выходе которого появляется информационный сигнал, который содержится во входном широкополосном сигнале, а вторая и третья - последовательно соединенные перемножитель, фильтр и квадратор в каждой ветви обработки, при этом перемножитель и фильтр во второй и третьей ветвях обработки выполняют функцию корреляторов, на выходе которых формируются значения взаимно корреляционных функций входного сигнала и его запаздывающей и опережающей копий, а также содержит генератор псевдослучайных последовательностей, сумматор, фильтр низкой частоты в кольце обратной связи и управляемый генератор.

При временной рассинхронизации принимаемого сигнала и сигнала, генерируемого генератором ПСП, величины корреляционных функций не равны в каналах опережения и отставания. На выходе сумматора присутствует разностный сигнал, характеризующий ошибку временной синхронизации. Временная позиция опорного генератора изменяется до тех пор, пока сигнал ошибки не станет равным нулю.

Недостатками такого подхода к слежению за задержкой являются длительный переходный процесс компенсации начальных расстроек по задержке и низкая устойчивость цифровой реализации алгоритма.

Задача, на решение которой направлены заявляемый способ слежения за временной задержкой сигнала и устройство для его реализации, - это ускорение переходного процесса компенсации начальных расстроек по задержке и повышение устойчивости системы при наличии обратной связи.

Поставленная задача решается следующим образом.

Во-первых, в способ слежения за временной задержкой сигнала, при котором осуществляют начальный поиск временной задержки сигнала τo, заключающийся в том, что формируют опорные сигналы, соответствующие временным позициям τo-K•Δτ и τo+K•Δτ, где К - коэффициент, характеризующий апертуру временного дискриминатора, Δτ - длительность чипа псевдослучайной последовательности, вычисляют корреляцию входного и опорных сигналов, формируя таким образом оценки корреляционной функции в моменты времени - K•Δτ и K•Δτ, дополнительно вводят следующую последовательность операций:

- начальный поиск временной задержки сигнала осуществляют с точностью до половины чипа псевдослучайной последовательности, равного Δτ,

- дополнительно формируют опорный сигнал, соответствующий временной задержке τo, при этом все опорные сигналы формируют при К, лежащем в интервале [0,25, 0,5],

- вычисляют корреляцию входного и опорного сигнала в момент времени, равный нулю, формируя, таким образом, дополнительную оценку корреляционной функции,

- восстанавливают корреляционную функцию сигнала с использованием всех полученных оценок в интервале от -0,5Δτ до 0,5Δτ,

- определяют временную позицию τ1, соответствующую максимальному значению восстановленной корреляционной функции,

- далее в течение всего времени приема сигнала:

- формируют опорные сигналы, соответствующие моментам времени τ1, τ1-L•K•Δτ и τ1+L•K•Δτ, где L - коэффициент поправки апертуры временного дискриминатора, L меньше единицы,

- вычисляют корреляцию входного и опорных сигналов, формируя, таким образом, оценку корреляционной функции в моменты времени -L•K•Δτ, ноль и L•K•Δτ,

- определяют максимальное значение корреляционной функции, при этом:

- если максимальное значение корреляционной функции окажется в момент времени -L•K•Δτ, корректируют временную позицию τ1 на величину M•L•K•Δτ, где М меньше или равно единице и является коэффициентом, характеризующим величину шага перестройки,

- если максимальное значение корреляционной функции окажется в момент времени L•K•Δτ, то корректируют временную позицию τ1 на величину M•L•K•Δτ,

- если максимальное значение корреляционной функции окажется в момент времени, равный нулю, то временную позицию τ1 не изменяют.

Во-вторых, в устройство слежения за задержкой сигнала, содержащее, по меньшей мере, три параллельные ветви обработки, первая ветвь из которых содержит перемножитель, а вторая и третья ветви - последовательно соединенные перемножитель, первый сумматор со сбросом, квадратор и второй сумматор со сбросом, при этом последовательно соединенные перемножитель, первый сумматор со сбросом, квадратор и второй сумматор со сбросом в каждой ветви обработки являются квадратурным коррелятором, и генератор псевдослучайных последовательностей, при этом первые входы перемножителей соединены с выходами генератора псевдослучайных последовательностей, дополнительно введены:

- в первую ветвь обработки последовательно соединенные первый сумматор со сбросом, квадратор и второй сумматор со сбросом, при этом последовательно соединенные перемножитель и первый сумматор со сбросом являются демодулятором, выход которого является информационным выходом устройства,

- а в устройство - блок задержки, блок коммутации, блок управления, при этом соответственно введены новые связи: вход блока задержки и первый вход блока коммутации объединены и являются сигнальным входом устройства, первый, второй, третий и четвертый выходы блока задержки подключены к входам блока коммутации, при этом четвертый выход соединен со вторым входом перемножителя в первой ветви обработки, вторые входы перемножителей во второй и третьей ветвях обработки соединены соответственно с первым и вторым выходом блока коммутации, выходы вторых сумматоров со сбросом с каждой ветви обработки соединены соответственно с первым, вторым и третьим входами блока управления, первый выход блока управления соединен со вторыми входами вторых сумматоров со сбросом в каждой ветви обработки, второй выход блока управления подключен ко вторым входам первых сумматоров со сбросом в каждой ветви обработки, третий выход блока управления соединен со входом генератора псевдослучайных последовательностей, а четвертый выход блока управления подключен к коммутатору.

Сопоставительный анализ заявляемого способа слежения за задержкой сигнала и устройства для его реализации с прототипом показывает, что заявляемое техническое решение обладает новизной. Сопоставительный анализ с другими техническими решениями [1 - 3] не позволил выявить признаки, заявленные в отличительной части формулы изобретения.

Введение новых признаков в формулу предлагаемого изобретения (способа и устройства) позволило решить проблему устойчивости системы при наличии обратной связи, исключить скачки временного положения опорного генератора.

Следовательно, изобретение отвечает критериям "новизна", "существенные отличия", "неочевидность" и соответствует изобретательскому уровню.

Описание изобретения поясняется графическими материалами. На фиг. 1 представлена блок-схема устройства-прототипа. На фиг. 2 - блок-схема заявляемого устройства слежения за временной задержкой сигнала. На фиг. 3 представлена схема блока задержки 14, схема приведена в качестве примера реализации, на которой показана коммутация выходных сигналов с блока задержки.

Устройство-прототип (фиг. 1) содержит: три параллельные ветви обработки, первая из которых содержит перемножитель 1, а вторая и третья - последовательно соединенные перемножитель, фильтр и квадратор в каждой ветви обработки, при этом перемножитель и фильтр во второй и третьей ветвях обработки выполняют функцию корреляторов, т.е. первая ветвь обработки содержит последовательно соединенные перемножитель 2, фильтр низкой частоты 3, квадратор 4, вторая ветвь обработки содержит перемножитель 5, фильтр низкой частоты 6 и квадратор 7, сумматор 8, фильтр низкой частоты 9, генератор 10, управляемый напряжением, и генератор 11 псевдослучайной последовательности.

Заявляемое устройство слежения за временной задержкой сигнала (фиг. 2) содержит: три параллельные ветви обработки, каждая из которых содержит последовательно соединенные перемножитель, первый сумматор со сбросом, квадратор и второй сумматор со сбросом, при этом последовательно соединенные перемножитель, первый сумматор со сбросом, квадратор и второй сумматор со сбросом в каждой ветви обработки являются квадратурными корреляторами, т.е. первая ветвь обработки содержит последовательно соединенные перемножитель 1, первый сумматор со сбросом 11, квадратор 12 и второй сумматор со сбросом 13, причем последовательно соединенные перемножитель и первый сумматор со сбросом являются демодулятором, выход которого является информационным выходом устройства, вторая ветвь обработки содержит последовательно соединенные перемножитель 2, первый сумматор со сбросом 3, квадратор 4 и второй сумматор со сбросом 5, третья ветвь обработки содержит последовательно соединенные перемножитель 6, первый сумматор со сбросом 7, квадратор 8 и второй сумматор со сбросом 9; генератор псевдослучайной последовательности 10, блок задержки 14, блок коммутации 15 и блок управления 16, при этом первые входы перемножителей 1, 2, 6 соединены с выходами генератора псевдослучайных последовательностей 10, вход блока задержки 14 и первый вход блока коммутации 15 объединены и являются сигнальным входом устройства, первый, второй, третий и четвертый выходы блока задержки 14 подключены к входам блока коммутации 15, при этом четвертый выход блока коммутации 15 соединен со вторым входом перемножителя 1 в первой ветви обработки, вторые входы перемножителей 2 и 6 во второй и третьей ветвях обработки соединены соответственно с первым и вторым выходом блока коммутации 15, выходы вторых сумматоров со сбросом 5, 9 и 13 с каждой ветви обработки соединены соответственно с первым, вторым и третьим входами блока управления 16, первый выход блока управления 16 соединен со вторыми входами вторых сумматоров со сбросом 5, 9, 13 в каждой ветви обработки, второй выход блока управления 16 подключен ко вторым входам первых сумматоров со сбросом 3, 7, 11 в каждой ветви обработки, третий выход блока управления 16 соединен со входом генератора псевдослучайных последовательностей 10, а четвертый выход блока управления 16 подключен к коммутатору 15.

Блок задержки 14 (фиг. 3) содержит первый 17, второй 18, третий 19 и четвертый 20 элементы задержки.

Заявляемый "Способ слежения за временной задержкой сигнала" реализуют, используя блок-схему устройств, изображенных на фиг. 2 и 3, следующим образом.

Предварительно проводят начальный поиск временной задержки сигнала τo с точностью до половины чипа псевдослучайной последовательности, равного Δτ.

Входной широкополосный сигнал поступает на вход блока задержки 14 и первый вход блока коммутации 15.

Величина апертуры временного дискриминатора в режиме слежения KΔτ на первом шаге при вхождении в синхронизм выбирается достаточно большой и определяется, исходя из ширины априорного интервала возможных значений временного положения. Блок задержки 14 (фиг. 3) в этом случае использует четыре элемента задержки 17, 18, 19 и 20. Апертура временного дискриминатора LKΔτ, на который осуществляется задержка сигнала в каждом элементе задержки, должна быть меньше величины шага перестройки генератора ПСП 10, так как в этом случае можно "перепрыгнуть" через точную временную позицию. В то же время, увеличение апертуры временного дискриминатора также нежелательно, так как это приводит к ухудшению оценки производной корреляционной функции сигнала. В режиме слежения используются два элемента задержки 18 и 19. Если требуемое временное разрешение системы слежения равно 1/8 Δτ, то при реализации устройства слежения за временной задержкой сигнала следует положить LK равным 1/8 (LK = 1/8).

Блок коммутации 15 осуществляет коммутацию выходных сигналов с блока задержки 14, как показано на фиг. 3. Выходные сигналы с блока коммутации 15 поступают на вторые входы перемножителей 2 и 6 соответственно второй и третьей ветвей обработки. А на второй вход перемножителя 1 первой ветви обработки поступает сигнал с четвертого выхода блока задержки 14. На первые входы перемножителей 1, 2 и 3 всех ветвей обработки поступает псевдослучайная последовательность с генератора ПСП 10, который формирует опорные сигналы, соответствующие временным позициям τo-K•Δτ, τo и τo+K•Δτ, где К - коэффициент, характеризующий апертуру временного дискриминатора (временной сдвиг в сторону опережения и отставания), Δτ - длительность чипа псевдослучайной последовательности, и формирует опорный сигнал, соответствующий временной задержке τo, при этом все опорные сигналы формируют при К, лежащем в интервале [0,25, 0,5].

Вычисляют корреляцию входного и опорного сигналов, формируя таким образом оценку в момент времени, равный нулю, для выполнения этих операций используют первую ветвь обработки, в которой последовательно соединенные перемножитель 1, первый сумматор со сбросом 11, квадратор 12 и второй сумматор со сбросом 13 выполняют функцию квадратурного коррелятора.

Вычисляют корреляцию входного и опорного сигналов, формируя таким образом оценки корреляционной функции в момент времени K•Δτ (в сторону опережения), для выполнения этих операций используют вторую ветвь обработки, в которой последовательно соединенные перемножитель 2, первый сумматор со сбросом 3, квадратор 4 и второй сумматор со сбросом 5 выполняют функцию квадратурного коррелятора.

Вычисляют корреляцию входного и опорного сигналов, формируя таким образом оценки корреляционной функции в момент времени -K•Δτ (в сторону отставания), для выполнения этих операций используют третью ветвь обработки, в которой последовательно соединенные перемножитель 6, первый сумматор со сбросом 7, квадратор 8 и второй сумматор со сбросом 9 выполняют функцию квадратурного коррелятора.

Выходные сигналы с каждой ветви обработки поступают на блок управления 16. После получения первой оценки блок управления 16 осуществляет интерполяцию и вычисление временной позиции, соответствующей максимальному значению восстановленной корреляционной функции, после чего по выходному сигналу с блока управления 16 генератор ПСП 10 формирует опорные сигналы, соответствующие моментам временит τ1, τ1-L•K•Δτ и τ1+L•K•Δτ, где L - коэффициент поправки апертуры временного дискриминатора, L меньше единицы (L < 1), т.е. выполняет первую коррекцию временной позиции.

Параллельно по выходному сигналу с блока управления 16 блок коммутации 15 коммутирует выходные сигналы элементов линии задержки 17 и 20 в положения, противоположные показанным на фиг. 3, после этого их положение не меняется в течение всего времени демодуляции луча сигнала.

Вычисляют корреляцию входного и опорных сигналов, формируя, таким образом, оценку корреляционной функции в моменты времени -L•K•Δτ, ноль L•K•Δτ.

Затем блок управления 16 переходит в режим слежения, сравнивает величины накопления, полученные в сумматорах 5, 9 и 13, определяет максимальное значение корреляционной функции и по результатам сравнения корректирует временную позицию следующим образом:

- если максимальное значение корреляционной функции (накопление в сумматоре со сбросом 9) окажется в момент времени -L•K•Δτ, то корректируют временную позицию τ1 в сторону запаздывания на величину -M•L•K•Δτ, где М меньше или равно единице (М ≤ 1) и является коэффициентом, характеризующим величину шага перестройки,

- если максимальное значение корреляционной функции (накопление в сумматоре со сбросом 5) окажется в момент времени L•K•Δτ, то корректируют временную позицию τ1 в сторону опережения на величину M•L•K•Δτ, где М меньше или равно единице (М ≤ 1) и является коэффициентом, характеризующим величину шага перестройки,

- если максимальное значение корреляционной функции (накопление в сумматоре 13) окажется в момент времени, равный нулю, то временную позицию τ1 не изменяют.

Блок задержек 14 (фиг. 3) работает следующим образом. Величина K•Δτ, на первом шаге при вхождении в синхронизм выбирается достаточно большой и определяется исходя из ширины априорного интервала возможных значений временного положения. При последующих шагах в режиме слежения значение апертуры временного дискриминатора K•Δτ, существенно меньше (например, LK•Δτ = 1/8Δτ) и может не меняться. Различное значение апертуры временного дискриминатора на первом и на последующих шагах обеспечивается, например, четырьмя линиями задержки, как показано на фиг. 3. На первом шаге задействованы все 4 линии задержки 17 - 20. Со второго шага блок коммутации 15 по управляющему сигналу с блока управления 16 производит отключение первой 17 и четвертой 20 линий задержки.

Блок управления 16 может быть реализован на процессоре и выполняет следующие операции: анализирует значения корреляционных функций, поступающих с каждой из трех ветвей обработки (после сумматоров со сбросом 5, 9, 13). В результате формирует корректирующий сигнал, поступающий на генератор ПСП 10. Корректирующий временной сдвиг на первом и на последующих шагах определяется по разным алгоритмам. На первом шаге по методу полиномиальной аппроксимации определяется положение максимального значения корреляционной функции в пределах всего априорного интервала. Корректирующий временной сдвиг τ1 здесь может принимать различные значения. На втором и последующих шагах блок управления 16 находит максимальное значение из трех поступающих с каждой ветви обработки величин корреляционной функции. Корректирующий временной сдвиг соответствует ветви с максимальным сигналом и может принимать значения -M•L•K•Δτ, ноль и M•L•K•Δτ.

Блок управления осуществляет коммутацию выходных сигналов с блока задержки 14 после первого шага.

Кроме того, блок управления 16 посылает команды сброса на сумматоры 3, 5, 7, 9, 11 и 13 в соответствии с интервалами когерентного и некогерентного накопления при формировании корреляционной функции в каждой ветви обработки.

Таким образом, заявляемые способ и устройство для его реализации, используя переменный шаг анализа и коррекции, позволяют существенно сократить время вхождения в синхронизм при сохранении высокой точности последующего временного слежения, а учет накопления в канале, связанном с демодулятором данных, позволит снизить дисперсию временной ошибки.

Предлагаемое изобретение позволило решить задачу по ускорению переходного процесса компенсации начальных расстроек по задержке, то есть сократить время вхождения в синхронизм, и повышению устойчивости системы при наличии обратной связи.

Изобретение относится к области радиотехники, в частности к способам и устройствам временной синхронизации для систем связи, в том числе с широкополосными сигналами, к сотовым системам радиосвязи множественного доступа с кодовым разделением каналов, базовым и мобильным станциям, использующим методы временной синхронизации. Достигаемый технический результат - ускорение переходного процесса компенсации начальных расстроек по задержке и повышение устойчивости системы при наличии обратной связи. Заявленный способ и устройство, используя переменный шаг анализа и коррекции, позволяют существенно сократить время вхождения в синхронизм при сохранении высокой точности последующего временного слежения, а учет накопления в канале, связанном с демодулятором данных, позволяет снизить дисперсию временной ошибки. Устройство слежения за временной задержкой содержит генератор псевдослучайных последовательностей, блок коммутации, блок задержки, блок управления, а также три параллельных ветви обработки, каждая из которых содержит перемножитель, первый сумматор со сбросом, квадратор, второй сумматор со сбросом. 2 с.п. ф-лы, 3 ил.

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ СИГНАЛА | 1997 |

|

RU2128398C1 |

| СПОСОБ СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1990 |

|

RU2011302C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| US 4355398, 19.10.1982 | |||

| US 4627080, 02.12.1986 | |||

| US 4726043, 16.02.1988. | |||

Авторы

Даты

2000-10-10—Публикация

1999-06-24—Подача