Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления.

Известно устройство (аналог) (А.с. СССР №1683013, МКИ G 06 F 7/72, Б.И. №41, 1991 г.), содержащее дешифраторы, элемент ИЛИ - НЕ, элементы И и НЕ, группы элементов ИЛИ и И, коммутатор и шифратор. Недостаток устройства - сложность построения.

Известно устройство (аналог) (патент РФ №2157560, МКИ G 06 F 7/72, 7/49; Б.И. №28, 2000 г.), содержащее шифраторы, блоки элементов И, мультиплексоры, табличные вычислители, регистры, преобразователи кода, блоки умножения на константу по модулю, квадраторы по модулю, блоки деления на четыре по модулю. Недостаток устройства - сложность построения.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является устройство (патент РФ №2188448, МКИ G 06 F 7/72, Б.И. №24, 2002 г.), содержащее дешифраторы, шифратор, управляемые фазовращатели, генератор гармонического сигнала, фазовращатели на фиксированное значение фазы и измеритель фазы гармонического сигнала.

Недостаток прототипа - сложность построения ввиду низкой загрузки используемых узлов при выполнении модульной операции. В устройстве применяется для каждого слагаемого отдельные дешифратор и управляемый фазовращатель, которые при проведении модульной операции используются однократно, что составляет основной недостаток прототипа.

Задача, на решение которой направлено заявляемое устройство, состоит в повышении надежности перспективных образцов вычислительной техники.

Технический результат выражается в упрощении устройства.

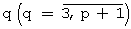

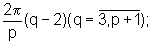

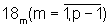

Технический результат достигается тем, что в известное устройство для сложения N чисел по модулю, содержащее дешифратор, шифратор, управляемый фазовращатель, генератор гармонического сигнала, (р-1) фазовращателей на фиксированные значения фазы и измеритель фазы гармонического сигнала, причем выход генератора гармонического сигнала соединен с входом 2 измерителя фазы гармонического сигнала, вход  которого соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное

которого соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное  (q-2), при этом вход (р+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход дешифратора подключен ко второму входу управляемого фазовращателя, выход измерителя фазы гармонического сигнала соединен с входом шифратора, выход которого является выходом устройства, согласно изобретению, введены мультиплексор, коммутатор, амплитудный детектор и усилитель гармонического сигнала, причем выход генератора гармонического сигнала соединен со входом коммутатора, управляющий вход которого соединен с выходом амплитудного детектора, а выход - со входом амплитудного детектора, с входом 1 измерителя фазы гармонического сигнала и с первым входом управляемого фазовращателя, выход которого соединен с входом усилителя гармонического сигнала, выход усилителя гармонического сигнала соединен с входом 1 измерителя фазы гармонического сигнала и с входом амплитудного детектора, управляющий вход устройства соединен с адресным входом мультиплексора, выход которого соединен со входом дешифратора, а информационные входы мультиплексора являются входами устройства.

(q-2), при этом вход (р+2) измерителя фазы гармонического сигнала является тактовым входом устройства, выход дешифратора подключен ко второму входу управляемого фазовращателя, выход измерителя фазы гармонического сигнала соединен с входом шифратора, выход которого является выходом устройства, согласно изобретению, введены мультиплексор, коммутатор, амплитудный детектор и усилитель гармонического сигнала, причем выход генератора гармонического сигнала соединен со входом коммутатора, управляющий вход которого соединен с выходом амплитудного детектора, а выход - со входом амплитудного детектора, с входом 1 измерителя фазы гармонического сигнала и с первым входом управляемого фазовращателя, выход которого соединен с входом усилителя гармонического сигнала, выход усилителя гармонического сигнала соединен с входом 1 измерителя фазы гармонического сигнала и с входом амплитудного детектора, управляющий вход устройства соединен с адресным входом мультиплексора, выход которого соединен со входом дешифратора, а информационные входы мультиплексора являются входами устройства.

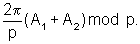

Сущность изобретения заключается в многократном использовании узла, состоящего из дешифратора и управляемого фазовращателя для представления каждого слагаемого и проведения операции модульного сложения. В фазовращателе сдвиг фазы Δϕi прямо пропорционален значению i-го слагаемого  т.е.

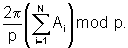

т.е.  где р - величина модуля. Таким образом, после последовательного прохождения гармонического сигнала через фазовращатель фаза гармонического сигнала на его выходе будет прямо пропорциональна значению модуля суммы N чисел. Мультиплексор предназначен для последовательной подачи одного из N слагаемых на вход дешифратора путем подачи на его адресный вход возрастающих по величине двоичных кодов чисел. Амплитудный детектор обеспечивает преобразование гармонического сигнала в постоянное напряжение. Оно поступает на управляющий вход коммутатора и прекращает подачу гармонического сигнала с выхода генератора на вход управляемого фазовращателя.

где р - величина модуля. Таким образом, после последовательного прохождения гармонического сигнала через фазовращатель фаза гармонического сигнала на его выходе будет прямо пропорциональна значению модуля суммы N чисел. Мультиплексор предназначен для последовательной подачи одного из N слагаемых на вход дешифратора путем подачи на его адресный вход возрастающих по величине двоичных кодов чисел. Амплитудный детектор обеспечивает преобразование гармонического сигнала в постоянное напряжение. Оно поступает на управляющий вход коммутатора и прекращает подачу гармонического сигнала с выхода генератора на вход управляемого фазовращателя.

Усилитель гармонического сигнала служит для компенсации потерь, возникающих при сдвиге фазы в управляемом фазовращателе, реализованном на основе линии задержки.

Несмотря на определенное снижение быстродействия предлагаемого устройства по сравнению с прототипом, оно может найти применение в вычислительных структурах, реализованных на управляемых фазовращателях, с целью унификации оборудования. Дополнительным достоинством данного устройства является гибкое изменение числа слагаемых от 2 до N путем регулирования частоты тактирующего сигнала.

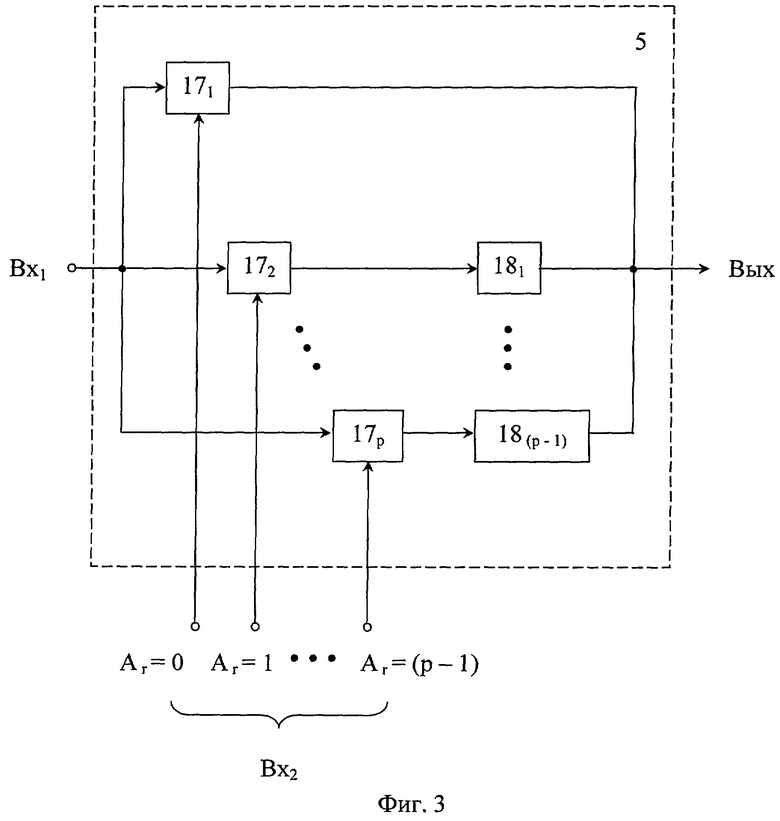

На фиг.1 представлена структурная схема предлагаемого устройства, где: 1 - генератор гармонического сигнала, 2 - измеритель фазы гармонического сигнала, 3 - фазовращатели на фиксированное значение фазы, равное  4 - дешифратор, 5 - управляемый фазовращатель, 6 - шифратор, 7 - выход устройства, 8 - коммутатор, 9 - амплитудный детектор, 10 - усилитель гармонического сигнала, 11 - управляющий вход устройства, 12 - мультиплексор, 131÷13N - входы устройства.

4 - дешифратор, 5 - управляемый фазовращатель, 6 - шифратор, 7 - выход устройства, 8 - коммутатор, 9 - амплитудный детектор, 10 - усилитель гармонического сигнала, 11 - управляющий вход устройства, 12 - мультиплексор, 131÷13N - входы устройства.

Выход генератора 1 гармонического сигнала соединен с входом 2 измерителя фазы 2 гармонического сигнала, вход  которого соединен с выходом генератора 1 гармонического сигнала через фазовращатель 3 на фиксированное значение фазы, равное

которого соединен с выходом генератора 1 гармонического сигнала через фазовращатель 3 на фиксированное значение фазы, равное  при этом вход (р+2) измерителя фазы 2 гармонического сигнала является тактовым входом устройства, выход дешифратора 4 подключен ко второму входу управляемого фазовращателя, 5 - выход измерителя фазы 2 гармонического сигнала соединен с входом шифратора 6, выход которого является выходом 7 устройства, выход генератора 1 гармонического сигнала соединен со входом коммутатора 8, управляющий вход которого соединен с выходом амплитудного детектора 9, а выход - со входом амплитудного детектора 9, с входом 1 измерителя фазы 2 гармонического сигнала и с первым входом управляемого фазовращателя 5, выход которого соединен с входом усилителя 10 гармонического сигнала, а его выход соединен с входом 1 измерителя фазы 2 гармонического сигнала и с входом амплитудного детектора 9, управляющий вход 11 устройства соединен с адресным входом мультиплексора 12, выход которого соединен со входом дешифратора 4, а информационные входы мультиплексора являются входами 131÷13N устройства.

при этом вход (р+2) измерителя фазы 2 гармонического сигнала является тактовым входом устройства, выход дешифратора 4 подключен ко второму входу управляемого фазовращателя, 5 - выход измерителя фазы 2 гармонического сигнала соединен с входом шифратора 6, выход которого является выходом 7 устройства, выход генератора 1 гармонического сигнала соединен со входом коммутатора 8, управляющий вход которого соединен с выходом амплитудного детектора 9, а выход - со входом амплитудного детектора 9, с входом 1 измерителя фазы 2 гармонического сигнала и с первым входом управляемого фазовращателя 5, выход которого соединен с входом усилителя 10 гармонического сигнала, а его выход соединен с входом 1 измерителя фазы 2 гармонического сигнала и с входом амплитудного детектора 9, управляющий вход 11 устройства соединен с адресным входом мультиплексора 12, выход которого соединен со входом дешифратора 4, а информационные входы мультиплексора являются входами 131÷13N устройства.

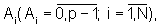

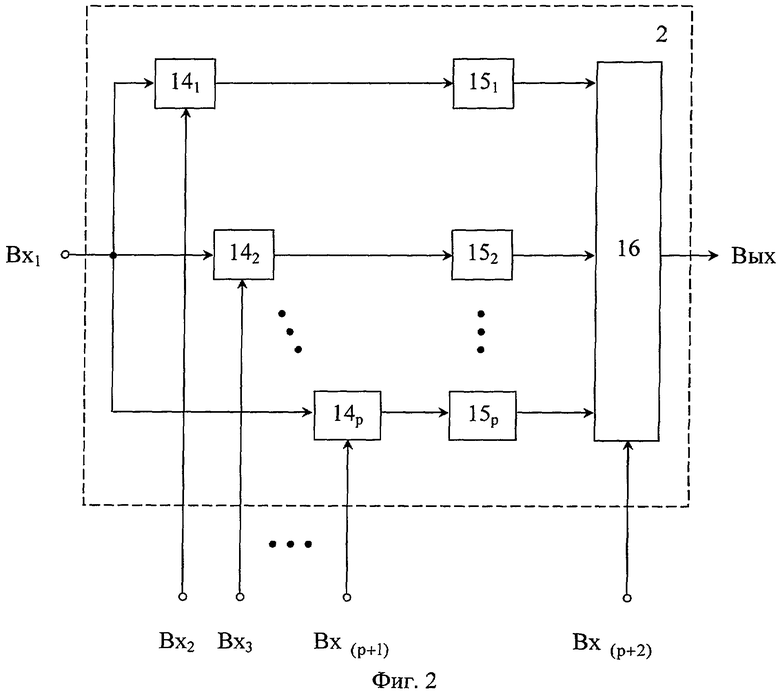

На фиг.2 представлена структурная схема измерителя фазы гармонического сигнала 2, где  - входы измерителя фазы, 141÷14р - аналоговые перемножители, 151÷15р - интеграторы, 11 - решающее устройство.

- входы измерителя фазы, 141÷14р - аналоговые перемножители, 151÷15р - интеграторы, 11 - решающее устройство.

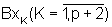

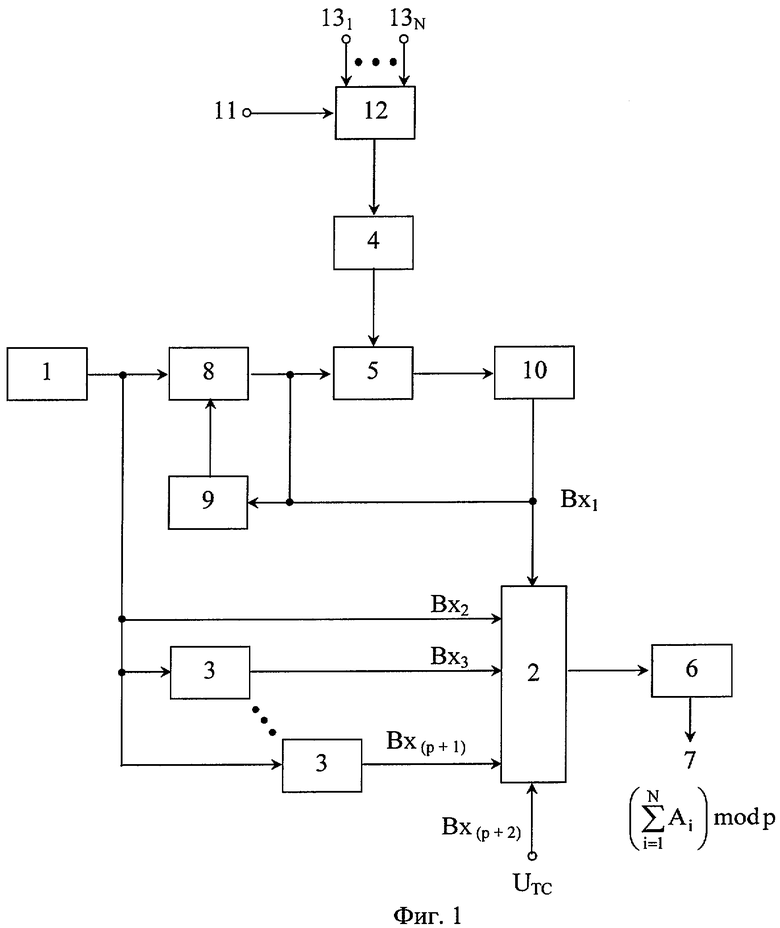

На фиг.3 представлена структурная схема управляемого фазовращателя 5, где: Bx1 и Вх2 - входы управляемого фазовращателя, 171÷17р - коммутаторы гармонического сигнала,  - линии задержки на время

- линии задержки на время  (ω - несущая частота гармонического сигнала).

(ω - несущая частота гармонического сигнала).

Рассмотрим работу устройства. На N входов 131÷13N устройства поступают двоичные позиционные коды чисел  С генератора 1 через открытый коммутатор 8 на первый вход управляемого фазовращателя 5 поступает гармонический сигнал. На управляющий вход 11 устройства поступает двоичный код, обеспечивающий соединение входа 131 устройства с выходом мультиплексора 12. После преобразования двоичного кода числа A1 дешифратора 4 в унитарный код он поступает на второй вход управляемого фазовращателя 5. В соответствии со значениями унитарного кода числа A1 в управляемом фазовращателе 5 путем подключения коммутаторами 171÷17p соответствующих линий задержки 181÷18(p-1) устанавливается набег фазы равный

С генератора 1 через открытый коммутатор 8 на первый вход управляемого фазовращателя 5 поступает гармонический сигнал. На управляющий вход 11 устройства поступает двоичный код, обеспечивающий соединение входа 131 устройства с выходом мультиплексора 12. После преобразования двоичного кода числа A1 дешифратора 4 в унитарный код он поступает на второй вход управляемого фазовращателя 5. В соответствии со значениями унитарного кода числа A1 в управляемом фазовращателе 5 путем подключения коммутаторами 171÷17p соответствующих линий задержки 181÷18(p-1) устанавливается набег фазы равный  С выхода фазовращателя 5 гармонический сигнал проходит через усилитель 10 гармонического сигнала, который обеспечивает компенсацию потерь, связанных с прохождением через линии задержки 181÷18(р-1). Сигнал с выхода усилителя 10 через амплитудный детектор 9 в виде постоянного напряжения поступает на управляющий вход коммутатора 8. При этом обеспечивается отключение гармонического сигнала с генератора 1 от первого входа управляемого фазовращателя 5. Теперь сюда поступает гармонический сигнал с выхода усилителя 10 с набегом фазы, соответствующим первому слагаемому A1. На адресный вход мультиплексора 12 поступает двоичный код, обеспечивающий соединение входа 132 устройства со входом дешифратора 4. Следовательно, на выходе фазовращателя 5 устанавливается суммарный набег фазы равный

С выхода фазовращателя 5 гармонический сигнал проходит через усилитель 10 гармонического сигнала, который обеспечивает компенсацию потерь, связанных с прохождением через линии задержки 181÷18(р-1). Сигнал с выхода усилителя 10 через амплитудный детектор 9 в виде постоянного напряжения поступает на управляющий вход коммутатора 8. При этом обеспечивается отключение гармонического сигнала с генератора 1 от первого входа управляемого фазовращателя 5. Теперь сюда поступает гармонический сигнал с выхода усилителя 10 с набегом фазы, соответствующим первому слагаемому A1. На адресный вход мультиплексора 12 поступает двоичный код, обеспечивающий соединение входа 132 устройства со входом дешифратора 4. Следовательно, на выходе фазовращателя 5 устанавливается суммарный набег фазы равный  Процесс повторяется и гармонический сигнал с выхода усилителя 10 снова поступает на первый вход фазовращателя 5, пока суммарный набег фазы сигнал не будет равен

Процесс повторяется и гармонический сигнал с выхода усилителя 10 снова поступает на первый вход фазовращателя 5, пока суммарный набег фазы сигнал не будет равен

В измерителе фазы 2 происходит сравнение фазы сигнала с выхода усилителя 10, поступающего на Bx1 измерителя фазы 2 с фазой опорных сигналов, поступающих непосредственно на Вх2 измерителя фазы 2 и через фазовращатели  ) на Bx(q+2) измерителя фазы 2.

) на Bx(q+2) измерителя фазы 2.

При этом максимальное напряжение будет на выходе того канала, фаза опорного сигнала которого совпадает с фазой гармонического сигнала на выходе усилителя 10. Отметим, что в отличие от прототипа, где сравнение можно провести только по завершении операции модульного сложения N чисел, в данном устройстве возможно обеспечить промежуточный контроль правильности вычислений, изменяя число слагаемых от 2 до N, т.е. момент прихода тактирующего сигнала на Bx(q+2) измерителя фазы 2.

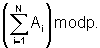

Пусть этот сигнал поступит после завершения сложения всех N операндов. Тогда на выходе измерителя фазы 2 появляется унитарный код, соответствующий номеру канала с максимальным напряжением, что соответствует коду  После преобразования этого кода в шифраторе 6 в двоичный код результат сложения N чисел по модулю р поступает на выход 7 устройства.

После преобразования этого кода в шифраторе 6 в двоичный код результат сложения N чисел по модулю р поступает на выход 7 устройства.

Пример: Пусть р=5, N=4 (A1=1, А2=4, А3=2, А4=1). На входе 131÷134 устройства поступают двоичные коды чисел  На управляющий вход 11 устройства поступает двоичный код 002. При этом обеспечивается соединение входа 131 устройства с выходом мультиплексора 12.

На управляющий вход 11 устройства поступает двоичный код 002. При этом обеспечивается соединение входа 131 устройства с выходом мультиплексора 12.

После преобразования двоичного кода числа A1=1 дешифратором 4 в унитарный код он поступает на второй вход управляемого фазовращателя 5, где коммутатором 172 подключается линия задержки 181 на время равное  После прохождения гармонического сигнала с выхода генератора 1 через коммутатор 8 (напряжение на его управляющем входе отсутствует), управляемый фазовращатель 5 и усилитель 10 фаза этого сигнала будет

После прохождения гармонического сигнала с выхода генератора 1 через коммутатор 8 (напряжение на его управляющем входе отсутствует), управляемый фазовращатель 5 и усилитель 10 фаза этого сигнала будет  Также сигнал с выхода коммутатора 8 поступает через амплитудный детектор 9 на управляющий вход коммутатора 8. Однако без использования усилителя 10 уровень сигнала недостаточен для прерывания подачи гармонического сигнала с генератора 1 на первый вход фазовращателя 5 (меньше порога срабатывания).

Также сигнал с выхода коммутатора 8 поступает через амплитудный детектор 9 на управляющий вход коммутатора 8. Однако без использования усилителя 10 уровень сигнала недостаточен для прерывания подачи гармонического сигнала с генератора 1 на первый вход фазовращателя 5 (меньше порога срабатывания).

Следовательно, сигнал с выхода усилителя 10 через амплитудный детектор 9 в виде постоянного напряжения поступает на управляющий вход коммутатора 8, отключая генератор 1 от первого входа управляемого фазовращателя 5. На адресный вход мультиплексора поступает двоичный код 012. При этом второй операнд A2=4 поступает на вход дешифратора 4 и далее в унитарном коде на второй вход управляемого фазовращателя 5, на первый вход которого поступает гармонический сигнал с фазой, соответствующей первому операнду A1=1. Следовательно, на выходе фазовращателя 5 устанавливается суммарный набег фазы, равный  а ввиду того, что гармоническая функция периодическая, то набег фазы будет равен нулю.

а ввиду того, что гармоническая функция периодическая, то набег фазы будет равен нулю.

Процесс повторяется для операндов А3=2 и А4=1 в фазовращателе 5 и после его завершения фаза на выходе усилителя 10 будет равна  Максимальное напряжение будет на выходе третьего канала измерителя фазы 2, т.е. на выходе интегратора 154. После прихода тактирующего сигнала UТС на Вх7 измерителя фазы 2 на его выходе образуется унитарный код числа 3, который преобразуется в шифраторе 6 в двоичный код и поступает на выход 7 устройства.

Максимальное напряжение будет на выходе третьего канала измерителя фазы 2, т.е. на выходе интегратора 154. После прихода тактирующего сигнала UТС на Вх7 измерителя фазы 2 на его выходе образуется унитарный код числа 3, который преобразуется в шифраторе 6 в двоичный код и поступает на выход 7 устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2263948C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2006 |

|

RU2313124C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2001 |

|

RU2192092C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД | 2001 |

|

RU2187886C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ n-РАЗРЯДНОГО ДВОИЧНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД ОСТАТКА ПО МОДУЛЮ m | 2003 |

|

RU2242085C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| Устройство сложения (вычитания) N чисел с настраиваемым модулем | 2016 |

|

RU2637988C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления. Техническим результатом является упрощение устройства. Указанный результат достигается за счет того, что устройство содержит шифратор, управляемый фазовращатель, генератор гармонического сигнала, фазовращатели на фиксированное значение фазы, измеритель фазы гармонического сигнала, мультиплексор, коммутатор, амплитудный детектор и усилитель гармонического сигнала. 3 ил.

Устройство для сложения N чисел по модулю р, содержащее дешифратор, шифратор, управляемый фазовращатель, генератор гармонического сигнала, (р-1) фазовращателей на фиксированные значения фазы и измеритель фазы гармонического сигнала, причем выход генератора гармонического сигнала соединен со вторым входом измерителя фазы гармонического сигнала, вход  которого соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное

которого соединен с выходом генератора гармонического сигнала через фазовращатель на фиксированное значение фазы, равное  , при этом (р+2)-ой вход измерителя фазы гармонического сигнала является тактовым входом устройства, выход дешифратора подключен ко второму входу управляемого фазовращателя, выход измерителя фазы гармонического сигнала соединен с входом шифратора, выход которого является выходом устройства, отличающееся тем, что в него введены мультиплексор, коммутатор, амплитудный детектор и усилитель гармонического сигнала, причем выход генератора гармонического сигнала соединен со входом коммутатора, управляющий вход которого соединен с выходом амплитудного детектора, а выход - со входом амплитудного детектора, с первым входом измерителя фазы гармонического сигнала и с первым входом управляемого фазовращателя, выход которого соединен с входом усилителя гармонического сигнала, выход усилителя гармонического сигнала соединен с первым входом измерителя фазы гармонического сигнала и с входом амплитудного детектора, управляющий вход устройства соединен с адресным входом мультиплексора, выход которого соединен со входом дешифратора, а информационные входы мультиплексора являются входами устройства.

, при этом (р+2)-ой вход измерителя фазы гармонического сигнала является тактовым входом устройства, выход дешифратора подключен ко второму входу управляемого фазовращателя, выход измерителя фазы гармонического сигнала соединен с входом шифратора, выход которого является выходом устройства, отличающееся тем, что в него введены мультиплексор, коммутатор, амплитудный детектор и усилитель гармонического сигнала, причем выход генератора гармонического сигнала соединен со входом коммутатора, управляющий вход которого соединен с выходом амплитудного детектора, а выход - со входом амплитудного детектора, с первым входом измерителя фазы гармонического сигнала и с первым входом управляемого фазовращателя, выход которого соединен с входом усилителя гармонического сигнала, выход усилителя гармонического сигнала соединен с первым входом измерителя фазы гармонического сигнала и с входом амплитудного детектора, управляющий вход устройства соединен с адресным входом мультиплексора, выход которого соединен со входом дешифратора, а информационные входы мультиплексора являются входами устройства.

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

Авторы

Даты

2006-02-20—Публикация

2004-06-28—Подача