Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления.

Известен преобразователь кода системы остаточных классов в напряжение (пат. 2290754 С1 Российская Федерация, МПК Н03М 1/66 (2006.01). заявл. 11.07.2005; опубл. 27.12.2006.), где в качестве основной функции применяется сложение целых остатков числа по модулям mi (i=1..N), содержащий информационные входы, генератор гармонического колебания, управляемые фазовращатели, фазовращатель на угол π/2, аттенюатор, балансный фазовый детектор, выход.

Недостаток - низкое быстродействие.

Известно устройство для сложения N чисел по модулю Р (пат. 2188448 С2 Российская Федерация, МПК G06F 7/72 (2006.01). заявл. 15.11.2000; опубл. 27.08.2002), содержащее информационные входы, дешифраторы, генератор гармонического сигнала, управляемые фазовращатели, фазовращатели на фиксированные значения фазы, измеритель фазы гармонического сигнала, шифратор, выход. Недостаток - низкое быстродействие.

Наиболее близким к заявляемому является изобретение (пат. 2270476 С1 Российская Федерация, МПК G06F 7/72 (2006.01). заявл. 28.06.2004; опубл. 20.02.2006.), содержащее генератор гармонического сигнала, измеритель фазы гармонического сигнала, фазовращатели на фиксированное значение фазы, дешифратор, управляемый фазовращатель, шифратор, выход устройства, коммутатор, амплитудный детектор, усилитель гармонического сигнала, управляющий вход устройства, мультиплексор, информационные входы устройства.

Недостаток - низкое быстродействие, обусловленное применением цифровых управляемых фазовращателей на основе линий задержки, коммутируемых в электрическую цепь посредством ключей.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в повышении быстродействия.

Технический результат выражается в выполнении искомой операции через сложение дискретных фаз гармоник без применения устройств, функционирующих на основе коммутации линий задержки посредством электрических ключей (управляемых фазовращателей).

Технический результат достигается тем, что в устройство для сложения k чисел по модулю m, содержащее k информационных входов устройства, измеритель фазы гармонического сигнала, введены синхронизирующий вход устройства, k-1 блоков сложения фаз, первый, второй и третий выходы устройства, при этом синхронизирующий вход устройства объединен с первым входом блоков сложения фаз, а также первым входом измерителя фазы гармонического сигнала, первый выход которого объединен с первым выходом устройства, второй выход измерителя фазы гармонического сигнала объединен с вторым выходом устройства, первый информационный вход устройства объединен с вторым входом первого блока сложения фаз, при этом i-й информационный вход устройства ( ) объединен с третьим входом (i-1)-го блока сложения фаз, выход j-го блока сложения фаз соединен с вторым входом (j+1)-го блока сложения фаз (

) объединен с третьим входом (i-1)-го блока сложения фаз, выход j-го блока сложения фаз соединен с вторым входом (j+1)-го блока сложения фаз ( ), выход (k-1)-го блока сложения фаз соединен с вторым входом измерителя фазы гармонического сигнала, а также объединен с третьим выходом устройства.

), выход (k-1)-го блока сложения фаз соединен с вторым входом измерителя фазы гармонического сигнала, а также объединен с третьим выходом устройства.

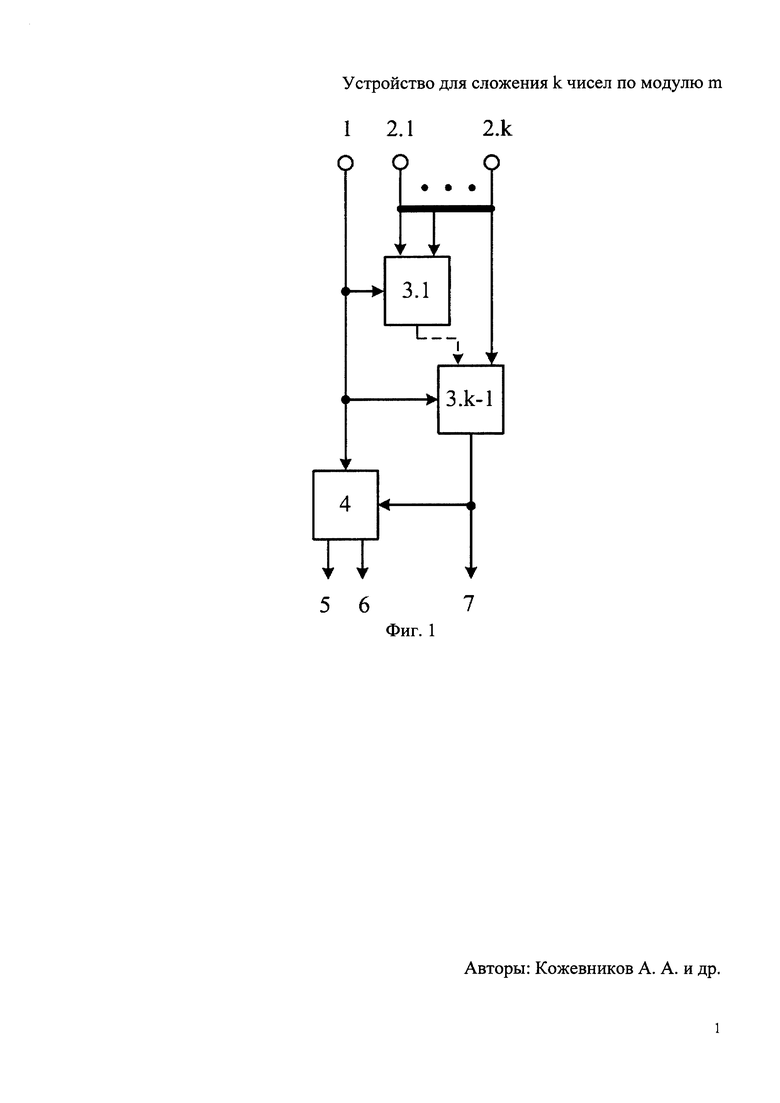

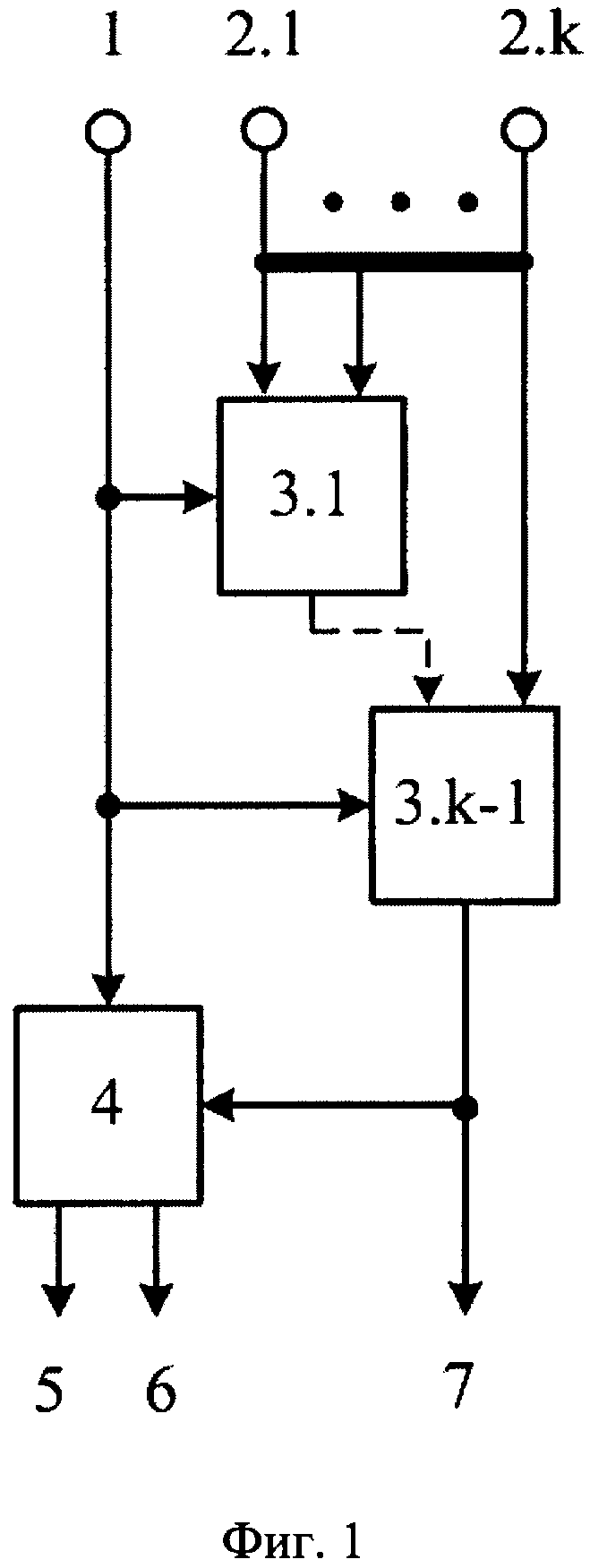

На фиг. 1 представлена структурная схема устройства для сложения k чисел по модулю m.

На фиг. 2 приведена схема блока сложения фаз.

На фиг. 3 приведена схема измерителя фазы гармонического сигнала.

Сущность изобретения заключается в осуществлении искомой операции непосредственным сложением фаз гармоник в соответствии с известными тригонометрическими выражениями, а не за счет набега фазы сигнала на некоторое дискретное значение, как в прототипе. Основной причиной, снижающей быстродействие прототипа по сравнению с реализуемым устройством, является переход от вычисления одной суммы k чисел к другой, поскольку влечет за собой процесс изменения дискретных величин фазовращения посредством перекоммутации линий задержек. Даже самые быстродействующие полупроводниковые ключи, работающие с сигналами в СВЧ-диапазоне, осуществляют данную операцию в течение единиц наносекунд (стр. 12, Щаврук Н.В. Проектирование и изготовление микроэлектромеханических переключателей на подложках GaAs для СВЧ диапазона: дис. … канд. техн. наук: 05.27.01 / Москва, 2015, 130 с.). Таким образом, применение свойств гармонических сигналов при выполнении операций над дискретно-фазированным представлением чисел без использования переключателей в реализуемом устройстве на рабочей частоте, например, 100 ГГц дает ускорение вычислений на два порядка.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1 и 3 должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Дополнительным эффектом является повышение точности вычислений за счет постоянства импеданса реализуемого устройства, в отличие от прототипа, где при переходе от вычисления одной суммы к другой производится изменение задержек сигнала. Другим положительным эффектом является расширение функциональных возможностей через выполнение на одном и том же устройстве искомой операции по любому модулю m, в отличие от прототипа, где значения задержек фазы фиксированы. Последнее обстоятельство также влечет за собой еще один положительный эффект, заключающийся в возможности одновременно суммировать остатки по разным модулям системы остаточных классов (СОК), что позволяет использовать реализуемое устройство в качестве выходного каскада в схеме вычисления позиционных характеристик модулярного числа.

Показанное на фиг. 1 устройство для сложения k чисел по модулю m содержит синхронизирующий вход устройства 1, информационные входы устройства 2.1-2.k, блоки сложения фаз 3.1-3.(k-1), измеритель фазы гармонического сигнала 4, первый 5, второй 6 и третий 7 выходы устройства.

Синхронизирующий вход устройства 1 объединен с первым входом блоков сложения фаз 3.1-3.(k-1), а также первым входом измерителя фазы гармонического сигнала 4, первый выход которого объединен с первым выходом устройства 5, при этом второй выход измерителя фазы гармонического сигнала 4 объединен с вторым выходом устройства 6, при этом информационный вход 2.1 объединен с вторым входом блока сложения фаз 3.1, при этом информационный вход 2.i объединен с третьим входом блока сложения фаз 3.(i-1)( ), при этом выход блока сложения фаз 3.j соединен с вторым входом блока сложения фаз 3.(j+1) (

), при этом выход блока сложения фаз 3.j соединен с вторым входом блока сложения фаз 3.(j+1) ( ), при этом выход блока сложения фаз 3.(k-1) соединен с вторым входом измерителя фазы гармонического сигнала 4, а также объединен с третьим выходом устройства 7.

), при этом выход блока сложения фаз 3.(k-1) соединен с вторым входом измерителя фазы гармонического сигнала 4, а также объединен с третьим выходом устройства 7.

Показанная на фиг. 2 схема блока сложения фаз содержит первый 8, второй 9 и третий 10 входы, смеситель 11, полосовой фильтр 12, смеситель 13, полосовой фильтр 14, усилитель 15 и выход 16.

Второй вход 9 объединен с первым входом смесителя 11, третий вход 10 объединен с вторым входом смесителя 11, выход которого соединен с входом полосового фильтра 12, выход которого соединен с вторым входом смесителя 13, при этом первый вход 8 объединен с первым входом смесителя 13, выход которого соединен с входом полосового фильтра 14, выход которого соединен с входом усилителя 15, выход которого объединен с выходом 16.

Показанная на фиг. 3 схема измерителя фазы гармонического сигнала содержит первый 17 и второй 18 входы, фазовращатель на фиксированное значение π/2 19, смеситель 20, смеситель 21, фильтры нижних частот 22 и 23, первый 24 и второй 25 выходы.

Первый вход 17 объединен с вторым входом смесителя 20 и входом фазовращателя на фиксированное значение π/2 19, выход которого соединен с вторым входом смесителя 21, второй вход 18 объединен с первым входом смесителя 20 и смесителя 21, выход которого соединен с фильтром нижних частот 23, выход которого объединен с вторым выходом 25, при этом выход смесителя 20 соединен с фильтром нижних частот 22, выход которого объединен с первым выходом 24.

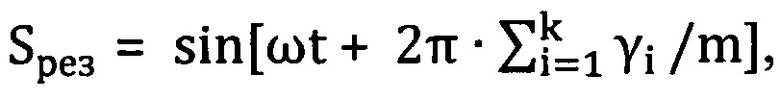

Работа устройства осуществляется следующим образом. На синхронизирующий вход 1 поступает гармонический сигнал S=sin(ωt). На информационные входы 2.1-2.k поступают дискретно-фазированные гармоники: Si=sin(ωt+2π⋅γi/m), где  a γi ∈ [0, m-1]. Здесь m - модуль системы остаточных классов (СОК). В первом блоке сложения фаз 3.1 на смесителе 11 (фиг. 2) производится перемножение сигналов:

a γi ∈ [0, m-1]. Здесь m - модуль системы остаточных классов (СОК). В первом блоке сложения фаз 3.1 на смесителе 11 (фиг. 2) производится перемножение сигналов:

S1=sin(ωt+2π⋅γ1/m) и

S2=sin(ωt+2π⋅γ2/m).

Из известного тригонометрического выражения

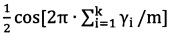

следует, что после полосовой фильтрации высокочастотной составляющей на блоке 13 формируется промежуточный результат:

Гармонический сигнал с входа 8 перемножается смесителем 13 с промежуточной гармоникой. Реализация тригонометрического выражения

после полосовой фильтрации более низкочастотной составляющей на блоке 14 и усиления в блоке 15 дает результат в виде гармоники с единичной амплитудой и фазой, смещенной относительно синхронизирующего сигнала на 2π⋅(Y1+Y2)/m:

Sвых 3.1=sin[ωt+2π⋅(γ1+γ2)/m].

В результате последовательной работы блоков сложения фаз на третьем выходе устройства 7 формируется сигнал:

который можно использовать для дальнейших операций в других модулярных дискретно-фазированных вычислительных устройствах.

Также данный сигнал поступает через второй вход 18 в измеритель фазы гармонического сигнала 4 (фиг. 3), где на смесителе 20 перемножается с синхронизирующей гармоникой S=sin(ωt), и согласно выражению (1), после фильтра нижних частот 22 на первом выходе 24 формируется уровень напряжения, пропорциональный  , который поступает на первый выход устройства 5. Параллельно в измерителе 4 происходит увеличение фазы синхронизирующего сигнала на фиксированное значение π/2 на блоке 19 (S=cos(ωt)) с дальнейшим перемножением в смесителе 21 с результирующей гармоникой Speз. При этом, согласно выражению (2), после фильтрации нижних частот 23 на втором выходе 25 формируется уровень напряжения, пропорциональный

, который поступает на первый выход устройства 5. Параллельно в измерителе 4 происходит увеличение фазы синхронизирующего сигнала на фиксированное значение π/2 на блоке 19 (S=cos(ωt)) с дальнейшим перемножением в смесителе 21 с результирующей гармоникой Speз. При этом, согласно выражению (2), после фильтрации нижних частот 23 на втором выходе 25 формируется уровень напряжения, пропорциональный  , который поступает на второй выход устройства 6. Аналоговые значения на первом 5 и втором 6 выходах устройства могут быть использованы, например, для получения в дальнейшем цифрового эквивалента модулярного числа или других применений.

, который поступает на второй выход устройства 6. Аналоговые значения на первом 5 и втором 6 выходах устройства могут быть использованы, например, для получения в дальнейшем цифрового эквивалента модулярного числа или других применений.

Пример

Произведем сложение трех чисел (k=3) по модулю m=5. Устройство для сложения (фиг. 1) будет содержать, соответственно, три информационных входа 2.1-2.3 и два блока сложения фаз 3.1-3.2. Пусть складываемые числа, например, равны А1=12, А2=33 и А3=21, целые остатки которых по модулю пять, соответственно, есть: γ1=2, γ2=3 и γ3=1. На синхронизирующий вход 1 поступает гармонический сигнал S=cos(ωt). На информационные входы 2.1-2.3 поступают дискретно-фазированные гармоники:

S1=sin(ωt+2π⋅2/5),

S2=sin(ωt+2π⋅3/5],

S3=sin(ωt+2π⋅1/5).

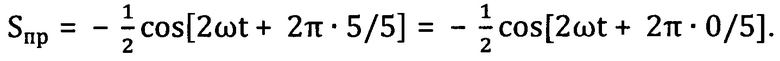

В первом блоке сложения фаз 3.1 на смесителе 11 (фиг. 2) производится перемножение сигналов S1 и S2. Из выражения (1) следует, что после полосовой фильтрации высокочастотной составляющей на блоке 12 формируется промежуточная гармоника:

Гармонический сигнал с входа 8 перемножается смесителем 13 с промежуточной гармоникой. Реализация выражения (2) после полосовой фильтрации более низкочастотной составляющей на блоке 14 и усиления в блоке 15 дает результат в виде гармоники с единичной амплитудой и фазой, смещенной относительно синхронизирующего сигнала на 2π⋅0/5:

Sвых 3.1=sin[ωt+2π⋅0/5].

В результате аналогичной операции на блоке 3.2 на третьем выходе устройства 7 формируется сигнал:

Speз=sin[ωt+2π⋅1/5],

который можно использовать для дальнейших операций в других модулярных дискретно-фазированных вычислительных устройствах.

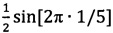

Также данный сигнал поступает через второй вход 18 в измеритель фазы гармонического сигнала 4 (фиг. 3), где на смесителе 20 перемножается с синхронизирующей гармоникой S=sin(ωt), и согласно выражению (1), после фильтра нижних частот 22 на первом выходе 24 формируется уровень напряжения, пропорциональный  , который поступает на первый выход устройства 5. Параллельно в измерителе 4 происходит увеличение фазы синхронизирующего сигнала на фиксированное значение π/2 на блоке 19 (S=cos(ωt)) с дальнейшим перемножением в смесителе 21 с результирующей гармоникой Speз. При этом согласно выражению (2) после фильтрации нижних частот 23 на втором выходе 25 формируется уровень напряжения пропорциональный

, который поступает на первый выход устройства 5. Параллельно в измерителе 4 происходит увеличение фазы синхронизирующего сигнала на фиксированное значение π/2 на блоке 19 (S=cos(ωt)) с дальнейшим перемножением в смесителе 21 с результирующей гармоникой Speз. При этом согласно выражению (2) после фильтрации нижних частот 23 на втором выходе 25 формируется уровень напряжения пропорциональный  , который поступает на второй выход устройства 6. Аналоговые значения на первом 5 и втором 6 выходах устройства могут быть использованы, например, для получения в дальнейшем цифрового эквивалента посредством аналого-цифрового преобразования и вычисления результирующего остатка по модулю. В данном случае (исходя из Speз) γрез=1. Проверим полученный результат. А1+А2+А3=12+33+21=66, что по модулю 5 дает целый остаток, равный 1.

, который поступает на второй выход устройства 6. Аналоговые значения на первом 5 и втором 6 выходах устройства могут быть использованы, например, для получения в дальнейшем цифрового эквивалента посредством аналого-цифрового преобразования и вычисления результирующего остатка по модулю. В данном случае (исходя из Speз) γрез=1. Проверим полученный результат. А1+А2+А3=12+33+21=66, что по модулю 5 дает целый остаток, равный 1.

Полученное устройство отражает принципы построения арифметических устройств на основе системы остаточных классов, работающих с дискретно-фазированной формой представления чисел. С точки зрения практического применения устройство реализует возможность построения аналоговых вычислителей СВЧ-диапазона, превосходящих по быстродействию современный уровень ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| ФАЗИРОВАННЫЙ КЛЮЧ ПО МОДУЛЮ m | 2017 |

|

RU2659866C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2020 |

|

RU2744337C1 |

| ЦИФРОВОЙ ФИЛЬТР В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2291557C1 |

| ЦИФРОВОЙ ФИЛЬТР В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2287893C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПО МОДУЛЮ m | 2020 |

|

RU2747568C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления. Техническим результатом является повышение быстродействия устройства за счет осуществления сложения дискретных фаз гармоник. Устройство содержит k информационных входов устройства, измеритель фазы гармонического сигнала, синхронизирующий вход устройства, k-1 блоков сложения фаз, три выхода устройства. 3 ил.

Устройство для сложения k чисел по модулю m, содержащее k информационных входов устройства, измеритель фазы гармонического сигнала, отличающееся тем, что введены синхронизирующий вход устройства, k-1 блоков сложения фаз, первый, второй и третий выходы устройства, при этом синхронизирующий вход устройства объединен с первым входом блоков сложения фаз, а также первым входом измерителя фазы гармонического сигнала, первый выход которого объединен с первым выходом устройства, второй выход измерителя фазы гармонического сигнала объединен с вторым выходом устройства, первый информационный вход устройства объединен с вторым входом первого блока сложения фаз, при этом i-й информационный вход устройства  объединен с третьим входом (i-1)-го блока сложения фаз, выход j-го блока сложения фаз соединен с вторым входом (j+1)-го блока сложения фаз

объединен с третьим входом (i-1)-го блока сложения фаз, выход j-го блока сложения фаз соединен с вторым входом (j+1)-го блока сложения фаз  , выход (k-1)-го блока сложения фаз соединен с вторым входом измерителя фазы гармонического сигнала, а также объединен с третьим выходом устройства.

, выход (k-1)-го блока сложения фаз соединен с вторым входом измерителя фазы гармонического сигнала, а также объединен с третьим выходом устройства.

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2270476C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 4598266 A, 01.07.1986. | |||

Авторы

Даты

2018-05-07—Публикация

2017-05-24—Подача