Область техники, к которой относится изобретение

Настоящее изобретение относится, в основном, к передаче данных по коммуникационной шине. Более конкретно, настоящее изобретение относится к механизму отслеживания фазы строба во время смены ведущего устройства на коммуникационной шине.

Предпосылки создания изобретения

Мультипроцессорная система повышает производительность системы, так как многочисленные процессоры работают параллельно. Типичная мультипроцессорная система имеет ряд процессоров, подключенных к коммуникационной шине. Хотя каждый процессор может использовать шину только в конкретный момент времени, были разработаны протоколы шины для оптимизации использования шины.

В такой мультипроцессорной системе одна часть коммуникационной шины, шина данных, является одним из наиболее важных ресурсов, так как весь обмен информацией происходит по этой шине. Поэтому важно, чтобы шина данных использовалась эффективно. В мультипроцессорной системе данные передаются от процессора на процессор в соответствии с заранее определенной диаграммой тактирования. Тактовые импульсы системной шины типично тактируют передачу данных с отправляющего процессора и на принимающий процессор. Следовательно, передача данных с одного процессора на другой процессор занимает один полный тактовый цикл тактовых импульсов системной шины. Данные могут передаваться синхронным с источником образом, чтобы повысить скорость передачи данных. При синхронной с источником передаче передача данных типично тактируется двумя дифференциальными строб-сигналами, которые сдвинуты по фазе, так что активные фронты, которые обеспечиваются обоими стробами, соответствуют тактовым импульсам быстрой передачи, период которых обычно короче периода тактовых импульсов системной шины. Эти стробы используются принимающим процессором для фиксации данных.

Дифференциальные строб-сигналы означают, что используются оба строб-сигнала как с активным низким уровнем, так и с активным высоким уровнем. Это вводит сложность для шины с активным низким уровнем, требуя, чтобы один из стробов предустанавливался и постустанавливался со значения установившегося состояния, равного логической 1, и в это значение. Кроме того, предустановка и постустановка стробов должны учитываться на принимающих процессорах, чтобы обеспечить надлежащее выделение данных и принять решение, какого строба необходимо выполнить предустановку во время следующей передачи данных. Основной проблемой, связанной с этим дифференциальным мультипроцессорным методом, являются непрерывные передачи данных с изменениями принадлежности шины, т.е. когда другой процессор становится отправляющим процессором или “ведущим устройством” и принимает на себя управление шиной данных.

Следовательно, существует потребность в механизме отслеживания фазы строба, чтобы обеспечивать надлежащие предустановку и постустановку строба, а также безошибочное выделение данных.

Краткое изложение сущности изобретения

Варианты выполнения настоящего изобретения направлены на способ и устройство для обеспечения надлежащих предустановки и постустановки строба между первой передачей данных и второй передачей данных в вычислительной системе. Способ включает в себя генерирование первого строб-сигнала и второго строб-сигнала, предустановку одного из упомянутых первого и второго строб-сигналов перед первой передачей данных, определение, какой из упомянутых первого и второго строб-сигналов будет по-стустановлен, и предустановку одного из упомянутых первого и второго строб-сигналов перед второй передачей данных.

Краткое описание чертежей

Преимущества настоящего изобретения станут более очевидны для специалиста в этой области техники после рассмотрения нижеследующего подробного описания и прилагаемых чертежей, в которых:

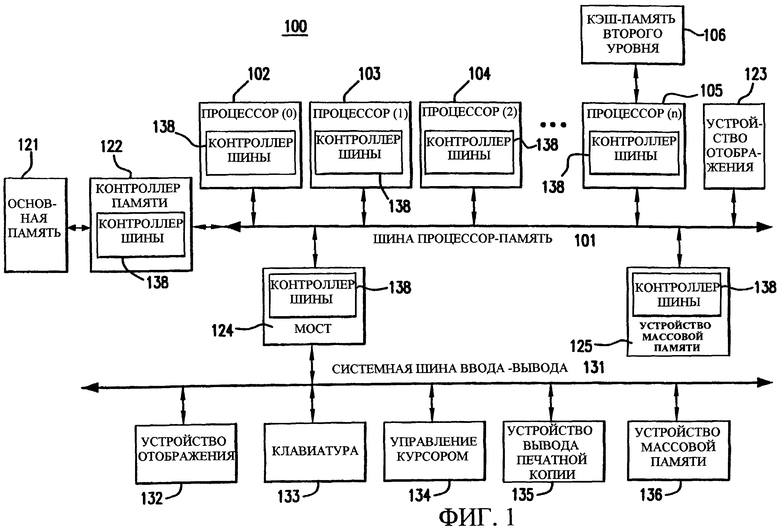

на фиг.1 представлена типичная блок-схема вычислительной системы;

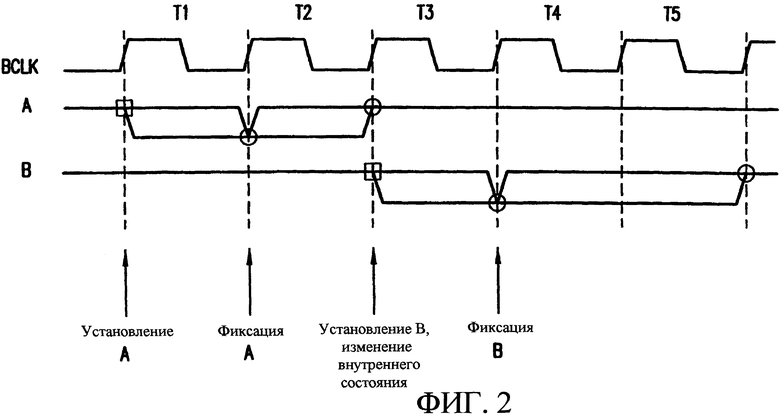

на фиг.2 представлена типичная диаграмма синхронизации для вычислительной системы по фиг.1;

на фиг.3 представлена диаграмма синхронизации, изображающая синхронизацию в соответствии с вариантом выполнения настоящего изобретения;

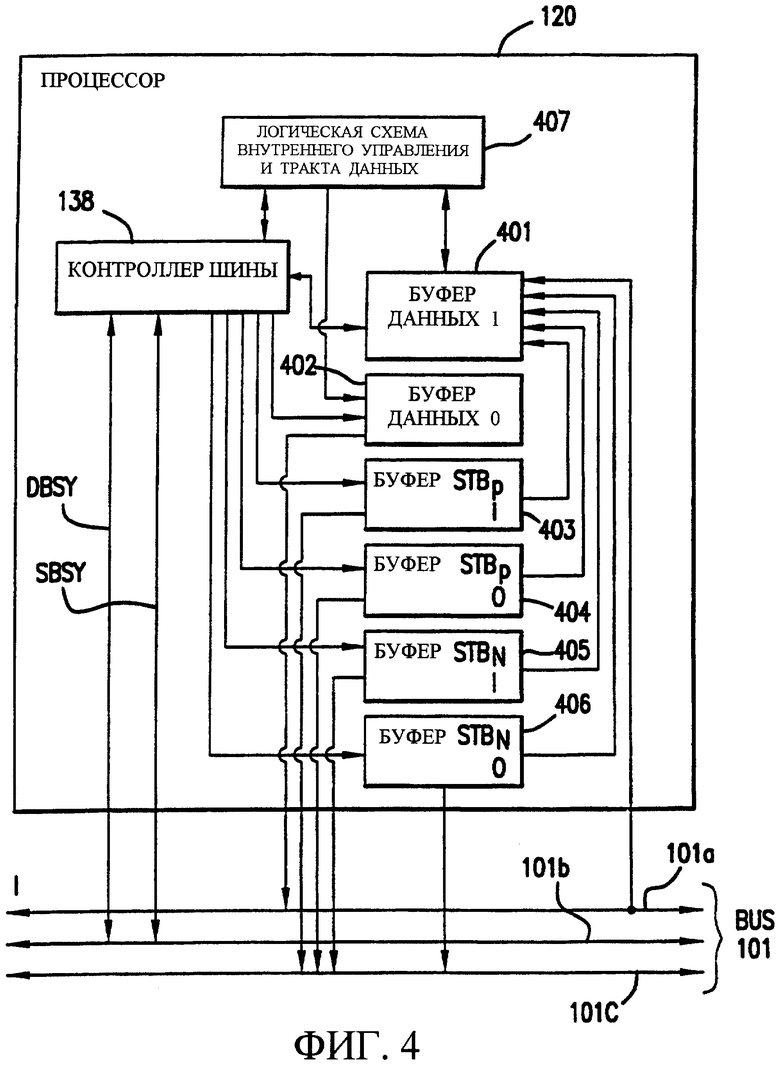

на фиг.4 представлена блок-схема процессора в соответствии с вариантом выполнения настоящего изобретения;

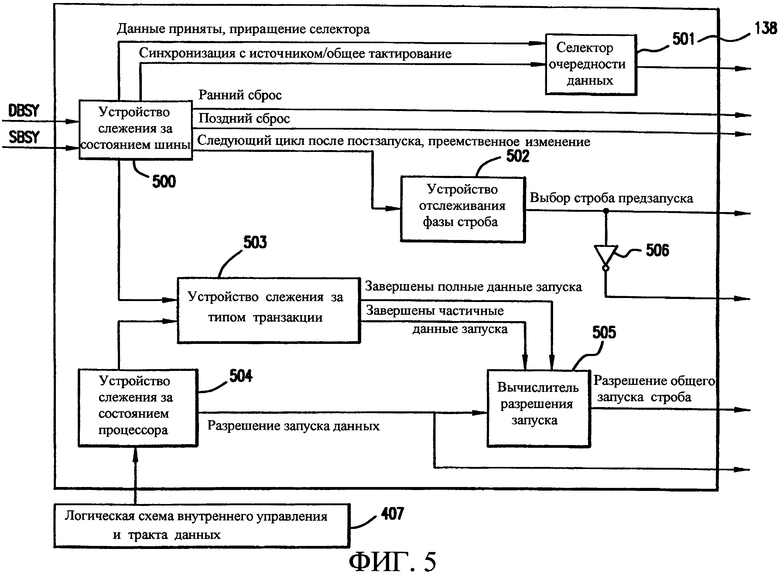

на фиг.5 представлена блок-схема контроллера шины в соответствии с вариантом выполнения настоящего изобретения.

Подробное описание изобретения

Ниже описываются варианты выполнения механизма отслеживания фазы строба для определения, предустановку и постустановку какого строба необходимо выполнить во время смены ведущего устройства на коммуникационной шине. Механизм отслеживания фазы строба позволяет установить надлежащий строб, который обеспечивает эффективную передачу данных по коммуникационной шине.

В нижеследующем описании с целью объяснения изложены многочисленные подробности, чтобы обеспечить полное понимание настоящего изобретения. Однако специалисту в этой области техники очевидно, что эти конкретные подробности не требуются для практического использования настоящего изобретения. В других случаях общеизвестные электрические схемы и решения показаны в виде блок-схем, чтобы излишне не затруднять понимание предмета изобретения.

На фиг.1 представлена блок-схема мультипроцессорной компьютерной системы, которая может быть использована с вариантами выполнения настоящего изобретения. Компьютерная система 100 содержит шину 101 процессор-память для обмена между различными процессорами, подключенными к шине 101. К шине 101 процессор-память также подключены исполнительные устройства, такие как мосты между шинами, запоминающие устройства, периферийные устройства и т. д. Шина 101 процессор-память включает шину арбитража, адресную шину, шину данных и шину управления (не показаны). В одном варианте выполнения каждый из процессоров 102, 103, 104 и 105 содержит небольшую внутреннюю кэш-память с очень высоким быстродействием (не показана), обычно упоминаемую как кэш-память первого уровня (L1), для временного хранения данных и команд, размещенную на той же интегральной схеме, что и связанный с ней процессор. Кроме того, кэш-память 106 второго уровня (L2) большей емкости подключена к процессору 105 для временного хранения данных и команд для использования процессором 105. В других вариантах выполнения кэш-память L2, такая как память 106, может быть подсоединена к любому из процессоров 102-105.

Шина 101 процессор-память обеспечивает доступ к памяти и подсистемам ввода-вывода. Контроллер 122 памяти подсоединен к шине 101 процессор-память для управления доступом к запоминающему устройству с произвольной выборкой (ЗУПВ) или другому динамическому запоминающему устройству 121 (обычно упоминаемому как основная память) для хранения информации и команд для процессоров 102-105. Устройство 132 отображения, клавиатурное устройство 133, устройство 134 управления курсором, устройство 135 вывода печатной копии и устройство 136 массовой памяти подсоединены к системной шине 131 ввода-вывода и к шине 101 процессор-память через мост 124 между шинами. Мост 124 подсоединен к шине 101 процессор-память и системной шине 131 ввода-вывода для создания канала связи или шлюза для устройств либо на шине 101 процессор-память, либо на шине 131 ввода-вывода для доступа или передачи данных между устройствами на другой шине. Мост 124 является интерфейсом между системной шиной 131 ввода-вывода и шиной 101 процессор-память. Шина 131 ввода-вывода передает информацию между периферийными устройствами 132-136.

Процессоры 102-105, мост 124 между шинами, устройство 125 массовой памяти и контроллер 122 памяти каждый содержит контроллер 138 шины. Контроллер 138 шины управляет обменом по шине 101 процессор-память, когда процессор или исполнительное устройство, содержащие его, управляет шиной 101 процессор-память.

На фиг.2 представлена временная диаграмма, изображающая то, что происходит на шине во время обычной транзакции тактирования. На этих временных диаграммах квадратный символ обозначает, что сигнал устанавливается, круглый символ обозначает, что производится выборка сигнала (фиксируется или выделяется), и треугольный символ обозначает, что сигнал принимается или наблюдается. Используемый термин “установленный” означает, что сигнал устанавливается в его активный уровень, и термин “неустановленный” означает, что сигнал устанавливается в его неактивный логический уровень.

Тактовый сигнал BCLK шины активен на его переднем фронте. В начале тактового цикла Т1 сигнал А устанавливается на шине. В начале Т2 BCLK фиксирует сигнал А. В начале Т3 устанавливается сигнал В под действием фиксации сигнала А. Сигнал А меняет состояние до его первоначального неактивного состояния в Т2. Из фиг.2 видно, что сигнал В устанавливается в ответ на сигнал А через два цикла BCLK после установления сигнала А.

На фиг.3 представлена временная диаграмма, изображающая синхронную с источником передачу данных в соответствии с одним вариантом выполнения настоящего изобретения. Сигнал INTCLK представляет тактовые импульсы, внутренние для процессора, который используется для синхронизации других сигналов и тактирования данных на шине данных. INTCLK приведен для иллюстрации зависимости между различными сигналами. Сигнал BCLK представляет собой тактовые импульсы, наблюдаемые на шине и обычно некоторым образом синхронизированные с сигналом INTCLK. В этом варианте выполнения частота сигнала INTCLK в два раза выше частоты сигнала BCLK. Сигнал ДАННЫЕ представляет собой данные на шине. В варианте выполнения, изображенном на фиг.3, сигнал ДАННЫЕ передается с частотой, которая в два раза выше обычной частоты передачи. Когда данные не установлены никаким из исполнительных устройств шины, она принимает высокий импеданс и остается со значением логической 1, как показано INTCLK 1A, 3В, 4А, 7В, 8А и 8В на фиг.3.

STBp и STBn представляют собой два строб-сигнала, которые используются для установления данных на шине. Сигналы STBp и STBn используются для синхронизации передачи данных. Любое принимающее исполнительное устройство шины или процессор могут использовать сигнал STBp и STBn для фиксации данных. Использование двух строб-сигналов (вместо одного) для стробирования данных устраняет проблему неустойчивой синхронизации, связанную с подходом, использующим один строб. Другим преимуществом использования двух строб-сигналов является уменьшение проблемы синфазного шума. Кроме того, трудно выполнить тактирование данных только с одним стробом на шине с частотой, которая в два раза выше частоты тактовых импульсов шины.

Сигналы STBp и STBn сдвинуты по фазе друг относительно друга, хотя сдвиг фазы не имеет места для всех тактовых импульсов. Посредством сдвига фазы, т.е. сдвига фронта одного сигнала на величину, равную половине периода сигнала BCLK, приемник может проверять оба сигнала STBp и STBn с целью получения данных. Следствием сдвига фазы является то, что сигнал ДАННЫЕ действителен тогда, когда происходят переходы в обоих сигналах STBp и STBn. Не имеет значения, у какого из сигналов STBp и STBn переход происходит на нарастающем фронте или на спадающем фронте импульса.

Чтобы осуществить эту особенность комплементарных фронтов, один из строб-сигналов данных устанавливается до фактического стробирования данных. Это установление обычно происходит за полпериода тактовых импульсов шины до первого пересечения стробов, которое происходит в центре окна проверки достоверности данных, как показано на фиг.3. Это раннее установление названо “предустановка”, как показано сигналом INTCLK 1A на сигнале STBp и сигналом INTCLK 4A на сигнале STBn. После этого в следующем тактовом импульсе устанавливается другой строб данных в момент, когда переключается строб данных предустановки. Обладая этой особенностью предустановки, два строба данных образуют пару комплементарных фронтов в тот момент, когда сами данные доступны. С этого момента два строба данных переключаются в соответствии с обычным процессом, соответствующим данным.

Таким образом, посредством создания строба данных с комплементарными фронтами и предустановкой достигается более высокая скорость передачи. На фиг.3 частота внутренних тактовых импульсов в два раза выше частоты тактовых импульсов шины. При двойном стробе данных с предустановкой данные могут передаваться с двойной скоростью по сравнению с обычной скоростью передачи: два элемента данных доступны за один тактовый импульс шины. В соответствии с вариантом выполнения настоящего изобретения также должна быть выполнена постустановка одного из строб-сигналов всякий раз, когда заканчивается передача данных (т.е. предустановка, передача, постустановка). Смена определяется как переход управления шиной к другому процессору или исполнительному устройству. Смена также дополнительно определяется как выделенный интервал времени, когда постустановка одного процессора находится в том же тактовом импульсе шины, что и предустановка в другом процессоре.

Как показано на фиг.3, внутренние сигналы, разрешение строба А1 и разрешение строба А2, обозначают внутреннее состояние передающего процессора и как он воздействует на внешние сигналы. В соответствии с настоящим изобретением эти сигналы сообщают буферам вывода строба передающего процессора или исполнительного устройства о выводе стробов из буфера. Сигнал DBSY представляет собой сигнал занятости шины данных. Этот сигнал устанавливается передающим процессором или исполнительным устройством для указания на то, что он использует или собирается использовать, или использовал шину данных. Сигнал SBSY представляет собой сигнал занятости строба. Этот сигнал устанавливается передающим процессором или исполнительным устройством для указания на то, что он использует или собирается использовать линии стробирования шины.

На фиг.3 два строб-сигнала SТВр и STBn тактируют данные с частотой, которая в два раза выше частоты тактовых импульсов BCLK. ДАННЫЕ доступны в течение второй половины BCLK 1 или в течение INTCLK 1B. STBp предустанавливается в BCLK 1. Во время BCLK 1 STBp имеет высокий уровень, тогда как STBn - низкий. Каждый из STBp и STBn продолжает переключаться с частотой тактовых импульсов шины.

Во время BCLK 3 заканчивается передача данных блока, инициированная STBp. Следующая передача данных происходит после одного пассивного тактового импульса (после передачи данных), “пересекающего” BCLK 3 и BCLK 4. В соответствии с настоящим изобретением имеет место последовательность событий, которая приводит к предустановке корректного строба и игнорированию некорректно зафиксированных данных ввода. В конце транзакции передающего процессора передающие процессоры конкурируют за проведение транзакции и постустанавливают корректный строб. Как показано на фиг.3, STBn теперь предустанавливает данные во время BCLK 4. Затем, STBn переключается во время BCLK 4 в тот самый момент, когда STBp переключается во время тактового импульса 4, начиная тактирование данных при следующей передаче данных.

На фиг.4 представлена блок-схема, изображающая более подробно процессор или исполнительное устройство в соответствии с одним вариантом выполнения настоящего изобретения. Исполнительное устройство 102 состоит из логической схемы 407 внутреннего управления и тракта данных, контроллера 138 шины, буферов 401 и 402 данных и буферов 403-406 стробов.

Как описано ниже, контроллер 138 шины управляет передачей по шине 101, когда процессор или исполнительное устройство, содержащее его, управляет шиной. Логическая схема 407 внутреннего управления и тракта данных работает как ядро процессора. Исполнительное устройство 102 также может включать в себя группу буферов 401 и 402 данных. Буфером 401 данных может быть буфер ввода, а буфером 402 данных может быть буфер вывода. Однако альтернативные варианты выполнения могут включать больше или меньше буферов данных или буферов данных, которые могут быть использованы как для ввода, так и для вывода, а не иметь две различные группы буферов.

Буфер 402 данных временно хранит данные, которые передаются от процессора 120 на другой процессор по линии (101а) данных шины 101. Буфер 401 данных временно хранит данные, которые передаются от другого процессора на процессор 120 по шине 101.

Буферы 403-406 стробов включают в себя буферы 403 и 404 ввода и вывода STBp соответственно и буферы 405 и 406 ввода и вывода STBn соответственно. Буферы стробов принимают сигналы от контроллера 138 для вывода корректного строба. Кроме того, буферы стробов вводят и принимают строб-сигналы с линии (101с) стробирования шины 101. Контроллер 138 также принимает и посылает сигналы DBSY и SBSY с линии (101b) управления шины 101 для указания на то, что процессор собирается использовать шину данных и линии стробирования шины.

На фиг.5 представлена блок-схема составных частей контроллера 138 шины. Контроллер 138 шины включает в себя устройство 500 отслеживания состояния шины, селектор 501 очередности данных, устройство 502 отслеживания фазы строба, устройство 503 слежения за типом транзакции, устройство 504 слежения за состоянием процессора и вычислитель 505 разрешения установки. Как показано на фиг.5, устройство 500 отслеживания состояния шины, селектор 501 очередности данных и устройство 502 отслеживания фазы строба работают тогда, когда процессор 102 принимает информацию, и устройство 500 слежения за шиной, устройство 503 слежения за типом транзакции, устройство 504 слежения за состоянием процессора и вычислитель 504 разрешения установки работают тогда, когда процессор 102 передает информацию.

При работе в режиме передачи процессор 102 устанавливает сигналы DBSY и SBSY. Устройство 500 отслеживания состояния шины контролирует шину и определяет, что эти сигналы были установлены. Как показано на фиг.3, эти сигналы обычно устанавливаются за один тактовый импульс шины до установки данных и обычно заканчиваются за тактовый импульс шины до окончания состояния установки данных. Хотя сигналы DBSY и SBSY представлены так, как показано на фиг.3, эти сигналы могут принимать различную форму в пределах сущности и объема настоящего изобретения. Какую бы форму не принимали эти сигналы, эти формы сигналов известны каждому процессору и исполнительному устройству системы. В соответствии с другим вариантом выполнения настоящего изобретения более или менее тех двух сигналов может быть использовано в пределах сущности и объема настоящего изобретения.

Выходные сигналы устройства слежения за состоянием шины включают в себя выходные сигналы на селектор 501 очередности данных, выходной сигнал на устройство 502 отслеживания фазы строба, выходной сигнал на устройство 503 слежения за типом транзакции и выходной сигнал на буферы данных и стробов. Что касается селектора 501 очередности данных, то одним входом от устройства слежения за состоянием шины является сигнал “данные приняты, приращение селектора”. Этот сигнал обеспечивает указание фиксаторам буфера ввода данных для посылки данных на ядро принимающего процессора. К тому времени, когда сигналы установлены, гарантируется, что данные находятся у принимающего исполнительного устройства.

Другим входным сигналом на селектор 501 очередности данных является сигнал “выбор синхронизация с источником/общее тактирование”. Этот сигнал указывает частоту, на которой происходит тактирование. Например, тактовые импульсы шины могут работать в режиме синхронизации с источником или в режиме общего тактирования.

Устройство слежения за состоянием шины также посылает сигнал на устройство 502 отслеживания фазы строба. Этот сигнал обеспечивает сигнал следующего цикла после постустановки для “преемственного” изменения отслеживаемой фазы строба. В соответствии с вариантом выполнения настоящего изобретения устройство отслеживания фазы строба преемственно (с вытеснением) принимает или предполагает, что произошла смена ведущего устройства в конце каждой следующей транзакции записи. Это определяется на основе состояния шины. Затем, если не произошла смена ведущего устройства, фаза устанавливается повторно (сбрасывается). Это возможно, так как, если нет смены, то шина свободна, предоставляя время для выполнения повторной установки (сброса). Выходной сигнал устройства отслеживания фазы строба посылается на буферы вывода строба, причем один является сигналом, инвертированным по отношению к другому, через инвертор 506. Это позволяет выполнить идентичными буферы вывода STBp и STBn.

Устройство 500 слежения за состоянием шины также выводит сигнал позднего сброса и сигнал раннего сброса. Сигнал позднего сброса сбрасывает буферы ввода данных и буферы ввода и вывода STBp и STBn. Кроме того, поздний сброс обеспечивает то, что сброс происходит после того, как будет принят фронт постустановки строба на втором тактовом импульсе ожидания шины, как показано на фиг.3. Сигнал раннего сброса сбрасывает любые другие компоненты в процессоре 102. Ранний сброс используется для инициализации буферов вывода в том случае, если процессор должен выполнить предустановку на втором цикле ожидания шины. Сигналы как раннего, так и позднего сброса устанавливаются тогда, когда процессор определяет, что будет два последовательных цикла шины.

Что касается процессора 102, функционирующего в качестве передающего процессора, то устройство 503 слежения за типом транзакции принимает входные сигналы от устройства слежения за состоянием шины и устройства 504 слежения за состоянием процессора, которое контролирует состояние процессора. Выходной сигнал от устройства слежения за типом транзакции (которое определяет, передаются частичные или полные данные) посылается на вычислитель 505 разрешения установки, который прекращает установку строба, устанавливаемого устройством слежения за состоянием процессора. Выходной сигнал от вычислителя 505 разрешения установки посылается на буферы вывода строба, и выходной сигнал от устройства слежения за состоянием процессора посылается на буфер вывода данных.

Хотя на прилагаемых чертежах были описаны и изображены некоторые примерные варианты выполнения, понятно, что такие варианты выполнения являются только иллюстративными, а не ограничительными для объема изобретения, и что настоящее изобретение не должно быть ограничено изображенными и описанными конкретными конструкциями и устройствами, так как специалист в этой области техники может придумать различные другие модификации.

Изобретение относится к передаче данных по коммуникационной шине, в частности к механизму отслеживания фазы строба во время смены ведущего устройства на коммуникационной шине. Технический результат - повышение скорости передачи данных. Способ включает в себя генерирование первого строб-сигнала и второго строб-сигнала, предустановку одного из упомянутых первого и второго строб-сигналов перед первой передачей данных, постустановку упомянутого предустановленного сигнала, определение, какой из упомянутых первого и второго строб-сигналов будет постустанавливаться, и предустановку одного из упомянутых первого и второго строб-сигналов перед второй передачей данных. 3 н. и 20 з.п. ф-лы, 5 ил.

| КАТОД ДЛЯ ЭЛЕКТРОННЫХ ПРИБОРОВ | 0 |

|

SU392565A1 |

| RU 97112199 А, 20.06.1999 | |||

| КАРДАННЫЙ ШАРНИР | 0 |

|

SU394599A1 |

| Способ осветления напитков | 1977 |

|

SU610862A1 |

| US 4463440 А, 31.07.1984 | |||

| Дифференциальный датчик давления | 1976 |

|

SU567104A1 |

| US 4672583 А, 09.06.1987 | |||

| US 4933908 А, 12.06.1990 | |||

| US 5303362 А, 12.04.1994. | |||

Авторы

Даты

2005-07-20—Публикация

2000-11-16—Подача