второго элементов И блока управления с установочным входом блока управления, управляющими входами двунаправленного и однонаправленного коммутаторов, причем в блоке управления выход первого элемента И соединен с синхровходом триггера, выход которого соединен с первым входом третьего элемента И и через элемент задержки - с его вторым входом, выход третьего элемента И соединен с первыми стробирующими входами источников информации периферийных блоков группы, выход первого элемента И соединен с вторыми стробирующими входами источников и стробирующими- входами приемников информации периферийных блоков группы, выход счетчика триггера блока управления соединен с первыми входами элементов И периферийных блоков группы, вторые и третьи

входы которых соединены соответственно с выходами готовности источников и приёмников информации, сбросовые входы источников и приемников информации соединены с входом общего сброса устройства, информационные выходы источников и информационные входы приемников информации через .двунаправленную информационную шину соединены с вторым информационным входом - выходом двунаправленного коммутатора, выход элемента И каждого периферийного блока соединен с .управляющими входами источника и приемника информации, группа выходов однонаправленного коммутатора и выходы элементов И периферийных блоков группы через адресную шину устройства соединены с группой входов элемента И каяздого периферийного блока группы, кроме первого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессора с М периферийными блоками | 1987 |

|

SU1434442A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ С МИКРОПРОЦЕССОРОМ, содержащее однонаправленный коммутатор, двунаправленный коммутатор, регистр срстояний и группу периферийных блоков, каждый из которых содерж1-1т источники и приемники информации, причем информационный вход однонаправленного коммутатора является адресным входом устройства, первый информационный вход - выход двунаправленного коммутатора соединен с информационным входом регистра состояния и является информационным входом - выходом устройства, тактовый и синхровход регистра состояний являются первым тактовым и синхронизируюо(им входами устройства, отличаю щ а е с я тем, что, с целью повышения производительности, в него введены блок управления, содержащий три элемента И, триггер, элемент задержки, дешифраторы состояния, два триггера, элемент ИЛИ, три элемента И, три счетчика, два формирователя импульсов, а в каждый периферийный блок группы - элемент И, причем входы дешифратора состояния соединены с выходами регистра состояний, выход деш1« ратора состояния соединен с первым установочным входом первого триггера, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых объединены и являются входом готовности устройства, третьи входы второго и третьего элементов И объединены с первым входом первого элемента И блока управления и являются вторым тактовым входом устройства, третий вход первого элемента И соединен с первым инверсным входом второго элемента И блока управления и с первым тактовым входом устройства, выходы первого, второго и третьего элементов И соединены соответственно со счетными входами первого, второго и третьего счетчиков, -установочные входы которых объединены с установочным входом первого триггера и соединены с выходом элемента ИЛИ, выход первого счетчика соединен с первыми входами ;о первого и второго формирователей sl импульсов, выход второго счетчика :о соединен с вторьм входом первого формирователя импульсов, выход третьего счетчика соединен с вторым входом второго формирователя импульсов, выход которого соединен с первым устаiHOBCMHiiM входом второго триггера и с первым входом элемента ИЛИ, второй вход которого является входом общего сброса устройства, выхрд первого формирователя импульсов соединен с вторым установочным входом торого триггера, выход которого соединен с вторьми входами первого и

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи между периферийными устройствами в микропроцессорной системе. Известны разнообразные устройства микропроцессорной связи, в которых применены общие магистральные шины для связи между микропроцессором (МП), памятью и периферийными устройствами (ПУ). Передача информа ции между ПУ 9 таких устройствах возможна в одном из двух рехсимов: с участием МП и без него Cl 3. В первом случае информация от ис точника информации передается вначале в МП, а затем из него в приемник информации. Однако такая процедура передачи приема информации между ПУ является мед/генной. Во втором случае процессор исклю чается из процедуры обмена информацией как промежуточное звено. Такой режим носит название прямой передач данных (ПГЩ). При этом устанавливается прямая связь между ПУ с целью передачи информации между ними, а разрешение на обмен в таком режиме дает МП, но затем он отключается от системных шин адреса и данных и не участвует в процедуре обмена информацией. Таким образом, МП простаивает в течение всего цикла ППД. Если цифровая информация, которой обмениваются ПУ, не подлежит дополнительной обработке в МП, а только передается из одного периферийного устройства в другое, то и в первом и во втором случае имеет место общий недостаток - снижение производительности микропроцессорной системы при передаче информации между ПУ, В первом случае из-за того, что для такой передачи привлекается МП и тем самым он непроизводительно тра1тит свой ресурс времени. Во втором случае из-за того, что МП простаивает во время передачи информации между ПУ в цикле ППД. Наиболее близким по технической сущности к изобретению является устройство микропроцессорной связи, содержащее регистр состояний, три однонаправленных кс ммутатора, один двунаправленный коммутатор, счетчик, три триггера, пять элементов ИЛИ, десять элементов И, элемент задержки, три формирователя гмпульсов и внешнее устройство (функционально эквивалентное периферийному устройству)23Недостатком известного устройства является ниэкая эффективность обмена информацией между внешними устройствами, если такая информация не подлежит дополнительной обмотке. в МП.

Целью изобретения является повышение эффективности обмена информацией за счет параллельной работы микропроцессора и передачи информации мезеду внешними устройствами.

Поставленная цель достигается тем что в устройство для сопряжения с микропроцессором, содержащее однонаправленный коммутатор, двунаправленный коммутатор, регистр состояний и группу периферийных блоков, каждый из которых содержит источник и приемник информации, причем информационный вход однонаправленного коммутатора является адресным входом устройства, первый информационный вход, - выход двунаправленного коммутатора соединен с информационным входом регистра состояния и является информационными входом - выходом устройства, тактовый и синхровход регистра состояний являются первым тактовым и синхронизирующим входами устройства, введены блок управления, содержащий три элемента И, счетный триггер, элемент задержки, дешифраторы состояния, два триггера, элемент ИЛИ, три элемента И, а в каждый периферийный блок группы - элемент И, три счетчика,два формирователя импульсов, причем входы дешифратора состояния соединены с выходами регистра состояний, выход дешифратора состояния соединен с первым установочным входом первого триггера, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых объединены и являются входом готовности устройства, третьи входы второго и третьего элементов И объединены с первым входом первого элемента И блока управления и являются вторым тактовым входом устройства, третий вход первого элемента И соединен с первым инверсным входом второго элемента И блока управления НС первым тактовым входом уст-, ройства, выходы первого-, второго и третьего элементов И соединены соответственно со счетными входами первого, второго и третьего счетчиков, установочные входы которых объединены с установочным входом

первого триггера и соединены с

выходом элемента ИЛИ, выход первого счетчика соединен с первыми входами первого и второго формирователей импульсов, вькод второго счетчика

соединен с вторьм входом первого формирователя импульсов, выход третьего счетчика соединен с вторым входом второго фЬрмирователя импульсов, выход которого соединен с первым установочным входом второго

триггера и с первым входом элемента ИЛИ, второй вход которого является входом общего сброса устройства, выход первого фЬрмирователя импульсов

соединен с вторым установочным входом второго триггера, выход которого соединен с вторыми входами первого и второго элементов И блока управления, с установочным входом

триггера блока управления, управляющими входами двунаправленного и однонаправленного коммутаторов, причем в блоке управления выход первого элемента И соединен с синхровходом

триггера, выход которого соединен с первым входом третьего элемента И и через элемент задержки - с его вторым входом, выход третьего элемента И соединен с первыми стробирующими входами источников информации периферийных блоков группы, выход первого элемента И соединен с вторыми стробирующими входами источников и стробирующими входами приемников информации периферийных блоков группы, выход счетного триггера блока управления соединен с первыми входами элементов И периферийных блоков группы, вторые и третьи входы которых соединены соответственно с выходами готовности источников и приемников информации, сбросовые входы источников и п жемников информации соединены с входом общего

сброса устройства, информационные выходы источников и информационные входы приемников информации через двунаправленную информационную шину соединены с вторым информационным

входом - выходом двунаправленного коммутатора, выход элемента И каждого периферийного блока соединен с управляющими входами источника

и приемника информации, группа выходов однонаправленного коммутатора и выходы элементов И периферийных блоков группы через адресную шину устройства соединены с группой входов элемента И каждого периферийного блока группы, кроме первого.

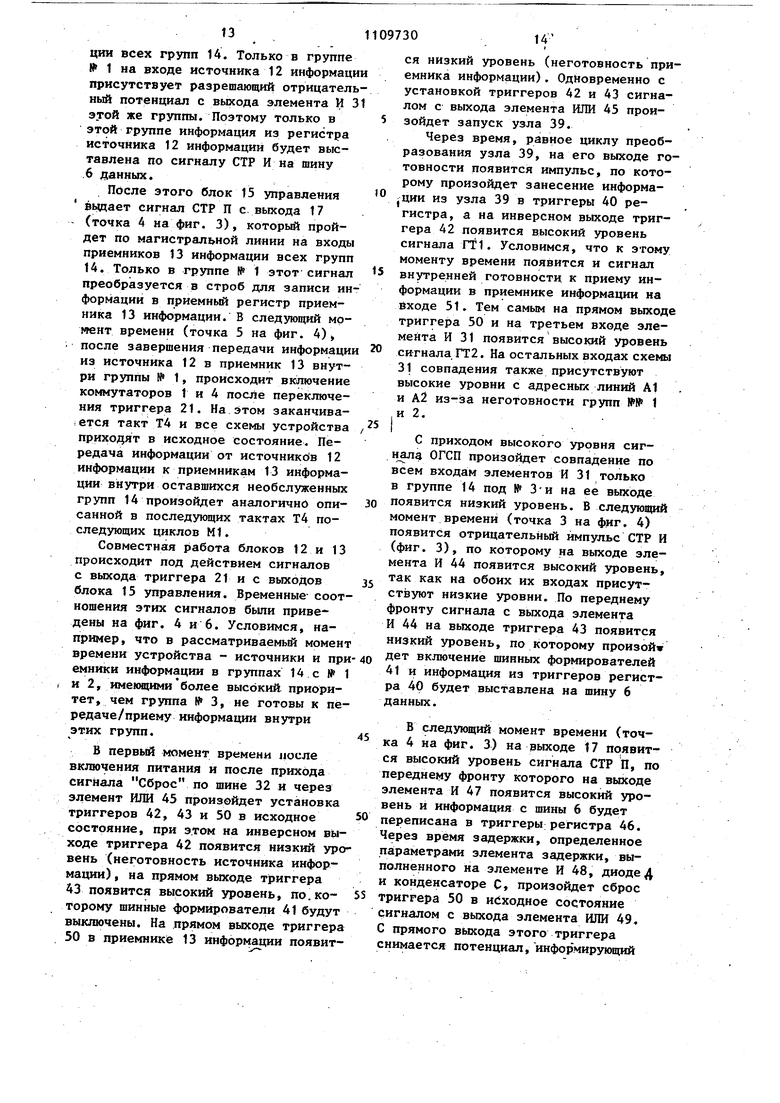

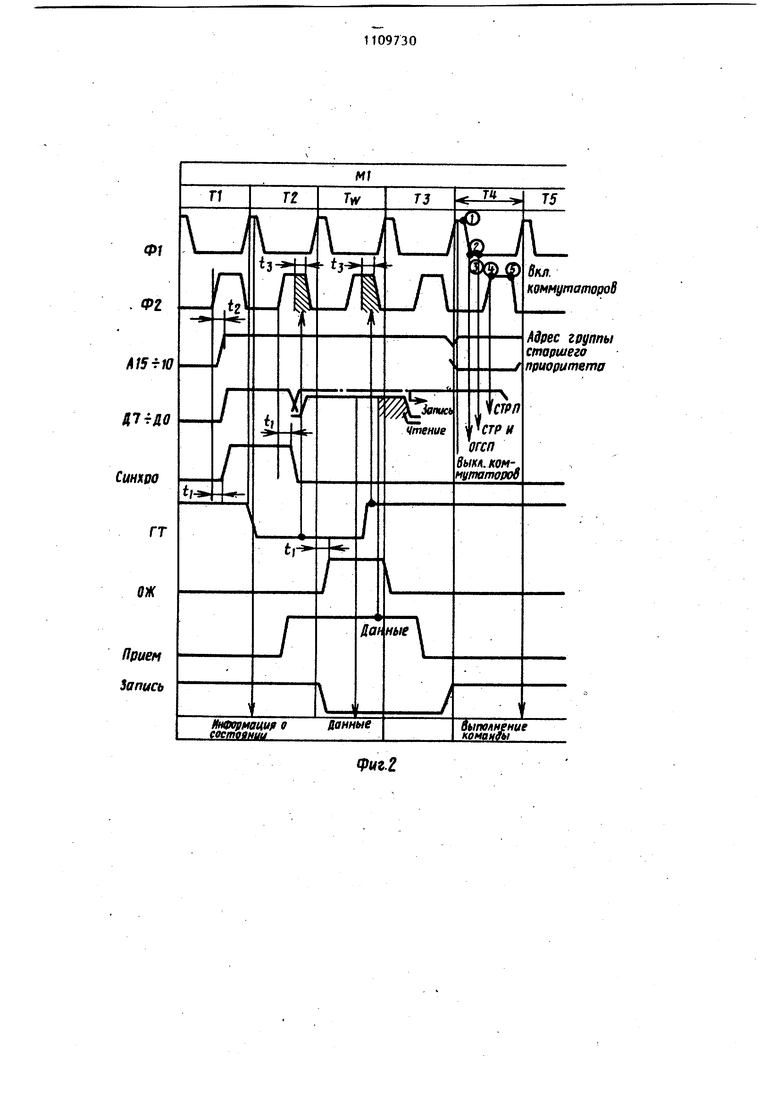

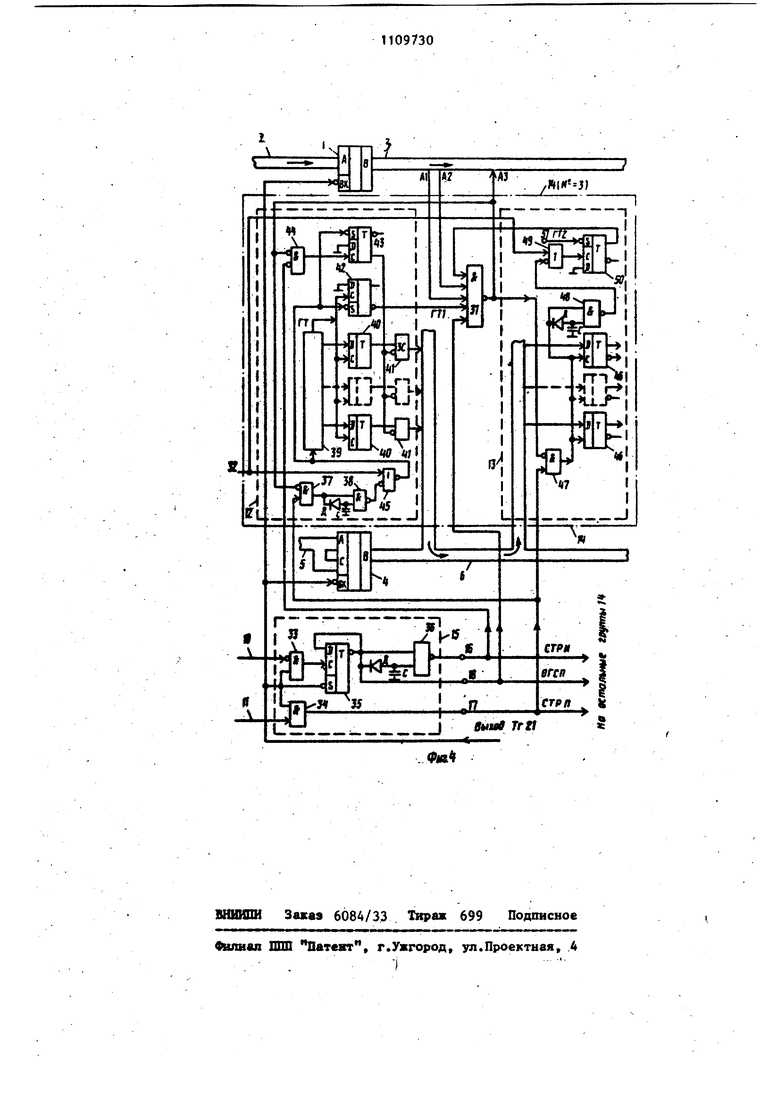

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 и 3 - временные диаграммы работы микропроцессора и устройства соответственно; на фиг. 4 - конкретный пример решения блока управления и группы периферийных блоков.

Устройство содержит (фиг. 1) однонаправленный коммутатор 1, адресный вход 2 устройства, общую адресную шину 3 устройства, двунаправленный коммутатор 4, вход - выход 5 .информации устройства, общую шину 6 информации устройства, регистр 7 состояния, вход 8 синхронизации уст.ройства, вход 9 Готовность устройства, первый тактовый вход 10 тактового сигнала Ф1, второй тактовый вход 11 тактового сигнала Ф2, источники 12 информации и приемники 13 информации, которые объединены в группы периферийных блоков 14, блок 15 управления передачей информации между внешними устройствами, первый выход 16 блока управления для стробирования всех источников информации, второй выход 17 блока управления для стробирования всех приемНИКОВ информации, третий выход 18 блока управления для определения группы старшего приоритета, дешифратор 19 состояний, триггеры 20 и 21, элемент ИЛИ 22, элементы И 23 - 25, счетчики 26 - 28, формирователи 29 и 30 сигналов, элемент И 31 в каждой группе внешних устройств и вход 32 общего сброса устройства.

На фиг. 3 приведен пример конкретного технического решения схем блоков 12, 13 и 15 устройства и соединение их между собой. Блок 13 управления передачей информации между внешними устройствами содержит элементы И 33 и 34, триггер 35 и элемент задержки, выполненный на элементе И 36, диоде 4 и конденсаторе С

Устройство-источник 12 информации состоит из элемента И 37, элемента задержки, выполненного на элементе И 38, диоде А и конденсаторе С, узла 39, имеющего информационные выходы и выход сигнала готовности, а также вход запуска, триггеров 40 регистра, трехстабильных шинных формирователей 41, триггера 42 готовности триггера 43, элемента И 44, элемента ИЛИ 45. Число триггеров 40 регистра и трехстабильных элементов 41 определяется разрядностью информационной посыпки АЦП и в данном примере равно 8.

Устройство-приемник информации состоит из триггеров 46 регистра, элемента И 47, элемента задержки, выполненного на элементеИ 48, диоде А и конденсаторе С, элементе ИЛИ 49, триггере 50 готовности с входом 51 внутренней готовности. Для конкретности на фиг. 4 изображена группа 14 под номером 3 (третий уровень приоритетности).

Однонаправленный коммутатор 1 предназначен для разделения и сопряжения адресного входа 2 устройства с общей адресной шиной 3 устройства. Двунаправленный коммутатор 4 используется для сопряжения информационного входа - выхода 5 устройства с общей шиной 6 данных устройства. Блок 15 управления передачей информации от источника 12 информации к приемнику 13 информации внутри одной из групп 14 с самым старшим приоритетом вьфабатывает следующие служебные сигналы: ОГСП - определение группы старшего приоритета, СТР И - строб источника информации и СТР П - строб приемника информации

Регистр 7 состояния необходим для фиксации байта состояния МП в момент прихода сигнала синхронизации Синхро от Mil. Этот байт состояния затем дешифрируется в дешифраторе 19 состояния.

На выполнение команды ввода данных в микропроцессор (МП) требуется три машинных цикла М. Каждый машинный цикл выполняется в течение времени, соответствующего длительности 3 - 4 тактов (Т1-Т4), длительность каждого из них соответствует периоду следования внешних тактовых сигналов Ф1 и Ф2. В течение машинного цикла Ml производится выборка команды. После загрузки команды в регистр команды первичный автомат МП по коду команды определяет, что данная команда ввода - двухбайтная.

Поэтому происходит переход первичного автомата из машинного цикла Ml к М2, т.е. из состояния Т4 автомат вновь переходит в состояние fl.

В машинном цикле М2 второй байт команды из памяти.считьюается по шине данных по сигналу разрешения ввода. Это второй байт команды определяет номер внешнего устройства ввода, от которого следует получить байт входных данных. В состоянии Т1 третьего машинного цикла МЗ первичный автомат выставляет на адресной шине адресную посыпку, которая была представлена во втором байте команды. В такте Т2 по прихрду импульса Ф2 проверяется наличие сигнала готовности. Затем МП переходит к такту ТЗ и -осуществляется передача данных в аккумулятор МП.

Каждый такт машинного цикла образует пару сигналов тактирования Ф1 и Ф2, поступающих от внешнего генератора. В начале каждого машинного цикла первичный автомат генерирует сигнал синхронизации микропроцессорной системы, по которому в регистр 7 состояния заносится слово состояния МП. Тем самым устройство микропроцессорной связи получает информацию о состоянии МП в каждом цикле.

Тактовые импульсы Ф1 делят каждый машинный цикл на такты. Логические цепи синхронизации в МП используют тактовые импульсы для формирования импульса синхронизации Синхро, который определяет начало каждого машинного цикла. Импульсы Синхро запускаются перепадом от низкого потенциала к высокому сигнала Ф2.

Итак, сигнал Синхро вырабатывается МП в начале каждого машинного цикла (фиг. 2) и используется в качестве сигнала, идентифицирующего информацию, представленную общей на информационном входе - выходе 5 устройства, как слово состояния. Поэтому сигналы, представленные на выходе восьмиразрядного регистра 7 состояния, используюгся в устройств для вьфаботки в дальнейшем управления передачей/приемом информации от источников к приемникам информации внутри одной группы стар шего приоритета. Всего МП типа ,К580 ИК80 имеет десять типов машинных циклов и соответственно десять кодов состояния, идентифицирующих зти циклы.. ,

Полный набор основных команд МП типа К580 ИК80 равен 72 командам. Первые три такта (Т1, Т2, ТЗ) первого машинного цикла МП одинаковы для команд.. В первом такте Т1 МП выставляет на общей шине адреса адрес очередной команды А15АО. Одновременно на шине Синхро появляется сигнал, который идентифицирует информацию на шине данных Д7-ДО как слово состояния и загружает его в регистр 7 состояния, а также свидетельствует о начале машинного цикла Ml. Для работы устройства необходимо идентифицировать в первом машинном цикле Ml при реализации любой команды только цикл Выборка команды, который имеет унитар . ньй код, соответствующий разрядам шины данных Д7-ДО, равный 1010 0010.

Сигнал Синхро связан с возрастающим фронтом импульса Ф2. Имеется задержка t. между переходом сигнала Ф2 низкого потенциала к высокому и возрастающим фронтом импульса Синхро. Существует также соответствующая задержка (также t)между следующим импульсом Ф2 и зйдним фронтом сигнала Синхро. Информация о состоянии отображается на шинах Д7-ДО в течение этого же интервала между импульсами Ф2. Переключение сигналов о состоянии подобным же образом управляется импульсами Ф2.

Возрастающий фронт импульса Ф2 в течение такта Т1 также загружает адресные пины (А15-АО). Сигналы на этих шинах становятся устойчивыми в пределах короткой задержки i2 относительно импульса Ф2 и продолжают оставаться стабильньми до появления первого импульса Ф2 после такта ТЗ. Это дает МП достаточное время для чтения данных из Памяти.

После того, как МП послал /адрес ) в память, возможно, что память запросит Ожидание, Это делается выдачей низкрго потенциала на шину .ГТ перед интервалом tj Установка готовности, который имеет место S в течение импульса Ф2 в пределах тактов Т2 или Т. До тех пор, пока шина ГТ находится под низким потен- , litHanoM, процессор будет пр остаивать, давая памяти время отреагировать н запрос МП (фиг. 2). МП отвечает на запрос ожидания путем вхождения в такт Т в конце хакта Т2, прежде чем перейти непосредственно к такту ТЗ. Вход в такт Т инициируется сигналом ожидания из МП, подтверждая запрос,памяти. П реход шины Ожидание низкого потенциала к высокому производится перед ним фронтом импульса Ф1 и имеет мес то в пределах короткой задержки t, входа в такт Т. Период ожидания может быть неопр . 1 деленной продолжительности. МП оста ся в состоянии ожидания до тех пор, пока шина ГТ не примет высокий потенциал. Сигнализация о готовности должна предшествовать заднему фронту импульса Ф2 на указанный интервал t- для того, чтобы гарантироват выход из Т такта. Тогда машинный цикл может быть продолжен, начиная с переднего фронта следующего импульса Ф1. Следовательно, интервал ожидания будет состоять из суммарного числа тактов Т и будет всегда кратен периоду импульсов тактового генератора. Из альтернативных состояний Т2 или всегда переходит в состояние ТЗ, в котором по шине данных поступают данные из памяти в регист кода операции МП. Дегшфратор кода операции и устройство управления МП формируют сигналы управления и синхронизации для внутренних пересылок данных, а также соответствующие дешифрируемой команде машинные циклы. Такты Т4 и Т5 отводятся для реализагщи операции, заданной кодом команды. На этом заканчивается машинный цикл М1. Рассмотрим более подробно работу МП в такте Т4 цикла Ml. Такт Т4 в цикле Ml имеет место для всех без исключения команд, в отличие от такта Т5, который имеет место только для 12-ти команд в цикле Ml . Кроме того, такты Т4 и Т5 цикла Ml характеризуют собой операции, которые будут полностью внутренними. Позтому в устройстве микропроцессорной связи такт Т4 полностью используется для передачи информации от источника 12 информации к прйемнику 13 информации внутри одной из групп периферийных блоков 1А (фиг.1). Для осуществления такой передачи информации необходимо произвести следующую последовательность операций: вьделить в машинном цикле Ml такт Т4, который всегда следует за тактом ТЗ, ко наступление такта ТЗ может быть задержано из-за времени ожидания МП; выключить коммутаторы 1 и 4 (фиг. 1) и тем самым разделить адресные входы 2 устройства и информационные входы - выходы 5 устройства от соответствуюпргх шин адре- «.v-. UJ 1.иитиетствующих шин адре са 3 и данных 6 устройства; onpejjeлить группу старшего приоритета из числа всех групп 14 внешних устройств, желающих произвести передачу/прием информации к этому моменту времени; вьадать сигнал строба источника информации (СТР И) и тем самым вьщать информацию из регистра источника информации на шину 6 данных .устройства; вьщать сигнал строба приемника информации (СТР ГТ), по которому выставленная на шине данных «информация будет переписана в регистр приемника информации; завершить цикл передачи/приема информации внутри группы 14 старшего приоритета и включить коммутаторы 1 и 4 и тем самым соединить общие адресные вход 2 устройства и информационный вход - выход 5 устройства с соответствующими шинами адреса 3 и данных 6 устройства. Устройство работает следующим образом. В первый момент после включения устройства (фиг. 3) с приходом сигнала Сброс на вход 32 злемента 1И 22 на выходе зтого элемента повится отрицательный потенциал, коорый установит в нулевое состояние ервый триггер 20 и триггеры счетиков 26, 27 и 28. Низкий уровень а выходе триггера 20 запретит проождение тактового сигнала Ф1 через лемент И 23, а тактового сигнала 2. - через элементы И 24 и 25. С приходом сигнала Синхро реистр 7 состояния зафиксирует код остояния, который в первом цикле l после включения Устройства всега будет Выборка команды. Дешифатор 19 кода состояния, настроеный только на состояние Выборка оманды, сработает, и на его выходе

появится потенциал, устанавливающий триггер 20 в единичное состояние. Тем самым откроется первый вход элемента И 23 и он начнет пропускать тактовые сигналы Ф1 после того, как появится сигнал ГТ памяти микропроцессорной системы на шине 9.

Такт ТА начинается всегда по переднему фронту второго импульса тактового сигнала Ф1, следующего после прихода переднего фронта сигнала ГТ (окончание такта ожидания н фиг. 3). Поэтому на вькоде счетчика 26 с коэффициентом счета К 2, который переключается по переднему фронту импульса Ф1, появится положительный потенциал с приходом второго импульса Ф1 (фиг. 3). Аналогичное проиэойдет и со счетчиком 27, который имеет коэффициент счета и на выходе которого появится положительный потенциал по приходу переднего фронта второго импульса Ф2, после того, как будет открыт элемен И 24 по входам, связанным с сигналом ГГ и с выходом триггера 20.

Так как выходы триггеров 26 и 27 соединены с входами формирователя 29 импульсов, то на вькоде схемные элементы формирователя 29 импульсов сформируют положительный импульс. Этим положительным импульсом установится в единичное состояние триггер 21 и на выходе этого триггера появится потенциал, который подается на вход блока 15 управления и на управлякицие входы коммутаторов 1 и 4. При этом указанные коммутаторы выключаются и произойдет разделение адресных входов 2 устройства и информационных входов - выходов 5 устройства от соответствующих шин 3 и 6 устройства.

Таким образом, по переднему фронту второго, после появления сигнала системной готовности ГТ на входе 9 импульса Ф1 произойдет выключение коммутаторов 1 и 4. При этом необходимо также учесть временную задержку, обусловленную временем выключения коммутаторов и временем переходных процессов остальных элементов схем.

Точки 1 на фиг. 3 соответствуют моменту времени, когда коммутаторы 1 и 4 выключились. В следующий момент времени (точка 2 на фиг. 3) после выключения коммутаторов 1 и 4

блок 15 управления выдаст сигнал Определение группы старшего приоритета (ОГСП). Группа № 1, выход элемента И 31 которой подключен к

щине А1, будет обладать самь1м старшим приоритетом. Приоритетность остальных групп убьшает по мере роста их номера.

Сигнал ОГСП снимается с третьего

выхода 18 блока 15 управления и подается на первые входы элементов И 31. Вторые и третьи входы этих элементов И соединены соответственно с выходами внутренней готовности источника информации (ГТ1) и приемника информации (ГТ2) этой же группы. Выходы элементов И 31 каждой группы соединены с входами элементов И последующих групп и с одной из адресных щин, разрядность которой соответствует уровню приоритетности данной, группы внешних устройств. Поэтому, например, выход элемента И 31 группы № 2 соединен с адресной

шиной А2, а выход элемента И 31 группы № 3 соединен соответственно с адресной шиной A3 и т.д.

Из фиг. 4 видно, что по сигналу ОГСП сработали бы схемы 31 совпадения в тех группах, в которых к

данному моменту времени появился сигнал ГТ1 как источников, так и сигнал ГТ 2 приемников информации. Но из всех этих групп разрешающий отрицательный потенциал появится только ни выходе элемента И 31 в группе с самым старшим приоритетом. Пусть в самом общем случае в указанный момент времени будут готовы передать

и принять информацию внутри группы все 16 групп. Тогда только на выхо де элемента И 31 группы 1 появится отрицательный потенциал совпадения, который закроет .все оставшиеся пятнадцать элементов И 31. Поэтому отрицательный потенциал с выхода элемента И 31 поступит на соответствующие входы источника 12 и приемника 13 информации только в

группе № 1 и подготовит их схемы для дальнейшей работы.

Через время задержки, необходимое для окончания переходшлх процессов после прихода сигнала ОГСП, блок 15 управления выработает на выходе 16 сигнал СТР И (точка 3 на фиг. 3), который пройдет по магистральной линии на входы источников 12 информации всех групп 14. Только в группе № 1 на входе источника 12 информаци присутствует разрешающий отрицатель ный потенциал с выхода элемента И 3 этой же группы/Поэтому только в этой группе информация из регистра источника 12 информации будет выставлена по сигналу СТР И на шину .6 данных. После этого блок 15 управления вццает сигнал СТР П с. выхода 17 -(точка 4 на фиг, 3), который пройдет по магистральной линии на входы приемников 13 информации всех групп 14. Только в группе № 1 этот сигнал преобразуется а строб для записи ин формации в приемный регистр приемника 13 информации. В следующий мрмент времени (точка 5 на фиг. 4) после завершения передачи информаци из источника 12 в приемник 13 внутри группы № 1, происходит включение коммутаторов i и 4 после переключения триггера 21. На этом заканчива.ется такт Т4 и все схемы устройства приходят в исходное состояние. Передача информации от истОчникЬв 12 информации к приемникам 13 информации внутри оставшихся необслуженных групп 14 произойдет аналогично описанной в последующих тактах Т4 последующих циклов Ml. Совместная работа блоков 12 и 13 происходит под действием сигналов с выхода триггера 21 и с выходов блока 15 управления. Временные- соот ношения этих сигналов были приведены на фиг. 4 и 6. Условимся, например, что в рассматриваемый момен времени устройства - источники и пр емники информации в группах 14 с № , и 2, имею1цимиболее высокий приоритет, чем группа № 3, не готовы к пе редаче/приему информации внутри этих групп. В первый момент времени после включения питания и после прихода сигнала Сброс по шине 32 и через элемент ИЛИ 45 произойдет установка триггеров 42, 43 и 50 в исходное состояние, при этом на инверсном вы ходе триггера 42 появится низкий ур вень (неготовность источника информации), на прямом выходе триггера 43 появится высокий уровень, по.которому шинные формирователи 41 будут выключены. На прямом выходе триггера 50 в приемнике 13 информации появит ся низкий уровень (неготовность приемника информации). Одновременно с установкой триггеров 42 и 43 сигналом с выхода элемента ИЛИ 45 произойдет запуск узла 39. Через время, равное циклу преобразования узла 39, на его выходе готовности появится импульс, по которому произойдет занесение информации из узла 39 в триггеры 40 регистра, а на инверсном выходе триггера 42 появится высокий уровень сигнала ГТ1. Условимся, что к этому моменту времени появится и сигнал внутренней готовности к приему информации в приемнике информации на входе 51. Тем самым на прямом выходе триггера 50 и на третьем входе элемента И 31 появится высокий уровень сигнала. ГТ2. На остальных входах схемы 31 совпадения также присутствуют высокие уровни с адресных линий А1 и А2 из-за неготовности групп №№ 1 1„г.. С приходом высокого уровня сигнала ОГСП произойдет совпадение по всем входам элементов И 31 только в группе 14 под № 3-й на ее выходе появится низкий уровень. В следующий момент времени (точка 3 на фиг. 4) появится отрицательный импульс СТР И (фиг. 3), по которому на выходе элемента И 44 появится высокий уровень, так как на обоих их входах присутствуют низкие уровни. По переднему фронту сигнала с выхода элемента И 44 на выходе триггера 43 появится низкий уровень, по которому произой дет включение шинных формирователей 41 и информация из триггеров регистра 40 будет выставлена на шину 6 данных. В следующий момент времени (точка 4 на фиг. 3) на выходе 17 появится высокий уровень сигнала СТР П, по переднему фронту которого на выходе элемента И 47 появится высокий уровень и информация с шины 6 будет переписана в триггеры регистра 46. Через время задержки, определенное параметрами элемента задержки, выполненного на элементе И 48, диоде 4 и конденсаторе С, произойдет сброс триггера 50 в и(ходное состояние сигналом с выхода элемента ИЛИ 49. прямого вькода этого триггера нимается потенциал, информирующий

о том, что в триггеры регистра 46 информация занесена.

По переднему фронту сигнала СТР П на выходе элемента И 37 появится высокий уровень, а на выходе элемента задержки, выполненного на элементе 38, диоде А и конденсаторе С, через соответствующее время задержки - отрицательный импульс, по которому прряэойдет сброс триггеров 42 и 43 в исходное состояние (аналогичное действию сигнала Сброс). При этом происходит также и повторный запуск узла 39. Время задержки элемента И 38 выбирается большим, чем время задержки элемента И 48, тем самым информация с шины 6 данных будет убрана (отключением шинных формирователей 41 по сбросу триггера 43) после того, как она будет принята в регистр 46 приемника информации.

Затем произойдет переключение триггера 21 (точка 5 на фиг. 3), по которому включаются коммутаторы 3 и 4, тем самым произойдет соединени адресного входа 2 устройства и инфомационного входа - выхода 5 устройства с соответствующими шинами 3 и устройства. Одновременно с этим сбросится триггер 35 в блоке 15 управления. Тем самым произойдет выключение блока 15 управления.

На этом заканчивается такт 14, и повторение указанных операций для

передачи/приема информации в оставшихся необслуженных группах 14 произойдет в такте Т4 цикла Ml следующе команды, который наступит сразу же после описанного цикла. Ml или же через циклы М2 - М5 в зависимости от вьтолняемой команды. При этом будет обслужена следующая группа, приоритетность которой является самой старшей из всех оставшихся необслуженных групп.

Таким образом, предлагаемое устройство позволяет в каждой команде при выполнении такта Т4 в цикле М.1 выполнять одновременную и параллель ную работу микропроцессора и передачу информации от источника к приемнику внутри одной из групп внешних устройств. Тем самым повышается эффективность обмена информацией. При этом не нарушается вьтолнение функци|1 МП в такте Т4, так как возможно кодирование внутренних операций для одной из возможных 21 команд внутренних операций.

В устройстве такт Т4 используется только в случае обоюдной готовности устройства - источника информации к передаче, а устройства-приемника информации к приему информации. Длительность такта Т4 составляет 1 мкс, т.е. и время передачи информации сокращается в 10 раз по сравнению с базовым объектом.

Фиг.1 Прием Запись

Фиг.2 Вкл. коммутаторов Адрес группы старшего приоритета

Ф1 Ф1

ГМ

сч.гб

Ф1-:г Сч 21

Л/хГг

СЧ.2В

Фг-З

огсп стр иСГР П

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Балашов Б.П., Пузанков Д.В | |||

| Микропроцессоры и микропроцессорные системы | |||

| М., Радио и связь, 1981 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-01—Подача