Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем случае, к устройству и к способу декодирования в системе связи и, в частности, к устройству и к способу осуществления турбодекодирования.

Уровень техники

В цифровых системах связи для эффективного исправления ошибок, которые могут возникать в канале связи во время передачи данных, обычно используют коды прямого исправления ошибок (ПИО, FEC). Это повышает достоверность передачи данных. Коды прямого исправления ошибок содержат турбокод. Поскольку турбокод способен лучше обеспечивать исправление ошибок при высокоскоростной передаче данных по сравнению со сверточным кодом, он одобрен для применения как в синхронной системе множественного доступа с кодовым разделением (МДКР, CDMA) стандарта 2000 года, МДКР2000 (CDMA2000), так и в асинхронной универсальной системе мобильной связи (УСМС, UMTS), обе из которых привлекают всеобщее внимание для использования в качестве системы мобильной связи третьего поколения.

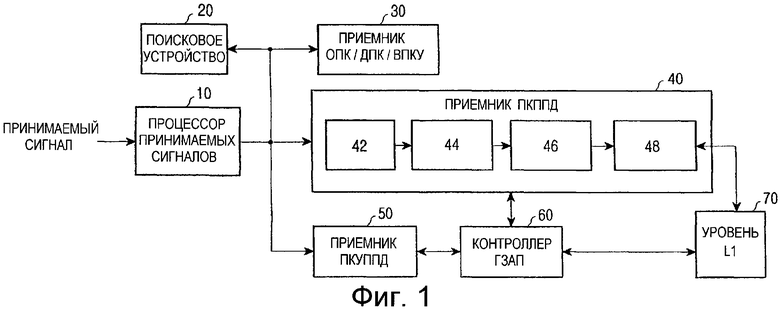

На Фиг.1 изображена блок-схема, на которой показан пример приемника системы мобильной связи третьего поколения. На Фиг.1 показана конструкция приемника, например, в системе соответствующей спецификации "эволюция 1х - данные и речь" (1x EV-DV), которая позволяет осуществлять высокоскоростную передачу пакетов данных.

Как показано на Фиг.1, процессор 10 принимаемых сигналов осуществляет обработку принятого сигнала в полосе радиочастот (РЧ), на промежуточной частоте (ПЧ) и в полосе частот исходных сигналов. Сигнал, обработанный процессором 10 принимаемых сигналов, разделяют по соответствующим каналам. Приемник 30 осуществляет обработку сигнала основного прямого канала (ОПК, F-FCH), сигнала дополнительного прямого канала (ДПК, F-SCH) и сигнала выделенного прямого канала управления (ВПКУ, F-DCCH). Приемник 40 осуществляет обработку сигнала прямого канала передачи пакетов данных (ПКППД, F-PDCH). Приемник 50 осуществляет обработку прямого канала управления передачей пакетов данных (ПКУППД, F-PDCCH). Приемник 40 содержит блоки 42, 44, 46 и 48. Функцией блока 42 является минимизация потерь, которые могут возникать в канале, и он содержит приемник компонента сигнала и устройство объединения (оба из которых на чертеже не показаны). Функцией блока 44 является преобразование сигнала таким образом, чтобы обеспечить возможность декодирования канала, и он содержит буфер демодуляции, устройство удаления кода Уолша, устройство обращения преобразования символов и дешифратор псевдослучайных последовательностей (все они на чертеже не показаны). Функцией блока 48 является осуществление декодирования и подачи результата декодирования в первый физический уровень 70 L1 для обращения к нему, и он содержит устройство турбодекодирования и буфер вывода (оба из которых на чертеже не показаны). Функцией блока 46 является передача символа демодуляции в блок 48 для его декодирования, и он содержит устройство объединения, устройство обращения перетасовки, обращенный перемежитель и буферное запоминающее устройство (все они на чертеже не показаны).

Поисковое устройство 20 представляет собой элемент, обеспечивающий поиск принятого сигнала, а контроллер 60 гибридного запроса с автоматическим повтором (ГЗАП, HARQ) представляет собой элемент, обеспечивающий выдачу запроса на повторную передачу символа, прием которого был произведен неудачно.

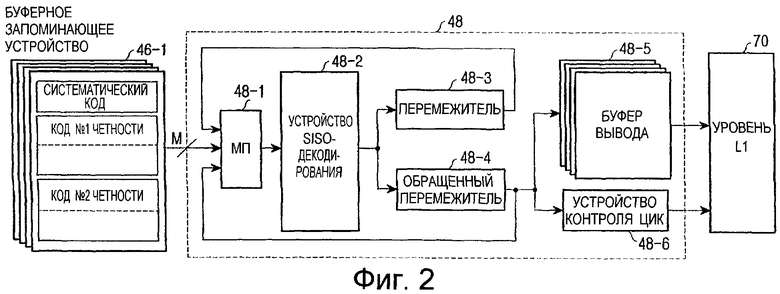

На блок-схеме из Фиг.2 показан пример обычного устройства турбодекодирования и, в частности, показан пример подробной конструкции блока 48 устройства турбодекодирования, показанного на Фиг.1. Изображенное на чертеже устройство турбодекодирования создано, например, посредством схемы с гибким вводом и гибким выводом данных (SISO). Устройство турбодекодирования может быть также реализовано с использованием схемы на основе максимума апостериорной вероятности (МАВ, MAP), или схемы на основе алгоритма Витерби с гибким выводом данных путем обмена содержимым регистров (RESOVA), которые применяют вместо схемы SISO. Схема SISO представляет собой схему вычисления достоверной вероятности для символа, а схема RESOVA представляет собой схему вычисления вероятности для кодового слова с учетом тракта, по которому проходит символ в виде длинного кодового слова.

Со ссылкой на Фиг.2, символы (информационные биты), запомненные в буферном запоминающем устройстве 46-1 блока 46, показанного на Фиг.1, подают на вход блока 48. В буферном запоминающем устройстве 46-1 осуществляют раздельное запоминание систематического кода, который представляет собой систематический код перемеженных битов, а также кода № 1 четности и кода №2 четности, которые представляют собой несистематические коды перемеженных битов. Биты систематического кода и биты кодов четности одновременно подают из буферного запоминающего устройства 46-1 в блок 48. Например, в системе, соответствующей спецификации "эволюция 1х - данные и речь" (1x EV-DV), буферное запоминающее устройство 46-1 представляет собой буферное запоминающее устройство для квазидополняющего турбокода (КДТК, QCTC), служащее для запоминания символов, принятых из передатчика, после их кодирования посредством кода КДТК (QCTC). Поскольку один код, вывод которого осуществляют из буферного запоминающего устройства 46-1, состоит из М бит, а из буферного запоминающего устройства 46-1 осуществляют вывод всего трех кодов, которыми являются систематический код и коды четности: код № 1 четности и код № 2 четности, то между буферным запоминающим устройством 46-1 и блоком 48 создана 3×M-битная шина, а коды с выхода буферного запоминающего устройства 46-1 подают в мультиплексор (МП) 48-1 блока 48.

Блок 48 устройства турбодекодирования содержит мультиплексор 48-1, устройство 48-2 SISO-декодирования (или устройство декодирования для схемы SISO), перемежитель 48-3, обращенный перемежитель 48-4, буфер 48-5 вывода и устройство 48-6 контроля посредством циклического избыточного кода (ЦИК, CRC). Мультиплексор 48-1 осуществляет мультиплексирование битов, поступивших из буферного запоминающего устройства 46-1, с выхода перемежителя 48-3 и с выхода обращенного перемежителя 48-4. Устройство 48-2 SISO-декодирования осуществляет SISO-декодирование сигнала, полученного на выходе мультиплексора 48-1, с использованием схемы, показанной на Фиг.3. Перемежитель 48-3 осуществляет перемежение сигнала, полученного на выходе устройства 48-2 SISO-декодирования, а обращенный перемежитель 48-4 осуществляет обращение перемежения сигнала, полученного на выходе устройства 48-2 SISO-декодирования. Буфер 48-5 вывода обеспечивает запоминание результата обращенного перемежения, полученного посредством обращенного перемежителя 48-4, таким образом, чтобы процессор 70 первого уровня L1 мог получать сведения о результате обращенного перемежения. Устройство 48-6 контроля посредством ЦИК осуществляет проверку результата обращенного перемежения, полученного посредством обращенного перемежителя 48-4, с использованием ЦИК и обеспечивает передачу результата проверки с использованием ЦИК в процессор 70 уровня L1.

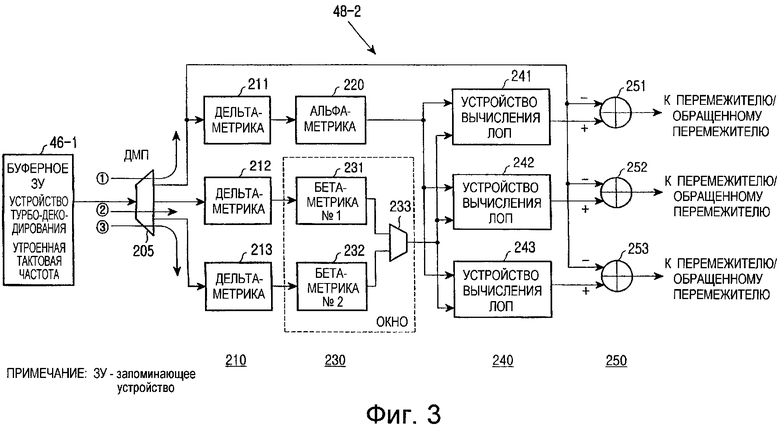

На блок-схеме из Фиг.3 показан пример обычного устройства SISO-декодирования. На чертеже показан пример, в котором устройство SISO-декодирования реализовано с использованием схемы, обеспечивающей режим "скользящего окна", и здесь сделано предположение, что количество окон равно 2. Устройство SISO-декодирования идентично по своей основной структуре устройству MAP-декодирования (или устройству декодирования для схемы MAP) и отличается от устройства MAP-декодирования только значением, получаемым на его выходе.

Со ссылкой на Фиг.3 устройство SISO-декодирования в процессе декодирования осуществляет вычисление нескольких метрик. То есть во время операции декодирования устройство SISO-декодирования вычисляет значения дельта-метрики, альфа (α) метрики, бета (β) метрики и логарифмического отношения правдоподобия (ЛОП, (LLR). Демультиплексор 205, обозначенный как ДМП (DEMUX), осуществляет доступ к информационным битам, запомненным в буферном запоминающем устройстве 46-1, с заранее заданной частотой, то есть с частотой, в три раза превышающей тактовую частоту (или рабочую частоту) устройства турбодекодирования, и создает первый выходной сигнал (1), второй выходной сигнал (2) и третий выходной сигнал (3). Блок 210 вычисления дельта-метрики содержит три вычислительные устройства 211-213, вычисляющие дельта-метрики, соответственно для первого, второго и третьего выходных сигналов (1)-(3). Дельта-метрика, вычисленная посредством устройства 211 вычисления дельта-метрики, поступает в устройство 220 вычисления альфа-метрики, и оно вычисляет соответствующую ей альфа-метрику. Блок 230 вычисления бета-метрики состоит из двух вычислительных устройств 231 и 232, а также мультиплексора 233. То есть блок 230 вычисления бета-метрики содержит вычислительное устройство 231, служащее для вычисления первой бета (β1) метрики, вычислительное устройство 232, служащее для вычисления второй бета (β2) метрики, и мультиплексор 233, служащий для мультиплексирования результатов вычислений, полученных посредством вычислительных устройств 231 и 232. Блок 240 вычисления ЛОП состоит из трех вычислительных устройств 241-243, в него поступает альфа-метрика, вычисленная посредством устройства 220 вычисления альфа-метрики, и результат мультиплексирования, полученный посредством мультиплексора 233, и он осуществляет вычисление соответствующего им значения ЛОП. Блок 250 вычитания состоит из трех вычитающих устройств 251-253, которые вычитают первый выходной сигнал (1), полученный из демультиплексора 205, из значений ЛОП, вычисленных посредством устройств 241-243 вычисления ЛОП, и обеспечивает подачу результата вычитания в перемежитель 48-3 и в обращенный перемежитель 48-4, показанные на Фиг.2, для их перемежения/обращенного перемежения.

Как описано выше, обычное устройство SISO-декодирования состоит из блока вычисления дельта-метрики, блока вычисления альфа-метрики и блока вычисления бета-метрики, обеспечивающих вычисление метрик, и блока вычисления ЛОП, обеспечивающего декодирование метрик на основании вероятности. В данном варианте блок вычисления бета-метрики состоит из двух вычислительных устройств, что соответствует количеству окон.

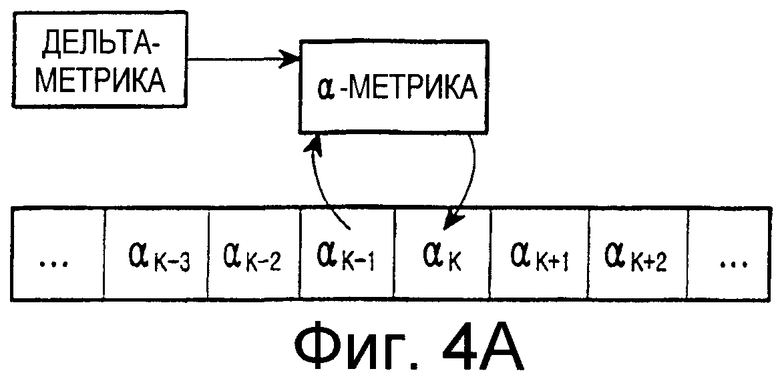

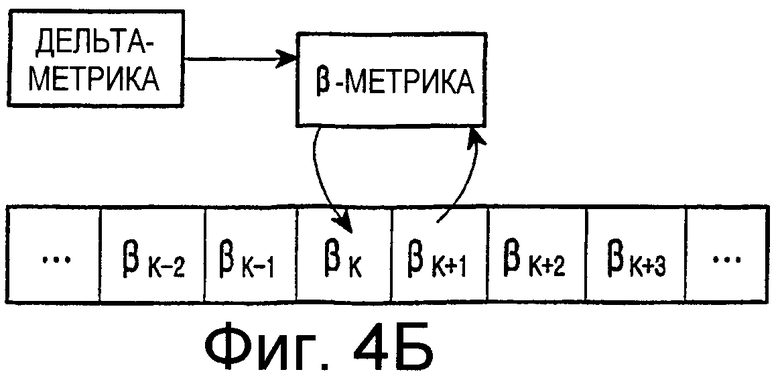

Дельта-метрика, также известная как "метрика состояния", отображает вероятность перехода устройства кодирования из одного состояния в другое состояние. Альфа (α) метрика, также известная как "метрика перехода в последующее состояние", представляет собой сумму метрики значения вероятности перехода из предыдущего состояния в последующее состояние и метрики значения вероятности возврата в предыдущее состояние. α-метрика относится к накопленной вероятности за период времени сигнала, вычисленной начиная с первого принятого сигнала, и ее вычисление осуществляют последовательно. Бета (β) метрика, также известная как "метрика возврата в предыдущее состояние", представляет собой накопленную вероятность перехода из текущего состояния в предыдущее состояние. Если вычислены обе метрики, α-метрика и β-метрика, то вычислено и значение ЛОП. ЛОП представляет собой вероятность появления символа и выражает отношение вероятности появления "1" к вероятности появления "0" в логарифмическом масштабе. Каждое из устройств 241-243 вычисления ЛОП, осуществляющих вычисление ЛОП, вычисляет вероятность появления символа, исходя из вероятности перехода в последующее состояние и в предыдущее состояние. Здесь положительное значение ЛОП отображает символ "1", а отрицательное значение ЛОП отображает символ "0". Для декодирования сигнала, прием которого осуществлен этим способом, устройство SISO-декодирования вычисляет значения обеих метрик: значение α-метрики и значение β-метрики. При этом, поскольку вычисление значения β-метрики должно быть осуществлено в порядке, противоположном порядку расположения принятого сигнала, запомненного в буферном запоминающем устройстве 46-1, значение ЛОП не может быть вычислено до тех пор, пока не будет полностью завершено вычисление β-метрики.

На Фиг.4A и Фиг.4Б показаны блок-схемы, на которых изображены примеры порядка вычисления метрик посредством обычного устройства SISO-декодирования из Фиг.3. В частности, на Фиг.4A показан процесс вычисления α-метрики, а на Фиг.4Б показан процесс вычисления β-метрики. Со ссылкой на Фиг.4A и Фиг.4Б, следует обратить внимание на то, что процесс вычисления α-метрики отличается от процесса вычисления β-метрики. Вычисление α-метрики αk осуществляют, исходя из (k-1)-той α-метрики, которая представляет собой предыдущее значение, а вычисление β-метрики βk осуществляют, исходя из (k+1)-той β-метрики, которая представляет собой следующее значение. Для вычисления β-метрики этим способом обращение к принятому сигналу должно быть осуществлено в порядке, противоположном тому порядку, в котором был выполнен его прием, что приводит к наличию исходной задержки в течение всей продолжительности принимаемого сигнала.

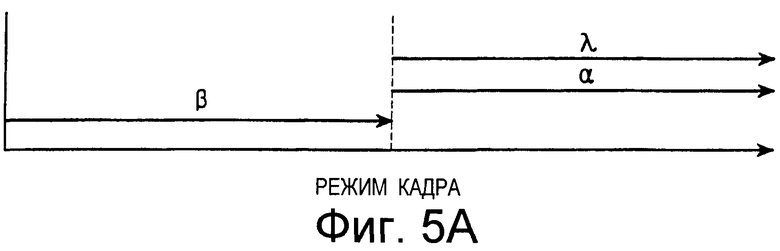

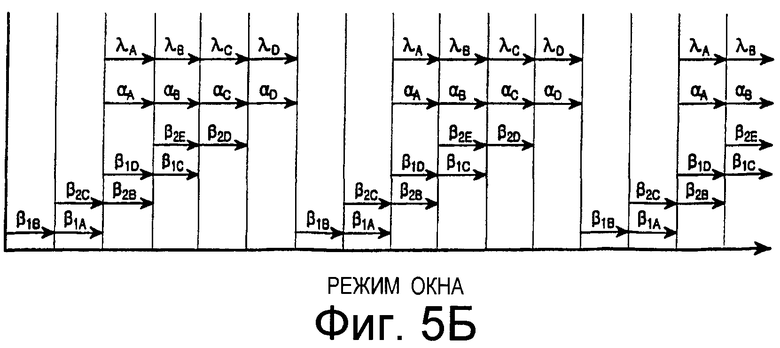

На блок-схемах из Фиг.5A и Фиг.5Б показан пример порядка выполнения вычислений посредством обычного устройства SISO-декодирования из Фиг.3 в режиме кадра и в режиме окна. В частности, на Фиг.5A показан порядок вычисления метрики устройством 48-2 SISO-декодирования в режиме кадра, а на Фиг.5Б показан порядок вычисления метрики устройством 48-2 SISO-декодирования из Фиг.3 в режиме окна.

Со ссылкой на Фиг.5A, поскольку вычисление метрики и значения ЛОП, обозначенного как λ, осуществляют после того, как полностью вычислена β-метрика, то возникает исходная задержка, равная периоду кадра. Устройство SISO-декодирования, имеющее такую схему, действующую в режиме кадра, вычисляет значение ЛОП λ путем вычисления α-метрики после вычисления β-метрики. Следовательно, при вычислении β-метрики возникает задержка по времени. Для уменьшения такой исходной задержки была предложена схема, действующая в режиме "скользящего окна".

Со ссылкой на Фиг.5Б, в режиме окна устройство 48-2 SISO-декодирования для вычисления β-метрики разделяет принятый сигнал на участки заданной длины. В том случае, если вычисление β-метрики осуществлено путем разделения принятого сигнала на участки заданной длины, то первоначально вычисленные значения имеют неточные значения вероятности, а вычисление более точных значений осуществляют позже. В действительности, при вычислении ЛОП может быть использовано значение, вычисленное за тот период времени, в котором вычислено точное значение. Здесь для удобства вычислений длина периода времени, в котором осуществляют неточные вычисления, задана равной длине периода времени, в котором осуществляют достоверные вычисления. В то время как в одном окне вычисляют точные значения, в другом окне вычисляют неточные значения, обеспечивая тем самым чередование точных значений и неточных значений. Примером вычисления β-метрики с использованием двух окон является блок 230 вычисления бета-метрики, показанный на Фиг.3. Следовательно, устройство 48-2 SISO-декодирования в режиме окна вычисляет три значения, которыми являются α-метрика, β1-метрика и β2-метрика. Вычисление дельта-метрики должно быть осуществлено до вычисления этих трех метрик.

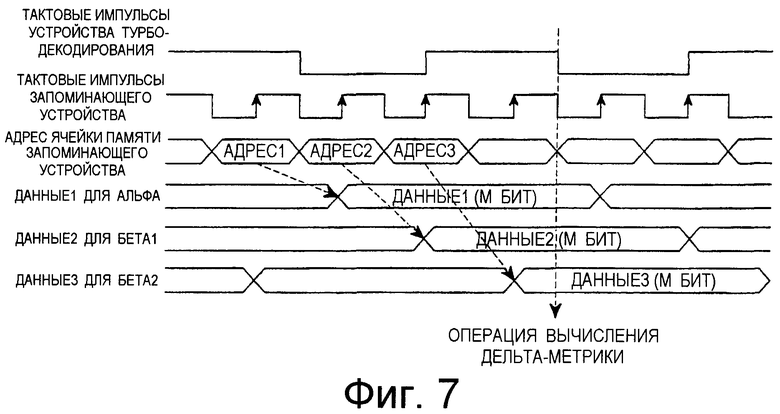

Со ссылкой на Фиг.3, устройства 211-213 вычисления дельта-метрики получают биты данных принятого сигнала, запомненные в ячейках памяти буферного запоминающего устройства 46-1, имеющих различные адреса, и вычисляют соответствующие дельта-метрики. То есть, как показано на Фиг.7, устройства 211-213 вычисления дельта-метрики осуществляют считывание сигналов из различных мест буферного запоминающего устройства 46-1 за время одного такта на рабочей частоте устройства турбодекодирования.

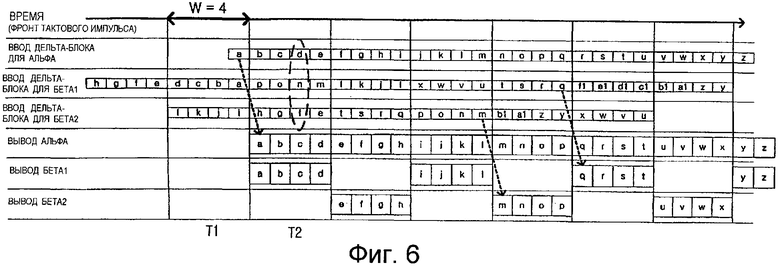

На блок-схеме из Фиг.6 показан пример последовательности обработки входных информационных битов и вывода метрики посредством устройства SISO-декодирования, изображенного на Фиг.3. Со ссылкой на Фиг.6, следует обратить внимание на то, что в устройства 211-213 вычисления дельта-метрики, входящие в состав устройства 48-2 SISO-декодирования, подают информационные биты принятого сигнала, запомненные в ячейках буферного запоминающего устройства 46-1, имеющих различные адреса. Горизонтальная линия обозначает ось времени, и можно заметить, что подачу различных информационных битов в устройства 211-213 вычисления дельта-метрики осуществляют по прошествии некоторого времени. Для обеспечения такого функционирования доступ к буферному запоминающему устройству 46-1 необходимо осуществлять в три раза быстрее, чем рабочая частота устройства турбодекодирования. То есть в качестве тактовой частоты для буферного запоминающего устройства 46-1 должна быть использована тактовая частота в три раза большая, чем тактовая частота устройства турбодекодирования.

На Фиг.7 показана временная диаграмма, на которой продемонстрирован пример синхронизации для операции доступа устройства SISO-декодирования из Фиг.3 к буферному запоминающему устройству. Со ссылкой на Фиг.7, устройство SISO-декодирования считывает информационные биты данные1 (data1), данные2 (data2) и данные3 (data3), запомненные в ячейках памяти буферного запоминающего устройства 46-1, имеющих различные адреса адрес1 (addr1), адрес2 (addr2) и адрес3 (addr3), и вычисляет дельта-метрику для α-метрики, дельта-метрику для β1-метрики и дельта-метрику для β2-метрики. Для этого операцию считывания из буферного запоминающего устройства 46-1 выполняют с частотой в три раза большей, чем тактовая частота устройства турбодекодирования.

Операцию доступа к буферному запоминающему устройству и операцию обработки данных, которые показаны на Фиг.6 и Фиг.7, выполняют с учетом того предположения, что размер W (или длина) окна W=4, который является намного меньшим, чем реально применяемая длина. При реальном использовании в высокоскоростном (или в высокопроизводительном) устройстве турбодекодирования размер окна устанавливают в интервале от 24 до 48 (W=24˜28), и в зависимости от обстоятельств может быть установлено еще большее его значение. Несмотря на то что изменяется размер W окна, структуру буфера не изменяют, а также не изменяют общий вид схемы последовательности обработки данных, но осуществляют ее увеличение пропорционально длине.

Со ссылкой на Фиг.6, буквы алфавита, записанные в каждом поле данных, подаваемых на вход из дельта-блока, отображают информационные биты, запомненные в ячейках памяти буферного запоминающего устройства 46-1, имеющих различные адреса, и представляют собой значение, используемое в устройстве 210 вычисления дельта-метрики. В том случае, когда вычисление β-метрики осуществляют перед вычислением α-метрики, два устройства 231 и 232 вычисления β-метрики работают поочередно (см. Фиг.6 со ссылкой на период T1 и период T2). Одновременно осуществляют вычисление α-метрики, начиная с того момента времени, когда вычислена достоверная β1-метрика (см. период T2). После вычисления β-метрики в течение начального периода W осуществляют вывод неточных значений вероятности, но в течение следующего периода W осуществляют вывод значения метрики с достоверной вероятностью. В выходном сигнале α, в выходном сигнале β1 и в выходном сигнале β2 буквы алфавита в каждом поле означают порядок метрики. Поскольку поступающие с выхода устройств вычисления 212 и 213 дельта-метрики сигналы для β1 и β2 чередуются друг с другом, то β-метрики, вычисленные посредством устройств 231 и 232 вычисления бета-метрики, являются непрерывными. Окружностью, показанной на Фиг.6 пунктирной линией, обозначено то, что необходимые в текущий момент времени информационные биты представляют собой принятые сигналы, хранящиеся в различных местах или в различных ячейках памяти буферного запоминающего устройства 46-1, имеющих адреса d, n и f.

Между тем, если сделано предположение, что устройство SISO-декодирования, показанное на Фиг.3, используют в системе, выполненной согласно спецификации "эволюция 1х - данные и речь" (1x EV-DV), в которой необходимо обеспечивать высокую скорость передачи данных, то требуется устройство турбодекодирования, работающее на частоте, приблизительно, 30-60 МГц. Следовательно, рабочая частота буферного запоминающего устройства 46-1 должна быть задана в диапазоне от 90 до 180 МГц, что в три раза превышает рабочую частоту устройства турбодекодирования. Такая рабочая частота устройства турбодекодирования является нецелесообразной для оконечного устройства мобильной связи, для которого необходимо обеспечивать низкую потребляемую мощность.

Как описано выше, система, соответствующая спецификации "эволюция 1х - данные и речь" (1x EV-DV), представляет собой типичную систему мобильной связи третьего поколения, позволяет осуществлять высокоскоростную передачу пакетов данных. В такой системе связи для обеспечения высокой производительности требуется высокоскоростное устройство турбодекодирования. Для обеспечения высокоскоростного декодирования подачу информационных битов (или символов), запомненных в буферном запоминающем устройстве, соединенном с предыдущим каскадом устройства турбодекодирования, в устройство турбодекодирования необходимо осуществлять надлежащим способом. Устройство SISO-декодирования со схемой, работающей в режиме скользящего окна, может обеспечить сокращение исходной задержки по сравнению с устройством SISO-декодирования со схемой, работающей в режиме кадра. Следовательно, предпочтительным вариантом является использование в качестве устройство турбодекодирования устройства SISO-декодирования со схемой, работающей в режиме скользящего окна. Устройство SISO-декодирования со схемой, работающей в режиме скользящего окна, выполняет операцию декодирования после считывания из буферного запоминающего устройства информационных битов, соответствующих количеству окон. Например, если количество окон равно 2, устройство SISO-декодирования вычисляет метрику для декодирования после трехкратного считывания информационных битов из буферного запоминающего устройства. Такая операция не вызывает никаких проблем в том случае, когда устройство турбодекодирования работает с низкой скоростью, но она может вызывать проблемы в том случае, когда устройство турбодекодирования работает с высокой скоростью. Это обусловлено тем, что в том случае, когда буферное запоминающее устройство должно работать в три раза быстрее, чем устройство турбодекодирования, а рабочая частота устройства турбодекодирования является низкой, использование в оконечном устройстве мобильной связи буферного запоминающего устройства, работающего на частоте в три раза более высокой, чем рабочая частота, является целесообразным решением, но когда рабочая частота устройства турбодекодирования является высокой, то использование буферного запоминающего устройства, работающего на частоте, в три раза превышающей рабочую частоту, является весьма нецелесообразным решением для оконечного устройства мобильной связи. Например, устройство турбодекодирования для системы МДКР2000 или для системы УСМС, предназначенной для предоставления услуг высокоскоростной передачи данных, должно работать с высокой скоростью для реализации всех его возможностей. Кроме того, даже при увеличении рабочей частоты буферного запоминающего устройства происходит резкое увеличение мощности, потребляемой оконечным устройством мобильной связи. Сильное увеличение потребляемой мощности непригодно для оконечного устройства мобильной связи, конструкция которого должна обеспечивать низкое энергопотребление.

Сущность изобретения

Следовательно, задачей настоящего изобретения является создание устройства и способа турбодекодирования, предназначенного для использования в системе связи, предоставляющей услуги высокоскоростной передачи пакетов данных, например, в системе, соответствующей спецификации "эволюция 1х - данные и речь" (1x EV-DV).

Другой задачей настоящего изобретения является создание устройства и способа, обеспечивающего согласование рабочей частоты устройства турбодекодирования с рабочей частотой буферного запоминающего устройства, которое подает информационные биты в устройство турбодекодирования, имеющееся в оконечном устройстве мобильной связи, работающем с высокой скоростью передачи.

Еще одной задачей настоящего изобретения является создание устройства и способа, позволяющих снизить потребление мощности оконечным устройством мобильной связи за счет устранения необходимости увеличения рабочей частоты буферного запоминающего устройства, в котором запоминают принятые информационные биты для их декодирования в мобильном оконечном устройстве, работающем с высокой скоростью передачи.

Для решения вышеуказанных и иных задач в настоящем изобретении предложено высокоскоростное буферное запоминающее устройство, работающее на той же самой частоте, что и устройство турбодекодирования, и расположенное между буферным запоминающим устройством приемника и устройством турбодекодирования, и предложено устройство декодирования, осуществляющее считывание информационных битов, запомненных в буферном запоминающем устройстве приемника, через высокоскоростное буферное запоминающее устройство, задержку считанных информационных битов на время, необходимое для устройства турбодекодирования, и последующее использование информационных битов с задержкой в устройстве декодирования с гибким вводом и гибким выводом данных (SISO), имеющемся в устройстве турбодекодирования. Буферное запоминающее устройство приемника осуществляет вывод информационных битов на рабочей частоте (или на тактовой частоте) устройства турбодекодирования. Настоящее изобретение устраняет необходимость увеличения рабочей частоты буферного запоминающего устройства приемника даже в случае увеличения скорости передачи данных, которые должны быть подвергнуты обработке в устройстве турбодекодирования. Таким образом, настоящее изобретение позволяет снизить мощность, потребляемую электронной схемой для аппаратуры мобильной связи.

Согласно первому варианту осуществления настоящего изобретения устройство турбодекодирования в системе связи содержит буферное запоминающее устройство и устройство SISO-декодирования. Буферное запоминающее устройство состоит из однонаправленного сдвигового регистра и одного или нескольких двунаправленных сдвиговых регистров. Устройство SISO-декодирования состоит из блоков вычисления метрик с первого по четвертый и блока вычитания.

Однонаправленный сдвиговый регистр имеет входной вывод, служащий для ввода данных, и выходной вывод, служащий для вывода данных. Однонаправленный сдвиговый регистр формирует потоки битов первой длины путем последовательного приема и сдвига битов входных данных, поступающих через входной вывод, а затем осуществляет последовательный вывод сформированных потоков битов первой длины через выходной вывод.

Каждый из двунаправленных сдвиговых регистров имеет первый вывод и второй вывод, которые служат для ввода/вывода данных, а биты входных данных разделены на группы, каждая из которых состоит из битов и имеет вторую длину, которая равна 1/2 первой длины. Двунаправленный сдвиговый регистр формирует потоки битов второй длины путем последовательного приема и сдвига битов нечетных групп из разделенных групп, поступающих через первый вывод, а затем осуществляет последовательный вывод сформированных потоков битов через первый вывод; и формирует потоки битов второй длины путем последовательного приема и сдвига битов четных групп из разделенных групп, поступивших через второй вывод, а затем осуществляет последовательный вывод сформированных потоков битов через второй вывод.

В первый блок вычисления метрики поступают биты с выходов соответствующих сдвиговых регистров, и он вычисляет соответствующие дельта-метрики. Во второй блок вычисления метрики поступают дельта-метрики из первого блока вычисления метрики, соответствующего однонаправленному сдвиговому регистру, и он вычисляет альфа-метрику. В третий блок вычисления метрики поступают дельта-метрики из первого блока вычисления метрики, соответствующего двунаправленным сдвиговым регистрам, и он вычисляет бета-метрики. В четвертый блок вычисления метрики поступает альфа-метрика, а также в него поступает результат мультиплексирования бета-метрик, и он вычисляет значения ЛОП, соответствующие соответствующим сдвиговым регистрам. Блок вычитания вычитает выходной сигнал однонаправленного сдвигового регистра из соответствующих значений ЛОП и осуществляет вывод результата вычитания для перемежения/обращенного перемежения.

В предпочтительном варианте буферное запоминающее устройство дополнительно содержит логическое устройство управления, определяющее, являются ли биты входных данных из разделенных групп битами нечетных групп или же битами четных групп, и подающее в двунаправленные сдвиговые регистры сигналы выбора, обеспечивающие подачу битов входных данных на первый вывод или на второй вывод в соответствии с результатом определения.

В предпочтительном варианте буферное запоминающее устройство дополнительно содержит демультиплексор и мультиплексор, соответствующие каждому из двунаправленных сдвиговых регистров. Демультиплексор имеет входной вывод, на который поступают биты входных данных, а также первый выходной вывод и второй выходной вывод, соединенные, соответственно, с первым выводом и со вторым выводом, подает биты нечетных групп на первый вывод через первый выходной вывод в ответ на соответствующий сигнал выбора, поступивший из логического устройства управления, и подает биты четных групп на второй вывод через второй выходной вывод. Мультиплексор осуществляет мультиплексирование потоков битов, выведенных через первый вывод, и потоков битов, выведенных через второй вывод, в ответ на соответствующий сигнал выбора, поступивший из логического устройства управления, и осуществляет вывод мультиплексированных потоков битов в первый блок вычисления метрики.

В предпочтительном варианте сигналами выбора являются управляющие сигналы, обеспечивающие подачу битов входных данных в двунаправленные сдвиговые регистры в различные моменты времени.

В предпочтительном варианте последовательный вывод битов нечетных групп осуществляют через первый вывод и одновременно осуществляют последовательный прием и сдвиг битов четных групп через второй вывод.

В предпочтительном варианте количество двунаправленных сдвиговых регистров определяется количеством окон.

В предпочтительном варианте первая длина и вторая длина определяются размером окон и количеством окон.

В предпочтительном варианте вторая длина определяется произведением размера окон на количество окон.

В предпочтительном варианте прием битов входных данных осуществляют на тактовой частоте устройства турбодекодирования.

Согласно второму варианту осуществления настоящего изобретения, устройство турбодекодирования в системе связи содержит буферное запоминающее устройство и устройство SISO-декодирования. Буферное запоминающее устройство состоит из двунаправленных сдвиговых регистров первой ступени и двунаправленного сдвигового регистра второй ступени. Устройство SISO-декодирования состоит из блоков вычисления метрик с первого по четвертый и блока вычитания.

Каждый из двунаправленных сдвиговых регистров первой ступени имеет первый вывод и второй вывод, которые служат для ввода/вывода данных, а биты входных данных разделены на группы, каждая из которых состоит из битов и имеет заданную длину. Двунаправленные сдвиговые регистры первой ступени формируют потоки вышеупомянутой длины путем последовательного приема и сдвига битов нечетных групп из разделенных групп, поступающих через первый вывод, а затем осуществляют последовательный вывод сформированных потоков битов через первый вывод; и формируют потоки битов вышеупомянутой длины путем последовательного приема и сдвига битов четных групп из разделенных групп, поступивших через второй вывод, а затем осуществляют последовательный вывод сформированных потоков битов через второй вывод.

Двунаправленный сдвиговый регистр второй ступени имеет третий вывод и четвертый вывод, которые служат для ввода/вывода данных, и этот двунаправленный сдвиговый регистр второй ступени формирует потоки битов вышеупомянутой длины путем последовательного приема битов, последовательно выведенных через первый вывод, через третий вывод и их сдвига, а затем осуществляет последовательный вывод сформированных потоков битов через третий вывод; и формирует потоки битов вышеупомянутой длины путем последовательного приема битов, последовательно выведенных через второй вывод, через четвертый вывод и их сдвига, а затем осуществляет последовательный вывод сформированных потоков битов через четвертый вывод.

В первый блок вычисления метрики поступают биты с выходов соответствующих сдвиговых регистров, и он вычисляет соответствующие дельта-метрики. Во второй блок вычисления метрики поступают дельта-метрики из первого блока вычисления метрики, соответствующего однонаправленному сдвиговому регистру, и он вычисляет альфа-метрику. В третий блок вычисления метрики поступают дельта-метрики из первого блока вычисления метрики, соответствующего двунаправленным сдвиговым регистрам, и он вычисляет бета-метрики. В четвертый блок вычисления метрики поступает альфа-метрика, а также в него поступает результат мультиплексирования бета-метрик, и он вычисляет значения ЛОП, соответствующие соответствующим сдвиговым регистрам. Блок вычитания вычитает выходной сигнал однонаправленного сдвигового регистра из соответствующих значений ЛОП и осуществляет вывод результата вычитания для перемежения/обращенного перемежения.

В предпочтительном варианте буферное запоминающее устройство дополнительно содержит логическое устройство управления, определяющее, являются ли биты входных данных из разделенных групп битами нечетных групп или битами четных групп, и подающее в двунаправленные сдвиговые регистры первой ступени сигналы выбора, обеспечивающие подачу битов входных данных на первый вывод или на второй вывод в соответствии с результатом определения.

В предпочтительном варианте буферное запоминающее устройство дополнительно содержит демультиплексор и мультиплексор, соответствующие каждому из двунаправленных сдвиговых регистров первой ступени. Демультиплексор имеет входной вывод, служащий для приема битов входных данных, а также первый выходной вывод и второй выходной вывод, соединенные, соответственно, с первым выводом и со вторым выводом, подает биты нечетных групп на первый вывод через первый выходной вывод в ответ на соответствующий сигнал выбора, поступивший из логического устройства управления, и подает биты четных групп на второй вывод через второй выходной вывод. Мультиплексор осуществляет мультиплексирование потоков битов, выведенных через первый вывод, и потоков битов, выведенных через второй вывод, в ответ на соответствующий сигнал выбора, поступивший из логического устройства управления, и осуществляет вывод мультиплексированных потоков битов в первый блок вычисления метрики.

В предпочтительном варианте буферное запоминающее устройство дополнительно содержит мультиплексор, соответствующий двунаправленному сдвиговому регистру второй ступени, а вышеупомянутый мультиплексор осуществляет мультиплексирование битов, выведенных через третий вывод, и битов, выведенных через четвертый вывод, в ответ на соответствующий сигнал выбора, поступивший из логического устройства управления, и осуществляет вывод мультиплексированных битов в первый блок вычисления метрики.

В предпочтительном варианте сигналами выбора являются управляющие сигналы, обеспечивающие подачу битов входных данных в двунаправленные сдвиговые регистры в различные моменты времени.

В предпочтительном варианте последовательный вывод битов нечетных групп осуществляют через первый вывод и одновременно осуществляют последовательный прием и сдвиг битов четных групп через второй вывод.

В предпочтительном варианте количество двунаправленных сдвиговых регистров первой ступени определяется количеством окон.

В предпочтительном варианте первая длина и вторая длина определяются размером окон и количеством окон.

В предпочтительном варианте вторая длина определяется произведением размера окон на количество окон.

В предпочтительном варианте прием битов входных данных осуществляют на тактовой частоте устройства турбодекодирования.

Краткое описание чертежей

Вышеупомянутые и иные задачи, отличительные признаки и преимущества настоящего изобретения станут более очевидными из приведенного ниже подробного описания при его рассмотрении совместно с сопроводительными чертежами, на которых изображено следующее:

на Фиг.1 изображена блок-схема, на которой показан пример приемника в системе мобильной связи;

на Фиг.2 изображена блок-схема, на которой показан пример обычного устройства турбодекодирования;

на Фиг.3 изображена блок-схема, на которой показан пример обычного устройства SISO-декодирования;

на Фиг.4A и Фиг.4Б изображены блок-схемы, на которых показан пример порядка вычисления метрики, осуществляемого посредством обычного устройства SISO-декодирования;

на Фиг.5A и Фиг.5Б изображены блок-схемы, на которых показан пример порядка вычисления в режиме кадра и режиме окна, осуществляемого посредством обычного устройства SISO-декодирования;

на Фиг.6 изображена блок-схема, на которой показан пример последовательности обработки входных информационных битов и вывода метрики, осуществляемых посредством устройства SISO-декодирования из Фиг.3;

на Фиг.7 изображена временная диаграмма, на которой показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой устройством SISO-декодирования из Фиг.3;

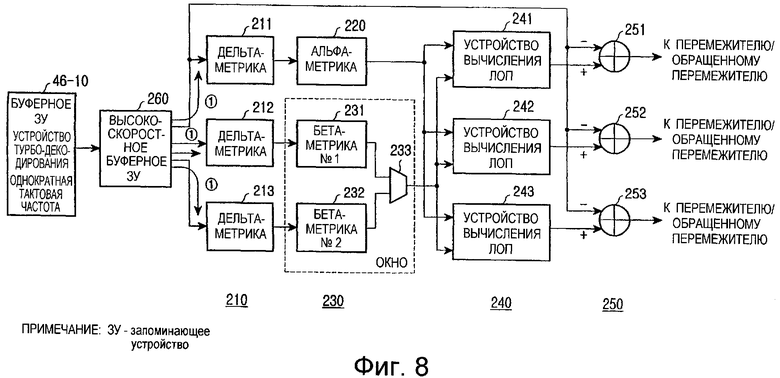

на Фиг.8 изображена блок-схема, на которой показан пример устройства SISO-декодирования согласно одному из вариантов осуществления настоящего изобретения;

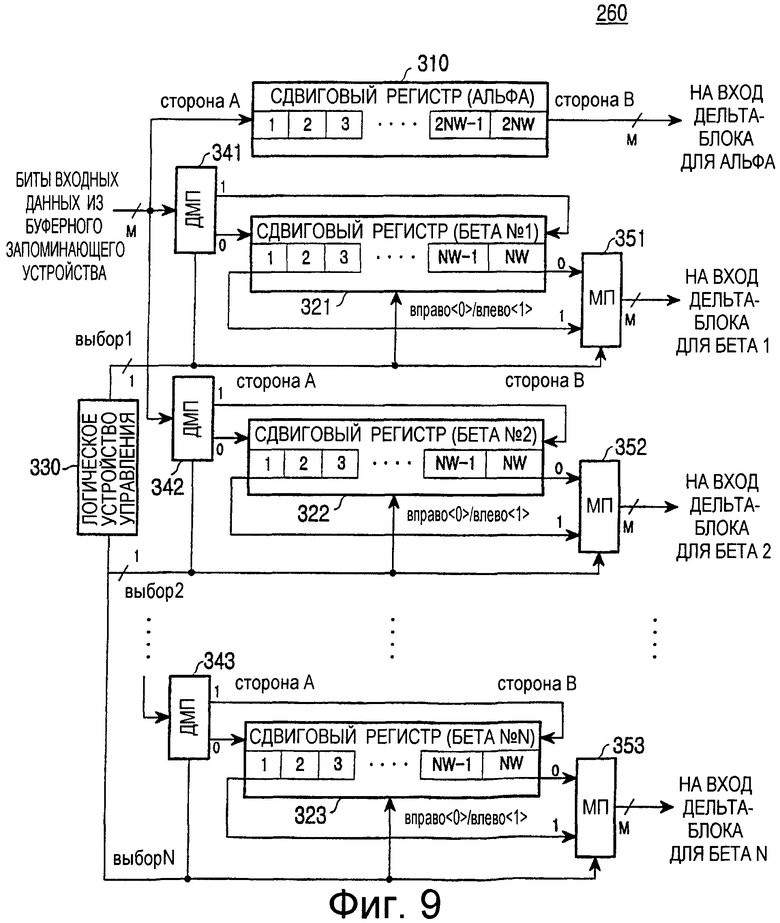

на Фиг.9 изображена блок-схема, на которой показан пример высокоскоростного буферного запоминающего устройства из Фиг.8 согласно одному из вариантов осуществления настоящего изобретения;

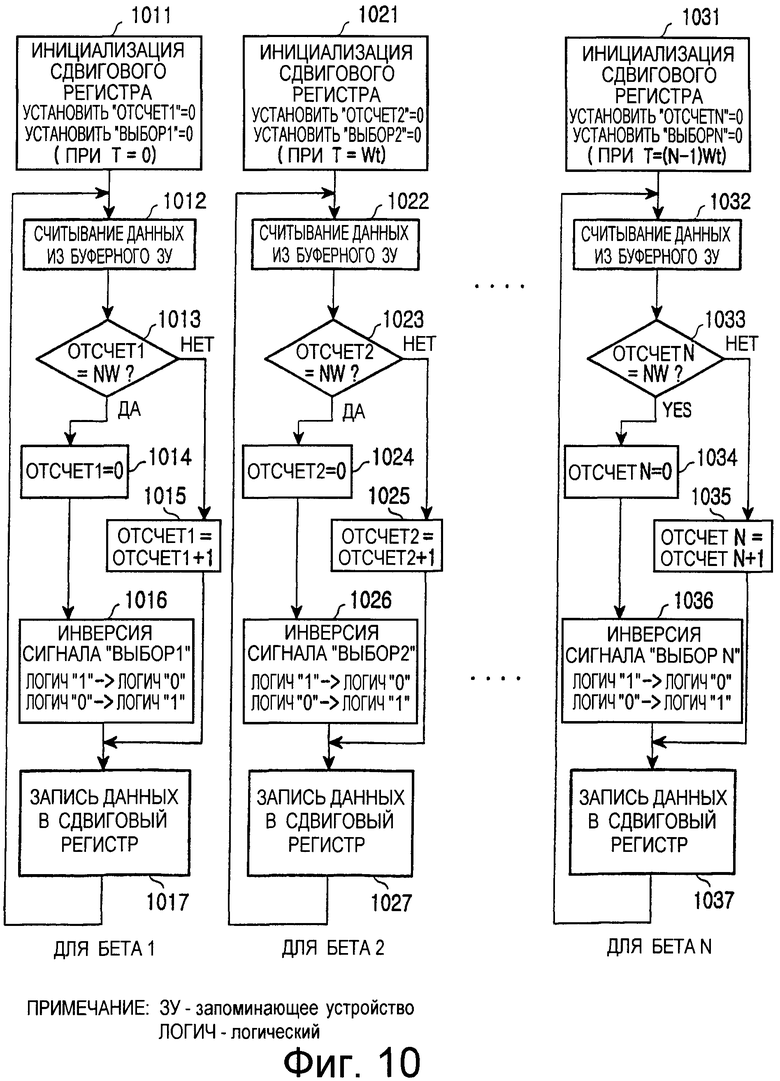

на Фиг.10 изображена схема последовательности операций, на которой показан пример операции управления, выполняемой посредством логического устройства управления из Фиг.9, согласно одному из вариантов осуществления настоящего изобретения;

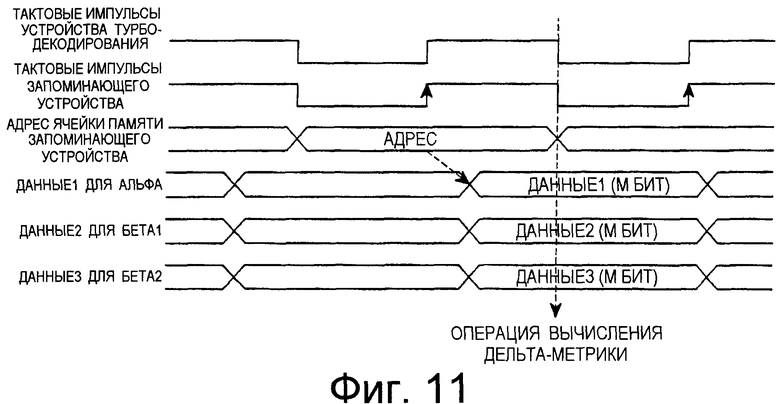

на Фиг.11 изображена временная диаграмма, на которой показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой высокоскоростным буферным запоминающим устройством из Фиг.9, согласно одному из вариантов осуществления настоящего изобретения;

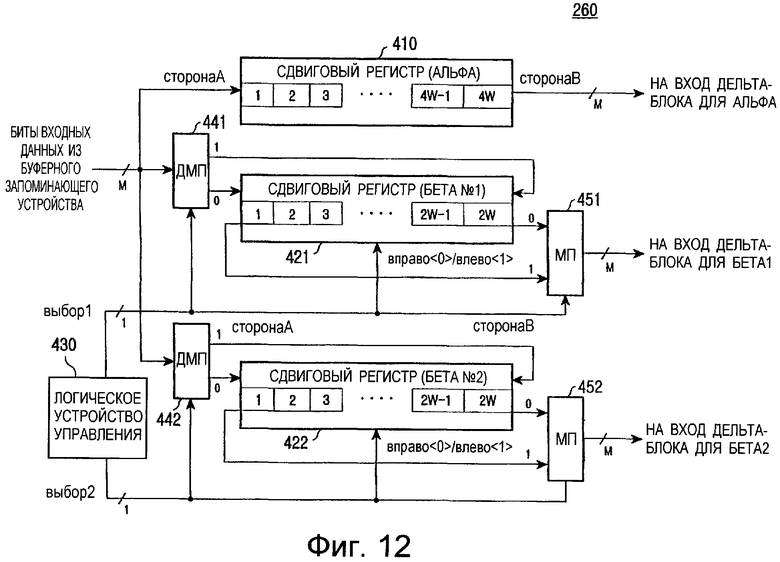

на Фиг.12 изображена блок-схема, на которой показан другой пример конструкции высокоскоростного буферного запоминающего устройства из Фиг.8 согласно варианту осуществления настоящего изобретения;

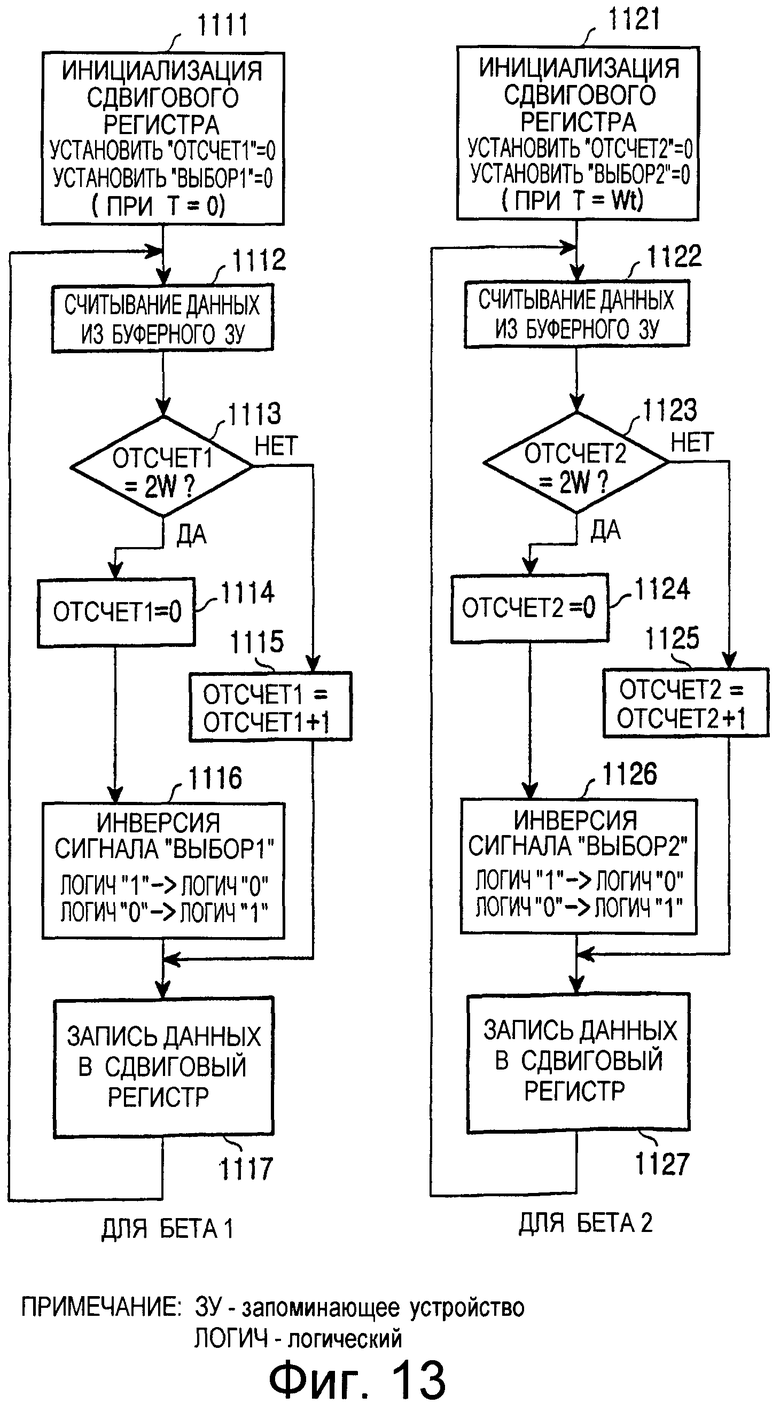

на Фиг.13 изображена схема последовательности операций, на которой показан пример операции управления, выполняемой посредством логического устройства управления из Фиг.12, согласно варианту осуществления настоящего изобретения;

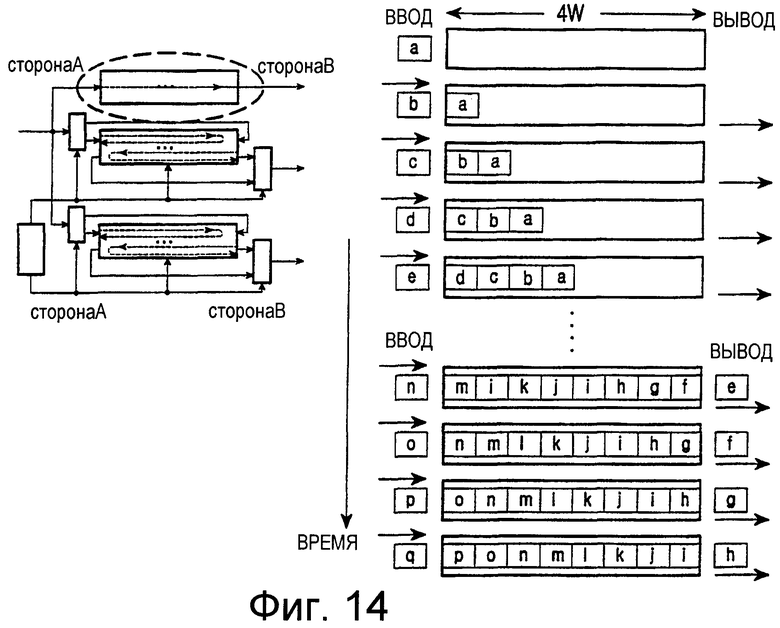

на Фиг.14 изображена блок-схема, на которой показан пример последовательности обработки данных, осуществляемой посредством сдвигового регистра для альфа-метрики из Фиг.12, согласно варианту осуществления настоящего изобретения;

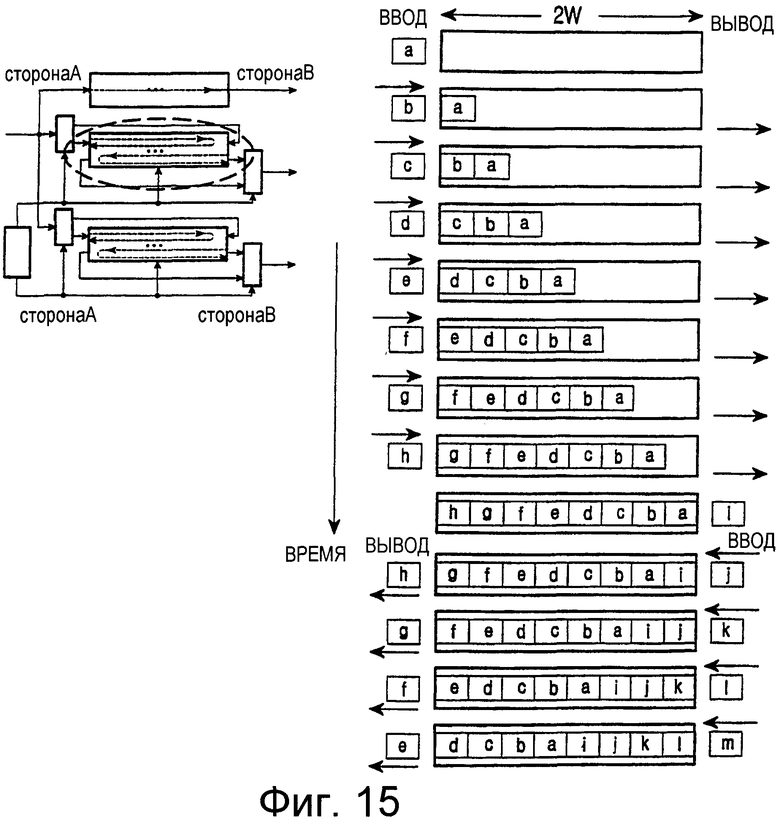

на Фиг.15 изображена блок-схема, на которой показан пример последовательности обработки данных, осуществляемой посредством сдвигового регистра для бета-метрики из Фиг.12, согласно варианту осуществления настоящего изобретения;

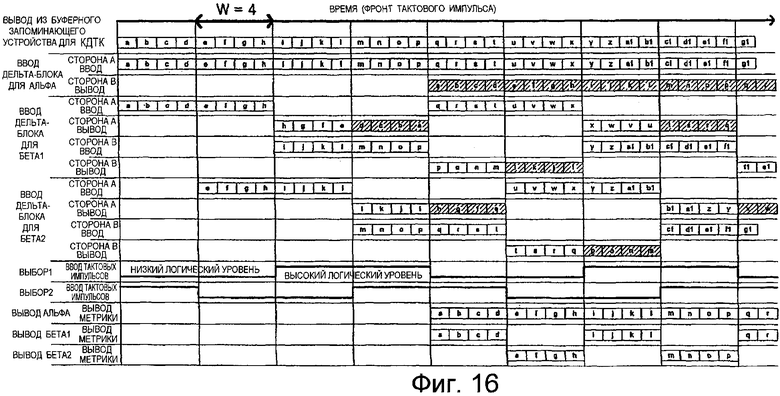

на Фиг.16 изображена блок-схема, на которой показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой высокоскоростным буферным запоминающим устройством из Фиг.12, согласно варианту осуществления настоящего изобретения;

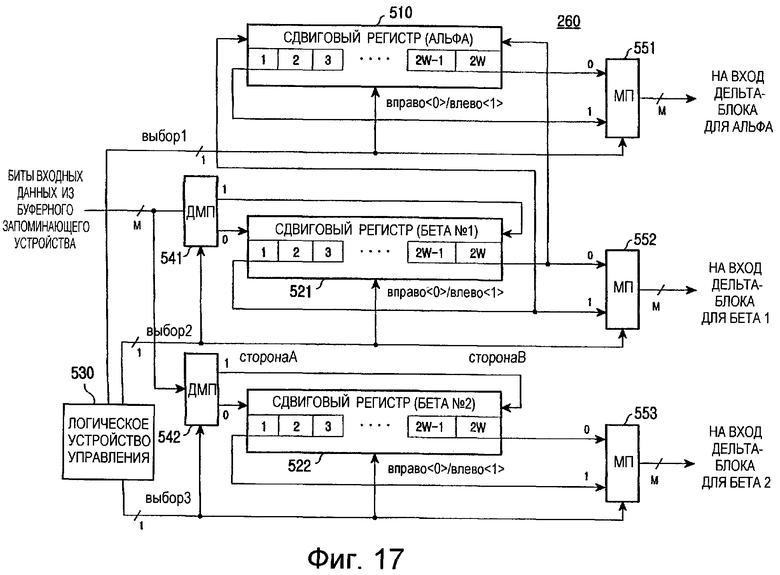

на Фиг.17 изображена блок-схема, на которой показан другой пример высокоскоростного буферного запоминающего устройства из Фиг.8 согласно варианту осуществления настоящего изобретения;

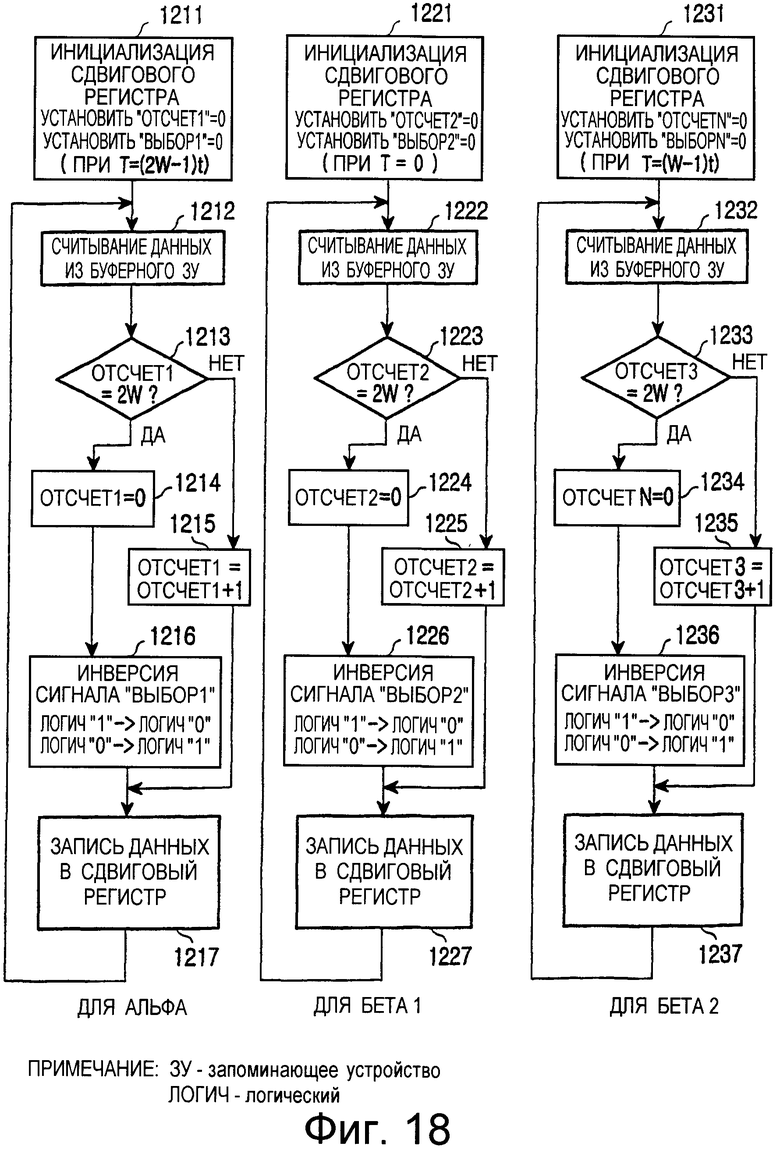

на Фиг.18 изображена схема последовательности операций, на которой показан пример операции управления, выполняемой посредством логического устройства управления из Фиг.17, согласно варианту осуществления настоящего изобретения;

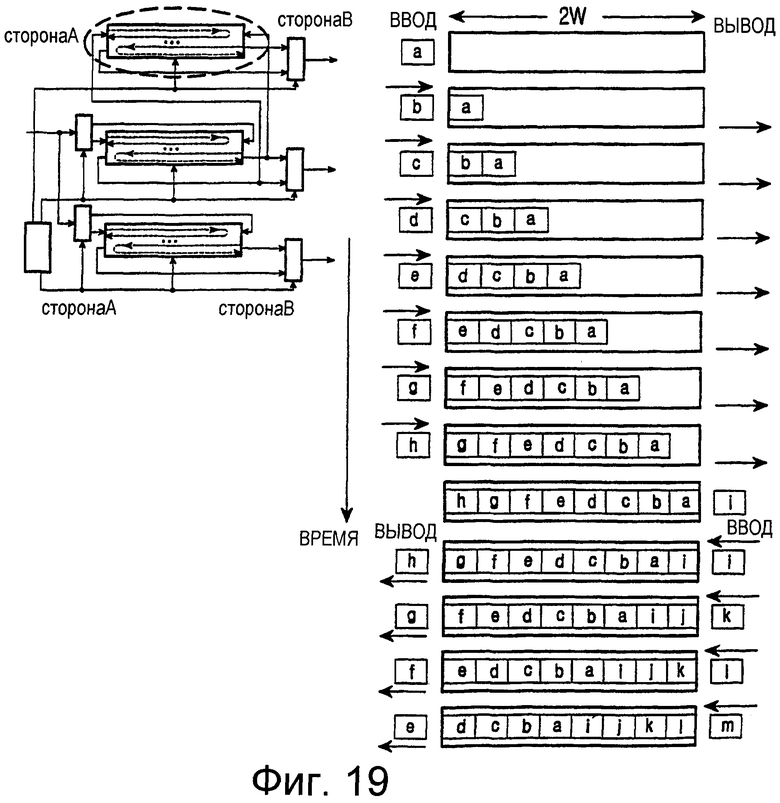

на Фиг.19 изображена блок-схема, на которой показан пример последовательности обработки данных, осуществляемой посредством сдвигового регистра для альфа-метрики из Фиг.17, согласно варианту осуществления настоящего изобретения; и

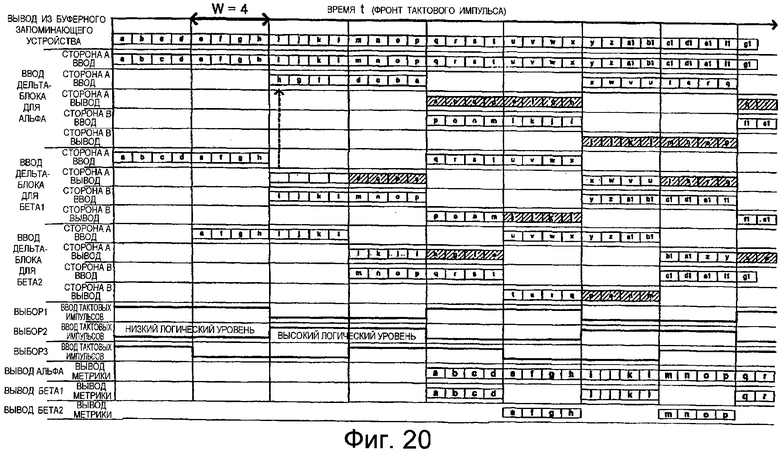

на Фиг. 20 изображена блок-схема, на которой показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой высокоскоростным буферным запоминающим устройством из Фиг.17, согласно варианту осуществления настоящего изобретения.

Подробное описание предпочтительных вариантов осуществления изобретения

Ниже приведено подробное описание нескольких вариантов осуществления настоящего изобретения со ссылкой на сопроводительные чертежи. Одинаковые или аналогичные элементы на чертежах обозначены одинаковыми номерами позиций. Подробное описание известных функций и конструкций, входящих в состав настоящего изобретения, здесь не приведено для краткости изложения.

На блок-схеме из Фиг.8 показан пример устройства SISO-декодирования согласно одному из вариантов осуществления настоящего изобретения. На чертеже показано только устройство SISO-декодирования, входящее в состав устройства турбодекодирования, изображенного на Фиг.2, и буферное запоминающее устройство, соединенное с предыдущей ступенью устройства SISO-декодирования.

Со ссылкой на Фиг.8, устройство декодирования согласно варианту осуществления настоящего изобретения содержит устройство SISO-декодирования, в состав которого входит блок 210 вычисления дельта-метрики, блок 220 вычисления альфа-метрики, блок 230 вычисления бета-метрики, блок 240 вычисления ЛОП и блок 250 вычитания. Устройство декодирования отличается тем, что дополнительно содержит высокоскоростное буферное запоминающее устройство 260, расположенное между устройством SISO-декодирования и буферным запоминающим устройством 46-10, в котором осуществляют запоминание принятых символов (или информационных битов), показанными на Фиг.3. Кроме того, буферное запоминающее устройство 46-10, входящее в состав устройства декодирования, отличается тем, что работает на тактовой частоте устройства турбодекодирования, а не на частоте буферного запоминающего устройства 46-1, имеющегося в обычном устройстве декодирования (см. Фиг.7 и Фиг.11), которая в три раза превышает тактовую частоту устройства турбодекодирования. То есть предложенное устройство декодирования отличается тем, что дополнительно содержит высокоскоростное буферное запоминающее устройство 260, расположенное после буферного запоминающего устройства 46-10, для обеспечения доступа к принятым информационным битам, запомненным в различных местах буферного запоминающего устройства 46-10, за 1 тактовый импульс устройства турбодекодирования, и обеспечивает подачу информационных битов, к которым был осуществлен доступ, в соответствующие вычислительные устройства 211-213 блока 210 вычисления дельта-метрики, за счет чего операцию вычисления дельта-метрики посредством блока 210 вычисления дельта-метрики выполняют за 1 тактовый импульс устройства турбодекодирования.

В предложенном устройстве декодирования, даже при его использовании в системе связи, предоставляющей услуги высокоскоростной передачи пакетов данных, например в системе, соответствующей спецификации "эволюция 1х - данные и речь" (1x EV-DV), не требуется увеличивать рабочую частоту буферного запоминающего устройства. Следовательно, это устройство декодирования пригодно для обеспечения снижения мощности, потребляемой оконечным устройством мобильной связи. В качестве справки, поскольку как в обычном устройстве декодирования из Фиг.3 передачу принятых информационных битов осуществляют непосредственно в устройство турбодекодирования через демультиплексор 205, соединенный с буферным запоминающим устройством 46-1 приемника, то операцию считывания данных из буферного запоминающего устройства 46-1 из приемника выполняют три раза, как показано на Фиг.6. Однако предложенное в изобретении устройство декодирования отличается тем, что вместо демультиплексора содержит дополнительное буферное запоминающее устройство 260, расположенное во входном каскаде устройства декодирования, что позволяет обеспечивать нормальную работу устройства SISO-декодирования за счет одной операции считывания за один тактовый импульс. То есть в предложенном устройстве декодирования при вычислении трех дельта-метрик необходима только лишь одна операция считывания из запоминающего устройства, и эту операцию выполняют с частотой, равной рабочей тактовой частоте устройства турбодекодирования. Такая операция возможна потому, что высокоскоростное буферное запоминающее устройство 260 заранее обеспечивает запоминание в нем принятого сигнала, а затем осуществляет перегруппировку принятого сигнала таким образом, чтобы он соответствовал требуемому входному сигналу для устройств 211 - 213 вычисления дельта-метрики.

Поскольку описание конструкции устройства SISO-декодирования было приведено выше, то его подробное описание будет опущено, а в изложенном ниже описании изобретения основное внимание сосредоточено на конструкции и функционировании высокоскоростного буферного запоминающего устройства 260 применительно к настоящему изобретению.

Высокоскоростное буферное запоминающее устройство 260 из предложенного устройства декодирования может быть выполнено так, как показано на Фиг.9, Фиг.12 и Фиг.17. На Фиг.9 показан вариант осуществления, в котором высокоскоростное буферное запоминающее устройство 260 состоит из одного однонаправленного сдвигового регистра 310 и из множества двунаправленных сдвиговых регистров 321, 322 и 323, количество которых равно количеству N окон. На Фиг.12 показан вариант осуществления, в котором высокоскоростное буферное запоминающее устройство 260 состоит из одного однонаправленного сдвигового регистра 410 и из множества двунаправленных сдвиговых регистров 421 и 422, количество которых совпадает с количеством окон, равным 2. Конструкции, показанные на Фиг.9 и Фиг.12, являются, в принципе, идентичными, но отличаются количеством окон. На Фиг.17 показан вариант осуществления, в котором высокоскоростное буферное запоминающее устройство 260 состоит из одного двунаправленного сдвигового регистра 510 и из множества двунаправленных сдвиговых регистров 521 и 522, количество которых совпадает с количеством окон, равным 2. Конструкция, показанная на Фиг.17, принципиально отличается от конструкций, показанных на Фиг.9 и Фиг.12. В конструкциях, показанных на Фиг.9 и Фиг.12, подачу информационных битов из буферного запоминающего устройства 46-10 в однонаправленный сдвиговый регистр и в двунаправленные сдвиговые регистры осуществляют одновременно. В отличие от этого, в конструкции, показанной на Фиг.17, информационные биты из буферного запоминающего устройства 46-10 подают в двунаправленные сдвиговые регистры 521 и 522, а в двунаправленный сдвиговый регистр 510, соответствующий однонаправленным сдвиговым регистрам 310 и 410 из первого и второго вариантов осуществления, подают информационные биты с выходов двунаправленных сдвиговых регистров 521 и 522.

Ниже более подробно раскрыты первый, второй и третий варианты осуществления изобретения, изображенные, соответственно, на Фиг.9, Фиг.12 и Фиг.17.

Первый вариант осуществления изобретения

На блок-схеме из Фиг.9 показан пример конструкции высокоскоростного буферного запоминающего устройства 260, изображенного на Фиг.8, согласно первому варианту осуществления настоящего изобретения. Со ссылкой на Фиг.9, высокоскоростное буферное запоминающее устройство 260 состоит из одного однонаправленного сдвигового регистра 310, N двунаправленных сдвиговых регистров 321-323, логического устройства 330 управления, демультиплексоров (ДМП) 341-343 и мультиплексоров (МП) 351-353.

Однонаправленный сдвиговый регистр 310 имеет 2NW областей памяти (длину) и содержит входной вывод, служащий для ввода данных, и выходной вывод, служащий для вывода данных. Здесь N - количество окон, а W - размер окон. Размер W окон может быть изменен. Однако даже при изменении размера W окон соотношение (например, 2W и 4W) сдвиговых регистров не изменяют. Для W=24 однонаправленный сдвиговый регистр 310 для α имеет размер, равный 96, а сдвиговые регистры 321-323 для β1 и β2 имеют размер, равный 48. При изменении W соответствующим образом изменяют длину сдвиговых регистров, а также изменяют последовательность обработки данных. Однако даже при изменении W структуру сдвиговых регистров не изменяют. Однонаправленный сдвиговый регистр 310 осуществляет последовательный прием битов входных данных из буферного запоминающего устройства 46-10 через входной вывод в соответствии с заданной тактовой частотой устройства турбодекодирования и сдвиг принятых битов входных данных слева (сторона A) направо (сторона B). После того как сформированы потоки битов данных первой длины (2NW), однонаправленный сдвиговый регистр 310 осуществляет последовательный вывод сформированных потоков битов данных первой длины через выходной вывод. Информационные биты, выведенные из однонаправленного сдвигового регистра 310, подают в устройство 211 вычисления дельта-метрики, соединенное с входным каскадом блока 220 вычисления альфа-метрики.

Каждый из двунаправленных сдвиговых регистров 321-323 имеет NW областей памяти и содержит первый вывод и второй вывод для ввода/вывода данных. Первый вывод представляет собой вывод, расположенный с левой стороны каждого из двунаправленных сдвиговых регистров 321-323, а второй вывод представляет собой вывод, расположенный с правой стороны каждого из двунаправленных сдвиговых регистров 321-323. Первый вывод и второй вывод могут обеспечивать как вывод данных, так и ввод данных. Количество двунаправленных сдвиговых регистров 321-323 определяется количеством окон. Если количество окон равно N, то количество двунаправленных сдвиговых регистров 321-323 задают равным N, а если количество окон равно двум, то количество двунаправленных сдвиговых регистров 321-323 задают равным 2. Биты входных данных, поступающие из буферного запоминающего устройства 46-10, разделены на группы, каждая из которых состоит из битов и имеет вторую длину (NW), которая равна 1/2 первой длины. Каждый из двунаправленных сдвиговых регистров 321-323 осуществляет последовательный прием битов нечетных групп из разделенных групп, поступивших через первый вывод, и выполняет их сдвиг слева (сторона A) направо (сторона B), и в том случае, если сформированы потоки битов второй длины, то каждый из двунаправленных сдвиговых регистров 321-323 осуществляет последовательный вывод сформированных потоков битов через первый вывод в порядке следования слева направо, который является обратным порядку их следования при вводе. Каждый из двунаправленных сдвиговых регистров 321-323 осуществляет последовательный прием битов четных групп из разделенных групп, поступивших через второй вывод, и их сдвиг справа налево, и в том случае, если сформированы потоки битов второй длины, то каждый из двунаправленных сдвиговых регистров 321-323 осуществляет последовательный вывод сформированных потоков битов через второй вывод в порядке следования слева направо, который является обратным порядку их следования при вводе.

Между выходным выводом буферного запоминающего устройства 46-10 и сдвиговыми регистрами 321-323 расположены демультиплексоры 341-343, а между сдвиговыми регистрами 321-323 и блоком 210 вычисления дельта-метрики расположены мультиплексоры 351-353. Входные выводы демультиплексоров 341-343 соединены с выходным выводом буферного запоминающего устройства 46-10, первые выходные выводы демультиплексоров 341-343 соединены со вторыми выводами сдвиговых регистров 321-323, а вторые выходные выводы демультиплексоров 341-343 соединены с первыми выводами сдвиговых регистров 321-323. Первые входные выводы мультиплексоров 351-353 соединены со вторыми выводами сдвиговых регистров 321-323, вторые входные выводы мультиплексоров 351-353 соединены с первыми выводами сдвиговых регистров 321-323, а выходные выводы мультиплексоров 351-353 соединены с устройствами 211-213 вычисления дельта-метрики.

Логическое устройство 330 управления создает сигналы выбора "выбор1" (select1) - "выборN" (selectN) для управления функционированием сдвиговых регистров 321-323 демультиплексоров 341-343 и мультиплексоров 351-353. Сигналы выбора могут быть охарактеризованы как сигналы, служащие для управления битами входных данных, поступающими из буферного запоминающего устройства 46-10, таким образом, чтобы обеспечить подачу битов входных данных в сдвиговые регистры 321-323 в различные моменты времени. Логическое устройство 330 управления определяет, являются ли биты входных данных, поступившие из буферного запоминающего устройства 46-10, битами нечетных групп или битами четных групп из разделенных групп, и обеспечивает подачу битов входных данных из буферного запоминающего устройства 46-10 на первые выводы или на вторые выводы сдвиговых регистров 321-323 в соответствии с результатом определения.

Например, в том случае, когда биты входных данных являются битами нечетных групп, логическое устройство 330 управления осуществляет вывод сигналов выбора с уровнем, равным "0", или с "низким логическим уровнем", а в том случае, когда биты входных данных являются битами четных групп, логическое устройство 330 управления осуществляет вывод сигналов выбора с уровнем, равным "1", или с "высоким логическим уровнем". В случае вывода сигналов выбора с уровнем, равным "0", демультиплексоры 341-343 подают биты входных данных из буферного запоминающего устройства 46-10 на первые выводы сдвиговых регистров 321-323. Затем сдвиговые регистры 321-323 осуществляют последовательный сдвиг информационных битов, полученных через их первые выводы, слева направо (в направлении направо). Одновременно с этим сдвиговые регистры 321-323 снова осуществляют последовательный сдвиг NW информационных битов, полученных ранее через их вторые выводы, а затем запомненных, слева направо, и осуществляют вывод подвергнутых сдвигу информационных битов через их вторые выводы.

В случае вывода сигналов выбора с уровнем, равным "1", демультиплексоры 341-343 подают биты входных данных из буферного запоминающего устройства 46-10 на вторые выводы сдвиговых регистров 321-323. Затем сдвиговые регистры 321-323 осуществляют последовательный сдвиг информационных битов, полученных через их вторые выводы, справа налево (в направлении налево). Одновременно с этим сдвиговые регистры 321-323 снова осуществляют последовательный сдвиг NW информационных битов, полученных ранее через их первые выводы, а затем запомненных, справа налево, и осуществляют вывод подвергнутых сдвигу информационных битов через их первые выводы.

Информационные биты, выведенные через первые выводы сдвиговых регистров 321-323, подают на вторые входные выводы мультиплексоров 351-353, а информационные биты, выведенные через вторые выводы сдвиговых регистров 321-323, подают на первые входные выводы мультиплексоров 351-353. Мультиплексоры 351-353 осуществляют мультиплексирование информационных битов, поданных через их первые входные выводы и вторые входные выводы, и осуществляют вывод мультиплексированных информационных битов в соответствующие устройства 211-213 вычисления дельта-метрики.

Как описано выше, предложенное устройство декодирования подает информационные биты, запомненные в различных местах буферного запоминающего устройства 46-10, в устройство SISO-декодирования с использованием высокоскоростного буферного запоминающего устройства 260, структура которого показана на Фиг.9. То есть высокоскоростное буферное запоминающее устройство 260 посредством сдвиговых регистров 310 и 321-323 изменяет порядок следования информационных битов, прием которых ранее был осуществлен последовательно таким образом, чтобы он соответствовал такому порядку их следования, который необходим для устройства SISO-декодирования со схемой, работающей в режиме скользящего окна.

Со ссылкой на Фиг.9, M бит из буферного запоминающего устройства 46-10 подают в сдвиговые регистры 310 и 321-323, имеющие 2NW или NW областей памяти. Здесь символом N обозначено количество окон, символом W обозначен размер окон, а символом М обозначено количество информационных битов, полученных из буферного запоминающего устройства 46-10 за один тактовый импульс устройства турбодекодирования. В том случае, когда буферное запоминающее устройство 46-10 представляет собой буферное запоминающее устройство для КДТК, М является суммой длины систематического кода в битах и длины кодов четности в битах. То есть М-битовый сигнал представляет собой сигнал, созданный путем суммирования М/3 битов систематического кода, М/3 битов первого кода четности и М/3 битов второго кода четности. Для обеспечения ввода М-битового сигнала сдвиговые регистры 310 и 321-323, демультиплексоры 341-343 и мультиплексоры 351-353 все выполнены М-разрядными. М-битовый выходной сигнал, то есть значения, выведенные из сдвиговых регистров 310 и 321-323, подают в устройства 211-213 вычисления дельта-метрики. Устройства 211-213 вычисления дельта-метрики получают три M/3-битовых сигнала, сумма которых равна М бит.

На Фиг.10 показаны операции управления, выполняемые логическим устройством 330 управления, изображенным на Фиг.9. В частности, на чертеже показана последовательность операций управления, в которой логическое устройство 330 управления осуществляет управление сдвиговыми регистрами 321-323 для β-метрики, демультиплексорами 341-343, соединенными с входами и с выходами сдвиговых регистров 321-323, и мультиплексорами 351-353.

На Фиг.10 операции 1011-1017 представляют собой последовательность операций управления сдвиговым регистром 321, демультиплексором 341 и мультиплексором 351. Операции 1021-1027 представляют собой последовательность операций управления сдвиговым регистром 322, демультиплексором 342 и мультиплексором 352. Операции 1031-1037 представляют собой последовательность операций управления сдвиговым регистром 323, демультиплексором 343 и мультиплексором 353. Поскольку соответствующие последовательности операций являются идентичными по выполняемым операциям, за исключением начальных моментов времени и наименований используемых сигналов, то для простоты ниже приведено описание только лишь последовательности операций 1011-1017. Для обеспечения выполнения этих операций управления логическое устройство 330 управления содержит счетчики, соответствующие сдвиговым регистрам 321-323. Для выполнения операции подсчета инициализацию счетчиков осуществляют в различные моменты времени с заданным смещением, равным W. Инициализацию счетчика № 1, соответствующего сдвиговому регистру 321, осуществляют в момент времени T=0, инициализацию счетчика № 2, соответствующего сдвиговому регистру 322, осуществляют в момент времени T=Wt, а инициализацию счетчика № N, соответствующего сдвиговому регистру 323, осуществляют в момент времени T=(N-1)Wt. Здесь символом t обозначено время, то есть длительность единичного тактового импульса.

Со ссылкой на Фиг.10, при выполнении операции 1011 логическое устройство управления 330 осуществляет инициализацию сдвигового регистра 321. При выполнении операции инициализации исходное значение отсчета счетчика № 1 устанавливают равным отсчет1=0, а исходное состояние сигнала выбора "выбор1" устанавливают равным выбор1=0. Кроме того, левый (сторона A) вывод сдвигового регистра 321 определяют как входной вывод, а правый (сторона B) вывод сдвигового регистра 321 определяют как выходной вывод. При выполнении операции 1012 логическое устройство 330 управления считывает информационные биты, осуществляя доступ к буферному запоминающему устройству 46-10 из Фиг.8. При выполнении операции 1013 логическое устройство 330 управления проверяет, является ли значение отсчета "отсчет1" равным NW, для определения того, является ли сдвиговый регистр 321 полностью заполненным. Если значение отсчета "отсчет1" равно NW, то при выполнении операции 1014 логическое устройство 330 управления устанавливает значение отсчета "отсчет1" равным 0. Если же значение отсчета "отсчет1" не равно NW, то при выполнении операции 1015 логическое устройство 330 управления увеличивает значение отсчета "отсчет1" на 1. После выполнения операции 1014 логическое устройство 330 управления при выполнении операции 1016 инвертирует сигнал "выбор1". То есть логическое устройство 330 управления преобразует сигнал "выбор1", равный "1", в сигнал "выбор1", равный "0", а сигнал "выбор1", равный "0", в сигнал "выбор1", равный "1", путем инверсии сигнала "выбор1". Посредством операции 1016 изменяют направление ввода-вывода и направление сдвига информационных битов. После операции 1016 или после операции 1015 выполняют операцию 1017, при которой логическое устройство 330 управления записывает информационные биты, полученные из буферного запоминающего устройства 46-10, в сдвиговый регистр 321. После выполнения операции 1017 логическое устройство 330 управления возвращается к выполнению операции 1012, обеспечивая многократное выполнение вышеуказанной операции.

На Фиг.11 изображена временная диаграмма, на которой показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой высокоскоростным буферным запоминающим устройством 260 из Фиг.9, согласно варианту осуществления настоящего изобретения. Со ссылкой на Фиг.11, высокоскоростное буферное запоминающее устройство 260 осуществляет доступ к информационным битам, запомненным в различных местах буферного запоминающего устройства 46-10. В этом примере высокоскоростное буферное запоминающее устройство 260 осуществляет доступ к информационным битам данные1, данные2 и данные3, запомненным в трех адресах буферного запоминающего устройства 46-10. При одновременном вводе всех трех информационных битов данные1, данные2 и данные3 в высокоскоростное буферное запоминающее устройство 260 за один тактовый импульс устройства турбодекодирования вычислительные устройства 211-213 блока 210 вычисления дельта-метрики одновременно выполняют операцию вычисления дельта-метрики. Информационный бит данные1 (М бит) относится к систематическому коду (М/3 бит) + коду № 1 четности (М/3 бит) + коду № 2 четности (М/3 бит), а данные данные2 и данные3 также равны по объему данным данные1.

Второй вариант осуществления изобретения

На блок-схеме из Фиг.12 показан другой пример конструкции высокоскоростного буферного запоминающего устройства 260, изображенного на Фиг.8, согласно второму варианту осуществления настоящего изобретения. На чертеже показана конструкция высокоскоростного буферного запоминающего устройства 260 для того варианта, когда количество окон N=2, то есть когда бета имеет два окна.

Со ссылкой на Фиг.12, высокоскоростное буферное запоминающее устройство 260 состоит из одного однонаправленного сдвигового регистра 410, N=2 двунаправленных сдвиговых регистров 421 и 422, логического устройства 430 управления, демультиплексоров (ДМП) 441 и 442, и мультиплексоров (МП) 451 и 452.

Сдвиговый регистр 410 имеет 2NW=4W областей памяти (длину) и содержит входной вывод, служащий для ввода данных, и выходной вывод, служащий для вывода данных. Сдвиговый регистр 410 осуществляет последовательный прием битов входных данных из буферного запоминающего устройства 46-10 через входной вывод в соответствии с тактовой частотой устройства турбодекодирования и сдвиг принятых битов входных данных слева (сторона A) направо (сторона B). После того как сформированы потоки битов данных первой длины (4W), сдвиговый регистр 410 осуществляет последовательный вывод сформированных потоков битов данных первой длины через выходной вывод. Информационные биты, выведенные из сдвигового регистра 410, подают в устройство 211 вычисления дельта-метрики, соединенное с входным каскадом блока 220 вычисления альфа-метрики.

Каждый из сдвиговых регистров 421 и 422 имеет NW=2W областей памяти и содержит первый вывод и второй вывод, служащие для ввода/вывода данных. Первый вывод представляет собой вывод, расположенный с левой стороны каждого из сдвиговых регистров 421 и 422, а второй вывод представляет собой вывод, расположенный с правой стороны каждого из сдвиговых регистров 421 и 422. Первый вывод и второй вывод могут обеспечивать как вывод данных, так и ввод данных. Количество сдвиговых регистров 421 и 422 определяется количеством окон. Если количество окон N=2, то количество сдвиговых регистров 421 и 422 задают равным 2. Биты входных данных, поступающие из буферного запоминающего устройства 46-10, разделены на группы, каждая из которых состоит из битов и имеет вторую длину (2W), которая равна 1/2 первой длины. Каждый из сдвиговых регистров 421 и 422 осуществляет последовательный прием битов нечетных групп из разделенных групп, поступивших через первый вывод, и их сдвиг слева (сторона A) направо (сторона B), и в том случае, если сформированы потоки битов второй длины, то каждый из сдвиговых регистров 421 и 422 осуществляет последовательный вывод сформированных потоков битов через первый вывод в порядке следования справа налево, который является обратным порядку их следования при вводе. Каждый из сдвиговых регистров 421 и 422 осуществляет последовательный прием битов четных групп из разделенных групп, поступивших через второй вывод, и их сдвиг справа налево, и в том случае, если сформированы потоки битов второй длины, то каждый из сдвиговых регистров 421 и 422 осуществляет последовательный вывод сформированных потоков битов через второй вывод в порядке следования слева направо, который является обратным порядку их следования при вводе.

Между выходным выводом буферного запоминающего устройства 46-10 и сдвиговыми регистрами 421 и 422 расположены демультиплексоры 441 и 442. Между сдвиговыми регистрами 421 и 422 и блоком 210 вычисления дельта-метрики расположены мультиплексоры 451 и 452. Входные выводы демультиплексоров 441 и 442 соединены с выходным выводом буферного запоминающего устройства 46-10, первые выходные выводы демультиплексоров 441 и 442 соединены со вторыми выводами сдвиговых регистров 421 и 422, а вторые выходные выводы демультиплексоров 441 и 442 соединены с первыми выводами сдвиговых регистров 421 и 422. Первые входные выводы мультиплексоров 451 и 452 соединены со вторыми выводами сдвиговых регистров 421 и 422, вторые входные выводы мультиплексоров 451 и 452 соединены с первыми выводами сдвиговых регистров 421 и 422, а выходные выводы мультиплексоров 451 и 452 соединены с устройствами 211-213 вычисления дельта-метрики.

Логическое устройство 430 управления создает сигналы выбора "выбор1" (select1) и "выбор2" (select2) для управления функционированием сдвиговых регистров 421 и 422, демультиплексоров 441 и 442, а также мультиплексоров 451 и 452. Сигналы выбора могут быть охарактеризованы как сигналы, служащие для управления битами входных данных, поступающими из буферного запоминающего устройства 46-10, таким образом, чтобы обеспечить подачу битов входных данных в сдвиговые регистры 421 и 422 в различные моменты времени. Логическое устройство 430 управления определяет, являются ли биты входных данных, поступившие из буферного запоминающего устройства 46-10, битами нечетных групп или битами четных групп из разделенных групп, и подает биты входных данных из буферного запоминающего устройства 46-10 на первые выводы или на вторые выводы сдвиговых регистров 421 и 422 в соответствии с результатом определения.

Например, в том случае, когда биты входных данных являются битами нечетных групп, логическое устройство 430 управления осуществляет вывод сигналов выбора с уровнем, равным "0", или с "низким логическим уровнем", а в том случае, когда биты входных данных являются битами четных групп, логическое устройство 430 управления осуществляет вывод сигналов выбора с уровнем, равным "1", или с "высоким логическим уровнем". В случае вывода сигналов выбора с уровнем, равным "0", демультиплексоры 441 и 442 подают биты входных данных из буферного запоминающего устройства 46-10 на первые выводы сдвиговых регистров 421 и 422. Затем сдвиговые регистры 421 и 422 осуществляют последовательный сдвиг информационных битов, полученных через их первые выводы, слева направо (в направлении направо). Одновременно с этим сдвиговые регистры 421 и 422 снова осуществляют последовательный сдвиг 2W информационных битов, полученных ранее через их вторые выводы, а затем запомненных, слева направо, и осуществляют вывод подвергнутых сдвигу информационных битов через их вторые выводы.

В случае вывода сигналов выбора с уровнем, равным "1", демультиплексоры 441 и 442 подают биты входных данных из буферного запоминающего устройства 46-10 на вторые выводы сдвиговых регистров 421 и 422. Затем сдвиговые регистры 421 и 422 осуществляют последовательный сдвиг информационных битов, полученных через их вторые выводы, справа налево (в направлении налево). Одновременно с этим сдвиговые регистры 421 и 422 снова осуществляют последовательный сдвиг 2W информационных битов, полученных ранее через их первые выводы, а затем запомненных, справа налево, и осуществляют вывод подвергнутых сдвигу информационных битов через их первые выводы.

Информационные биты, выведенные через первые выводы сдвиговых регистров 421 и 422, подают на вторые входные выводы мультиплексоров 451 и 452, а информационные биты, выведенные через вторые выводы сдвиговых регистров 421 и 422, подают на первые входные выводы мультиплексоров 451 и 452. Мультиплексоры 451 и 452 осуществляют мультиплексирование информационных битов, поданных через их первые входные выводы и вторые входные выводы, и осуществляют вывод мультиплексированных информационных битов в соответствующие устройства 211-213 вычисления дельта-метрики.

Со ссылкой на Фиг.8, вычислительные устройства 211-213 первого блока 210 вычисления метрики осуществляют прием битов, поступивших с выхода сдвиговых регистров 410, 421 и 422, и вычисляют соответствующие дельта-метрики. Второй блок 220 вычисления метрики вычисляет альфа-метрику, получая дельта-метрику из вычислительного устройства 211 первого блока 210 вычисления метрики, соответствующего сдвиговому регистру 410. Третий блок 230 вычисления метрики вычисляет бета-метрики, получая дельта-метрики из вычислительных устройств 212 и 213 первого блока 210 вычисления метрики, соответствующих сдвиговым регистрам 421 и 422. Вычислительные устройства 241-243 четвертого блока 240 вычисления метрики вычисляют значения ЛОП, соответствующие сдвиговым регистрам 410, 421 и 422, получая альфа-метрику и результат мультиплексирования бета-метрик, полученный посредством мультиплексора 233. Вычитающие устройства 251-253 блока 250 вычитания вычитают выходной сигнал сдвигового регистра 410 из соответствующих значений ЛОП и осуществляют вывод результатов вычитания для их перемежения и обращенного перемежения.

На схеме последовательности операций из Фиг.13 показан пример операций управления, выполняемых логическим устройством 430 управления из Фиг.12, согласно варианту осуществления настоящего изобретения. В частности, на чертеже показана последовательность операций управления, в которой логическое устройство 430 управления осуществляет управление двунаправленными сдвиговыми регистрами 421 и 422 для β-метрики, демультиплексорами 441 и 442, соединенными с входами и с выходами сдвиговых регистров 421 и 422, а также мультиплексорами 451 и 452.

На Фиг.13 операции 1111-1117 представляют собой последовательность операций управления сдвиговым регистром 421, демультиплексором 441 и мультиплексором 451. Операции 1121-1127 представляют собой последовательность операций управления сдвиговым регистром 422, демультиплексором 442 и мультиплексором 452. Поскольку соответствующие последовательности операций являются идентичными по выполняемым операциям, за исключением начальных моментов времени и наименований используемых сигналов, то для простоты ниже приведено описание только лишь последовательности операций 1111-1117. Для обеспечения выполнения этих операций управления логическое устройство 430 управления содержит счетчики, соответствующие сдвиговым регистрам 421 и 422. Для выполнения операции подсчета инициализацию счетчиков осуществляют в различные моменты времени с заданным смещением, равным W. Инициализацию счетчика № 1, соответствующего сдвиговому регистру 421, осуществляют в момент времени T=0, а инициализацию счетчика № 2, соответствующего сдвиговому регистру 422, осуществляют в момент времени T=Wt. Здесь символом t обозначено время, то есть длительность единичного тактового импульса.

Со ссылкой на Фиг.13, при выполнении операции 1111 логическое устройство 430 управления осуществляет инициализацию сдвигового регистра 421. При выполнении операции инициализации исходное значение отсчета счетчика №1 устанавливают равным отсчет1=0, а исходное состояние сигнала выбора "выбор1" устанавливают равным выбор1=0. Кроме того, левый (сторона A) вывод сдвигового регистра 421 определяют как входной вывод, а правый (сторона B) вывод сдвигового регистра 421 определяют как выходной вывод. При выполнении операции 1112 логическое устройство 430 управления считывает информационные биты, осуществляя доступ к буферному запоминающему устройству 46-10 из Фиг.8. При выполнении операции 1113 логическое устройство 430 управления проверяет, является ли значение отсчета "отсчет1" равным 2W, для определения того, является ли сдвиговый регистр 421 полностью заполненным. Если значение отсчета "отсчет1" равно 2W, то при выполнении операции 1114 логическое устройство 430 управления устанавливает значение отсчета "отсчет1" равным 0. Если же значение отсчета "отсчет1" не равно 2W, то при выполнении операции 1115 логическое устройство 430 управления увеличивает значение отсчета "отсчет1" на 1. После выполнения операции 1114 логическое устройство 430 управления при выполнении операции 1116 инвертирует сигнал "выбор1". То есть логическое устройство 430 управления преобразует сигнал "выбор1", равный "1", в сигнал "выбор1", равный "0", а сигнал "выбор1", равный "0", в сигнал "выбор1", равный "1", путем инверсии сигнала "выбор1". Посредством операции 1116 изменяют направление ввода/вывода и направление сдвига информационных битов. После операции 1116 или после операции 1115 выполняют операцию 1117, при которой логическое устройство 430 управления записывает информационные биты, полученные из буферного запоминающего устройства 46-10, в сдвиговый регистр 421. После выполнения операции 1117 логическое устройство 430 управления возвращается к выполнению операции 1112, обеспечивая многократное выполнение вышеуказанной операции.

На блок-схеме из Фиг.14 показан пример последовательности обработки данных сдвиговым регистром 410 для альфа-метрики, изображенным на Фиг.12. Со ссылкой на Фиг.14, сдвиговый регистр 410 осуществляет последовательный прием информационных битов из буферного запоминающего устройства 46-10, показанного на Фиг.8, и их сдвиг слева направо. На чертеже "сторона А" обозначает место ввода информационных битов, а "сторона B" представляет собой место вывода информационных битов. При подаче информационных битов на вход сдвигового регистра 410 вывод битов входных данных осуществляют с задержкой на 4W. Сдвиговый регистр 410 попросту имеет структуру обратного магазинного типа (FIFO).

На Фиг.15 показана последовательность обработки данных сдвиговым регистром 421 для бета-метрики, изображенным на Фиг.12. Эта последовательность обработки данных идентична последовательности обработки данных другим сдвиговым регистром 422 для бета-метрики.

Со ссылкой на Фиг.15, сдвиговый регистр 421 вводит задержку данных, последовательно считываемых из буферного запоминающего устройства 46-10, на заданное время для того, чтобы момент времени вывода данных совпадал с моментом времени, желательным для устройства турбодекодирования. Сдвиговый регистр 421 осуществляет последовательное запоминание битов входных данных. Если сдвиговый регистр 421 заполнен, то сдвиговый регистр 421 осуществляет вывод предшествующих битов данных при одновременном перемещении запомненных битов данных в направлении, противоположном направлению ввода, и подает биты выходных данных в устройство 212 вычисления дельта-метрики. В результате, на противоположной стороне сдвигового регистра 421 возникает пустое пространство. По мере ввода новых информационных битов вновь происходит заполнение этого пустого пространства в направлении, противоположном направлению ввода, в котором был осуществлен ввод предшествующих битов данных. Таким способом обеспечивают повторное выполнение операций ввода данных в сдвиговый регистр 421 и их вывода из него, и в результате этого подачу информационных битов в соответствующее устройство 212 вычисления дельта-метрики осуществляют в соответствии с потоком данных, изображенным на чертеже.

На блок-схеме из Фиг.16 показан пример синхронизации операции доступа к буферному запоминающему устройству, выполняемой высокоскоростным буферным запоминающим устройством 260 из Фиг.12, согласно варианту осуществления настоящего изобретения. На Фиг.16 условным обозначением "ввод дельта-блока для альфа" обозначена процедура ввода/вывода информационных битов для однонаправленного сдвигового регистра 410 из Фиг.12, где "сторона A" обозначает вводимые биты данных, а "сторона B" обозначает выводимые биты данных. Кроме того, условным обозначением "ввод дельта-блока для бета1" обозначена процедура ввода/вывода информационных битов для двунаправленного сдвигового регистра 421, а условным обозначением "ввод дельта-блока для бета2" обозначена процедура ввода/вывода информационных битов для двунаправленного сдвигового регистра 422. В условных обозначениях "ввод дельта-блока для бета1" и "ввод дельта-блока для бета2" наименованиями "сторона A вход" и "сторона А выход" обозначены те информационные биты, ввод-вывод которых осуществляют через первый вывод, а наименованиями "сторона B вход" и "сторона B выход" обозначены те информационные биты, ввод/вывод которых осуществляют через второй вывод. Наименованиями "выбор1" и "выбор2" обозначены управляющие сигналы, генерация которых была осуществлена логическим устройством 430 управления, и которые были затем поданы в сдвиговые регистры 421 и 422. Наименованиями "вывод альфа", "вывод бета1" и " вывод бета2" обозначены выводимые результирующие метрики, а вычисление значения ЛОП осуществляют с использованием этих выведенных метрик.

В части "ввод дельта-блока для бета1" ввод информационных битов на начальном этапе осуществляют через сторону А. Ввод информационных битов производят в следующем порядке: a, b, c, d..., h, а вывод информационных битов со стороны А осуществляют по истечении промежутка времени, равного 2W, прошедшего с начального момента времени. Во время выполнения операции вывода со стороны A выполняют операцию ввода со стороны B. Это означает, что сдвиговый регистр 421 работает таким образом, что изменяет направление выполняемого им сдвига. По истечении следующего промежутка времени, равного 2W, когда со стороны А снова выполняют операцию ввода, осуществляя ввод q-того информационного бита, со стороны B производят вывод p-того информационного бита.

Функционирование части "ввод дельта-блока для бета2" осуществляют тем же самым способом, что и функционирование части "ввод дельта-блока для бета1". Однако поскольку время инициализации сдвигового регистра 422 отличается от времени инициализации сдвигового регистра 421, то ввод/вывод информационных битов выполняют в иные периоды времени.

В части "ввод дельта-блока для альфа" со стороны А выполняют только операцию ввода, а со стороны B выполняют только операцию вывода. Вывод первого полученного a-того информационного бита осуществляют по истечении промежутка времени, равного 4W, прошедшего с начального момента времени.