Изобретение относится к системам передачи информации по каналам связи и может быть использовано в устройствах декодирования по алгоритму Витерби.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения его диагностики.

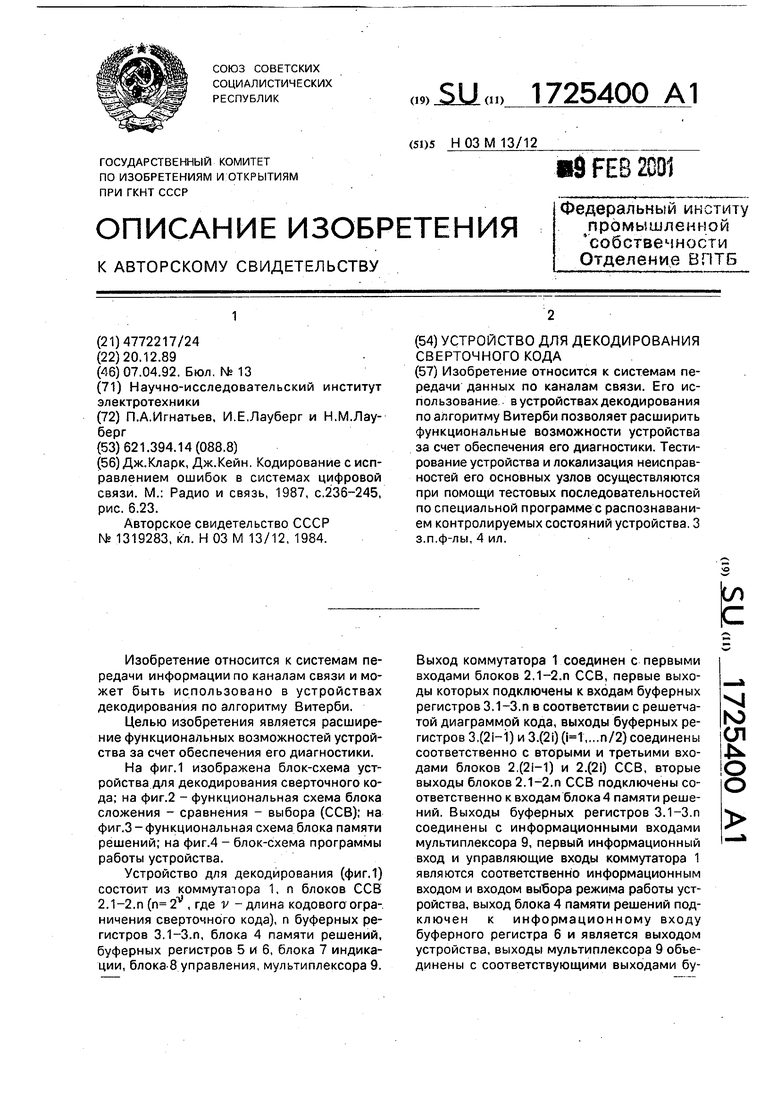

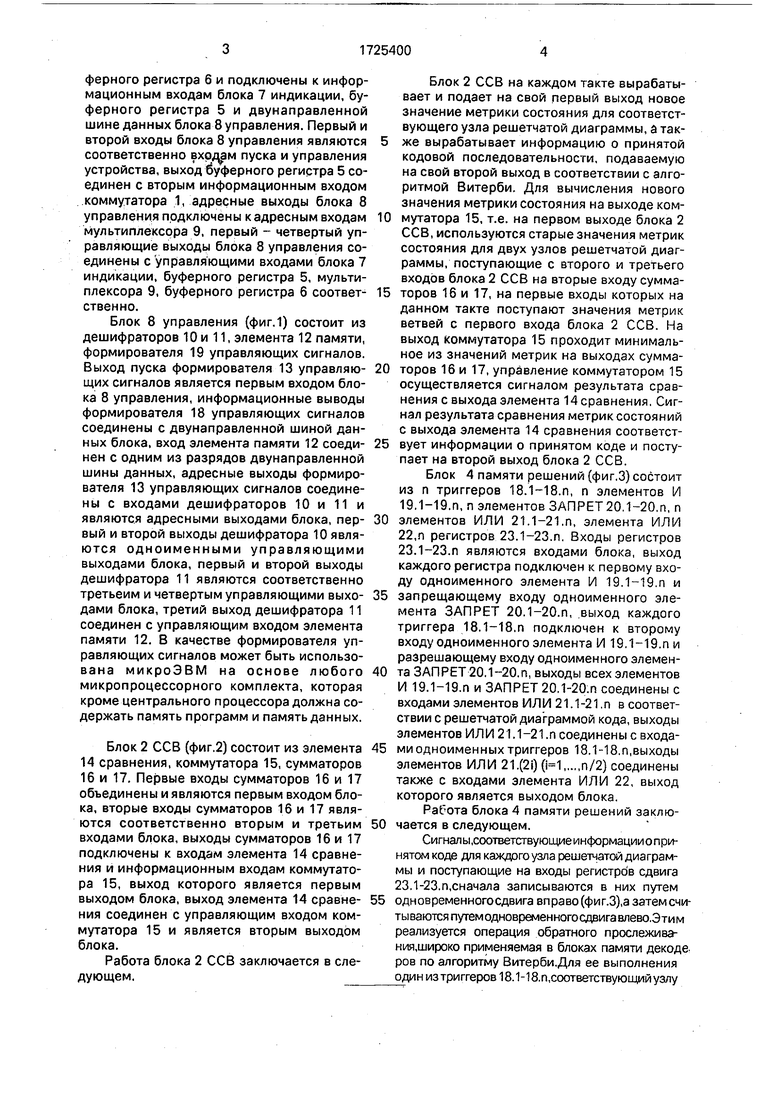

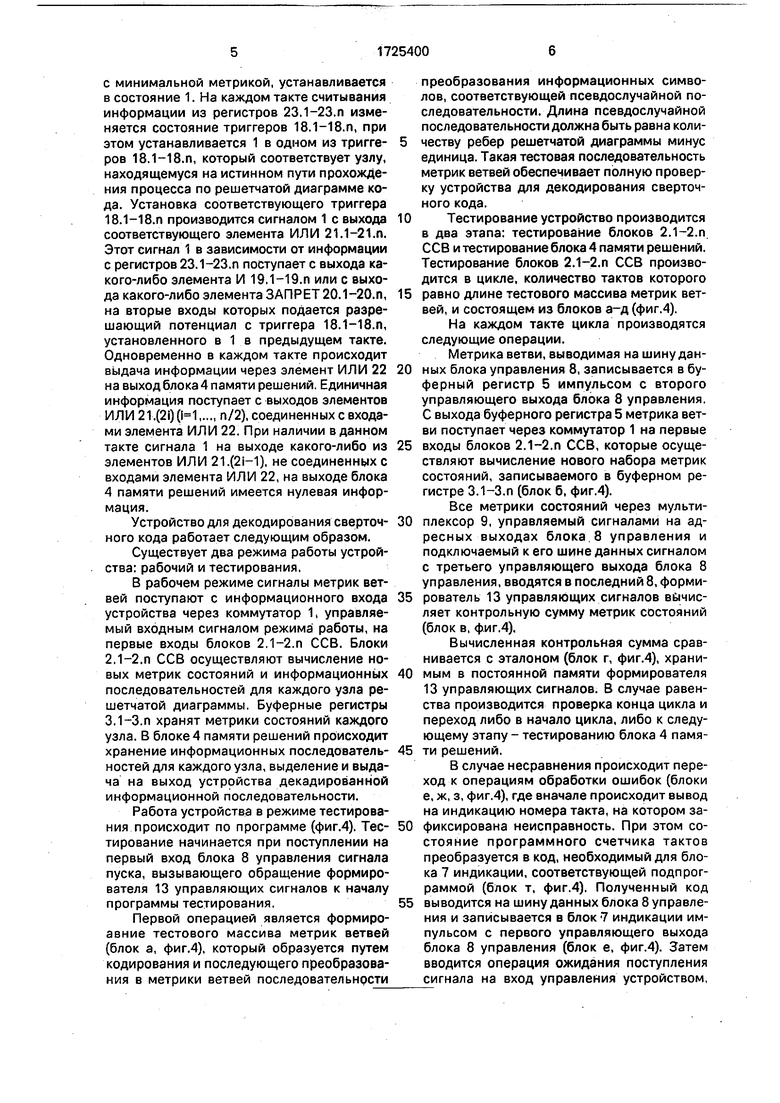

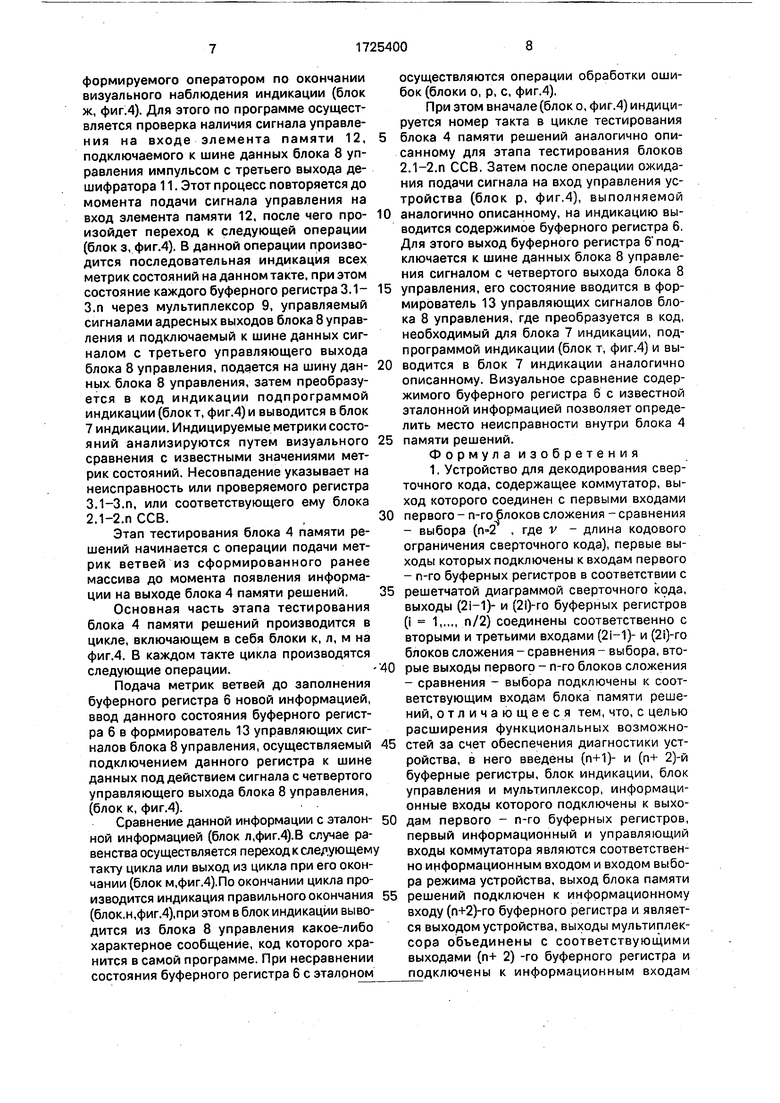

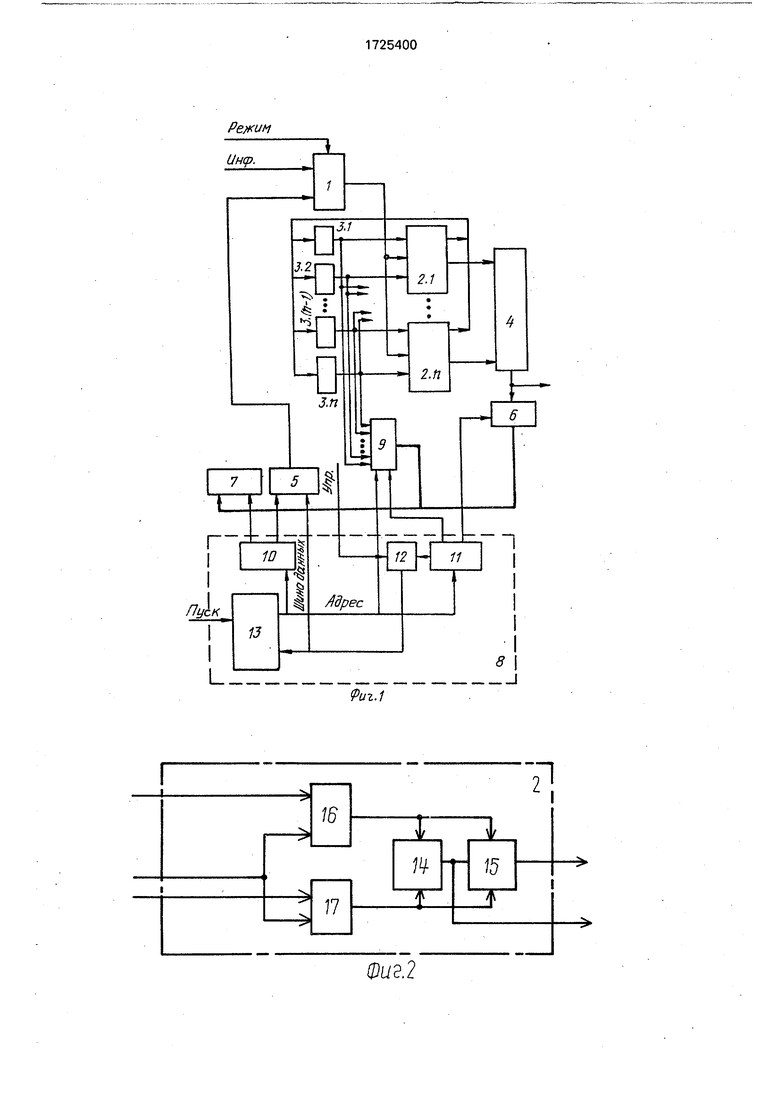

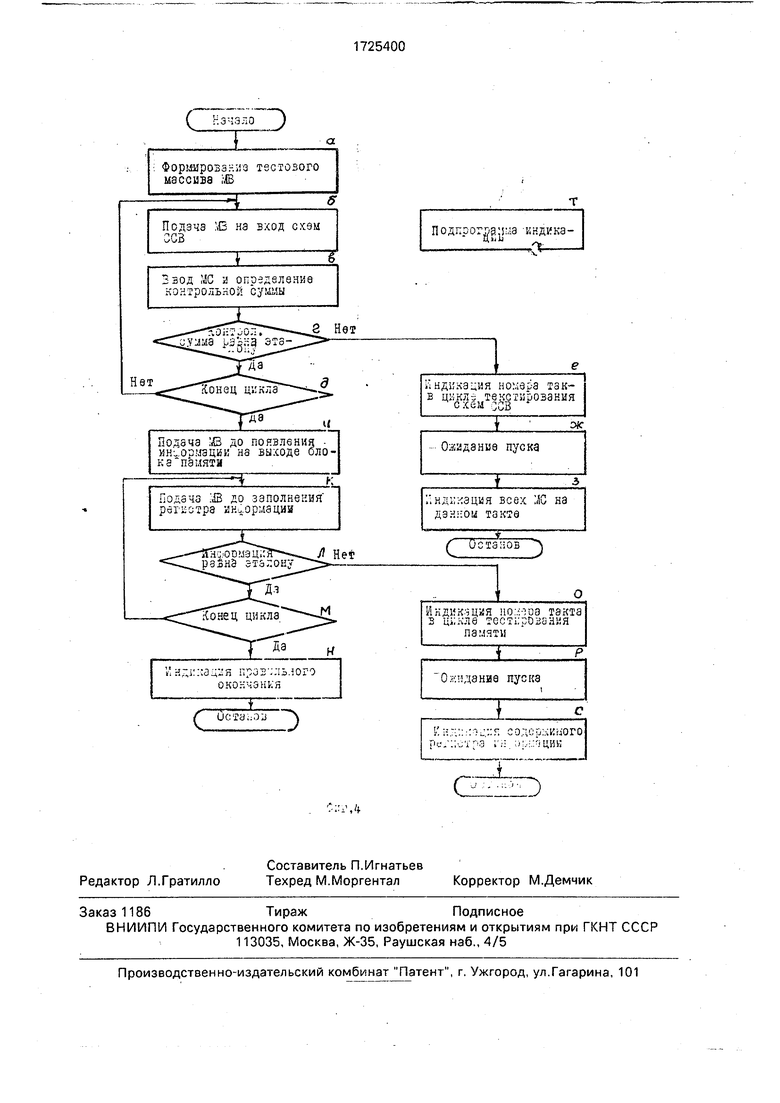

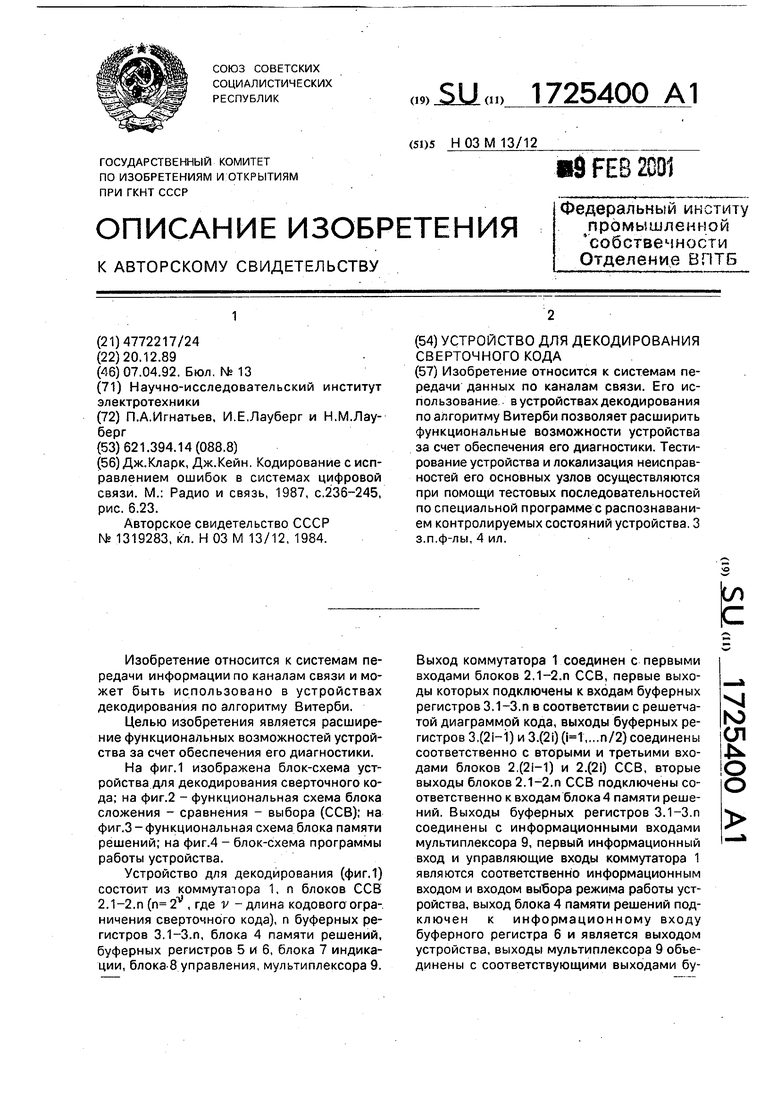

На фиг.1 изображена блок-схема устройства для декодирования сверточного кода; на фиг.2 - функциональная схема блока сложения - сравнения - выбора (ССВ); на фиг.З-функциональная схема блока памяти решений; на фиг.4 - блок-схема программы работы устройства.

Устройство для декодирования (фиг.1) состоит из коммутатора 1, п блоков ССВ 2.1-2.П ( , где v -длина кодового ограничения сверточного кода), п буферных регистров 3.1-З.п, блока 4 памяти решений, буферных регистров 5 и 6, блока 7 индикации, блока-8 управления, мультиплексора 9.

Выход коммутатора 1 соединен с первыми входами блоков 2.1-2.П ССВ, первые выходы которых подключены к входам буферных регистров 3.1-З.п в соответствии с решетчатой диаграммой кода, выходы буферных регистров 3.(2Ы) и 3.(2i) (,...n/2) соединены соответственно с вторыми и третьими входами блоков 2.(21-1) и 2.(2i) ССВ, вторые выходы блоков 2.1-2.П ССВ подключены соответственно к входам блока4 памяти решений. Выходы буферных регистров 3.1-З.п соединены с информационными входами мультиплексора 9, первый информационный вход и управляющие входы коммутатора 1 являются соответственно информационным входом и входом выбора режима работы устройства, выход блока 4 памяти решений под- ключен к информационному входу буферного регистра 6 и является выходом устройства, выходы мультиплексора 9 объединены с соответствующими выходами буVIN3 СЛ 1 О О

ферного регистра б и подключены к информационным входам блока 7 индикации, буферного регистра 5 и двунаправленной шине данных блока 8 управления. Первый и второй входы блока 8 управления являются соответственно входам пуска и управления устройства, выход буферного регистра 5 соединен с вторым информационным входом коммутатора 1, адресные выходы блока 8 управления подключены к адресным входам мультиплексора 9, первый - четвертый управляющие выходы блока 8 управления соединены с управляющими входами блока 7 индикации, буферного регистра 5, мультиплексора 9, буферного регистра б соответственно.

Блок 8 управления (фиг.1) состоит из дешифраторов 10 и 11, элемента 12 памяти, формирователя 19 управляющих сигналов. Выход пуска формирователя 13 управляющих сигналов является первым входом блока 8 управления, информационные выводы формирователя 18 управляющих сигналов соединены с двунаправленной шиной данных блока, вход элемента памяти 12 соединен с одним из разрядов двунаправленной шины данных, адресные выходы формирователя 13 управляющих сигналов соединены с входами дешифраторов 10 и 11 и являются адресными выходами блока, первый и второй выходы дешифратора 10 являются одноименными управляющими выходами блока, первый и второй выходы дешифратора 11 являются соответственно третьеим и четвертым управляющими выходами блока, третий выход дешифратора 11 соединен с управляющим входом элемента памяти 12. В качестве формирователя управляющих сигналов может быть использована микроЭВМ на основе любого микропроцессорного комплекта, которая кроме центрального процессора должна содержать память программ и память данных.

Блок 2 ССВ (фиг.2) состоит из элемента 14 сравнения, коммутатора 15, сумматоров 16 и 17. Первые входы сумматоров 16 и 17 объединены и являются первым входом блока, вторые входы сумматоров 16 и 17 являются соответственно вторым и третьим входами блока, выходы сумматоров 16 и 17 подключены к входам элемента 14 сравнения и информационным входам коммутатора 15, выход которого является первым выходом блока, выход элемента 14 сравнения соединен с управляющим входом коммутатора 15 и является вторым выходом блока.

Работа блока 2 ССВ заключается в следующем.

Блок 2 ССВ на каждом такте вырабатывает и подает на свой первый выход новое значение метрики состояния для соответствующего узла решетчатой диаграммы, а также вырабатывает информацию о принятой кодовой последовательности, подаваемую на свой второй выход в соответствии с алго- ритмой Витерби. Для вычисления нового значения метрики состояния на выходе ком0 мутатора 15, т.е. на первом выходе блока 2 ССВ, используются старые значения метрик состояния для двух узлов решетчатой диаграммы, поступающие с второго и третьего входов блока 2 ССВ на вторые входу сумма5 торов 16 и 17, на первые входы которых на данном такте поступают значения метрик ветвей с первого входа блока 2 ССВ. На выход коммутатора 15 проходит минимальное из значений метрик на выходах сумма0 торов 16 и 17, управление коммутатором 15 осуществляется сигналом результата сравнения с выхода элемента 14 сравнения. Сигнал результата сравнения метрик состояний с выхода элемента 14 сравнения соответст5 вует информации о принятом коде и поступает на второй выход блока 2 ССВ.

Блок 4 памяти решений (фиг.З) состоит из п триггеров 18.1-18.n, n элементов И 19.1-19.п,п элементов ЗАПРЕТ 20,1-20.П, п

0 элементов ИЛИ 21.1-21.п, элемента ИЛИ 22,п регистров 23.1-23.п. Входы регистров 23.1-23.п являются входами блока, выход каждого регистра подключен к первому входу одноименного элемента И 19.1-19.п и

5 запрещающему входу одноименного элемента ЗАПРЕТ 20.1-20.П, .выход каждого триггера 18.1-18.п подключен к второму входу одноименного элемента И 19.1-19.п и разрешающему входу одноименного элемен0 та ЗАПРЕТ 20.1-20.П, выходы всех элементов И 19.1-19.П и ЗАПРЕТ 20.1-20.П соединены с входами элементов ИЛИ 21.1-21.п в соответствии с решетчатой диаграммой кода, выходы элементов ИЛИ 21.1-21.п соединены с входа5 ми одноименных триггеров 18.1-18.п,выходы

элементов ИЛИ 21.(2i) (i 1n/2) соединены

также с входами элемента ИЛИ 22, выход которого является выходом блока.

Работа блока 4 памяти решений заклю0 чается в следующем.

Сигнал ы .соответствующие информации о принятом коде для каждого узла решетчатой диаграммы и поступающие на входы регистров сдвига 23.1-23.п,сначала записываются в них путем

5 одновременного сдвига вправо (фиг.З).а затем считываются путем одновременногосдвига влево.Эти м реализуется операция обратного прослежива- ния,широко применяемая в блоках памяти декоде. ров по алгоритму Витерби.Для ее выполнения один из триггеров 18.1-18.п,соответствующийузлу

с минимальной метрикой, устанавливается в состояние 1. На каждом такте считывания информации из регистров 23.1-23.П изменяется состояние триггеров 18.1-18.П, при этом устанавливается 1 в одном из триггеров 18.1-18.п, который соответствует узлу, находящемуся на истинном пути прохождения процесса по решетчатой диаграмме кода. Установка соответствующего триггера 18.1-18.п производится сигналом 1 с выхода соответствующего элемента ИЛИ 21.1-21.п. Этот сигнал 1 в зависимости от информации с регистров 23.1-23.п поступает с выхода какого-либо элемента И 19.1-19.П или с выхода какого-либо элемента ЗАПРЕТ 20.1-20.П, на вторые входы которых подается разрешающий потенциал с триггера 18.1-18.п, установленного в 1 в предыдущем такте. Одновременно в каждом такте происходит выдача информации через элемент ИЛИ 22 на выход блока 4 памяти решений. Единичная информация поступает с выходов элементов ИЛИ21-.(21)(1 1п/2), соединенных с входами элемента ИЛИ 22. При наличии в данном такте сигнала 1 на выходе какого-либо из элементов ИЛИ 21.(21-1), не соединенных с входами элемента ИЛИ 22, на выходе блока 4 памяти решений имеется нулевая информация.

Устройство для декодирования сверточ- ного кода работает следующим образом.

Существует два режима работы устройства: рабочий и тестирования.

В рабочем режиме сигналы метрик ветвей поступают с информационного входа устройства через коммутатор 1, управляемый входным сигналом режима работы, на первые входы блоков 2.1-2.П ССВ. Блоки 2.1-2.П ССВ осуществляют вычисление новых метрик состояний и информационных последовательностей для каждого узла решетчатой диаграммы. Буферные регистры 3.1-З.п хранят метрики состояний каждого узла. В блоке 4 памяти решений происходит хранение информационных последовательностей для каждого узла, выделение и выдача на выход устройства декадированной информационной последовательности.

Работа устройства в режиме тестирования происходит по программе (фиг.4). Тестирование начинается при поступлении на первый вход блока 8 управления сигнала пуска, вызывающего обращение формирователя 13 управляющих сигналов к началу программы тестирования.

Первой операцией является формирование тестового массива метрик ветвей (блок а, фиг.4), который образуется путем кодирования и последующего преобразования в метрики ветвей последовательнрсти

преобразования информационных символов, соответствующей псевдослучайной последовательности. Длина псевдослучайной последовательности должна быть равна количеству ребер решетчатой диаграммы минус единица. Такая тестовая последовательность метрик ветвей обеспечивает полную проверку устройства для декодирования сверточ- ного кода.

0 Тестирование устройство производится в два этапа: тестирование блоков 2.1-2.П ССВ и тестирование блока 4 памяти решений. Тестирование блоков 2.1-2.П ССВ производится в цикле, количество тактов которого

5 равно длине тестового массива метрик ветвей, и состоящем из блоков а-д (фиг.4).

На каждом такте цикла производятся следующие операции.

Метрика ветви, выводимая на шину дан0 ных блока управления 8, записывается в буферный регистр 5 импульсом с второго управляющего выхода блока 8 управления. С выхода буферного регистра 5 метрика ветви поступает через коммутатор 1 на первые

5 входы блоков 2.1-2.П ССВ, которые осуществляют вычисление нового набора метрик состояний, записываемого в буферном регистре 3.1-З.п (блок б, фиг.4).

Все метрики состояний через мульти0 плексор 9, управляемый сигналами на адресных выходах блока 8 управления и подключаемый к его шине данных сигналом с третьего управляющего выхода блока 8 управления, вводятся в последний 8, форми5 рователь 13 управляющих сигналов вычисляет контрольную сумму метрик состояний (блок в, ф.иг.4).

Вычисленная контрольная сумма сравнивается с эталоном (блок г, фиг.4), храни0 мым в постоянной памяти формирователя 13 управляющих сигналов. В случае равенства производится проверка конца цикла и переход либо в начало цикла, либо к следующему этапу - тестированию блока 4 памя5 ти решений.

В случае несравнения происходит переход к операциям обработки ошибок (блоки е, ж, з, фиг.4), где вначале происходит вывод на индикацию номера такта, на котором за0 фиксирована неисправность. При этом состояние программного счетчика тактов преобразуется в код, необходимый для блока 7 индикации, соответствующей подпрограммой (блок т, фиг.4). Полученный код

5 выводится на шину данных блока 8 управления и записывается в блок 7 индикации импульсом с первого управляющего выхода блока 8 управления (блок е, фиг.4). Затем вводится операция ожидания поступления сигнала на вход управления устройством,

формируемого оператором по окончании визуального наблюдения индикации (блок ж, фиг.4). Для этого по программе осуществляется проверка наличия сигнала управле- ния на входе элемента памяти 12, подключаемого к шине данных блока 8 управления импульсом с третьего выхода дешифратора 11. Этот процесс повторяется до момента подачи сигнала управления на вход элемента памяти 12, после чего про- изойдет переход к следующей операции (блок з, фиг.4). В данной операции производится последовательная индикация всех метрик состояний на данном такте, при этом состояние каждого буферного регистра 3.1- З.п через мультиплексор 9, управляемый сигналами адресных выходов блока 8 управления и подключаемый к шине данных сигналом с третьего управляющего выхода блока 8 управления, подается на шину дан- ных блока 8 управления, затем преобразуется в код индикации подпрограммой индикации (блок т, фиг.4) и выводится в блок 7 индикации. Индицируемые метрики состо- яний анализируются путем визуального сравнения с известными значениями метрик состояний. Несовпадение указывает на неисправность или проверяемого регистра 3.1-З.п, или соответствующего ему блока 2.1-2.П ССВ.,

Этап тестирования блока 4 памяти решений начинается с операции подачи метрик ветвей из сформированного ранее массива до момента появления информации на выходе блока 4 памяти решений.

Основная часть этапа тестирования блока 4 памяти решений производится в цикле, включающем в себя блоки к, л, м на фиг.4. В каждом такте цикла производятся следующие операции.

Подача метрик ветвей до заполнения буферного регистра 6 новой информацией, ввод данного состояния буферного регистра 6 в формирователь 13 управляющих сигналов блока 8 управления, осуществляемый подключением данного регистра к шине данных под действием сигнала с четвертого управляющего выхода блока 8 управления, (блок к, фиг.4).

Сравнение данной информации с эталон- ной информацией (блок л,фиг.4).В случае равенства осуществляется переход к следующем такту цикла или выход из цикла при его окончании (блок м,фиг.4).По окончании цикла производится индикация правильного окончания (блок.н,фиг.4),при этом в блок индикации выводится из блока 8 управления какое-либо характерное сообщение, код которого хранится в самой программе. При несравнении состояния буферного регистра 6 с эталоном

осуществляются операции обработки ошибок (блоки о, р, с, фиг.4).

При этом вначале (блок о, фиг.4) индицируется номер такта в цикле тестирования блока 4 памяти решений аналогично описанному для этапа тестирования блоков 2.1-2.П ССВ. Затем после операции ожидания подачи сигнала на вход управления устройства (блок р, фиг.4), выполняемой аналогично описанному, на индикацию выводится содержимое буферного регистра 6. Для этого выход буферного регистра 6 подключается к шине данных блока 8 управления сигналом с четвертого выхода блока 8 управления, его состояние вводится в формирователь 13 управляющих сигналов блока 8 управления/где преобразуется в код, необходимый для блока 7 индикации, подпрограммой индикации (блок т, фиг.4) и выводится в блок 7 индикации аналогично описанному. Визуальное сравнение содержимого буферного регистра 6 с известной эталонной информацией позволяет определить место неисправности внутри блока 4 памяти решений.

Формула изобретения 1, Устройство для декодирования свер- точного кода, содержащее коммутатор, выход которого соединен с первыми входами первого - п-го блоков сложения - сравнения

-выбора ( , где v - длина кодового ограничения сверточного кода), первые выходы которых подключены к входам первого

-n-го буферных регистров в соответствии с решетчатой диаграммой сверточного кода, выходы (21-1)- и (2i)-ro буферных регистров (i 1,.,., п/2) соединены соответственно с вторыми и третьими входами (2Ы)- и (2i)-ro блоков сложения - сравнения - выбора, вторые выходы первого - n-го блоков сложения

-сравнения - выбора подключены к соответствующим входам блока памяти решений, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения диагностики устройства, в него введены (п+1)- и (п+ 2)-й буферные регистры, блок индикации, блок управления и мультиплексор, информационные входы которого подключены к выходам первого - n-го буферных регистров, первый информационный и управляющий входы коммутатора являются соответственно информационным входом и входом выбора режима устройства, выход блока памяти решений подключен к информационному входу (п+2)-го буферного регистра и является выходом устройства, выходы мультиплексора объединены с соответствующими выходами (п+ 2) -го буферного регистра и подключены к информационным входам

блока индикации и (п+1)-го буферного регистра и к двунаправленной шине данных блока управления, первый и второй входы которого являются соответственно входами пуска и управления устройства, выход (п+1)- го буферного регистра соединен с вторым информационным входом коммутатора, адресные выходы блока управления подключены к адресным входам мультиплексора, первый - четвертый управляющие выходы блока управления соединены с управляющими входами соответственно блока индикации, (п+1)-го буферного регистра, мультиплексора и (п+2)-го буферного регистра.

2. Устройство поп.1,отличающее- с я тем, что блок управления содержит первый и второй дешифраторы, элемент памяти и формирователь управляющих сигналов, вход пуска которого является первым входом блока, информационные выводы формирователя управляющих сигналов соединены с двунаправленной шиной данных блока, вход элемента памяти является вторым входом блока, выход элемента памяти соединен с соответствующим разрядом шины данных блока, адресные выходы фор- мирователя управляющих сигналов соеди- нены с входами первого и второго дешифраторов и являются адресными выходами блока, первый и второй выходы первого дешифратора являются одноименными управляющими выходами блока, первый и второй выходы второго дешифратора явля- ются соответственно третьим и четвертым управляющими выходами блока, третий выход второго дешифратора соединен с управляющим входом элемента памяти.

3.Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок сложения - сравнения - выбора содержит элемент сравнения, коммутатор и первый и второй сумматоры, первые входы которых объединены и являются первым входом блока, вторые входы первого и второго сумматоров являются соответственно вторым и третьим входами блока, выходы первого и второго сумматоров подключены соответственно к первому и второму входам элемента сравнения и соответственно к первому и второму информационным входам коммутатора, выход которого является первым выходом блока, выход элемента сравнения соединен с управляющим входом коммутатора и является вторым выходом блока.

4.Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок памяти решений содержит первый - n-й триггеры, первый - n-й элементы И, первый - n-й элементы ЗАПРЕТ, первый - (п+1)-й элементы ИЛИ, первый - п-й регистры, входы которых являются соответствующими входами блока, выход каждого регистра подключен к первому входу одноименного элемента И и запрещающему входу одноименного элемента ЗАПРЕТ, выход каждого триггера подключен к второму входу одноименного элемента И и разрешающему входу одноименного элемента ЗАПРЕТ, выходы всех элементов И и ЗАПРЕТ соединены с входами первого - п-го элементов ИЛИ в соответствии с решетчатой диаграммой сверточного кода, выходы первого - п-го элементов ИЛИ соединены с входами одноименных триггеров, выходы (2i)-x элементов ИЛИ (...., п/2) подключены к входам (п+1)-го элемента ИЛИ, выход которого является выходом блока.

0fo.J

( Нзчзло )

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

Изобретение относится к системам передачи данных по каналам связи. Его использование в устройствах декодирования по алгоритму Витерби позволяет расширить функциональные возможности устройства за счет обеспечения его диагностики. Тестирование устройства и локализация неисправностей его основных узлов осуществляются при помощи тестовых последовательностей по специальной программе с распознаванием контролируемых состояний устройства. 3 з.п.ф-лы, 4 ил.

Формирование тестового массива МБ

Подэчз IB на вход схем OGB

Ввод МО и определение контрольной суммы

Подача В до появления - иHL.o2.uaцкк на выходе блока памяти

±

Подача Ж до заполнения регистра информации

V H-i:::aa n провального ококчзккя

Л Сстга;1эи N

Подпрограмма -кндкка- о,.

Ожидание пуска

±

;кд1-;кэция всех X на дэн;:оц такте

Ожидание пуска

К и ;;.:.: т ц:: п содсол-скного pu/:;-j ipa i ;;. .

| Дж.Кларк, Дж.Кейн | |||

| Кодирование с исправлением ошибок в системах цифровой связи | |||

| М.: Радио и связь, 1987, с.236-245, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-07—Публикация

1989-12-20—Подача