Область техники, к которой относится изобретение

Настоящее раскрытие относится к области электронных компонентов.

Более конкретно, настоящее раскрытие относится к интерфейсу управления температурой для такого электронного компонента, как процессор.

Уровень техники

Управление температурой электронных компонентов наглядно показывает продолжающееся борьбу между миниатюризацией компонентов, с одной стороны, и ростом потребления энергии, с другой стороны. Современные микропроцессоры используют изощренные технологические приемы для сбережения потребляемой энергии и сами проводят управляемую приостановку работы, когда температуры достигают определенных тепловых показателей.

Например, один процессор известного уровня техники включает штырек (вывод) для останова синхронизирующих импульсов, который позволяет системе остановить синхронизирующие импульсы процессора по разным причинам. Одним известным применением этого вывода - это обеспечение периодического сигнала на выводе останова синхроимпульсов, заставляющего процессор периодически останавливаться и повторно запускаться (см. патент США № 5.560.001). Такая управляемая приостановка работы синхроимпульсов эффективно снижает рабочую скорость процессора, тем самым, как правило, снижая потребление мощности и температуру.

Кроме того, процессор известного уровня техники может сам иметь тепловые датчики и может сам выполнять инициированную изнутри приостановку работы. Когда инициированная изнутри приостановка работы проводится по соображениям теплоэнергетики, внешний сигнал может быть установлен (выдан) для оповещения системы (см., например, выходной сигнал PROCHOT# процессора Пентиум 4).

Эти механизмы, однако, могут и не обеспечить надлежащего управления и/или возможностей синхронизации для некоторых приложений.

Краткое описание чертежей

Настоящее изобретение иллюстрируется лишь в качестве примера, не ограничивающего объем притязаний, со ссылкой на сопроводительные чертежи.

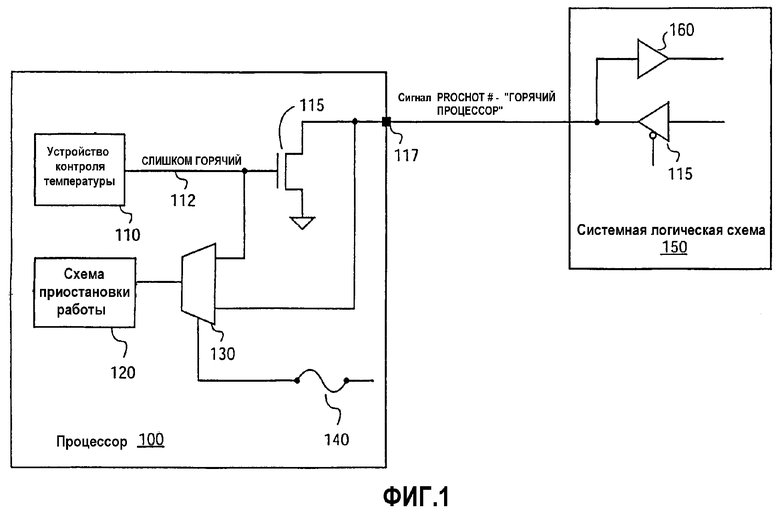

Фиг.1 иллюстрирует одно воплощение системы, имеющей двунаправленный интерфейс для информирования о горячем процессоре.

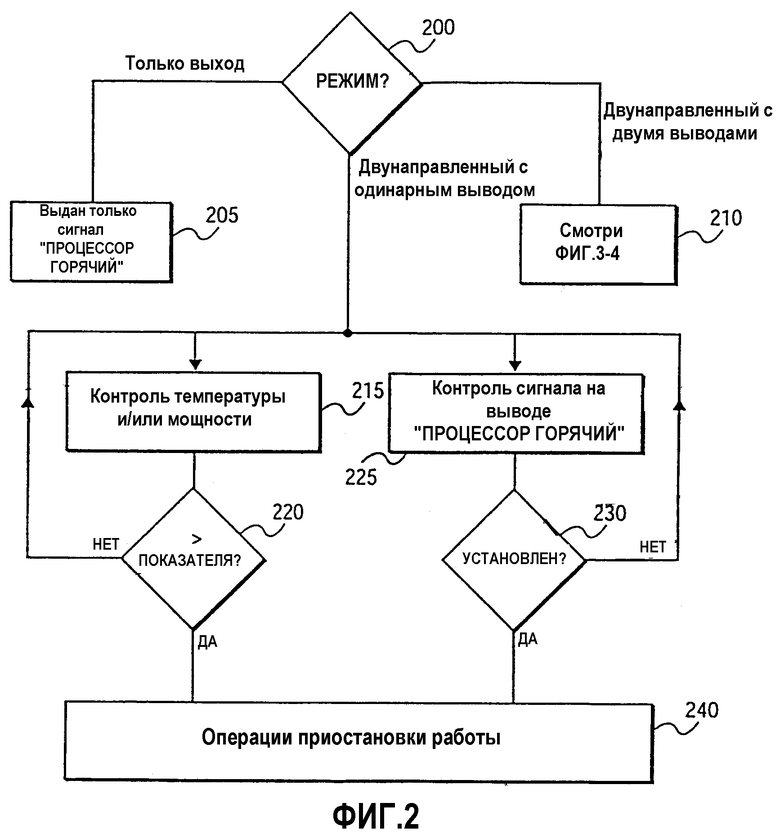

Фиг.2 - блок-схема, иллюстрирующая операции системы, показанной на Фиг.1, согласно одному воплощению.

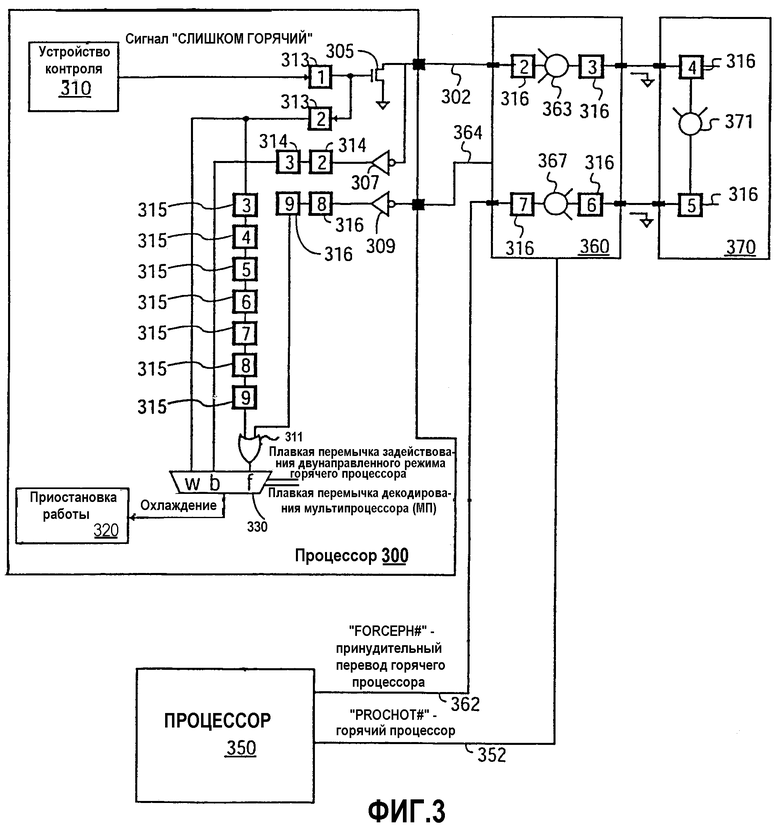

Фиг.3 иллюстрирует одно воплощение многопроцессорной системы, использующей интерфейс для информирования о горячем процессоре.

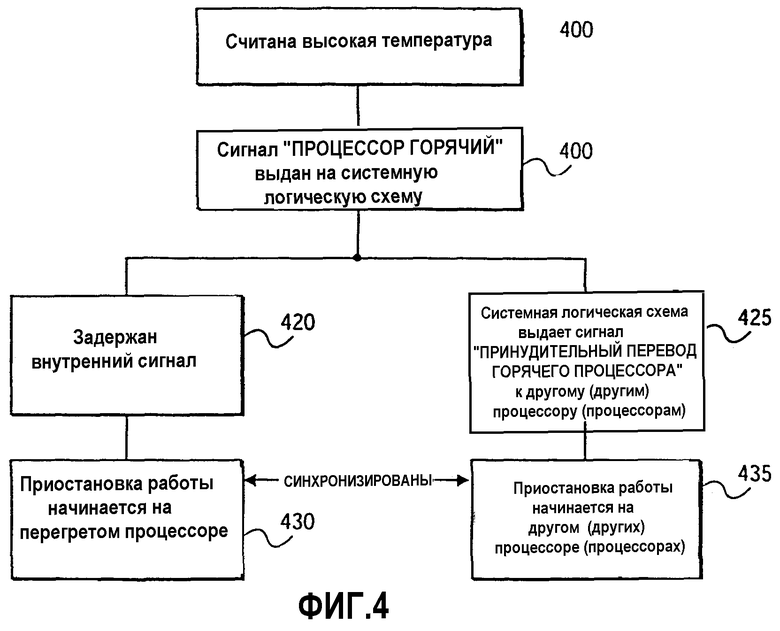

Фиг.4 - блок-схема, иллюстрирующая операции системы, показанной на Фиг.3, согласно одному воплощению.

Подробное описание

Нижеприведенное описание раскрывает технические приемы для интерфейса управления температурой процессора. В нижеприведенном описании приведены многочисленные специфические подробности, такие как логические реализации, тактовые импульсы, наименование сигналов, типы и взаимозависимости компонентов системы, а также выборы логического разбиения/интеграции, для того, чтобы обеспечить более полное понимание настоящего изобретения. Специалистам в данной области техники будет, однако понятно, что изобретение может быть реализовано без таких специфических подробностей. В других примерах управляющие структуры, а также схемы на уровне вентилей не были показаны подробно, чтобы не усложнять описание изобретения.

В одном воплощении предлагается двунаправленный интерфейс сигнала (PROCHOT#) (ПРОЦЕССОР ГОРЯЧИЙ) горячего процессора, чтобы обеспечить как наблюдение за системой, так и управление системой за тепловым состоянием процессора. Такой двунаправленный интерфейс может быть использован, например, в настольных и мобильных системах, где ограниченные возможности управления и наблюдения должны быть компенсированы использованием дополнительных штырьков (выводов). В другом воплощении интерфейс с двумя выводами для сигналов ПРОЦЕССОР ГОРЯЧИЙ и принудительного перевода горячего интерфейса (FORCEPH#) (ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ГОРЯЧЕГО ПРОЦЕССОРА) дает возможность системе как наблюдать, так и управлять установкой механизма приостановки работы.

«Процессор» может быть выполнен в виде одной интегральной схемы в некоторых воплощениях изобретения. В других воплощениях множество интегральных схем могут сообща образовать процессор. В других воплощениях аппаратно-реализованные стандартные программы и стандартные программы системы программного обеспечения (например, стандартные программы двоичного перевода) могут сообща образовать процессор. Множество различных типов интегральных схем и других электронных компонентов могли бы извлечь преимущества от использования таких технических приемов управления температурой. Например, процессор 100 может быть процессором общего назначения (например, микропроцессором) или может быть процессором или устройством специального назначения. Например, цифровые процессоры сигналов, графические процессоры, сетевые процессоры или какого-либо типа компонент специального назначения, которые могут быть использованы в системе, могли бы извлечь преимущества из «видимой» системной и управляемой приостановки работы.

Фиг.1 иллюстрирует один вариант осуществления процессора 100, имеющего двунаправленный интерфейс сигналов горячего процессора (узел 117 интерфейса PROCHOT#). Интерфейсом может быть штырек (вывод), шарик или какой-либо другой тип соединителя или их набор, который может обеспечить, по меньшей мере, один узел интерфейса (интерфейсный узел) к другим компонентам. Процессор 100 включает логическую схему 110 контроля температуры, которая контролирует температуру самого процессора. Большое разнообразие известных или, иначе, доступных технических средств контроля температуры может быть использовано. Например, может быть использована встроенная схема, контролирующая температуру. Кроме этого, могут быть использованы внешние датчики или средства оценки потребляемой мощности (например, счетчики рабочего состояния/устройства контроля, устройства контроля тока и т.д.). Устройство 110 контроля температуры соединено с выходной схемой запуска 115, которая возбуждает узел 117 интерфейса через сигнальную линию 112 сигналом «ТОО НОТ» (СЛИШКОМ ГОРЯЧИЙ). Сигнал «ТОО НОТ» также направляется к логической схеме 120 приостановки работы через мультиплексор 130. Мультиплексором управляют с помощью плавкой перемычки 140, которая выбирает или однонаправленный, или двунаправленный режимы работы в иллюстрируемом воплощении.

В варианте осуществления по Фиг.1 системная логическая схема 150 связана с процессором 100 и может приводиться в действие через формирователь 115 или принимать через входной буфер 160 сигнал PROCHOT#. Сама системная логическая схема может включать в себя несколько тепловых датчиков для определения состояния, когда система в целом достигла неприемлемого уровня температуры, и может соответственно выдавать сигнал PROCHOT#.

Операции для одного воплощения системы по Фиг.1 показаны на Фиг.2. На этапе 200 разделяются различные режимы работы. В некоторых вариантах осуществления полупроводниковые плавкие перемычки могут быть выжжены для выбора режима работы. Другие средства выбора, такие как регистры конфигурации и аналогичные средства, могут быть также использованы для выбора режима работы. В режиме "только выхода" плавкая перемычка 140 заставляет мультиплексор 130 выбрать сигнал ТОО НОТ в качестве входного для логической схемы 120 приостановки работы. Таким образом, внешнее состояние сигнала PROCHOT# не учитывается, используя сигнал PROCHOT# в качестве действующего выходного сигнала лишь в случае, как показано на этапе 205. В двунаправленном режиме с одинарным выводом как системная логическая схема 150, так и процессор 100 могут выдать сигнал PROCHOT# для управления приостановкой работы. Как показано на этапах 215 и 225, процессор 100 контролирует свою температуру и контролирует интерфейс PROCHOT#. Если температура не превышает выбранного показателя, то процессор продолжает контроль температуры, как показано на этапе 220. Аналогичным образом, если сигнал PROCHOT# не установлен, то процессор 100 будет продолжать контролировать интерфейс, как показано на этапе 230. Если сигнал PROCHOT# установлен или если температура превышает выбранный показатель, то работа процессора приостанавливается посредством логической схемы 120 приостановки работы, как показано на этапе 240.

Приостановка работы, выполняемая логической схемой управляемой приостановки работы, может быть осуществлена любым соответствующим техническим известным или иначе доступным приемом. Например, тактовый импульс к устройству может быть периодически остановлен. Альтернативно, производительность обработки может быть снижена посредством ограничения производительности на какой-либо ступени конвейера. Альтернативно, тактовая частота может быть изменена. Эти или какие-либо другие технические приемы, эффективно снижающие производительность обработки процессором, могут быть использованы логической схемой приостановки работы.

В третьем режиме двунаправленная реализация PROCHOT# с двумя выводами может быть использована, как показано на этапе 210. Фиг.3 и 4 иллюстрируют другие подробности одного воплощения, использующего реализацию с двумя выводами. Реализация с двумя выводами может обеспечить как наблюдение за внутренним измерителем температуры процессора, так и выдачу команды приостановки работы. В реализации с одинарным выводом выдача команды приостановки работы будет накладывать маску на установление сигнала процессора на том же самом выводе штыря. В воплощении по Фиг.3 в целях наглядности показаны два процессора, но могут быть добавлены и другие процессоры. Оба процессора 300 и 350 имеют выводы FORCEPH# (ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ПРОЦЕССОРА) и PROCHOT# (ПРОЦЕССОР ГОРЯЧИЙ). Сигнальные линии 364 и 362 передают пару сигналов FORCEPH#, выдаваемые системной логической схемой к процессорам 300 и 350, а сигнальные линии 302 и 352 передают соответственно сигналы PROCHOT# (ПРОЦЕССОР ГОРЯЧИЙ), выдаваемые процессорами 300 и 350 к системной логической схеме.

Процессор 300 включает в себя устройство контроля 310 для обнаружения слишком горячего состояния процессора 300 (или в некоторых воплощениях слишком большого потребления мощности). Каждый пронумерованный блок представляет собой элемент задержки, такой как триггер-защелка. Устройство 305 запуска связано с устройством 310 контроля для приема сигнала «ТОО НОТ» (СЛИШКОМ ГОРЯЧИЙ) от устройства 310 контроля и для выдачи сигнала PROCHOT# на сигнальной линии 302. Первый тракт к мультиплексору 330 принимает сигнал «ТОО НОТ» (СЛИШКОМ ГОРЯЧИЙ) через блок задержки 313-1 и блок задержки 313-2, и передает его далее к входу "w" мультиплексора 330. Второй тракт к мультиплексору 330 принимает сигнал «ТОО НОТ» через блок задержки 313-1, выходную схему 305 запуска (также тем самым считывая любые внешне установленные сигналы на сигнальной линии 302), через инвертирующий формирователь 307 и через блоки 314-2 и 314-3 задержки к входу "b" мультиплексора 330.

Третий тракт к мультиплексору включает в себя входы как от сигнальной линии 302 (PROCHOT#), так и от сигнальной линии 364, которая возбуждается системной логической схемой 360. Сигнальная линия 364 может быть сигнальной линией сигнала FORCEPH# (ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ГОРЯЧЕГО ПРОЦЕССОРА) принудительного перевода горячего процессора, которая позволяет использовать внешние условия, чтобы определить, когда проводить операции приостановки работы. В одном воплощении система может пожелать начать приостановку работы множества процессоров одновременно (то есть в течение одного и того же периода тактового импульса для синхроимпульсов внешней шины) даже в случае, если оба процессора не могут одновременно сами проводить приостановку работы. В этом варианте осуществления может оказаться целесообразным согласовать задержки сигнала СЛИШКОМ ГОРЯЧИЙ к логической схеме 320 управляемой приостановки работы с задержкой, ожидаемой через тракт системной логической схемы. Например, в воплощении по Фиг.3 сигнал СЛИШКОМ ГОРЯЧИЙ «ТОО НОТ» проходит через блок 313-1 задержки, выходную схему 305 запуска, через блок 316-2 задержки, комбинационную логическую схему 363, блок 316-3 задержки в системную логическую схему 370, через блок 316-4 задержки, комбинационную логическую схему 371, блок 316-5 задержки назад к системной логической схеме 360, через блок 316-6 задержки, комбинационную логическую схему 367, блок 316-7 задержки, и затем во второй процессор 350. Предполагая, что второй процессор имеет идентичные логические схемы с логическими схемами, показанными для процессора 300, тракт передачи проходит через элементы, соответствующие входному буферу 309, двум дополнительным блокам 316-8 и 316-9 задержки, вентилю 311 ИЛИ, и входу "f" мультиплексора 330.

Аналогичным образом тракт передачи сигнала СЛИШКОМ ГОРЯЧИЙ, внутреннего для процессора 300, включает в себя 9 блоков задержки и вентиль 311 ИЛИ. Внутри процессора, в режиме с двумя выводами сигнал СЛИШКОМ ГОРЯЧИЙ проходит через блоки 313-1 и 313-2 задержки, а затем через блоки задержки с 315-3 по 315-9, и в вентиль 311 ИЛИ. Вентиль ИЛИ подает в мультиплексор 330 сигнал индикации о том, что должна быть проведена (управляемая) приостановка работы в случае, если или системная логическая схема 360 и 370 установит сигнал FORCEPH# на сигнальной линии 364, или если устройство 310 контроля укажет, что должна быть выполнена (управляемая) приостановка работы. Компоненты 360 и 370 системной логики могут быть локальными (360) и глобальными (370) управляющими интегральными схемами прикладной ориентации (ИСПО, ASIC). Для раскрытых технических приемов не является существенным, будет ли какая-либо или все логические схемы дискретными или интегральными. Логическая схема может быть включена в сами процессоры, или другие системные компоненты, такие как мосты шины, или в интегральные схемы ИСПО или аналогичные компоненты. Кроме этого, абсолютное число или длина различных задержек не является существенной, однако, обеспечение согласования задержек целесообразно в некоторых воплощениях.

В варианте осуществления по Фиг.3 два управляющих входа к мультиплексору ("плавкая перемычка задействования двунаправленного режима горячего процессора" и "плавкая перемычка декодирования мультипроцессора МП") управляют выбором режима. Если плавкая перемычка декодирования мультипроцессора МП укажет, что целесообразна мультипроцессорная реализация (с двумя выводами) PROCHOT#/FORCEPH# (ПРОЦЕССОР ГОРЯЧИЙ/ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ГОРЯЧЕГО ПРОЦЕССОРА), то выбирают тракт передачи сигналов "f" к мультиплексору. Если плавкая перемычка "плавкая перемычка задействования двунаправленного режима горячего процессора" укажет, что требуется только двунаправленный режим, то выбирают вход "b" мультиплексора. Если плавкие перемычки указывают, что ни двунаправленный, ни мультипроцессорный (с двумя выводами) режимы не требуются, то используют режим "только выход", и выбирается тракт передачи сигналов "w" к мультиплексору.

Фиг.4 иллюстрирует операции мультипроцессорной системы, в которой выбран режим с двумя выводами (например, вход "f" на мультиплексоре 330 для варианта воплощения по Фиг.3). В блоке 400 воспринимается высокая температура (например, устройством 310 контроля). На этапе 410 выдают сигнал ПРОЦЕССОР ГОРЯЧИЙ к системной логической схеме. Как показано на этапе 420, внутренний сигнал СЛИШКОМ ГОРЯЧИЙ задерживается. В воплощении по Фиг.3 тракт передачи сигналов через элементы задержки 313-1, 313-2 и 315-3 по 315-9 создает задержки. Как показано на этапе 425, установленный сигнал ПРОЦЕССОР ГОРЯЧИЙ также распространяется через системную логическую схему, подвергаясь задержкам и приводя в результате к формированию сигнала ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ГОРЯЧЕГО ПРОЦЕССОРА (FORCEPH#) для другого процессора (процессорам) в системе. Например, в варианте воплощения по Фиг.3 сигнал ПРИНУДИТЕЛЬНЫЙ ПЕРЕВОД ГОРЯЧЕГО ПРОЦЕССОРА может быть выдан к процессору 350 по сигнальной линии 362.

Благодаря задержке внутри первого процессора, которая предназначена для согласования задержки в тракте передачи через системную логику в дополнение к каким-либо внутренним задержкам, процессоры начинают приостановку работы синхронно, как показано на этапах 430 и 435. Может оказаться целесообразным в некоторых системах иметь такую синхронизацию приостановки работы, чтобы поддерживать работу процессоров на однородной скорости, тем самым приблизительно уравновешивая требования работы и проблемы управления температурой/энергией. Процессор соответственно может быть принудительно переведен в состояние приостановки работы даже в случае, когда не требуется его перехода в состояние приостановки работы.

Таким образом были раскрыты технические приемы для интерфейса управления температурой процессора. Хотя некоторые приведенные в качестве примера варианты воплощения были описаны и показаны на сопроводительных чертежах, следует понять, что такие варианты воплощения являются исключительно иллюстративными и не ограничивающими объема защиты изобретения, и что это изобретение не ограничивается специфическими структурами и устройствами, описанными и показанными здесь, поскольку различные другие модификации будут очевидны для специалистов средней квалификации в данной области техники после изучения приведенного здесь раскрытия.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2008 |

|

RU2399088C2 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| КОНВЕЙЕРНЫЙ ПРИЕМНИК БАЗОВОЙ СТАНЦИИ СОТОВОЙ ЯЧЕЙКИ ДЛЯ УПЛОТНЕНННЫХ СИГНАЛОВ С РАСШИРЕННЫМ СПЕКТРОМ | 1996 |

|

RU2154913C2 |

| МИКРОКОМПЬЮТЕР И СПОСОБ ЕГО ТЕСТИРОВАНИЯ | 2006 |

|

RU2374679C2 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Вычислительная система с холодным резервом | 2021 |

|

RU2771211C1 |

| ВЫБОРОЧНАЯ ПРИОСТАНОВКА ШИННЫХ УСТРОЙСТВ | 2002 |

|

RU2304300C2 |

| СТАНДАРТНЫЙ АНАЛОГОВЫЙ ИНТЕРФЕЙС ДЛЯ МНОГОЯДЕРНЫХ ПРОЦЕССОРОВ | 2007 |

|

RU2417412C2 |

| ПАРАЛЛЕЛЬНО СОГЛАСОВАННАЯ ШИННАЯ СИСТЕМА | 2001 |

|

RU2239230C2 |

Изобретение относится к области электронных компонентов, а именно к интерфейсу управления температурой процессора. Технический результат - обеспечение надлежащего управления в случае перегрева процессора и/или возможностей синхронизации приостановки работы нескольких процессоров в случае перегрева одного из них. В одном варианте выполнения процессор включает в себя двунаправленный интерфейс и выходную логическую схему для выдачи первого сигнала, указывающего внутреннюю высокую температуру на двунаправленном интерфейсе. Логическая схема приостановки работы приостанавливает операции процессора в случае, если указана внутренняя высокая температура или если принят внешний сигнал на двунаправленном интерфейсе. 4 н. и 17 з.п. ф-лы, 4 ил.

| US 2001003207 A1, 07.07.2001 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ УВЕЛИЧЕНИЯ ЭФФЕКТИВНОСТИ ПРОЦЕССОРА | 1996 |

|

RU2176813C2 |

| US 5719800 A, 17.02.1998. | |||

Авторы

Даты

2006-04-20—Публикация

2003-03-06—Подача