Область техники, к которой относится изобретение

Настоящее изобретение относится к полупроводниковым устройствам и более конкретно к интерфейсным полупроводниковым устройствам со структурами системного взаимодействия.

Уровень техники

Полупроводниковые устройства сегодняшнего дня характеризуются постоянно возрастающими возможностями для обработки данных при более малых размерах и продолжением функционирования при более высоких частотах. Более высокие скорости обработки и уменьшенный размер могут привести к различным результатам, включая результаты, относящиеся к мощности и температурной зависимости. Соответственно, сейчас многие производимые процессоры являются многоядерными в одном корпусе и даже многоядерными на одном кристалле. Такие процессоры могут выполнять высокоуровневые задачи обработки данных при пониженных температурах, уменьшающих рассеивание тепла. Более того, с помощью многоядерных процессоров может быть сделано большее количество обработки данных при более низких частотах.

Однако интегрирование множества ядер в одном корпусе, таком как панель с микросхемой, может привести к различным результатам. Одним из таких результатов является влияние множественности ядер на электрические характеристики. В особенности, многоядерные процессоры, каждый из которых включает в себя цифровые логические схемы, так же как и схемы интерфейса входов/выходов (I/O), создают значительную электрическую нагрузку на среду взаимодействия, через которую панель процессора связана с системой. Например, многие компьютерные системы включают в себя системную шину, часто упоминаемую как внешняя шина (FSB), которая является многоабонентской шиной, используемой для соединения процессора с другими системными компонентами, такими как контроллер-концентратор памяти (МСН), системная память и другие компоненты системы. Чтобы избежать результатов с негативными электрическими характеристиками, FSB может управляться таким образом, чтобы работать при более низкой частоте, воздействующей на рабочие характеристики. Такое понижение частоты шины может значительно воздействовать на характеристики для двойного ядра или других многоядерных устройств, таким образом требования по частотной полосе пропускания могут увеличиться в пропорции к количеству ядер.

Некоторые двуядерные процессоры спроектированы таким образом, что их ядра соединены вместе в корпусе таким способом, который подобен прокладке маршрутов между панелями многоядерных процессоров в системах с многоядерными процессорами. Однако такая конструкция понижает электрические характеристики внешней шины (FSB). В частности, длина трассировки значительно увеличивается, также увеличивается емкостное сопротивление, которое может значительно ограничить частоту I/O. Другие способы соединения ядер могут привести к значительным усилиям в проектировании, что увеличивает сложность и ухудшает основу архитектуры ядра.

Краткое описание чертежей

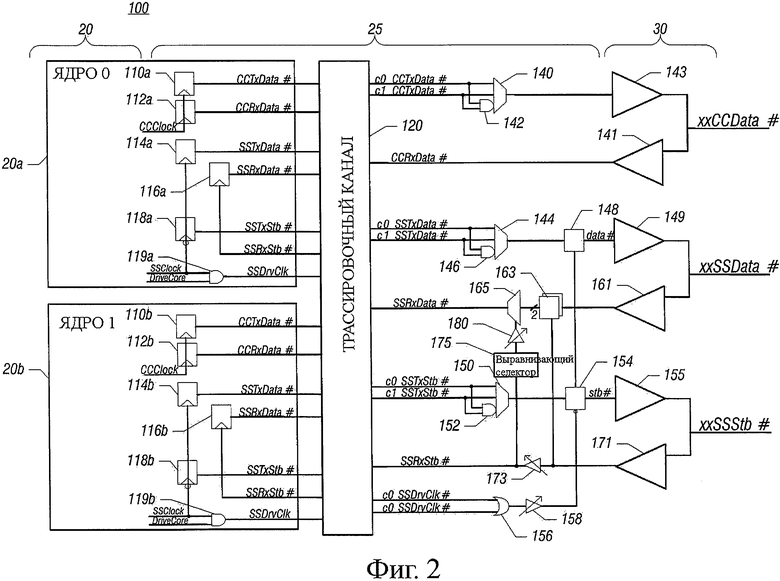

Фиг.1 - блок- схема процессора в соответствии с одним из вариантов осуществления настоящего изобретения.

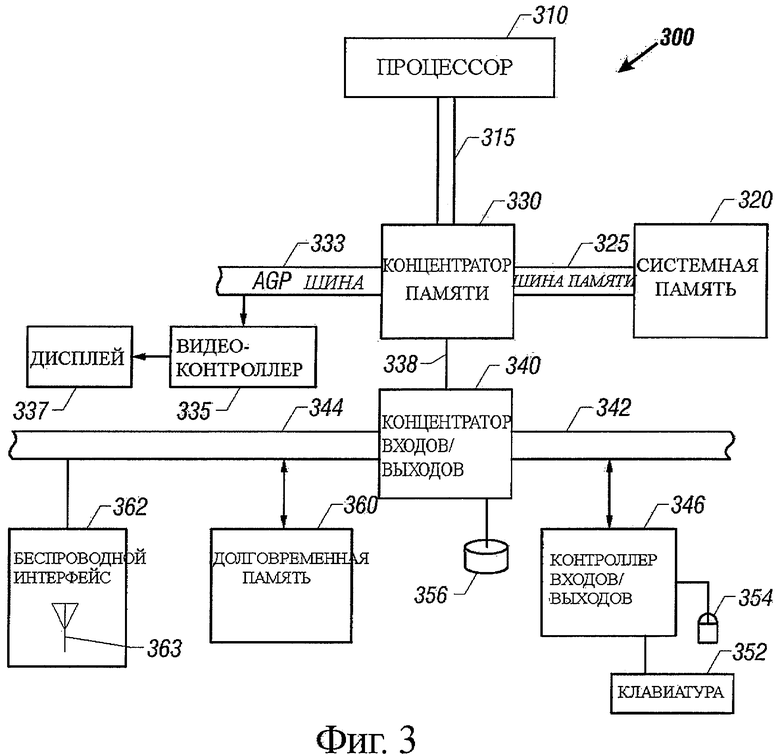

Фиг.2 - схематическая диаграмма процессора в соответствии с одним из вариантов осуществления настоящего изобретения.

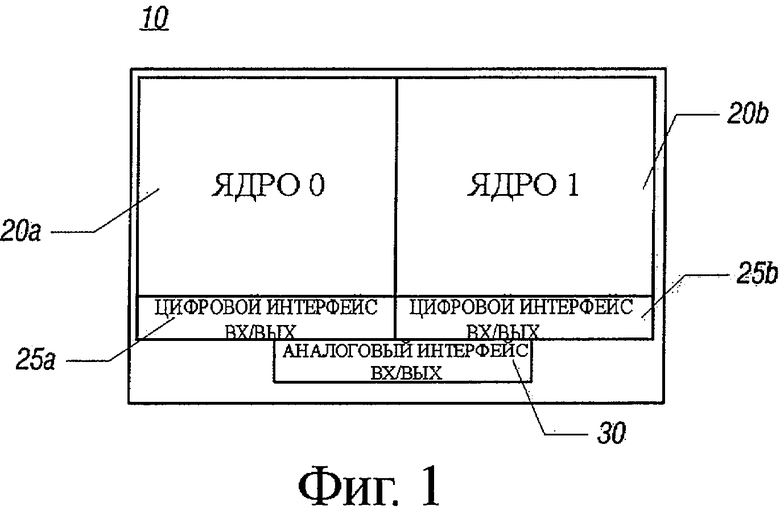

Фиг.3 - блок- схема типичной системы на основе процессора, с которой могут быть использованы варианты осуществления настоящего изобретения.

Подробное описание изобретения

В различных вариантах осуществления изобретения ядра многоядерных устройств могут быть соединены внутри корпуса с минимальными воздействиями и на архитектуру ядер, и на частоту входов/выходов. В частности, с помощью представления единичной нагрузки для системной шины воздействие частоты при работе многоядерных устройств может быть минимизировано. В описанных здесь вариантах осуществления изобретения единичная нагрузка может быть получена с помощью цифрового комбинирования сигналов шины многоядерных устройств на единственном кристалле (т.е. на одной панели процессора) и передачи комбинации в системную шину через стандартный аналоговый интерфейс. Для получения этой комбинации сигналов цифровой интерфейс, логически связанный между ядрами и стандартным аналоговым интерфейсом, может действовать, по существу, как логическая схема «монтажное ИЛИ».

В некоторых системах системная шина, использующая логические схемы прерывания приемопередатчика (GTL+), может быть применена для соединения вместе системных компонентов. Такая системная шина может логически действовать как логическая схема «монтажное ИЛИ». Посредством перевода логической схемы «монтажное ИЛИ» в цифровую схематику связи многоядерных устройств со стандартным аналоговым интерфейсом панели процессора может быть реализовано улучшение электрических характеристик и легкость в использовании. То есть только единичная электрическая нагрузка регистрируется системной шиной, и для управления комбинированием входов и выходов ядра нужны минимальные изменения в базовой архитектуре ядра или изменения вообще не нужны. Соответственно, оказывается минимальное воздействие на каналы связи ядра, быстродействие или логические операции.

Обратимся сейчас к фигуре 1, показывающей блок-схему процессора, в соответствии с одним из вариантов осуществления настоящего изобретения. Более конкретно, как показано на фиг.1, панель 10 процессора может содержать двухядерный процессор, включающий в себя первое ядро 20а (т.е. ядро 0) и второе ядро 20b (т.е. ядро 1). В общем, ядро панели 10 процессора может быть определено здесь как ядро 20. Хотя в варианте осуществления изобретения, показанного на фиг.1, показано только два ядра, следует понимать, что обзор настоящего изобретения не имеет таких ограничений, и в других вариантах осуществления изобретения могут быть представлены дополнительные ядра в данном процессоре.

Каждое ядро 20 может включать в себя всю логику и ресурсы для данного ядра, такие как ресурсы каналов связи ядра, исполнительных модулей, кэш-памяти, регистровых файлов и других подобных структур. Более того, каждое ядро 20 может включать в себя собственный выделенный цифровой интерфейс входов/выходов, соответственно цифровой интерфейс 25а и цифровой интерфейс 25b (в общем, цифровой интерфейс входов/выходов 25). Как описывается в дальнейшем, цифровой интерфейс входов/выходов 25 может включать в себя различные логические схемы, чтобы обеспечить интерфейс для сигналов между объединенным ядром и аналоговым интерфейсом входов/выходов процессора. В различных вариантах осуществления изобретения цифровой интерфейс 25 может включать в себя всю логику управления шиной для его объединенного ядра (как если бы было представлено только одно ядро). Другими словами, каждый цифровой интерфейс входов/выходов 25 является контроллером шины для объединенного ядра 20. Таким образом, как показано на фиг.1, каждое ядро 20 включает в себя всю логику ядра, так же как логическая схема цифрового интерфейса. Более того, должно быть понятно, что первое ядро 20а и второе ядро 20b могут быть идентичны или, по меньшей мере, в значительной степени идентичны. Соответственно, единичная архитектура ядра может использоваться или копироваться, чтобы создать корпус, имеющий два или более ядер с той же самой схематикой и функциональностью. В других вариантах осуществления изобретения первое ядро 20а и второе ядро 20b могут быть различных типов, таких как архитектура с разнородными ядрами. При использовании этого способа логика различных ядер может быть очень различной при условии, что каждый соответствующий цифровой вход/выход будет, в основном, одинаковым. Такие разнородные ядра могут применять совместимый протокол шины, например, протокол FSB.

Однако каждое ядро 20 нуждается в схемном решении с выделенным аналоговым интерфейсом. Вместо этого стандартный аналоговый интерфейс 30 (analog I/O) входов/выходов может быть представлен и использоваться для соединения сигналов от обоих ядер 20а и 20b туда и обратно для взаимодействия с каждой панелью 10 процессора. Этот стандартный аналоговый интерфейс между ядрами многоядерного устройства и взаимодействие, например, шины, с которой соединен процессор, может улучшить время ожидания сигнала и облегчить проектирование при интегрировании многоядерного процессора в систему, используя общую шину, такую как внешняя шина (FSB). Хотя это не показано в обобщенном виде фигуры 1, должно быть понятно, что могут быть применены некоторые дополнительные (например, стандартные) логические схемы цифрового интерфейса между цифровыми входами/выходами 25 и аналоговыми входами/выходами 30 для маршрутизации сигналов между данным ядром и аналоговыми входами/выходами 30.

В то время как описывается это частное применение, показанное на фигуре 1, должно быть понятно, что пределы настоящего изобретения не так ограничены. То есть в различных вариантах осуществления изобретения могут быть представлены различные формы выделенной схематики процессора для многоядерных устройств, с одиночным набором аналоговой схематики, чтобы обеспечить интерфейс шиной или другими средствами взаимодействия для многоядерных устройств. Таким образом, электрическая нагрузка, возникающая при взаимном соединении, минимизируется, т.е. соответствует нагрузке при единичном ядре. В результате взаимное соединение может осуществляться при такой же частоте, как в том случае, когда в панели процессора находится одноядерный процессор. Более того, уменьшается сложность архитектуры, т.к. внутри ядер не требуется никакой дополнительной логической схематики для осуществления связи многоядерных устройств. Более того, уменьшается общая схематика кристалла, т.к. применяется только единственный набор аналоговых интерфейсов.

Обратимся сейчас к фигуре 2, показывающей блок-схему процессора в соответствии с одним из вариантов осуществления настоящего изобретения. Более конкретно, как показано на фиг.2, процессор 100 может быть двухядерным процессором, включающим в себя ядра 20а и 20b. Заметьте, что использование одинаковых цифровых ссылок на фигурах 1 и 2 отображает присутствие одинаковых компонентов. Как показано в цифровых обозначениях ссылок в верхней части фиг.2, процессор 100 может быть разбит на участок 20 с ядрами, участок цифровых входов/выходов (также обозначаемый здесь в ссылках как цифровой участок) 25 и участок аналоговых входов/выходов (также обозначаемый здесь в ссылках как аналоговый участок) 30. Участок 20 ядер может быть с выделенными участками логических схем и использоваться для формирования индивидуальных ядер. Более того, участок цифровых входов/выходов 25 может включать в себя некоторое количество выделенных логических схем в каждом из ядер 20а и 20b, и некоторое количество дополнительной интерфейсной логики, осуществляющей связь между ядрами 20а и 20b и участком 30 аналоговых входов/выходов. Как далее показано на фиг.2, аналоговый участок 30 может быть единичным стандартным аналоговым интерфейсом для обеспечения связи между ядрами 20а и 20b и внешней по отношению к процессору шиной или другим межкомпонентным соединением.

Как показано на фиг.2, ядро 20а включает в себя различные цифровые логические схемы, которые могут быть частью цифрового участка 25 для использования в качестве интерфейса между логикой ядер и трассировочным каналом 120. Различные цифровые логические схемы могут быть представлены для каждой из многочисленных сигнальных линий, используемых для передачи соответствующих сигналов: передача данных, получение данных и стробирующих сигналов, в добавление к линиям для передачи тактовых сигналов. В частности, показанное на фиг.2 ядро 20а может включать в себя синхронный триггер 110а, который синхронизируется стандартным тактовым сигналом (CCClock) для каждой линии стандартных тактовых данных для передачи данных и соответствующий триггер 112а, подобным образом синхронизируемый для каждой линии стандартных тактовых данных для данных, которые должны быть получены. В то время как пределы настоящего изобретения не ограничены в этом отношении, в некоторых вариантах настоящего изобретения 16 стандартных линий тактовых данных может быть представлено в каждом направлении передачи и получения данных. Как показано на фиг.2, отходящие линии стандартных тактовых данных могут быть обозначены как CCTxData#, в то время как приходящие линии стандартных тактовых данных могут быть обозначены как CCRxData#. Заметьте, что символ # после названия сигнала используется для обозначения логического сигнала, возбуждаемого низким уровнем сигнала, т.е. обозначает сигнал в активном состоянии, когда он переведен на низкий уровень. Однако такие логические уровни с активным сигналом низкого уровня служат только для иллюстрации, и пределы настоящего изобретения не ограничены в этом отношении.

Ядро 20а может, кроме того, включать в себя триггер 114а, служащий для того, чтобы обеспечить источник синхронизирующих данных, которые должны передаваться на линию объединенного источника синхронизирующих данных передачи (т.е. SSTxData#). Подобным образом, источник приходящих синхронизирующих данных может быть получен по линии источника синхронизирующих данных приема (т.е. SSRxData#) через устройство хранения, например, через устройство, работающее по принципу "первым пришел - первым обслужен" (FIFO) 116а. Заметьте, что такой маршрут источника синхронизирующих данных может улучшить характеристики с помощью многократной передачи данных на шину синхронизации (например, 4х). Кроме того, ядро 20а может дополнительно включать в себя триггер 118а, служащий для того, чтобы обеспечить данными линию источника синхронизирующего передающего стробирующего сигнала (т.е. SSTxStb#). Заметьте, что триггеры 114а и 118а могут быть синхронизированы в противоположных отношениях через источник синхроимпульсов (т.е. SSClock). В свою очередь, источник синхроимпульсов и сигнал ядра (DriveCore) могут быть соединены с помощью логического вентиля 119а, который, в свою очередь соединяется, чтобы обеспечить ведущий синхронизирующий сигнал (т.е. SSDrvClk). Заметьте, что подобная логическая схема, которая обсуждалась выше, представлена в ядре 20b (показана с одинаковыми цифровыми ссылками и буквенным обозначением "b").

Каждая из обсуждаемых выше сигнальных линий может быть спарена для передачи в трассировочный канал 120, который, в свою очередь, обеспечивает передачу сигналов туда и обратно из дополнительной цифровой логики внутри цифрового участка 25. Трассировочный канал 120 может включать в себя усилители, повторители и подобные устройства. Такая дополнительная логика внутри цифрового участка 25 может использоваться для выбора активного ядра из ядер 20а и 20b для передачи/получения данных через сигнальные линии. Соответственно, трассировочный канал 120 может включать в себя логические схемы для определения маршрута сигналов в/из ядер 20а и 20b из/в выбранных сигнальных линий в цифровом участке 25. В направлении передачи стандартные синхронизирующие сигналы передачи (т.е. c0CCTxData# или c1CCTxData#) из обоих ядер могут быть спарены с помощью мультиплексора 140, который управляется (DFT/ control register-related signals) сигналами, отвечающими требованиям удобства тестирования или сигналами, относящимися к управляемому регистру (не показаны на фиг.2). Такие DFT сигналы могут позволять использование двухядерного процессора, который должен быть конвертирован в процессор с одиночным ядром для целей тестирования или отладки программ. Однако по умолчанию или в нормальном режиме мультиплексор 140 может выбрать выход логического вентиля 142. Логический вентиль 142 может эмулировать действие или действовать как логический эквивалент шины с логическим элементом «монтажное ИЛИ», такой как шины, основанной на использовании логической схемы прерывания приемопередатчика (GTL+), также логический вентиль 142 может действовать как вентиль ИЛИ в варианте осуществления изобретения с низким активным уровнем сигнала. В свою очередь, выбранная линия данных может быть передана на аналоговый участок 30 или более конкретно в аналоговый буфер 143, который служит буфером для цифрового сигнала для перевода его на соответствующий уровень и для передачи в направлении взаимодействующего элемента, с которым связан процессор 100, например, шиной. Соответственно, желаемые данные могут быть переданы в направлении линии общих синхронизирующих данных шины (например, xxCCData#). Приходящие общие сигналы синхронизации данных, получаемые через линии xxCCData#, могут быть спарены через входной буфер 141 и переданы далее в направлении линии общих синхронизирующих приемных данных (т.е. xxCCRxData#) в трассировочный канал 120. Из трассировочного канала 120 данные могут быть переданы или на триггер 112а, или на триггер 112b, в зависимости от выбранного ядра. Альтернативно, приходящие сигналы могут быть переданы всем ядрам, а сами ядра определят, будут ли они обрабатывать сигналы или нет.

Снова обратимся к фигуре 2. Источник синхронизирующих данных, которые должны быть переданы от одного из ядер 20а и 20b, могут быть направлены через трассировочный канал 120 и переданы через линию данных ядер на мультиплексор 144 (т.е. c0SSTxData# или c1SSTxData#). Кроме того, эти линии спарены с логическим вентилем 146, который работает, как обсуждалось выше, в отношении к логическому вентилю 142. Выбранные данные от мультиплексора 144 передаются на триггер-защелку 148. После синхронизирования источником синхронизирующих импульсов триггер-защелка передает данные на цифровой участок 25 и в буфер 149 аналогового участка 30. Таким образом, данная линия источника синхронизирующих данных (т.е. xxSSData#) может иметь сигнал, переданный после этого.

Для приходящего на процессор 100 из шины источника синхронизирующих данных характерно то, что данные соединяются через буфер 161 и передаются на выбранную тригтер-защелку 163. Работа триггер-защелки 163 может управляться приходящим сигналом от источника синхронизирующего стробирующего сигнала (т.е. SSRxStb#). Когда данные, находящиеся в регистре-защелке, прошли через нее, они передаются на мультиплексор 165, а затем в трассировочный канал 120 в качестве источника синхронизирующих приемных данных (т.е. SSRxData#). Как показано на фиг.2, мультиплексор 165 может управляться на основе приходящего сигнала от источника синхронизирующего стробирующего сигнала, который обеспечивается через инвертор 173 с переменной задержкой, выравнивающий селектор 175, и другой инвертор 180 с переменной задержкой. Исходя из ядра, для которого предназначаются данные, трассировочный канал 120 будет передавать данные из источника синхронизирующих приемных данных в FIFO, или 116а, или 116b. Альтернативно, а так же как со стандартными синхронизирующими сигналами, описанными ранее, источник синхронизирующих приемных данных может быть доступен для передачи данных для обоих FIFO, 116а и 116b. Как показано на фиг.2, эти FIFO управляются сигналом, приходящим от источника синхронизирующего стробирующего сигнала, так же проходящего через трассировочный канал 120.

Снова обратимся к фигуре 2. Источник синхронизирующих передающих стробирующих сигналов может генерироваться в ядрах 20а и 20b и передаваться через трассировочный канал 120 к мультиплексору 150 и связанному с ним логическому вентилю 152. В частности, каждое ядро может генерировать синхронизирующие стробирующие сигналы, передаваемые к мультиплексору 150 через линии источника синхронизирующих передающих стробирующих сигналов (т.е. c0SSTxStb# и c1SSTxStb#). Выбранный стробирующий сигнал выдается от мультиплексора 150 и триггер-защелки 154, которая, в свою очередь, синхронизируется с помощью источника ведущего синхронизирующего сигнала, который является производным от приходящего сигнала источника ведущих синхронизирующих сигналов (т.е. c0SSdrvClk# и c1SSDrvClk#) из данного ядра через трассировочный канал 120 и через логический вентиль 156 ИЛИ и через инвертор 158 с переменной задержкой. Выбранный источник синхронизирующего стробирующего сигнала обрабатывается через тригтер-защелку 154 и передается в буфер 155 для передачи в направлении шины, как источник синхронизирующего стробирующего сигнала (т.е. xxSSStb#). В свою очередь, приходящие стробирующие сигналы в направлении линий источника синхронизирующих стробирующих сигналов выдаются в буфер 171, который, в свою очередь, далее проходит через инвертор 173 с переменной задержкой и трассировочный канал 120 в направлении приемной линии источника синхронизирующих стробирующих сигналов (т.е. SSRxStb#). В свою очередь, источник синхронизирующего стробирующего сигнала обеспечивается через трассировочный канал 120 для управления одним из выбранных FIFO 116а и 116b. В то время как здесь описано частное применение варианта изобретения, показанного на фигуре 2, должно быть понятно, что пределы настоящего изобретения не ограничены в этом отношении, и другие применения стандартного аналогового интерфейса для многоядерных процессоров, например, двухядерных процессоров, могут быть также реализованы.

На фиг.3 изображена блок-схема типичной системы на основе процессора, с

которой могут быть использованы варианты осуществления настоящего изобретения. Термин «система», как он применяется здесь, может относиться к любому типу системы, основанной на применении процессора, например, главный компьютер, настольный компьютер, сервер, ноутбук, портативное устройство, бытовое электронное устройство, телевизионная абонентская приставка или подобные им устройства. Система 300 включает в себя процессор 310, который может быть процессором общего назначения или специального назначения. В варианте осуществления настоящего изобретения процессор 310 может быть многоядерным процессором, например, двухядерным. Более того, процессор 310 может включать в себя стандартный аналоговый интерфейс, позволяющий уменьшить электрическую нагрузку, в добавление к облегчению подключения конструкции с одним ядром в многоядерный процессор.

В одном из вариантов осуществления изобретения процессор 310 может быть присоединен через внешнюю шину 315 к концентратору 330 памяти, который, в свою очередь, может быть соединен с системной памятью 320, которая может быть оперативной памятью с динамическим доступом (DRAM) в одном из вариантов осуществления изобретения, при этом связь осуществляется через шину 325 памяти. В то время как в показанном на фигуре 3 варианте осуществления изобретения это не отображено, должно быть понятно, что в различных вариантах изобретения могут быть подключены к внешней шине 315 дополнительные многоядерные процессоры, или другие подобные процессоры. Концентратор 330 памяти может также быть соединен через шину 333 ускоренного графического порта (AGP) с видеоконтроллером 335, который может быть соединен с дисплеем 337. Шина 333 ускоренного графического порта (AGP) может соответствовать спецификации интерфейса AGP, исправление 2.0, публикация 4 мая 1998 г., корпорацией Интел, Санта Клара, Калифорния.

Концентратор 330 памяти может также соединяться (через канал связи 338 концентратора) с концентратором 340 входов/выходов, который соединен с первой шиной 342 и со второй шиной 344. Первая шина 342 может быть соединена с контроллером 346 входов/выходов, который управляет доступом к одному или нескольким устройствам входов/выходов. Как показано на фиг.3, эти устройства могут включать в себя в одном из вариантов осуществления изобретения входные устройства, такие как клавиатура 352 и мышь 354. Концентратор 340 входов/выходов может также соединяться с, например, накопителем 356 на жестком диске. Должно быть понятно, что другие средства хранения информации могут быть также включены в систему 300.

Вторая шина 344 может быть также соединена с различными компонентами, включающими в себя, например, долговременную память 360, такую как флэш-память и беспроводной интерфейс 362. Беспроводной интерфейс 362 может использоваться в определенных вариантах осуществления изобретения для связи с отдаленными устройствами. Как показано на фиг.3, беспроводной интерфейс 362 может включать в себя дипольную или другую антенну 363 (наряду с другими компонентами, не показанными на фиг.3). Конечно, дополнительные устройства могут быть связаны с первой шиной 342 и со второй шиной 344. Хотя описание делает ссылки на специфические компоненты системы 300, предполагается, что могут быть возможными многочисленные модификации и вариации описанных и проиллюстрированных вариантов осуществления изобретения.

Варианты осуществления изобретения могут быть воплощены в программном коде, который может храниться на носителе данных, имеющем хранящиеся на нем инструкции, которые могут использоваться, чтобы программировать систему для выполнения инструкций. Носитель данных может включать в себя, хотя это не является ограничением, любой тип дисков, включающих в себя флоппи диски, оптические диски, запоминающее устройство для чтения компакт дисков (CD-ROM), запоминающее устройство для чтения и записи компакт дисков (CD-RW), магнитно-оптические диски, полупроводниковые устройства, такие как запоминающие устройства только для чтения (ROM), оперативные запоминающие устройства (RAM), такие как динамическое ОЗУ (DRAM), статическое ОЗУ (SRAM), стираемое программируемое постоянное запоминающее устройство (EPROM), флэш-память, электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карточки или любые другие типы устройств, подходящих для хранения инструкций в электронном виде.

В то время как настоящее изобретение описано по отношению к ограниченному числу вариантов осуществления изобретения, специалисты в данной области техники оценят многочисленные модификации и вариации, которые здесь потенциально возможны. Подразумевается, что прикрепленная формула изобретения охватывает все такие модификации и вариации, которые соответствуют духу и цели настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИКА ИНТЕРФЕЙСА ДЛЯ МНОГОЯДЕРНОЙ "СИСТЕМЫ НА КРИСТАЛЛЕ" (SoC) | 2010 |

|

RU2470350C2 |

| СОВМЕСТИМОСТЬ ОДНОПРОВОДНОЙ И ТРЕХПРОВОДНОЙ ШИН | 2005 |

|

RU2352980C2 |

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2627100C2 |

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| ИНТЕЛЛЕКТУАЛЬНЫЕ ЭЛЕКТРОННЫЕ УСТРОЙСТВА ДЛЯ СИСТЕМЫ АВТОМАТИЗАЦИИ ПОДСТАНЦИИ И СПОСОБ ЕЕ РАЗРАБОТКИ И УПРАВЛЕНИЯ | 2009 |

|

RU2504913C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОТЛАДКИ МНОГОЯДЕРНОЙ СИСТЕМЫ | 2007 |

|

RU2405192C2 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2599971C2 |

| ПАРАЛЛЕЛЬНО СОГЛАСОВАННАЯ ШИННАЯ СИСТЕМА | 2001 |

|

RU2239230C2 |

| КОМПЬЮТЕРНО-ТЕЛЕКОММУНИКАЦИОННОЕ УСТРОЙСТВО (ТЕЛЕКОММУНИКАЦИОННЫЙ ОРГАНАЙЗЕР (ТОГ)) | 1997 |

|

RU2127448C1 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2579140C1 |

Изобретение относится интерфейсным полупроводниковым устройствам со структурами системного взаимодействия. Техническим результатом является повышение надежности работы за счет выполнения соединения ядер внутри корпуса с минимальными воздействиями на архитектуру ядер и на частоту входов/выходов. Процессор содержит множество ядер процессора для выполнения инструкций, при этом каждое из ядер включает в себя выделенную схему цифрового интерфейса. Процессор дополнительно включает в себя аналоговый интерфейс, соединенный с ядрами процессора через схему цифрового интерфейса. Аналоговый интерфейс может быть использован для организации перемещения данных между корпусом чипа, включающем в себя ядра и средства межкомпонентного соединения, такие как общая шина, связывающая их. Способ перемещения потока данных описывает работу многоядерного процессора. 3 н. и 8 з.п. ф-лы, 3 ил.

1. Многоядерный процессор, содержащий:

первое ядро процессора для выполнения инструкций, первое ядро процессора включает в себя логическую схему первого цифрового интерфейса,

второе ядро процессора для выполнения инструкций, второе ядро процессора включает в себя логическую схему второго цифрового интерфейса,

средство аналогового интерфейса, соединенного с первым ядром процессора через логическую схему первого цифрового интерфейса и со вторым ядром процессора через логическую схему второго цифрового интерфейса, при этом средство аналогового интерфейса предназначено для перемещения потока данных между первым и вторым ядрами процессора и необходимым для этого межкомпонентным соединением, и

стандартный цифровой интерфейс, осуществляющий связь между первым и вторым ядрами процессора и средством аналогового интерфейса,

в котором стандартный цифровой интерфейс содержит мультиплексор для выбора потока данных из первого ядра процессора или второго ядра процессора для коммуникации с межкомпонентными соединениями, при этом мультиплексор получает выходной сигнал выбранных логических средств для эмулирования шины «монтажное ИЛИ», таким образом, что средство аналогового интерфейса передает комбинацию потока данных от первого и второго ядер процессора в межкомпонентное соединение, чтобы представлять единичную электрическую нагрузку для многоядерного процессора к межкомпонентному соединению.

2. Многоядерный процессор по п.1, содержащий панель процессора, включающую в себя первое и второе ядро процессора и средства аналогового интерфейса.

3. Многоядерный процессор по п.2, в котором первое ядро процессора и второе ядро процессора содержат разнородные ядра, при этом логическая схема первого цифрового интерфейса и логическая схема второго цифрового интерфейса, в основном, подобны.

4. Многоядерный процессор по п.2, в котором средство аналогового интерфейса служит для того, чтобы представлять единичную электрическую нагрузку для процессора и межкомпонентного соединения.

5. Многоядерный процессор по п.1, в котором стандартный цифровой интерфейс содержит маршрутизатор для маршрутизации потока данных в направлении линии общих синхронизирующих данных или линии источника синхронизированных данных.

6. Многоядерный процессор по п.5, в котором стандартный цифровой интерфейс дополнительно содержит линию данных стробирующего сигнала, при этом линия данных стробирующего сигнала и линия источника синхронизированных данных управляются общим ведущим синхронизирующим сигналом.

7. Многоядерный процессор по п.5, в котором линия источника синхронизированных данных содержит:

первую защелку-триггер для получения приходящих данных для ядра первого процессора и вторую защелку-триггер для получения приходящих данных для ядра второго процессора, при этом первая и вторая защелки-триггеры могут управляться приходящим стробирующим сигналом и; и

мультиплексор, соединенный с первой и второй защелками-триггерами, при этом мультиплексор может управляться выравнивающим селектором, который может управляться приходящим стробирующим сигналом.

8. Компьютерная система, содержащая:

многоядерный процессор, включающий в себя первое ядро, имеющее первый цифровой интерфейс, второе ядро, имеющее второй цифровой интерфейс, стандартный аналоговый интерфейс, соединенный с первым ядром и вторым ядром, и единичную основу, включающую в себя первое и второе ядра, первый и второй цифровой интерфейс, и стандартный аналоговый интерфейс,

стандартный цифровой интерфейс, спаренный между первым и вторым цифровыми интерфейсами и стандартным аналоговым интерфейсом, и включающий в себя мультиплексор для получения данных первого ядра и данных второго ядра для передачи на общее межкомпонентное соединение,

логические средства, соединенные с мультиплексором, при этом логические средства служат для эмулирования межкомпонентного соединения как «монтажное ИЛИ»,

динамическое ОЗУ (DRAM),

общее межкомпонентное соединение для связи многоядерного процессора с динамическим ОЗУ, и

в которой стандартный аналоговый интерфейс представляет единичную электрическую нагрузку от первого ядра и второго ядра к общему межкомпонентному соединению.

9. Способ перемещения потока данных, содержащий:

обеспечение мультиплексора данными от первого ядра,

обеспечение мультиплексора данными от второго ядра,

выбор данных от первого ядра или данных от второго ядра для вывода данных из мультиплексора,

выполнение операции в режиме «монтажного ИЛИ» через логический вентиль, соединенный с мультиплексором, который получает данные первого ядра и данные второго ядра и имеет выход, соединенный с мультиплексором, и

маршрутизацию выбранных данных через стандартный аналоговый интерфейс для первого ядра и для второго ядра к общей шине.

10. Способ по п.9, дополнительно содержащий обеспечение данными первого ядра коммуникационного мультиплексора через первый шинный контроллер первого ядра и обеспечение данными второго ядра коммуникационного мультиплексора через второй шинный контроллер второго ядра.

11. Способ по п.9, дополнительно содержащий обеспечение мультиплексора данными третьего ядра и выбор данных первого ядра или второго ядра или третьего ядра для вывода данных из мультиплексора.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US 20020169938 A1, 14.11.2002 | |||

| US 4389710 А, 21.06.1983 | |||

| СИСТЕМА И СПОСОБ ОБЕСПЕЧЕНИЯ КОГЕРЕНТНОСТИ ПАМЯТИ В МНОГОШИННОЙ КОМПЬЮТЕРНОЙ СИСТЕМЕ | 1997 |

|

RU2221271C2 |

| КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ В КОМПЬЮТЕРНОЙ СИСТЕМЕ | 1999 |

|

RU2220444C2 |

Авторы

Даты

2011-04-27—Публикация

2007-03-13—Подача