Изобретение относится к вычислительной технике и может быть использовано при создании систем для решения информационно-расчетных задач повышенной надежности в случае воздействия внешнего разрушительного потока частиц и излучений.

Известна резервированная двухпроцессорная вычислительная система [1] (аналог), содержащая схему сравнения и два идентичных канала, каждый из которых содержит системный генератор, выход которого подключен к первому входу процессора, первый выход процессора подключен к первому входу коммутатора, второй выход процессора подключен к первому входу элемента ИЛИ, выход которого подключен к первому входу временного анализатора исправности и первому входу триггера, выход которого подключен к первому входу элемента ИЛИ-НЕ, импульсный генератор, выход которого подключен ко второму входу временного анализатора исправности, выход которого подключен к первому входу счетчика сбоев и второму входу триггера, первый выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, схему начальной установки, выход которой подключен ко второму входу процессора, второму входу элемента ИЛИ, второму входу счетчика сбоев, второй выход которого подключен к первому входу схемы сравнения, второй вход которой подключен ко второму входу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы, к которому подключены необходимые внешние устройства (модули).

Недостатком резервированной двухпроцессорной вычислительной системы является отсутствие системы самодиагностики для обнаружения неисправности и холодного резерва, который обеспечивает повышение надежности в случае воздействия внешнего разрушительного потока частиц и излучений.

Наиболее близкой по технической сущности к изобретению является система, которая состоит из двух каналов 1.1, 1.2 резервирования каждый из которых содержит блок 2 процессора, блок 3 последовательного интерфейса, блок 4 памяти, блок 5 ввода-вывода, шину 6 последовательного интерфейса, локальную шину 7, системную шину 8, блока 9 общей памяти и шин 10, 11 ввода-вывода.

В системе используется режим мультипроцессирования - работы двух блоков процессора в структуре с общей памятью. Такой режим позволяет процессорам обмениваться результатами обработки при дублировании в параллельном интерфейсе [2].

Описанная система как наиболее близкая к предполагаемому принята за прототип.

Недостатком резервированной двухпроцессорной вычислительной системы является отсутствие системы самодиагностики для обнаружения неисправности и холодного резерва, который обеспечивает повышение надежности в случае воздействия внешнего разрушительного потока частиц и излучений.

Задачей изобретения является повышение надежности в случае воздействия внешнего разрушительного потока частиц и излучений.

Текущий «горячий» резерв при воздействии внешнего разрушительного потока частиц и излучений выключается, и система переходит на дублированный резерв («холодный» резерв), который до момента неисправности находился в выключенном состоянии.

Система содержит устройство управления восстановлением YYB стойкого к данным воздействиям и регулярно заблаговременно копирует в него текущее рабочее состояние ВМ, что позволяет не полностью повторять вычисления сначала, а продолжать от успешно законченного этапа выполняемой программы.

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1-57, где:

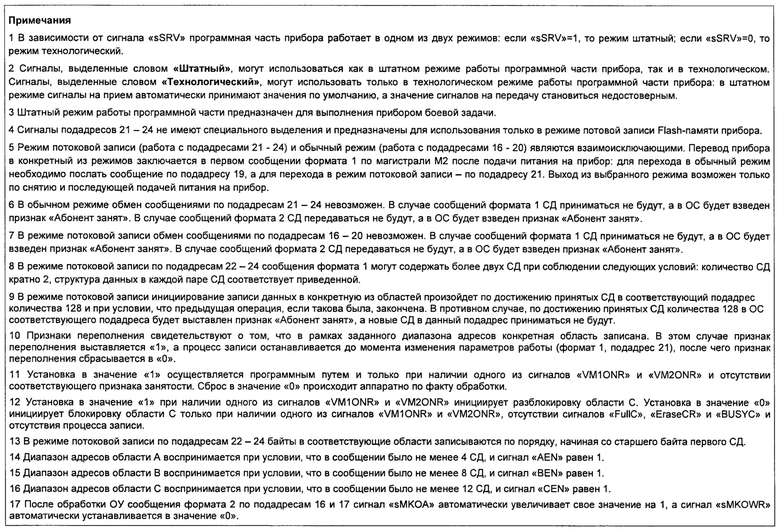

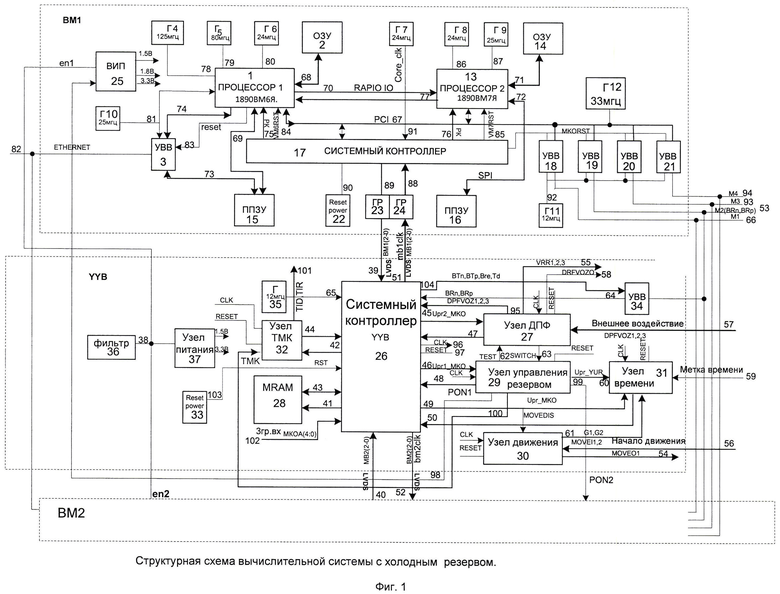

• на фиг.1 представлена структурная схема вычислительной системы с холодным резервом:

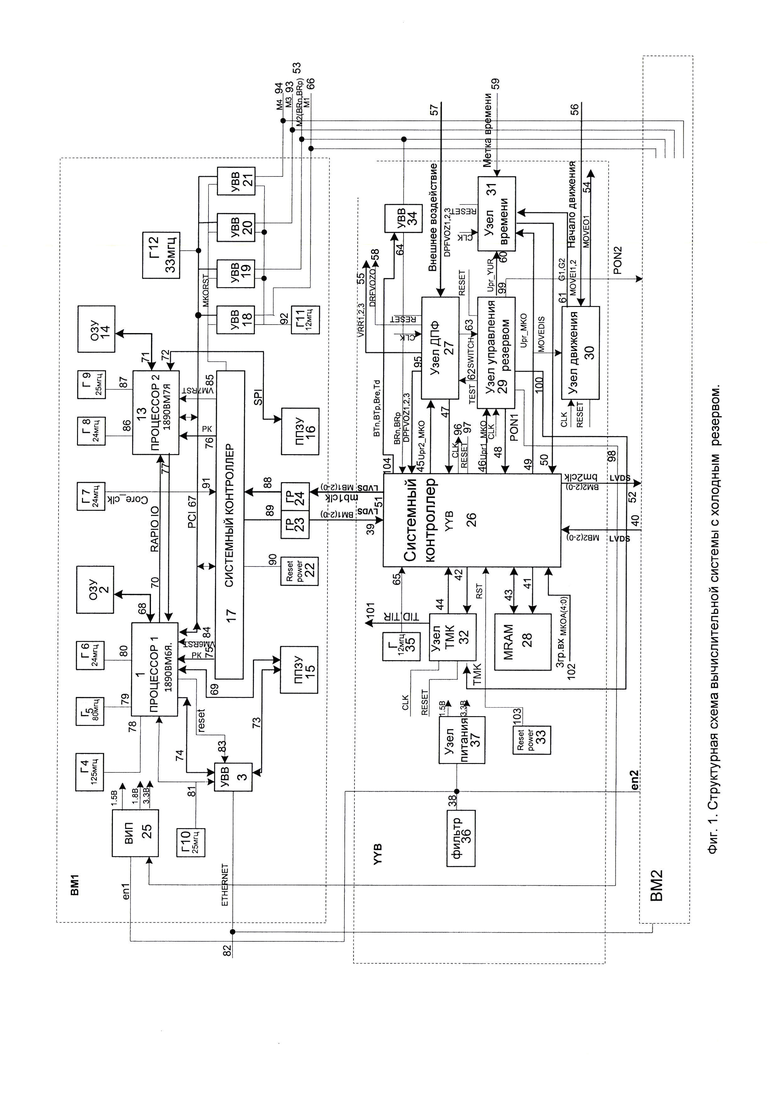

• на фиг.2 представлена функциональная схема системного контроллера ВМ;

• на фиг.3 представлена функциональная схема узла BM_REC;

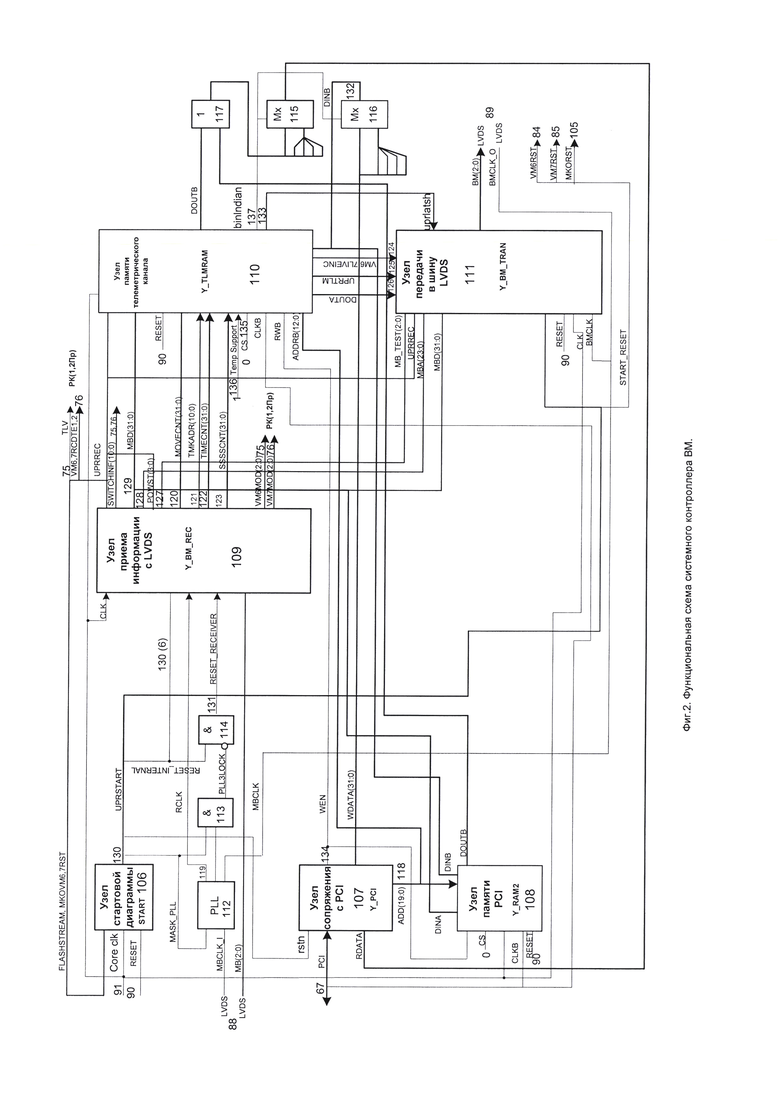

• на фиг.4 представлена функциональная схема узла BM_TRAN;

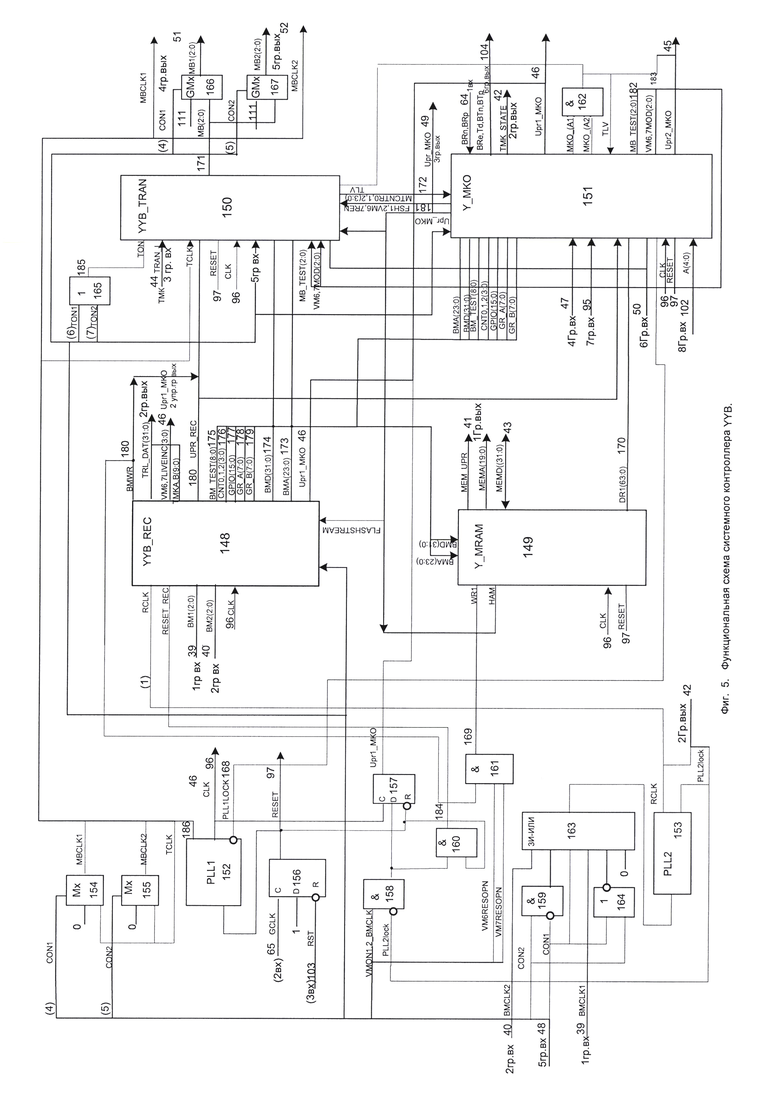

• на фиг.5 представлена функциональная схема системного контроллера УУВ;

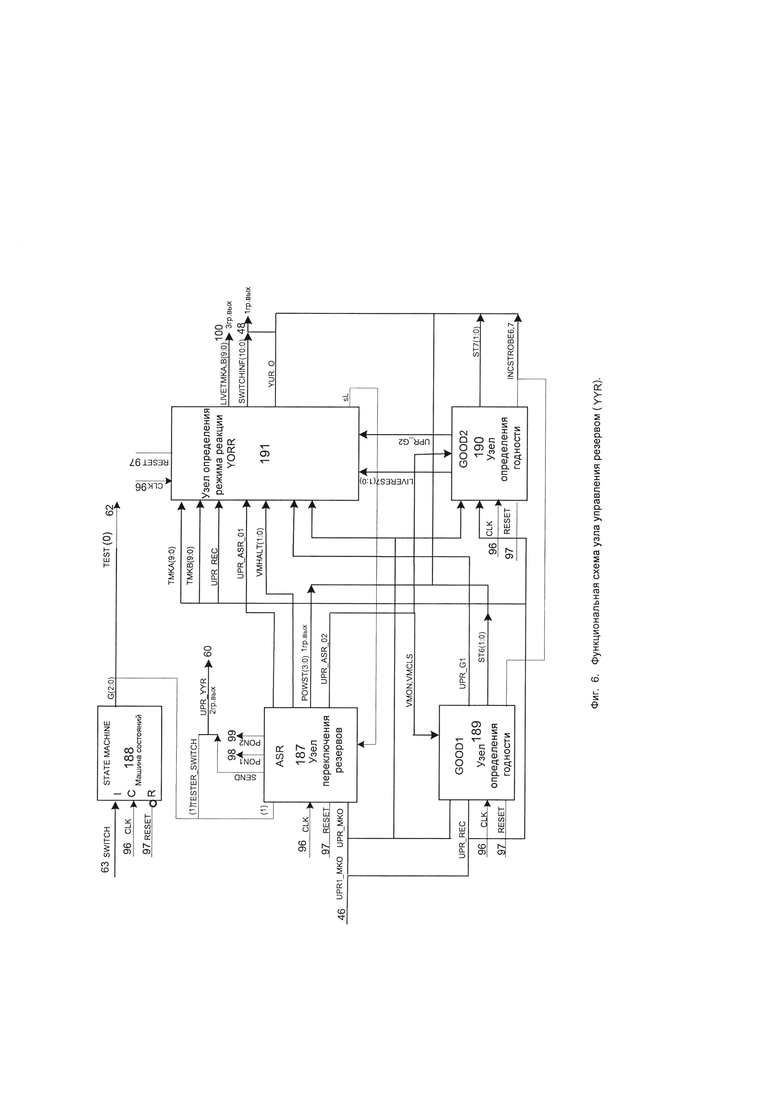

• на фиг.6 представлена функциональная схема узла управления резервом (YYR);

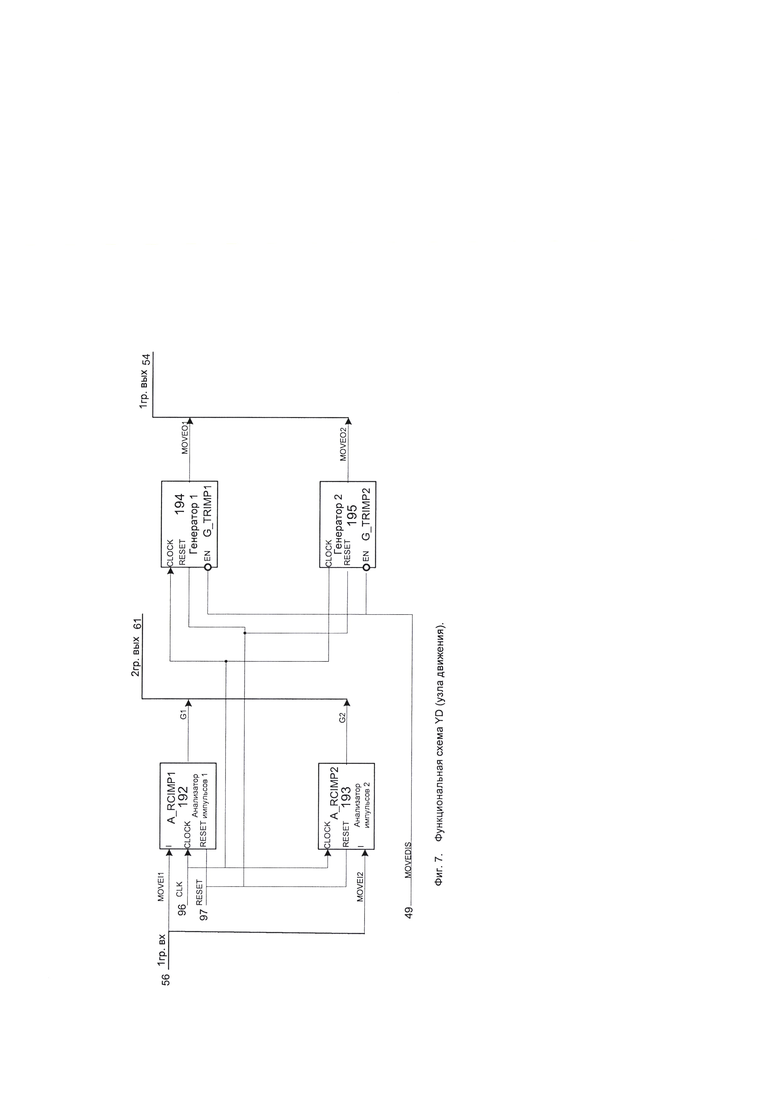

• на фиг.7 представлена функциональная схема узла движения (Y_D);

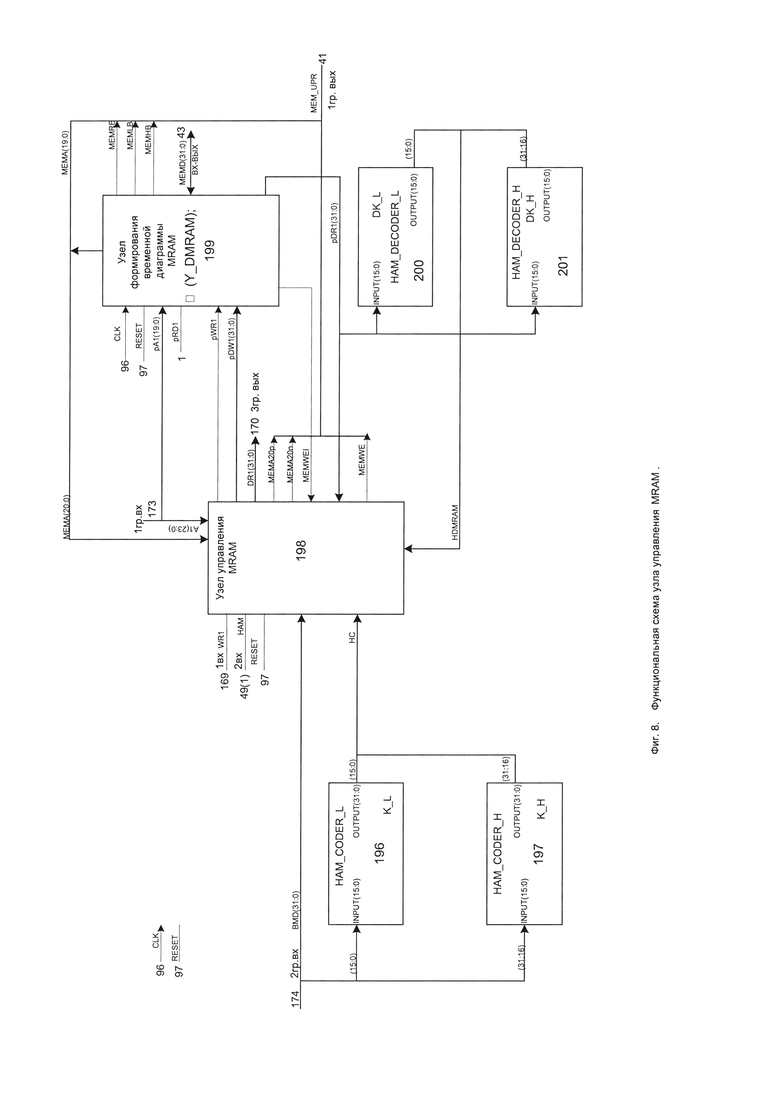

• на фиг.8 представлена функциональная схема узла управления MRAM;

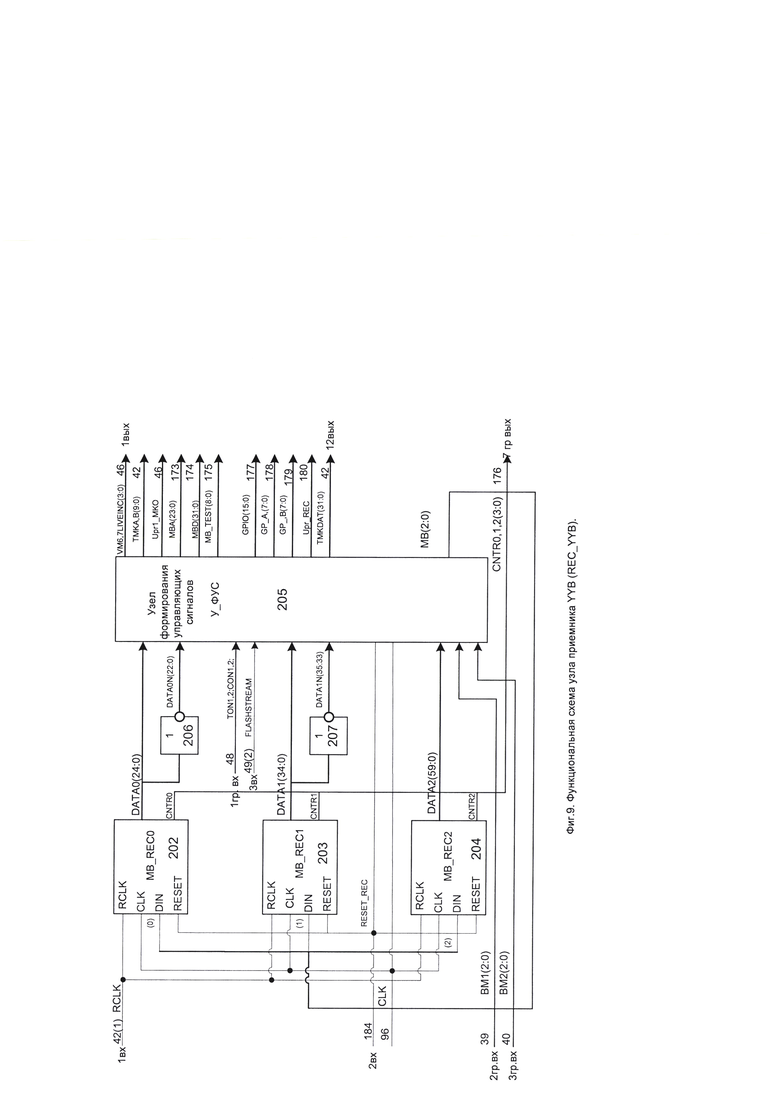

• на фиг.9 представлена функциональная схема узла приемника (YYB_REC);

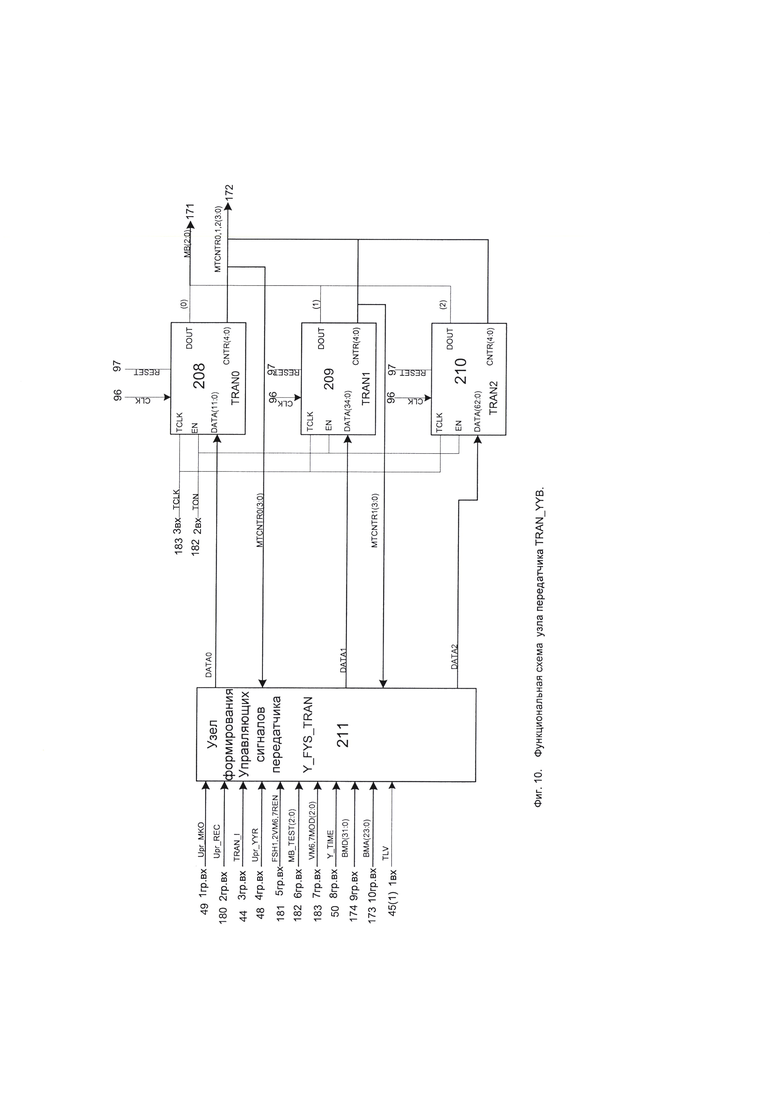

• на фиг.10 представлена функциональная схема узла передатчика (YYB_TRAN);

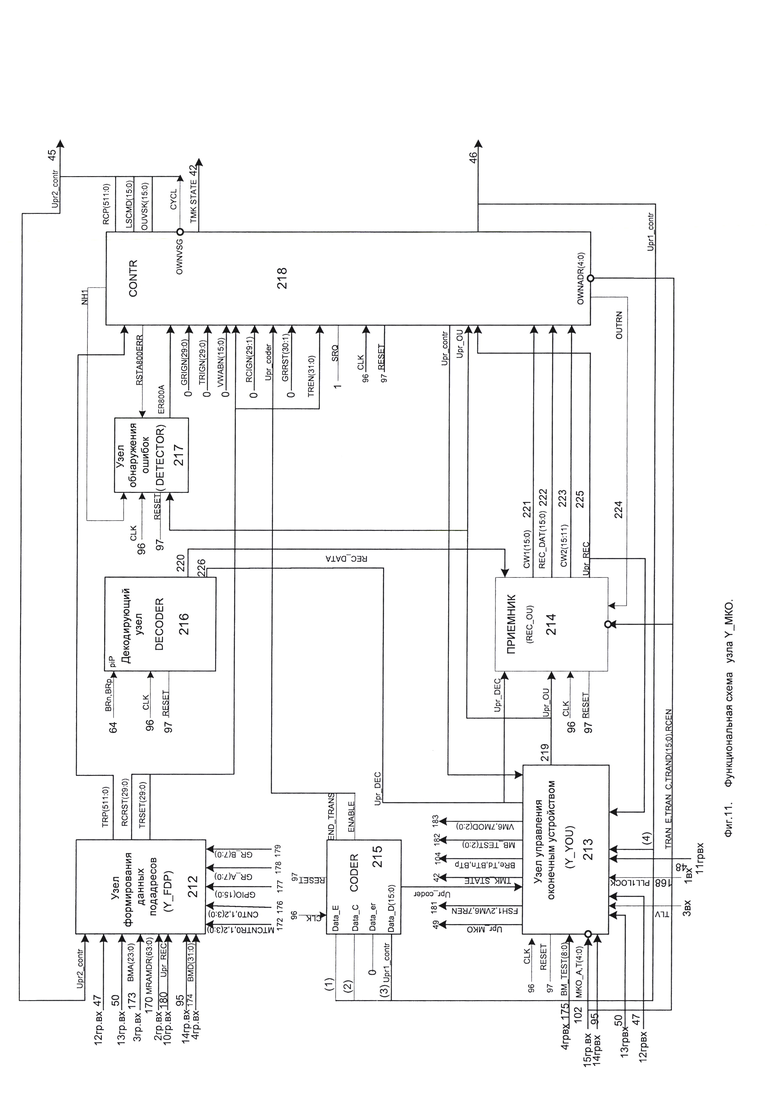

• на фиг.11 представлена функциональная схема узла МКО;

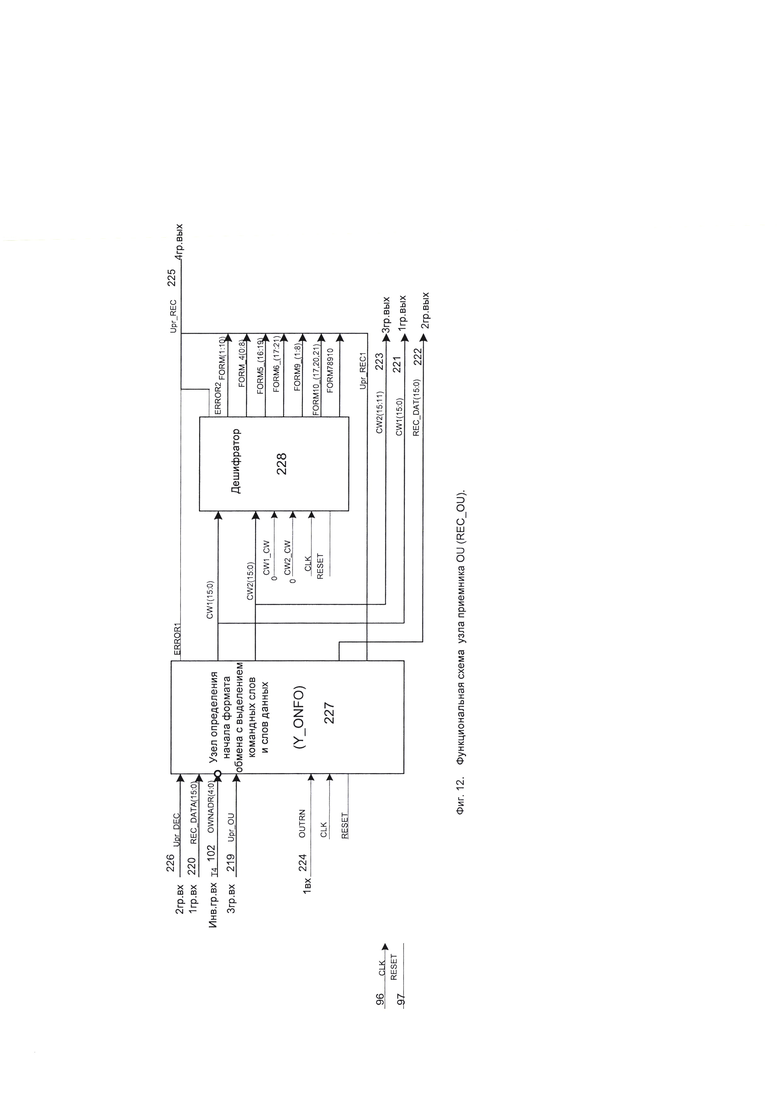

• на фиг.12 представлена функциональная схема узла приемника OU (REC_OU);

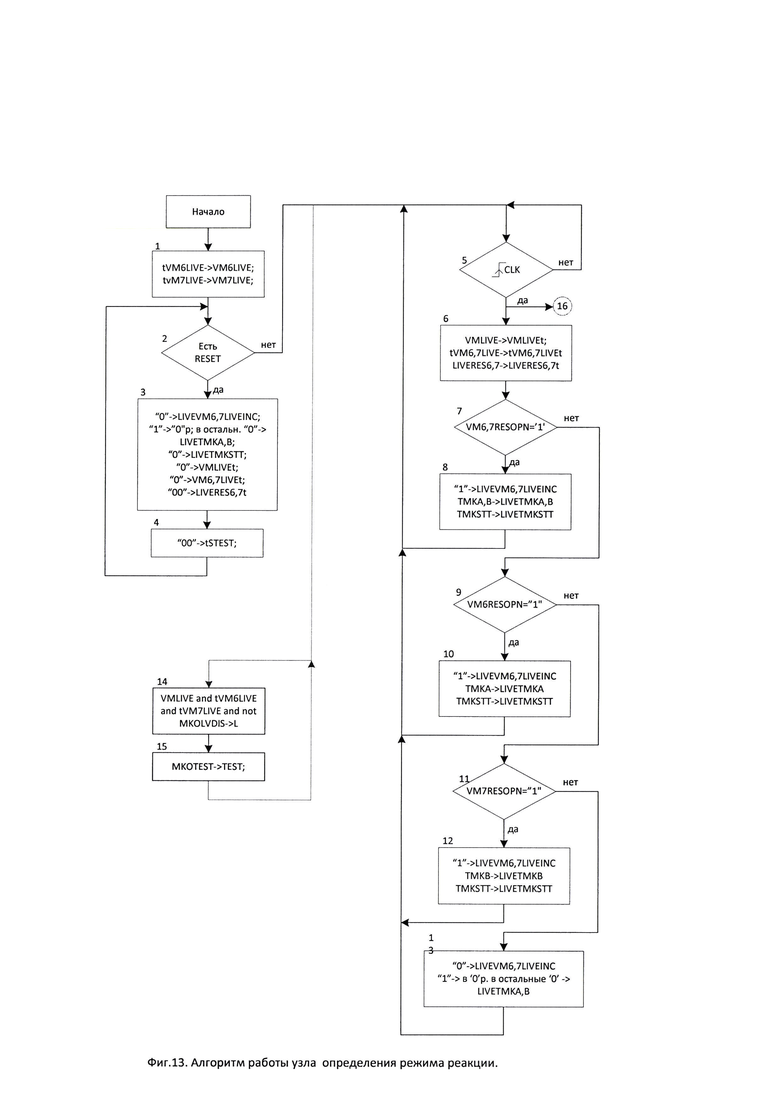

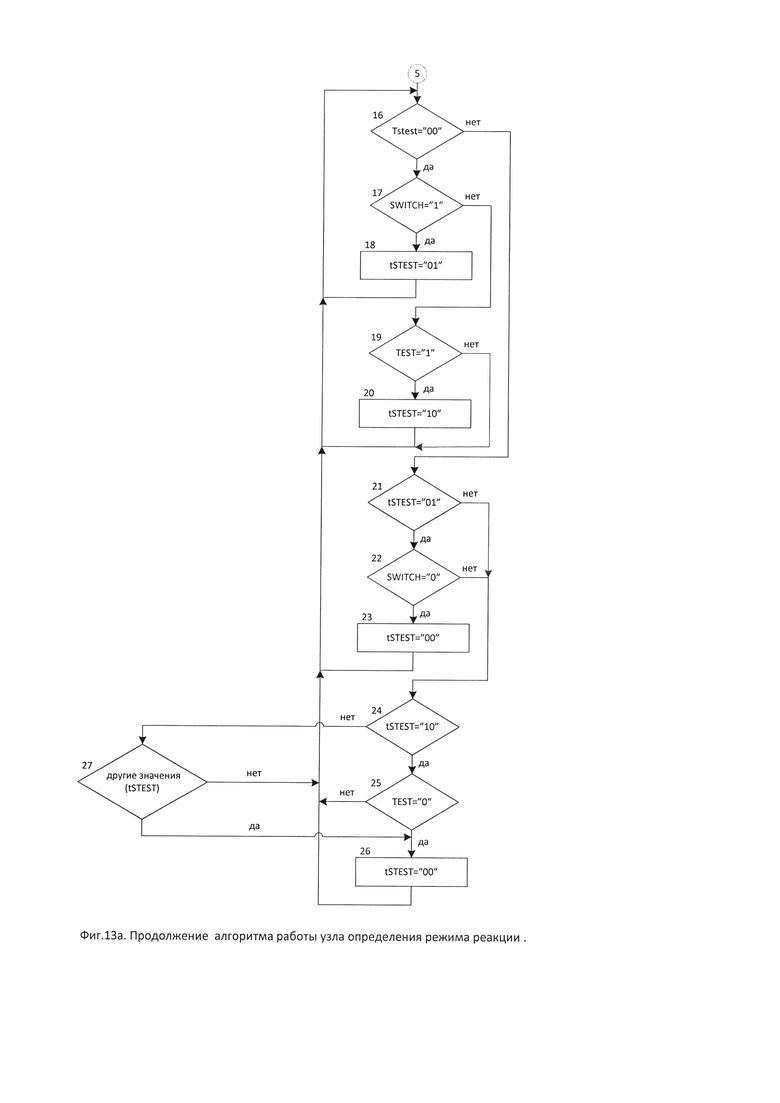

• на фиг.13 представлен алгоритм работы узла определения режима реакции;

• на фиг.13а представлено продолжение алгоритма работы узла определения режима реакции;

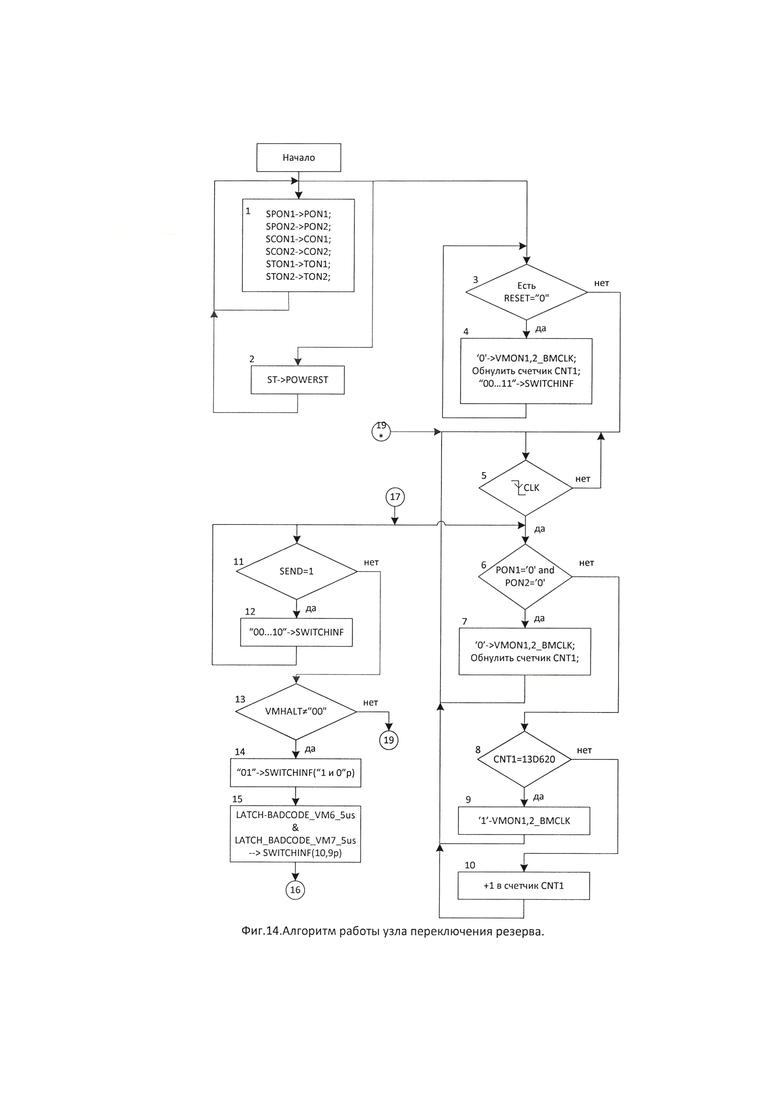

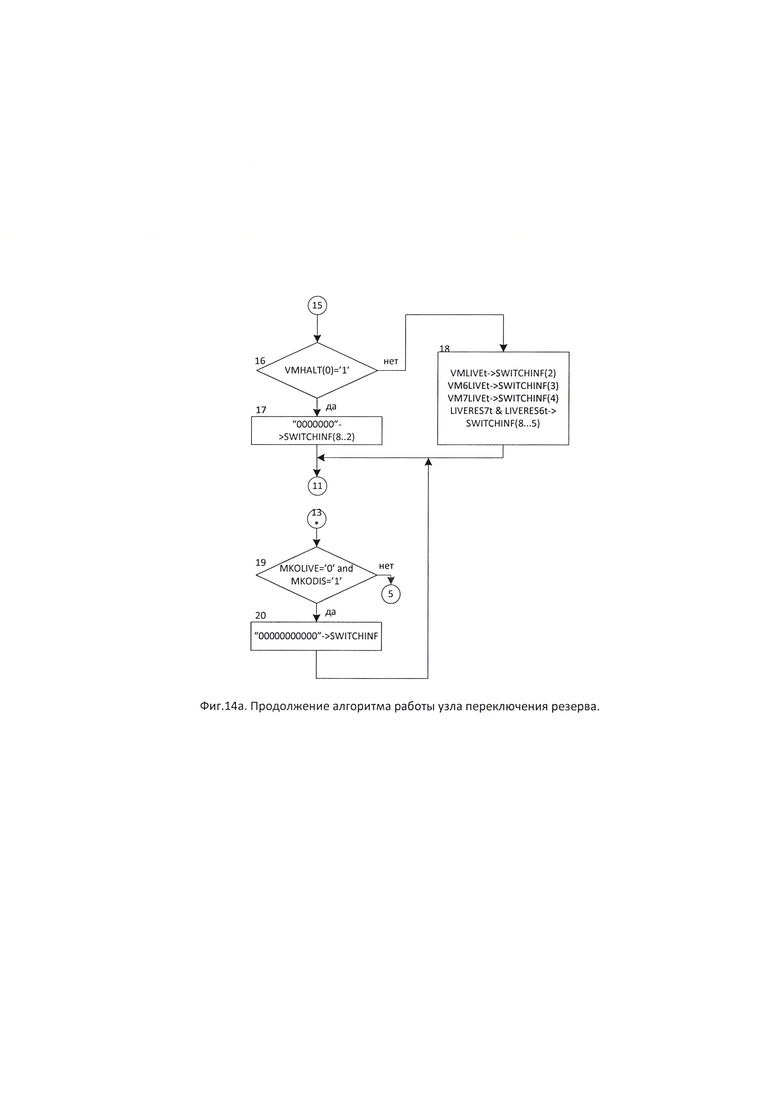

• на фиг.14 представлен алгоритм работы узла переключения резерва;

• на фиг.14а представлено продолжение алгоритма работы узла переключения резерва;

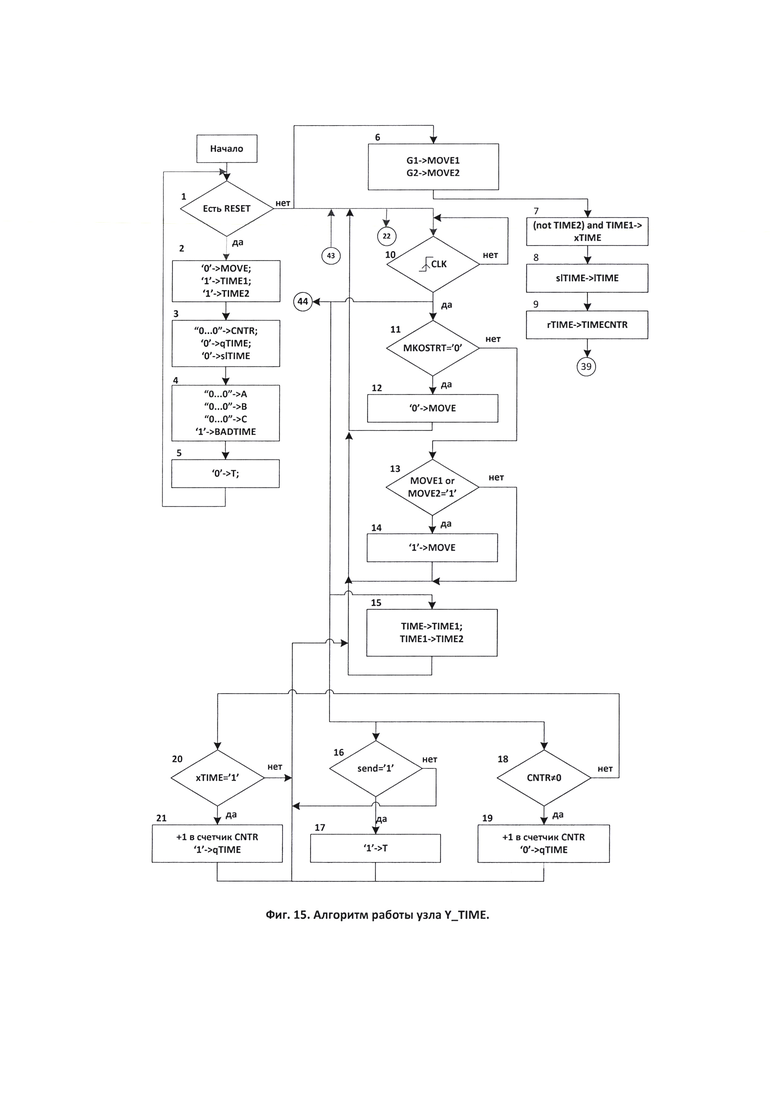

• на фиг.15 представлен алгоритм работы узла времени Y_TIME 31;

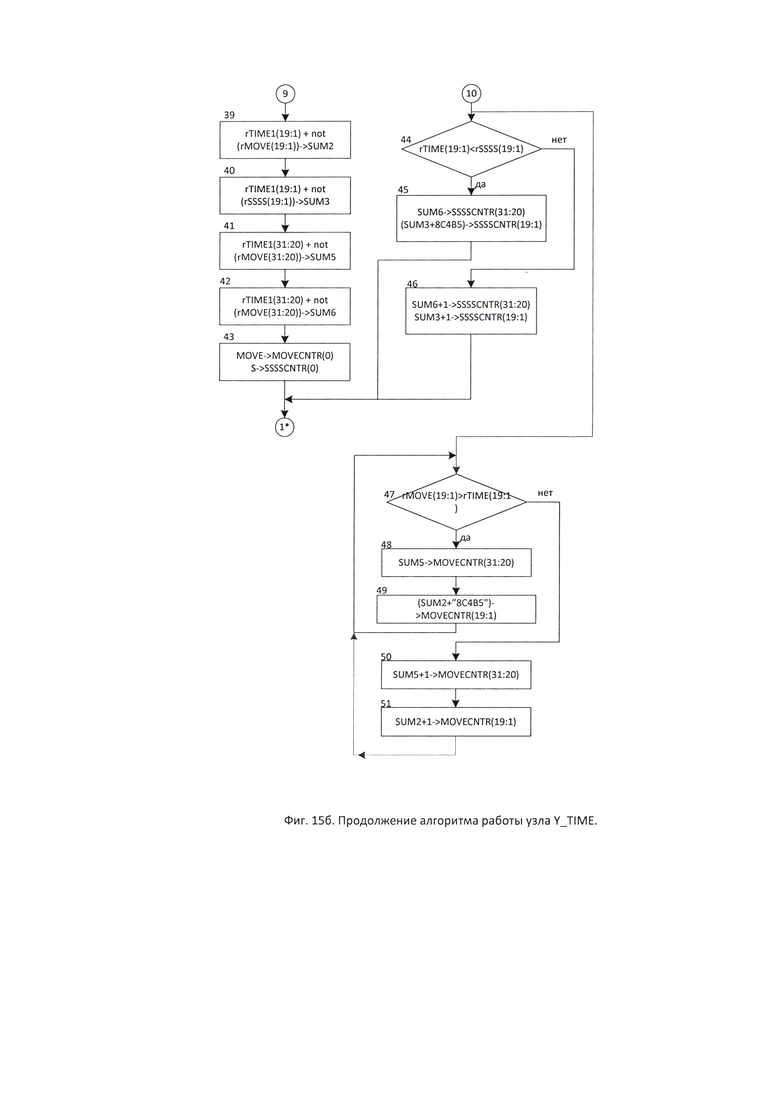

• на фиг.15а представлено продолжение алгоритма работы узла времени Y_TIME 31;

• на фиг.15б представлено продолжение алгоритма работы узла времени Y_TIME 31;

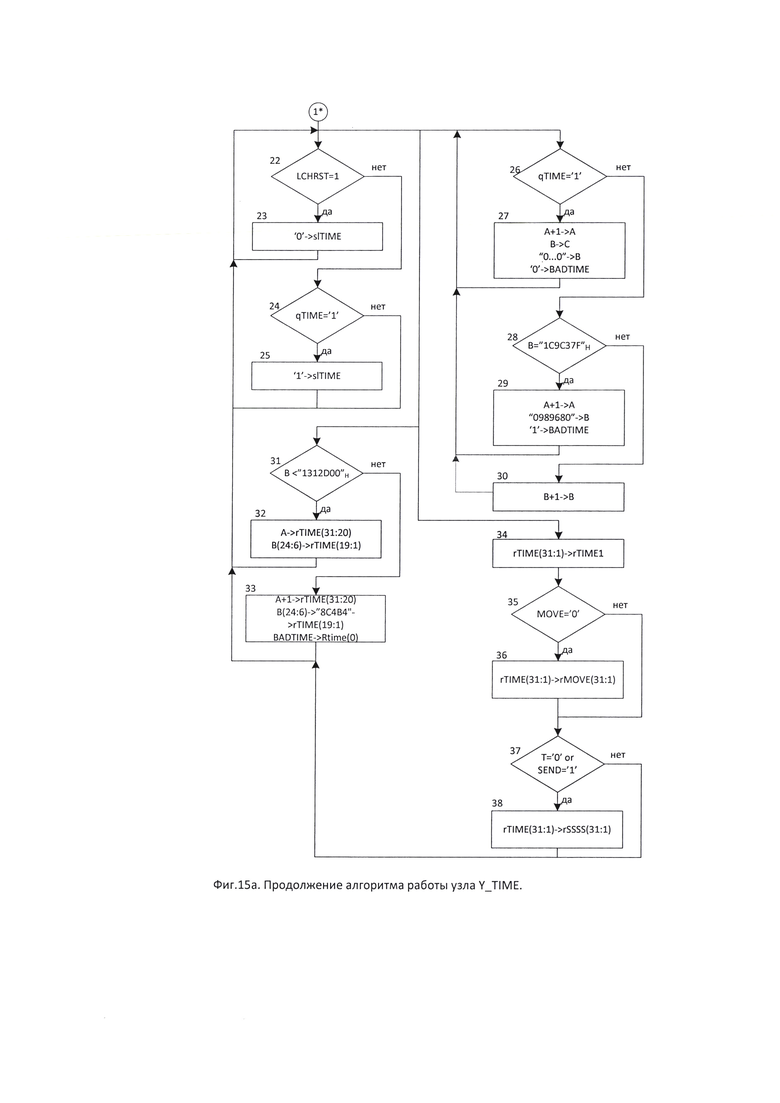

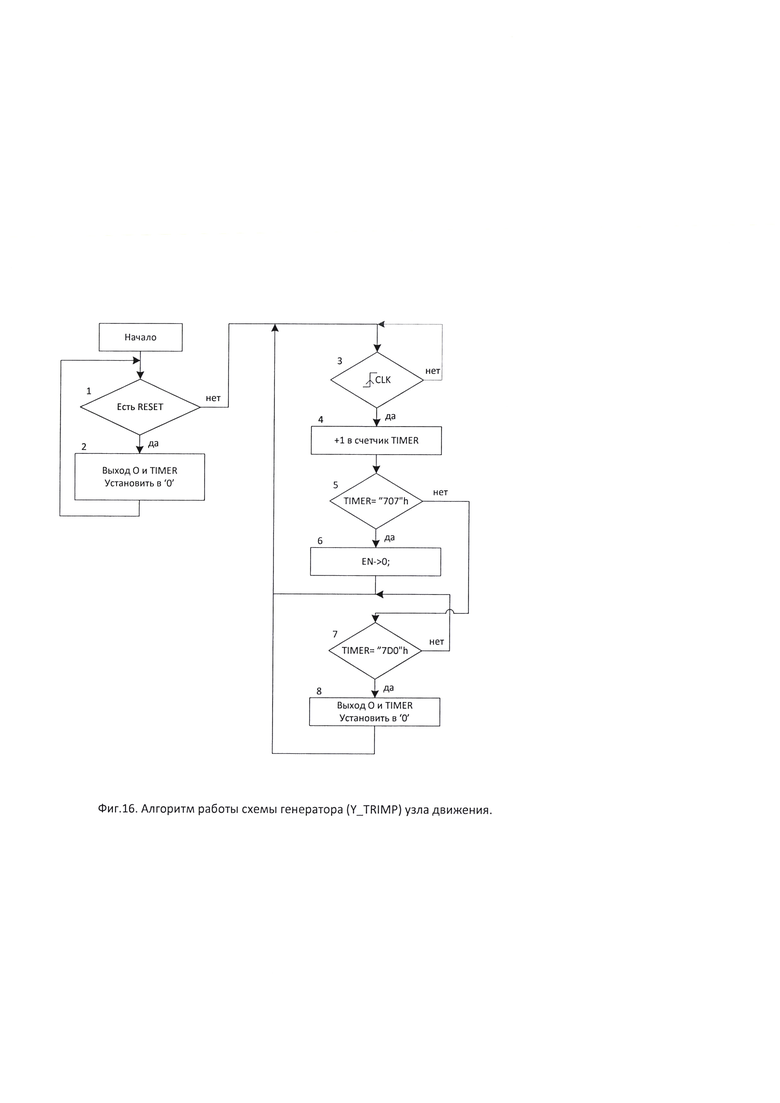

• на фиг.16 представлен алгоритм работы схемы Y_TRIMP узла движения 30:

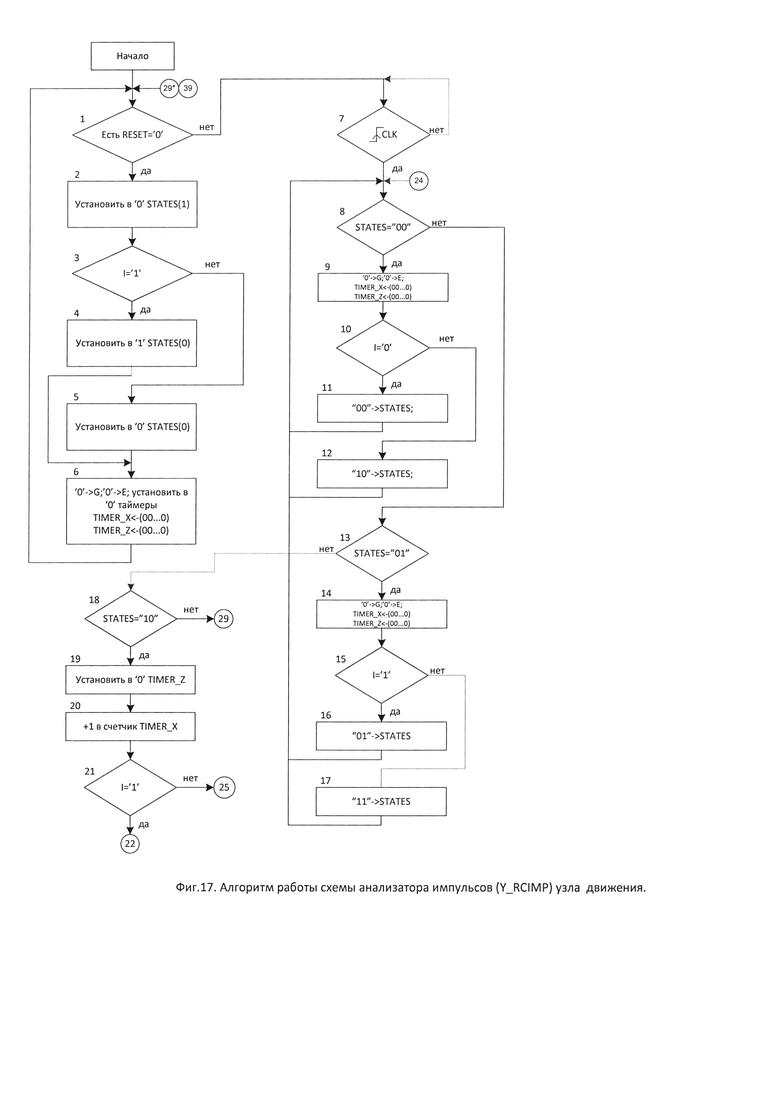

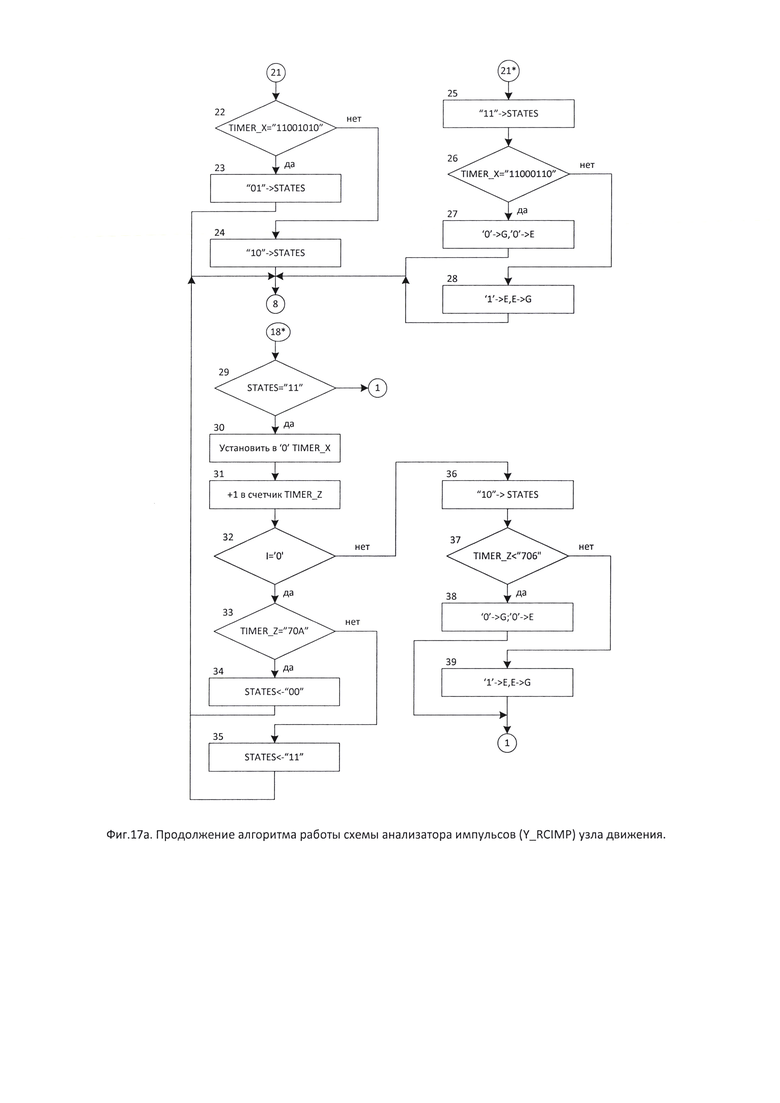

• на фиг.17 представлен алгоритм работы схемы Y_RCIMP узла движения 30:

• на фиг.17а представлено продолжение алгоритма работы схемы Y_RCIMP узла движения 30:

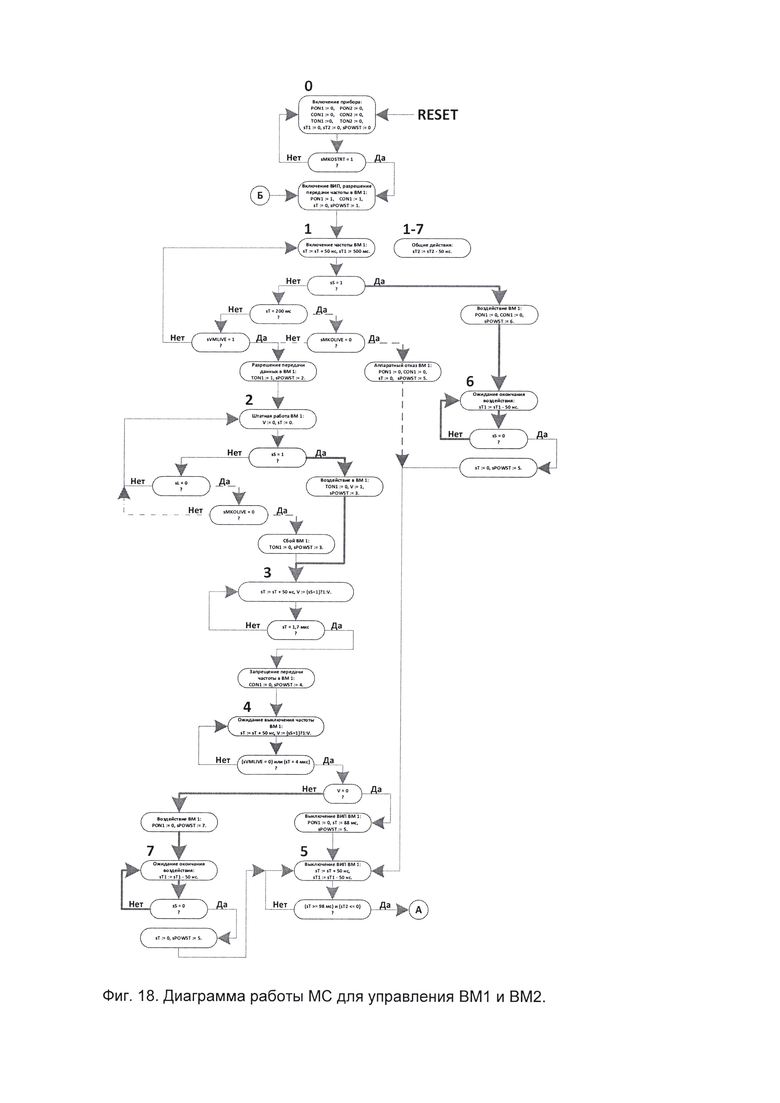

• на фиг.18 представлена диаграмма МС для управления ВМ1 и ВМ2;

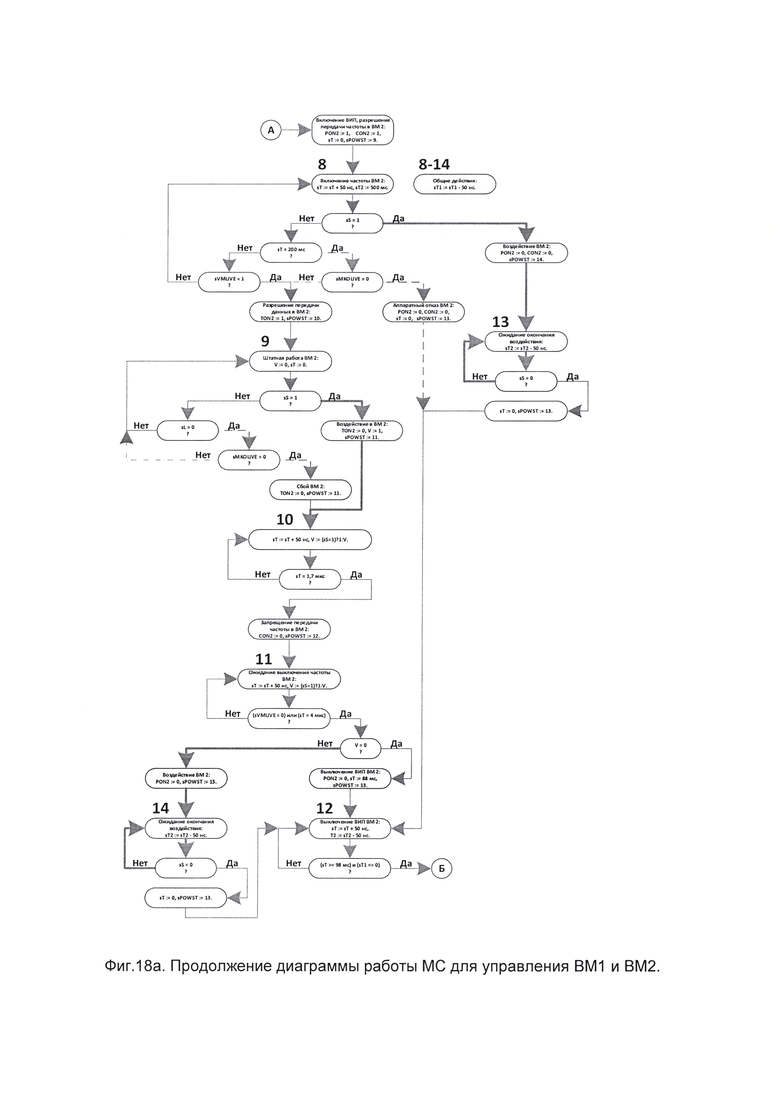

• на фиг.18а представлено продолжение диаграммы МС для управления ВМ1 и ВМ2;

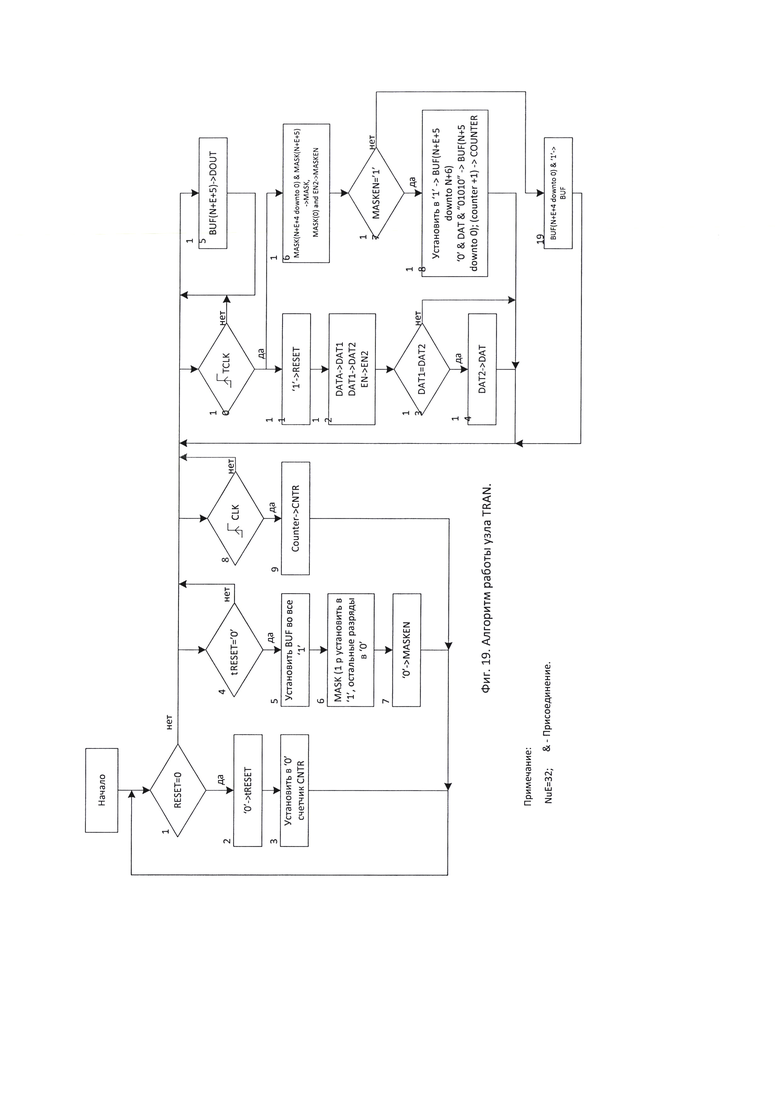

• на фиг.19 представлен алгоритм работы TRAN передатчика:

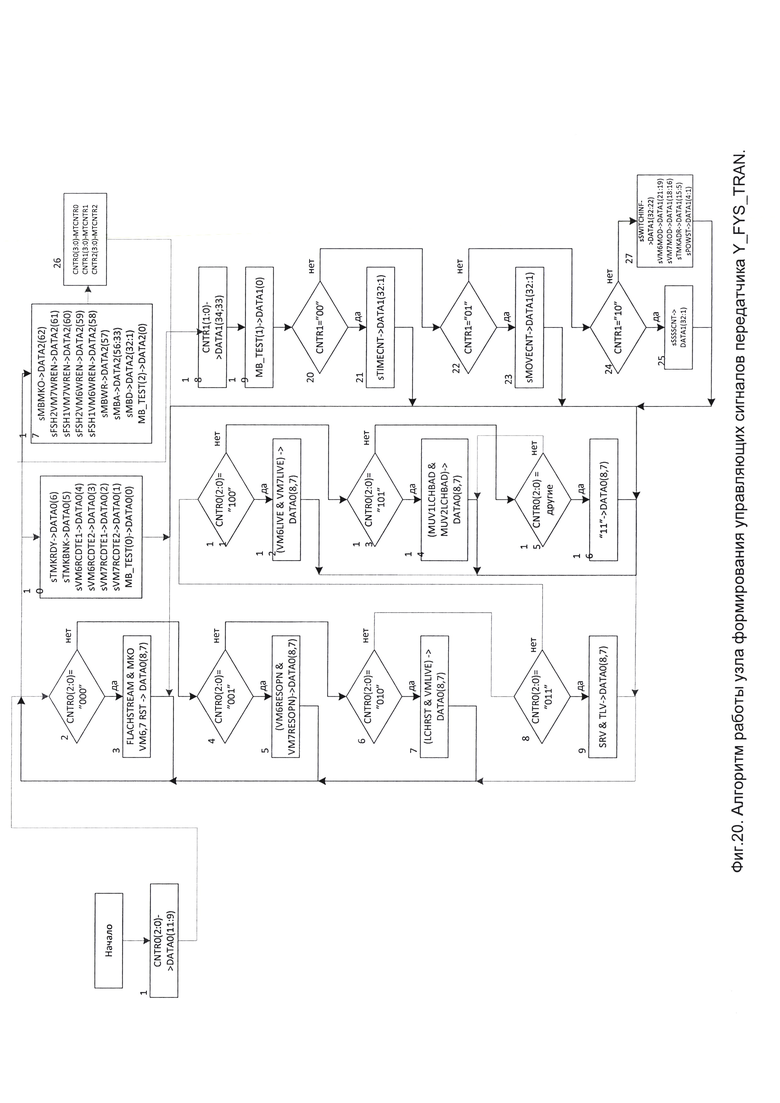

• на фиг.20 представлен алгоритм работы узла формирования управляющих сигналов передатчика Y_FYS_TRAN;

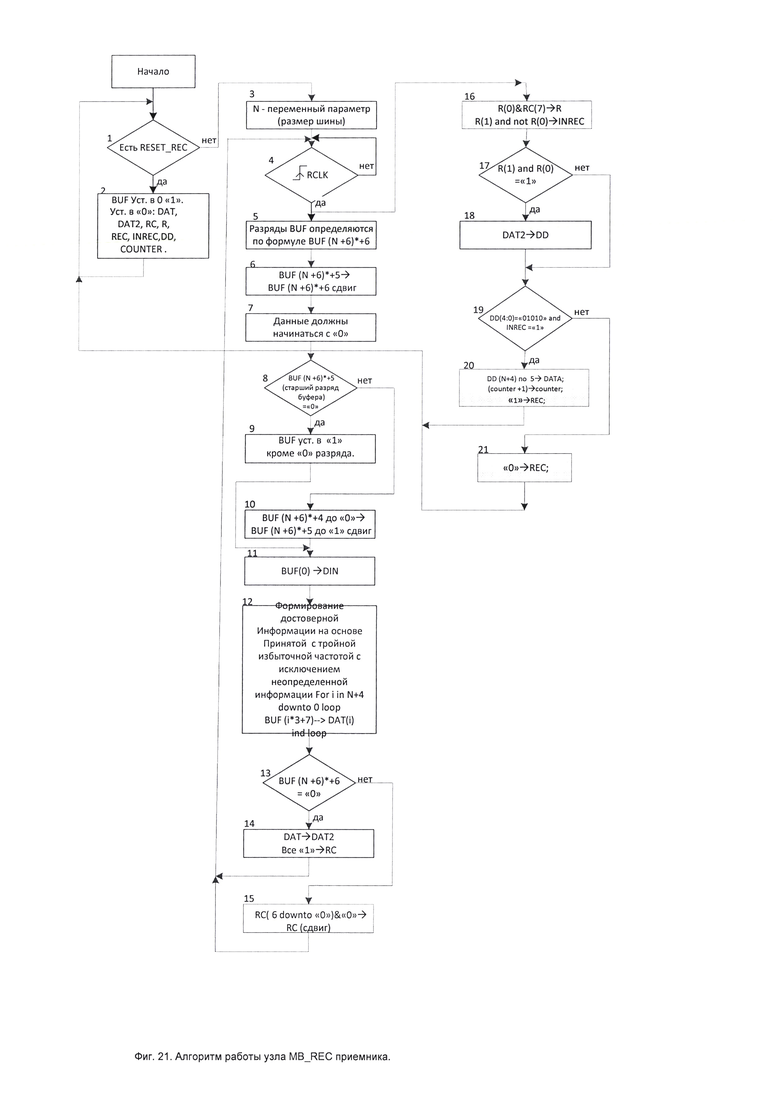

• на фиг.21 представлен алгоритм работы узла BM_REC приемника;

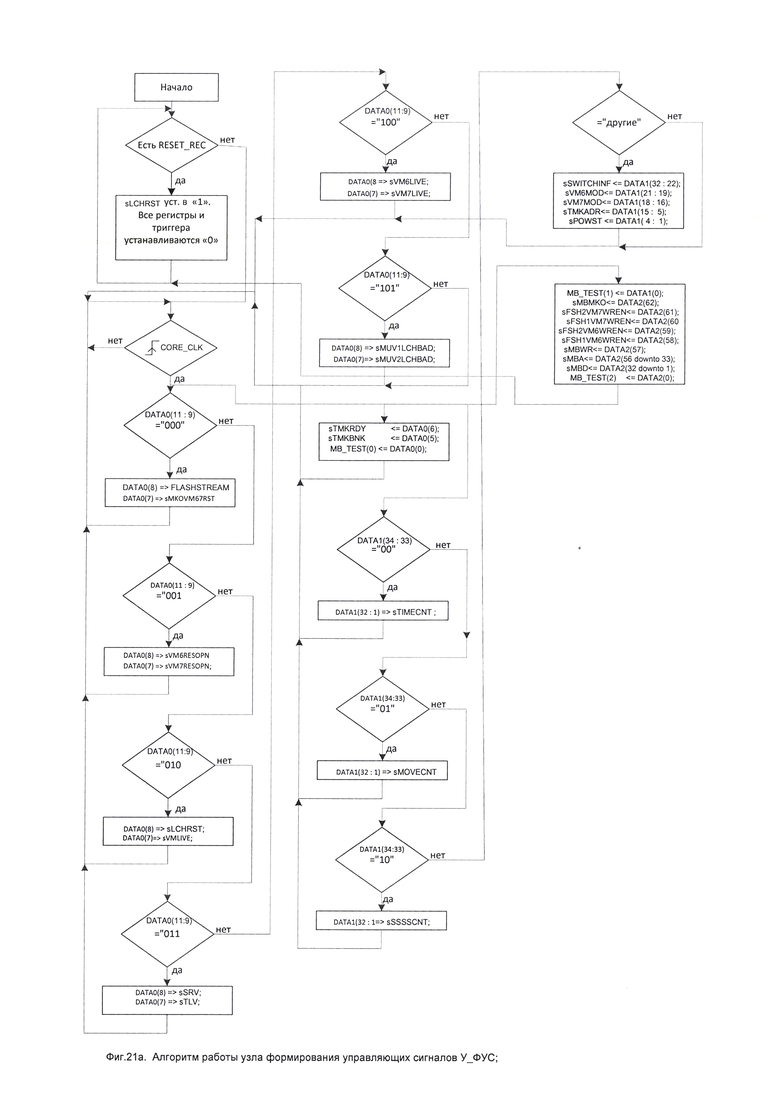

• на фиг.21а представлен алгоритм работы узла формирования управляющих сигналов У_ФУС;

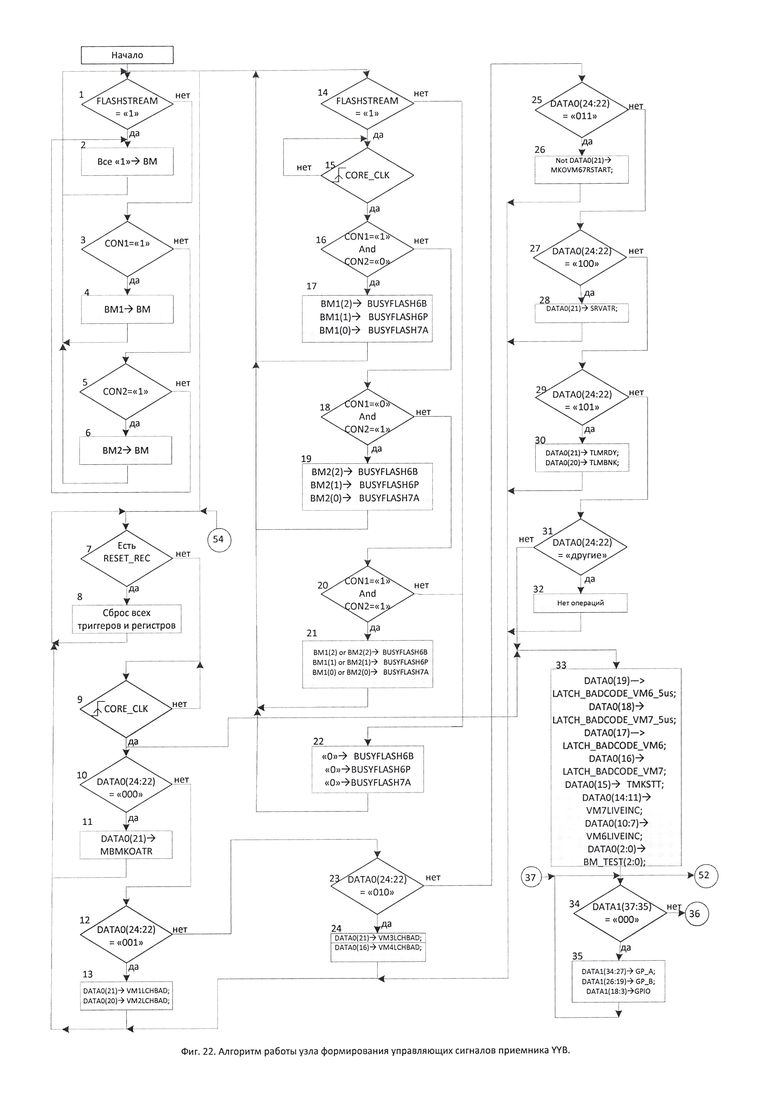

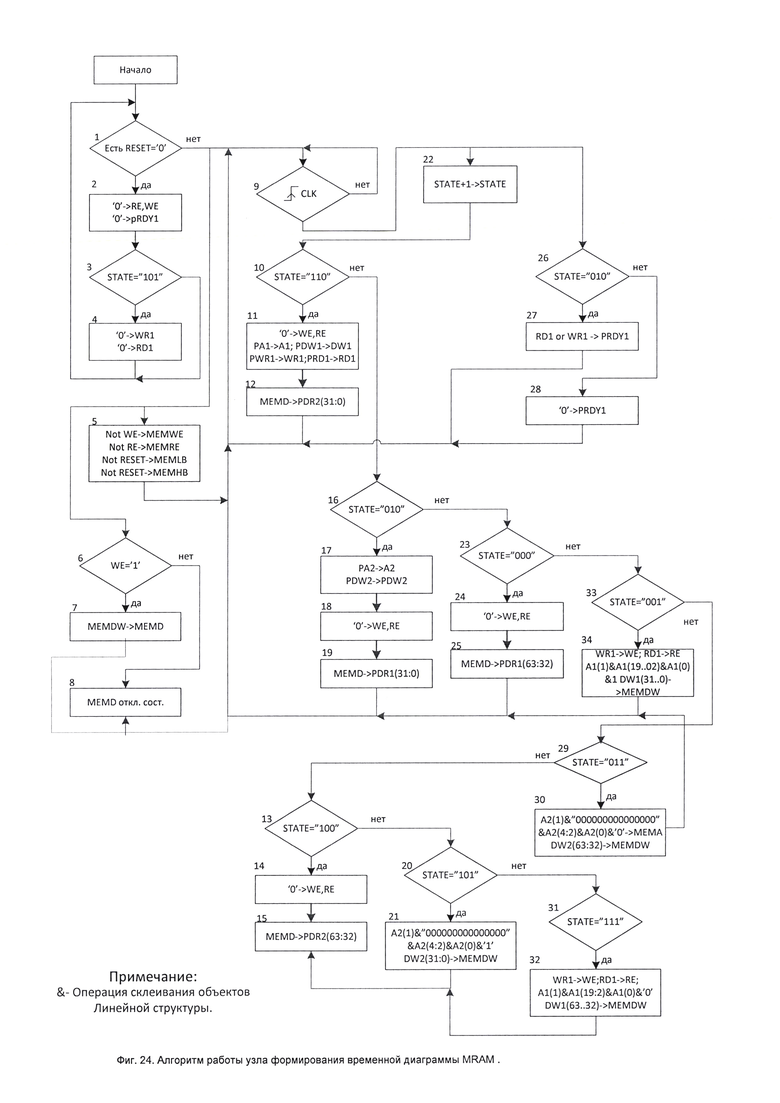

• на фиг.22, 22а представлены алгоритмы работы узлов формирования управляющих сигналов приемника YYB.

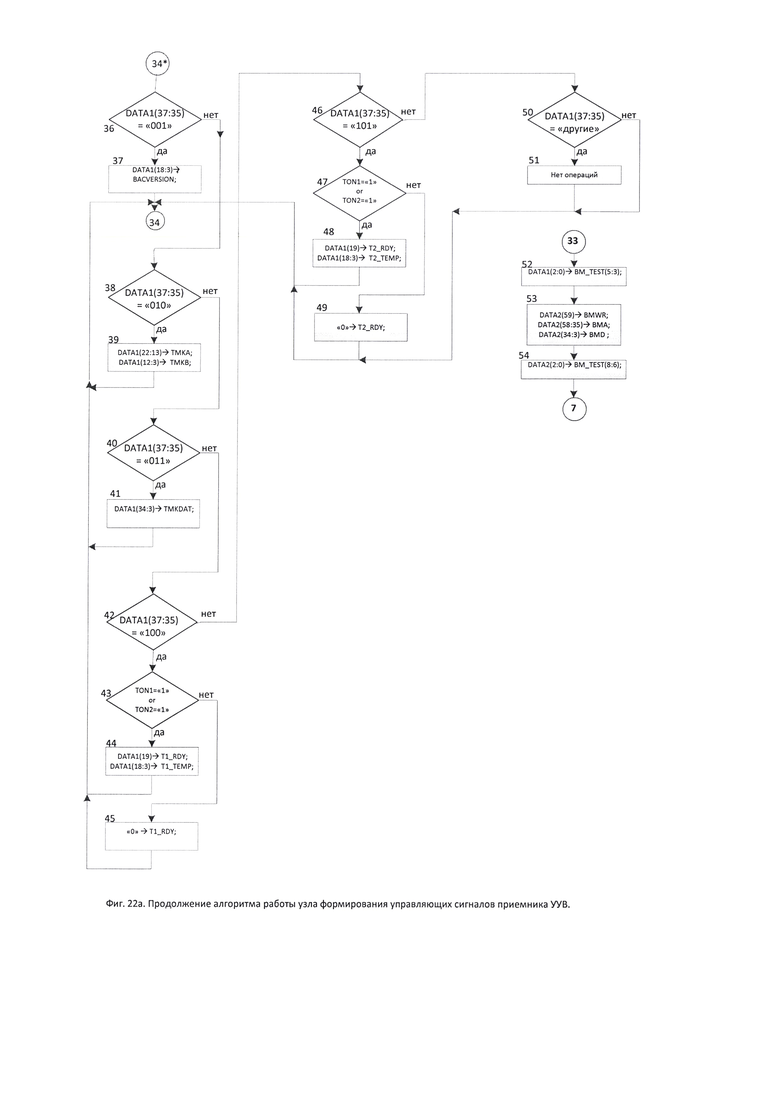

• на фиг.23 представлен алгоритм узла управления MRAM;

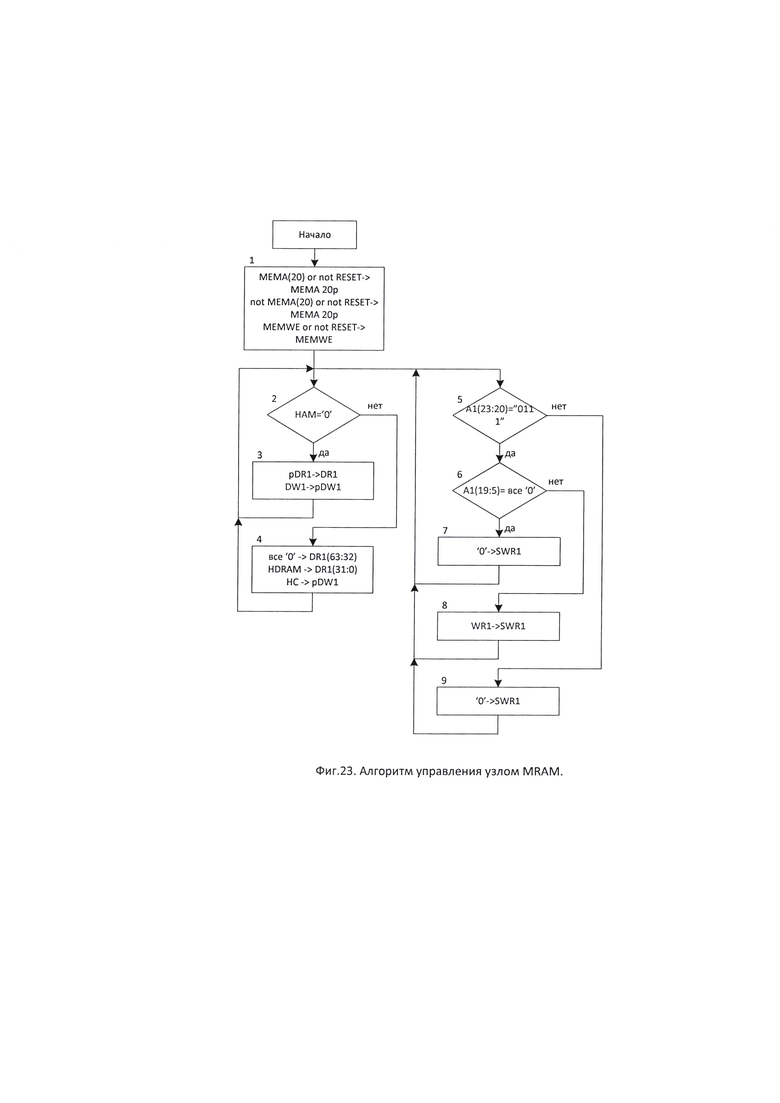

• на фиг.24 представлен алгоритм работы узла формирования временной диаграммы MRAM (Y_DMRAM);

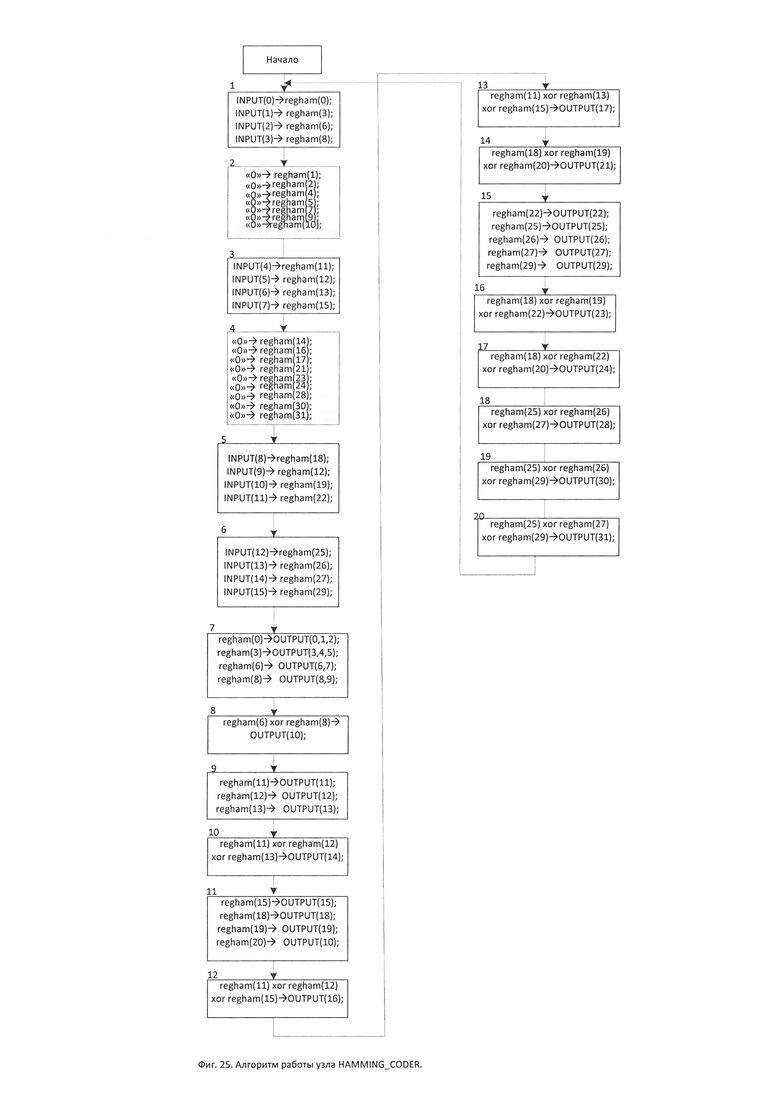

• на фиг.25 представлен алгоритм работы узлов HAMMING_CODER (кодер_L 196, кодер_L 197;

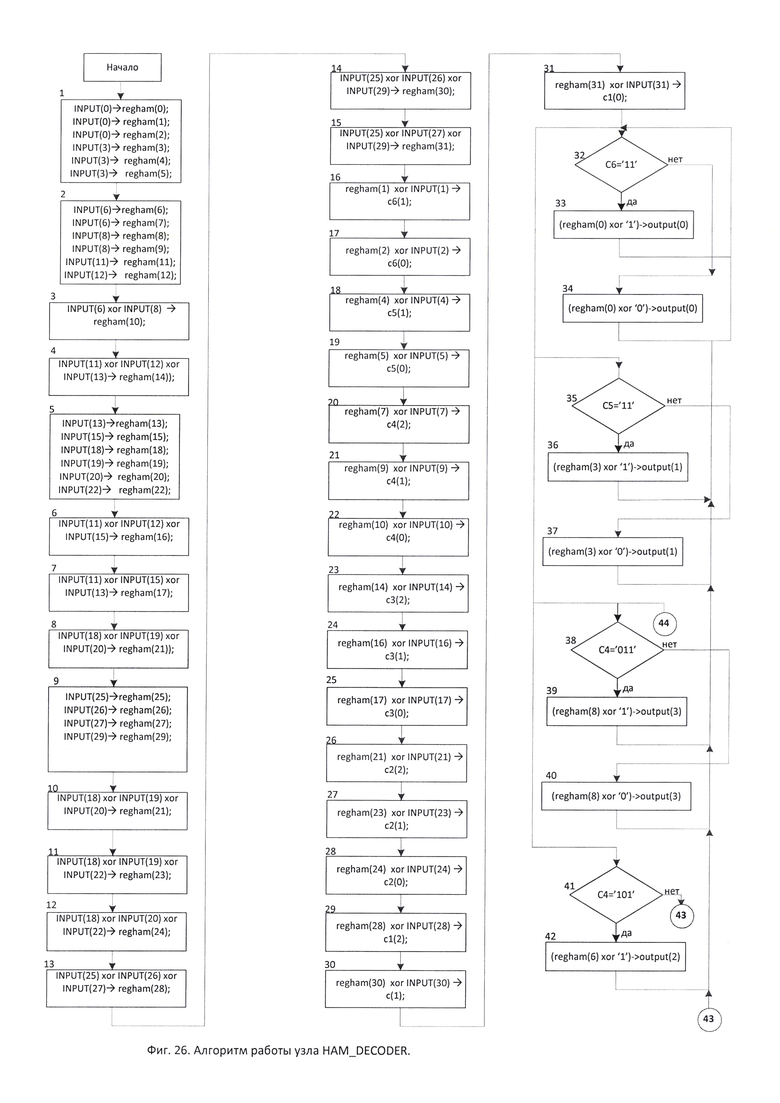

• на фиг.26 представлен алгоритм работы узлов HAMMING_DECODER 197,198;

• на фиг.26а представлено продолжение алгоритма работы узлов HAMMING_DECODER;

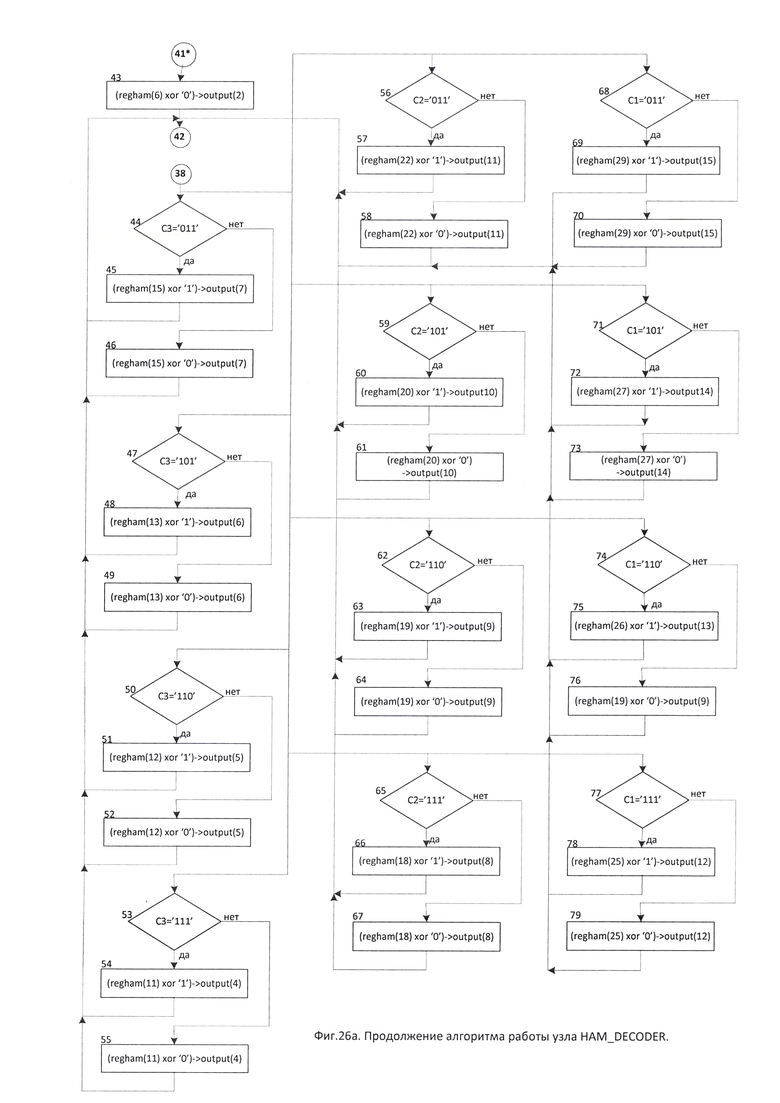

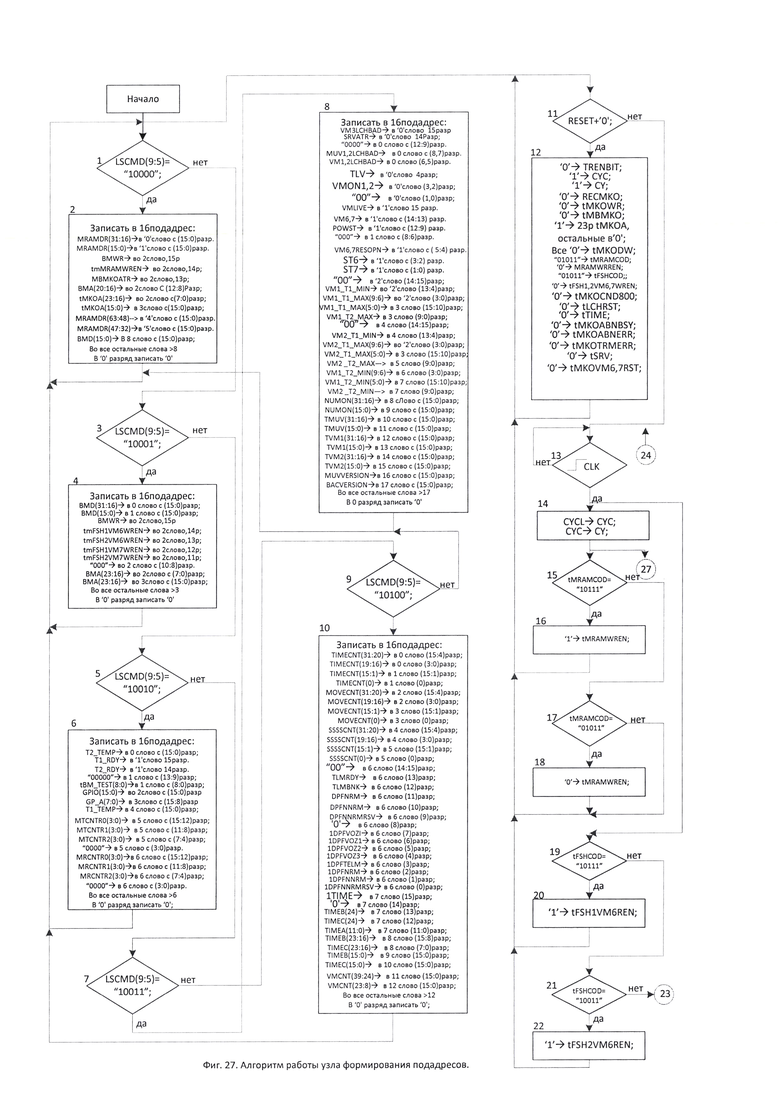

• на фиг.27 представлен алгоритм работы узла формирования подадресов;

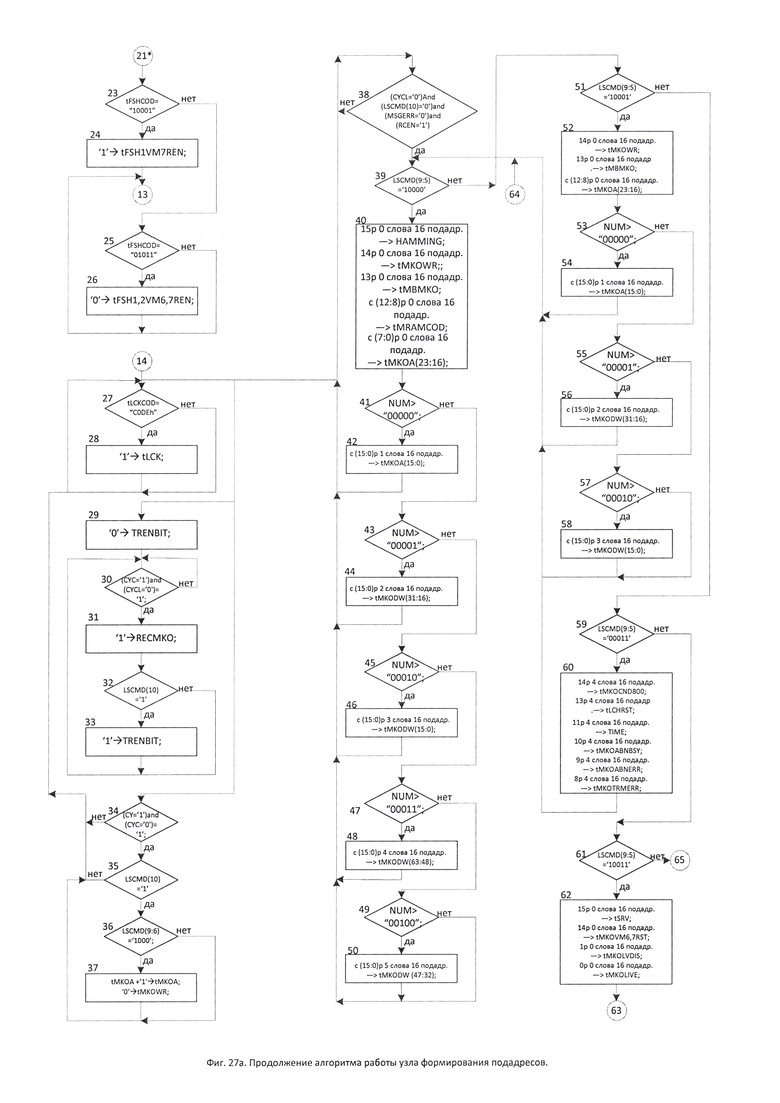

• на фиг.27а, б представлено продолжение алгоритма работы узла формирования подадресов;

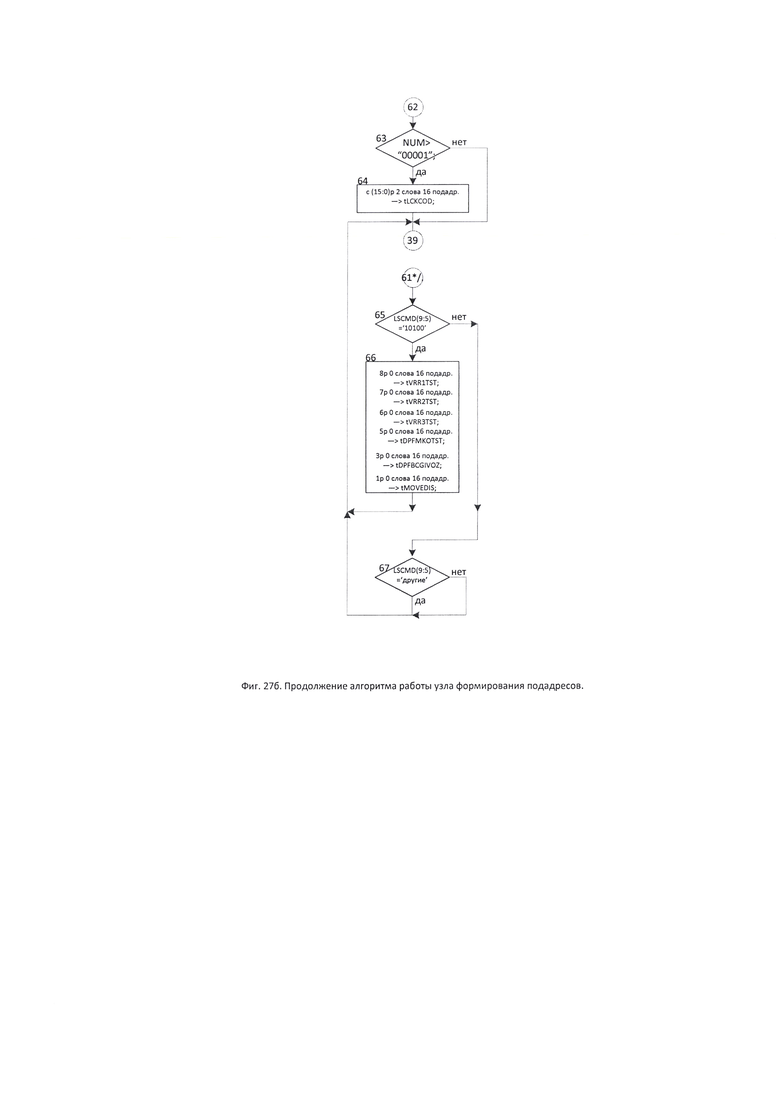

• на фиг.28 представлен алгоритм работы узла управления оконечным устройством (Y_YOU) 213;

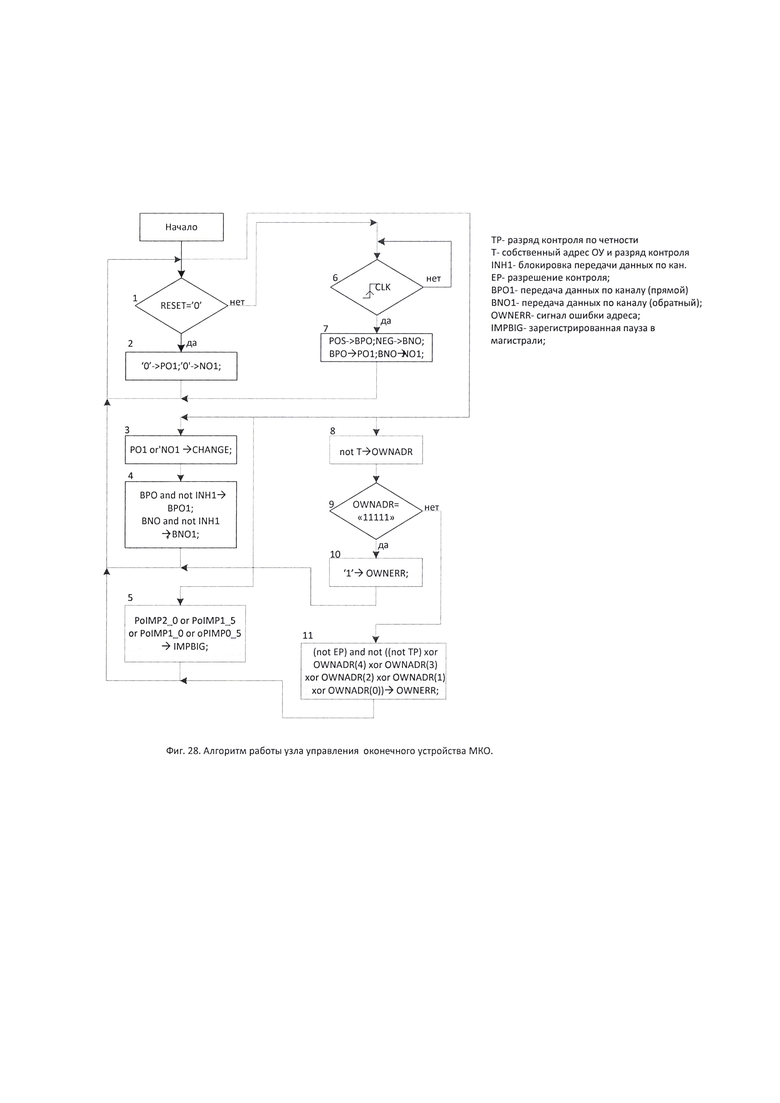

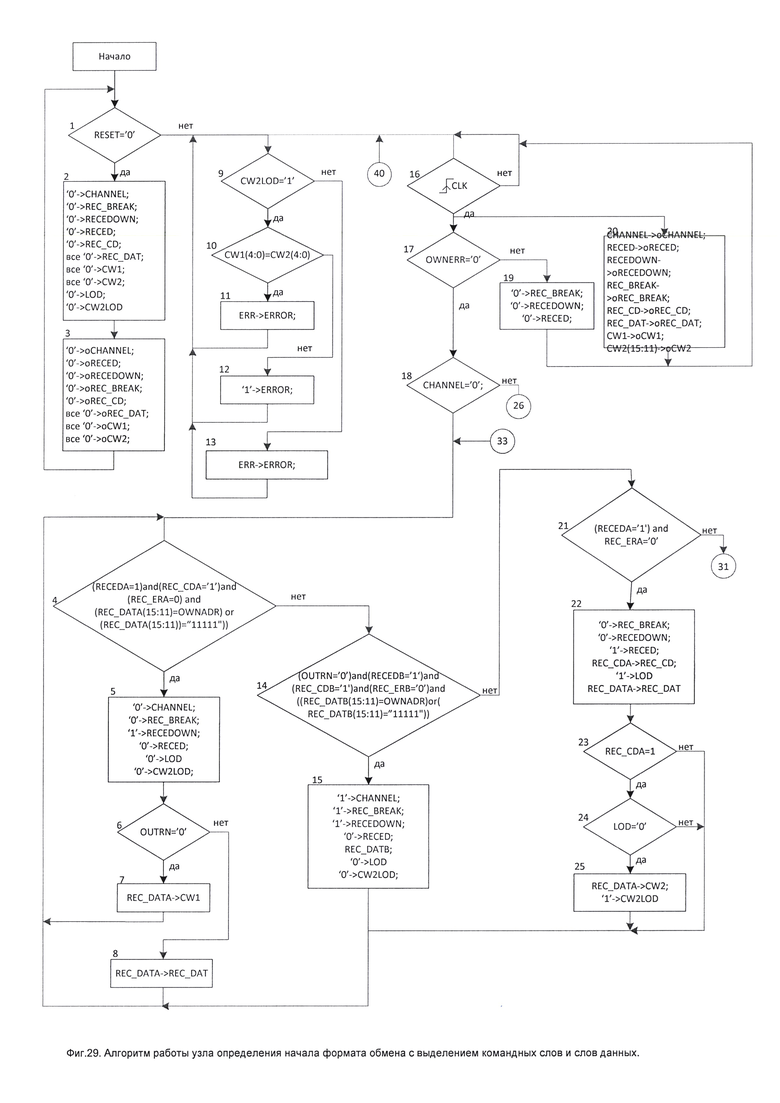

• на фиг.29 представлен алгоритм работы узла определения начала формата обмена с выделением командных слов и слов данных;

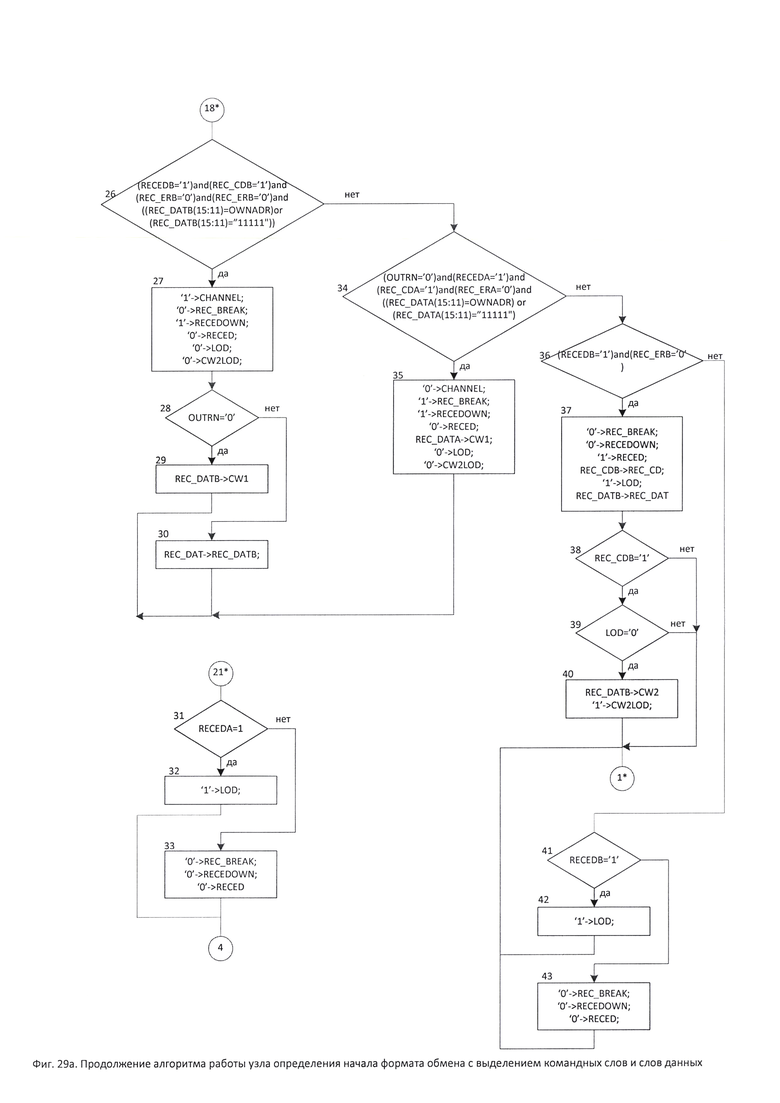

• на фиг.29а представлено продолжение алгоритма работы узла определения начала формата обмена с выделением командных слов и слов данных;

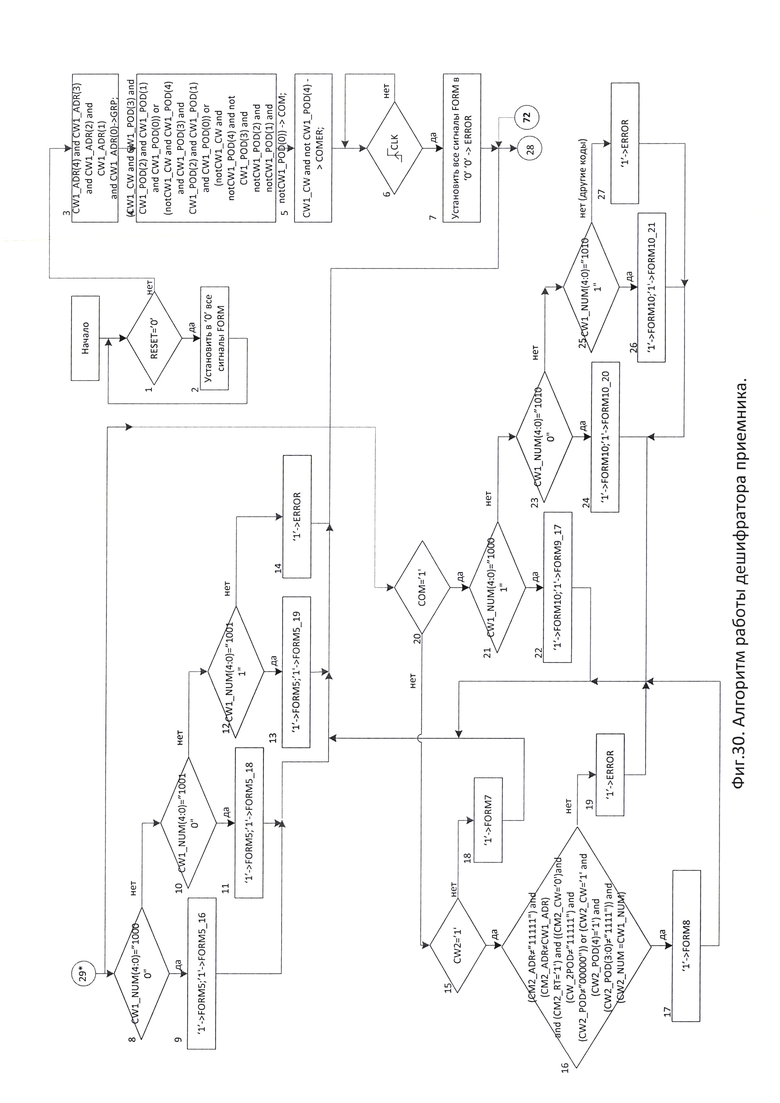

• на фиг.30 представлен алгоритм работы дешифратора приемника;

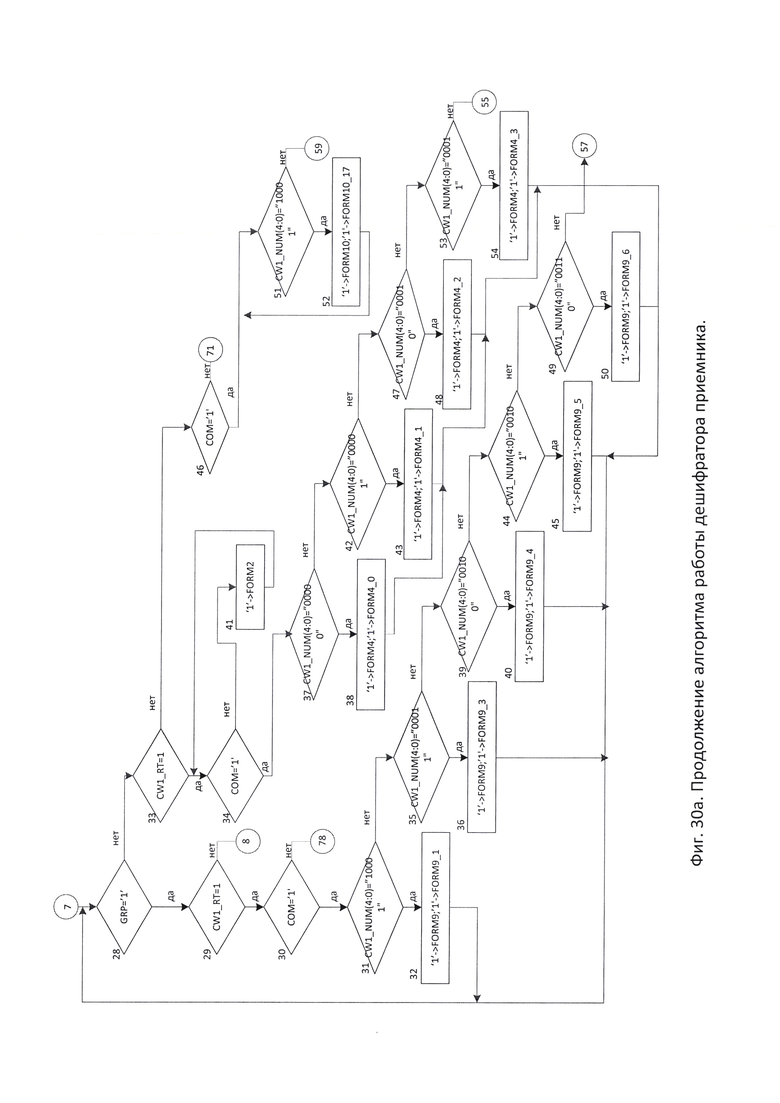

• на фиг.30а представлено продолжение алгоритма работы дешифратора приемника;

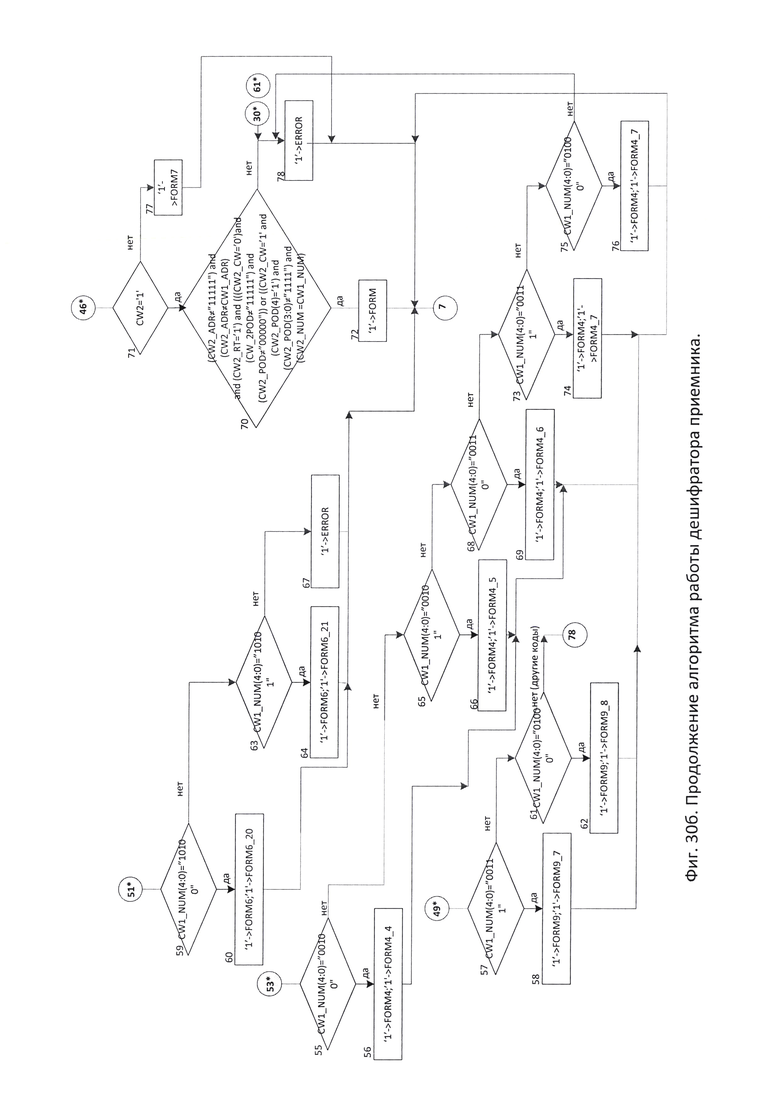

• на фиг.30б представлено продолжение алгоритма работы дешифратора приемника;

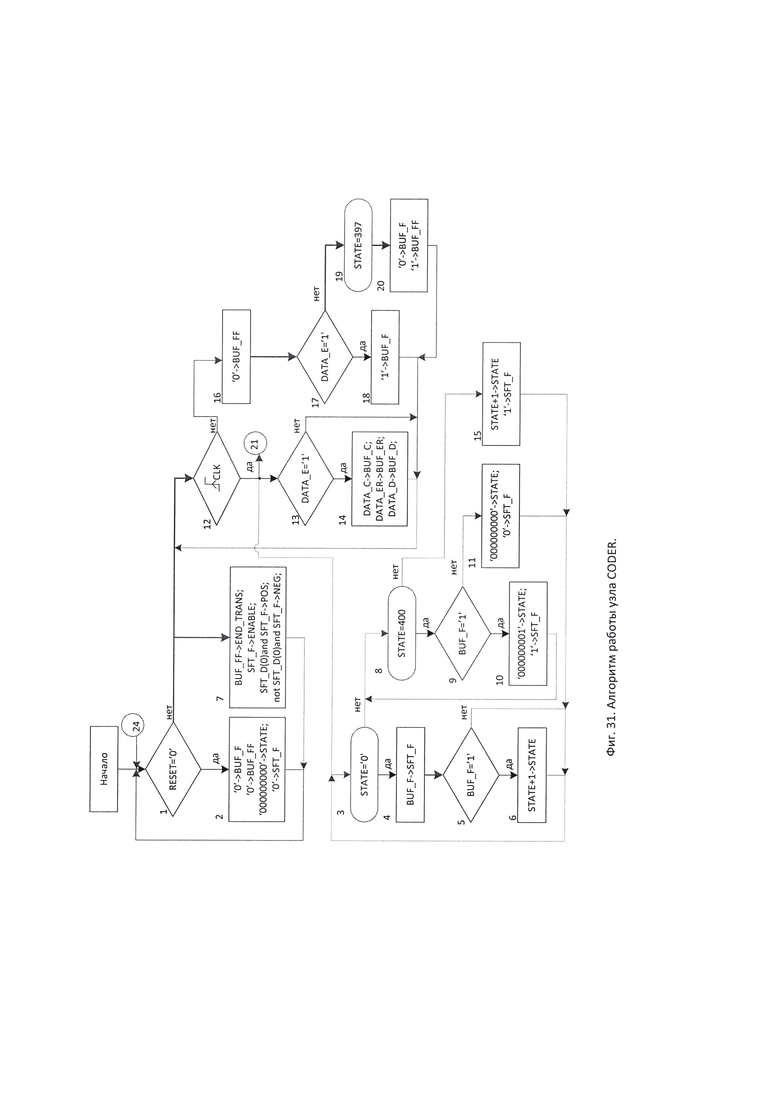

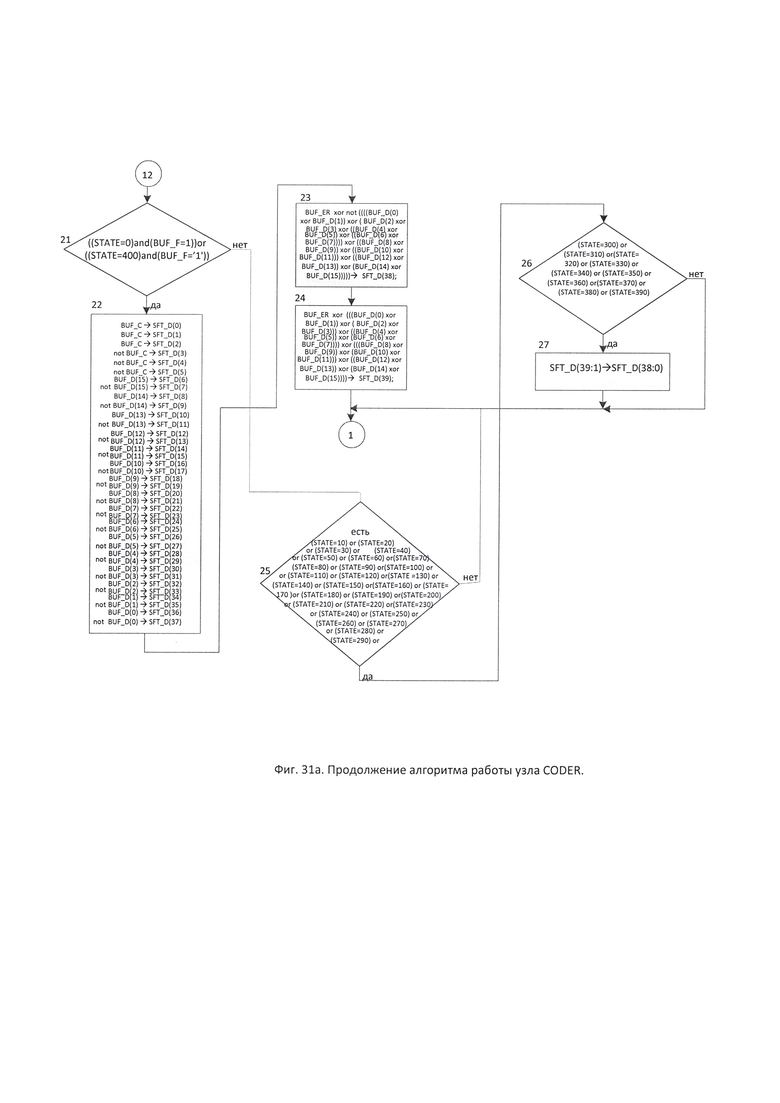

• на фиг.31 представлен алгоритм работы узла CODER OU;

• на фиг.31а представлено продолжение алгоритма работы узла CODER OU;

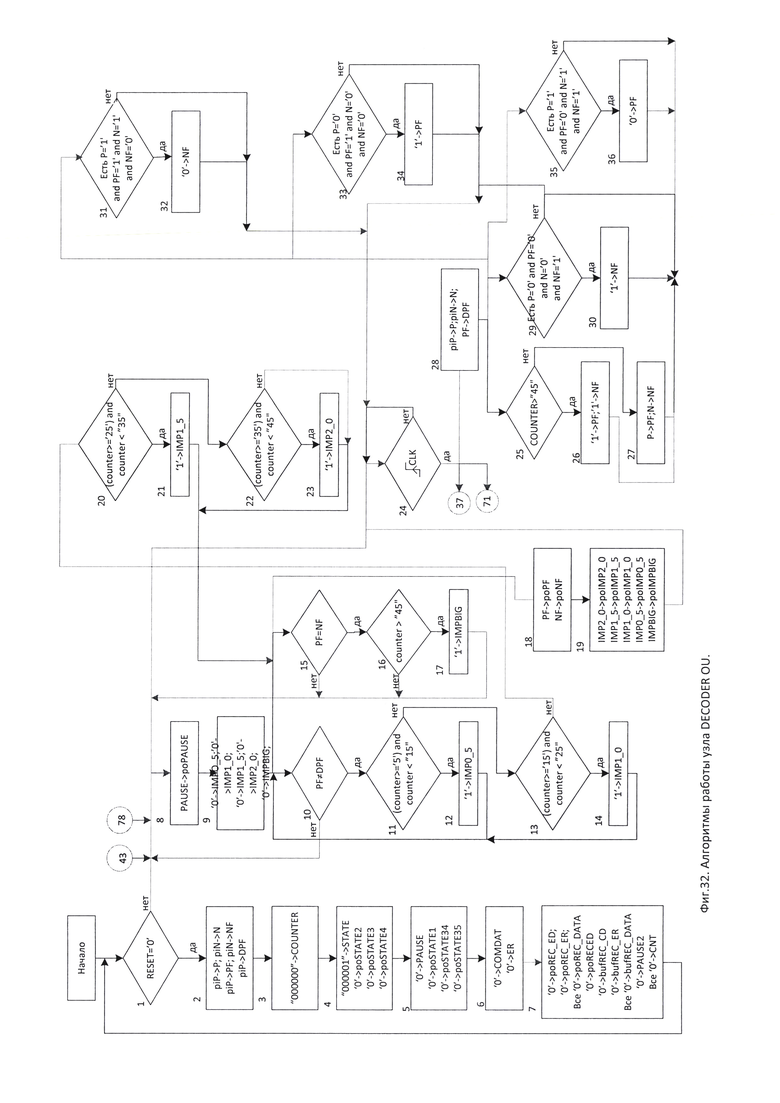

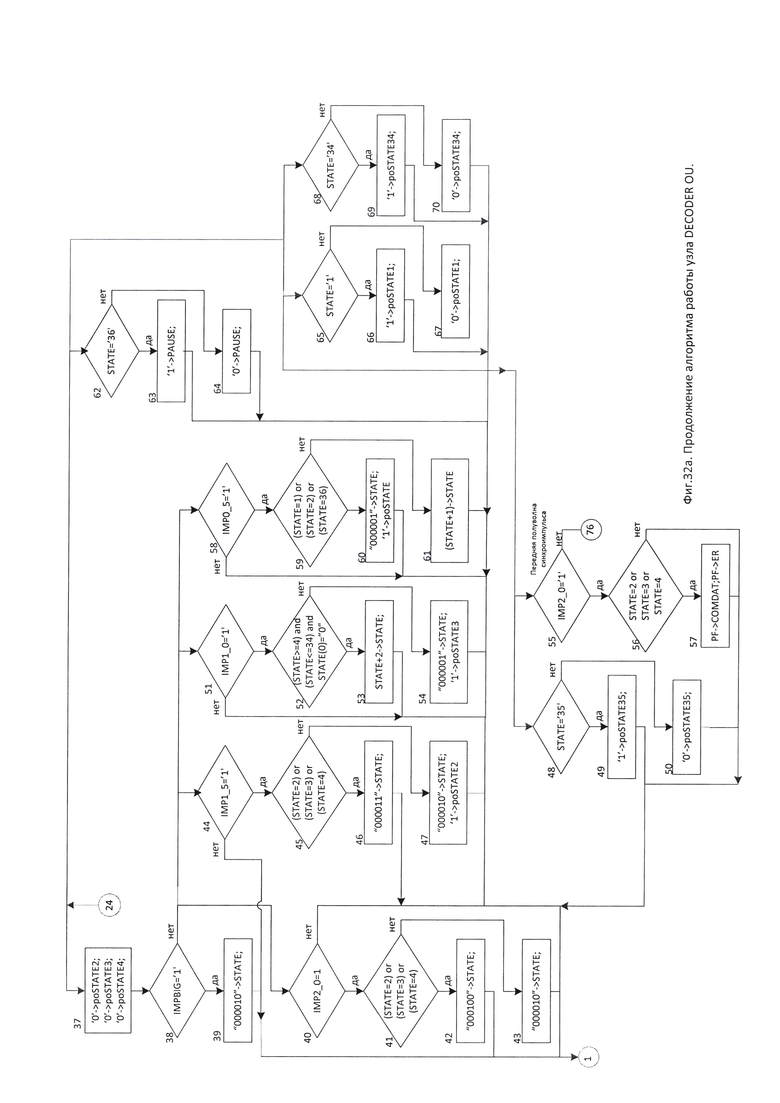

• на фиг.32 представлен алгоритм работы узла DECODER OU;

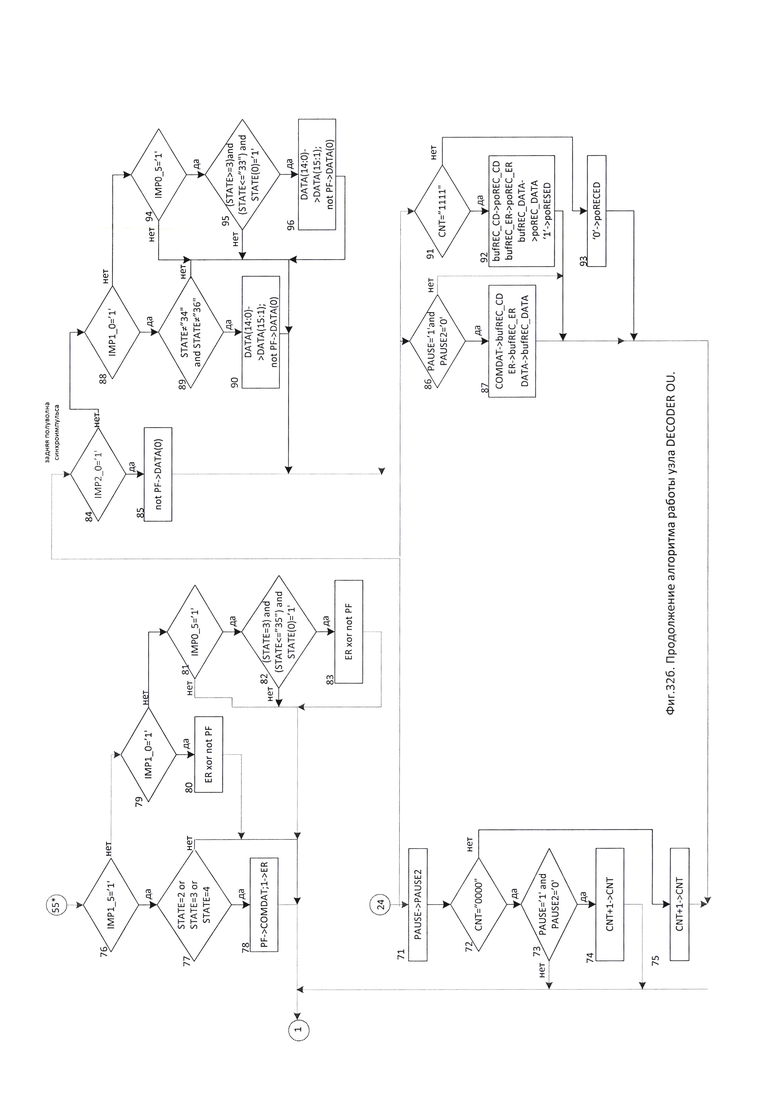

• на фиг.32а представлено продолжение алгоритма работы узла DECODER OU;

• на фиг.32б представлено продолжение алгоритма работы узла DECODER OU;

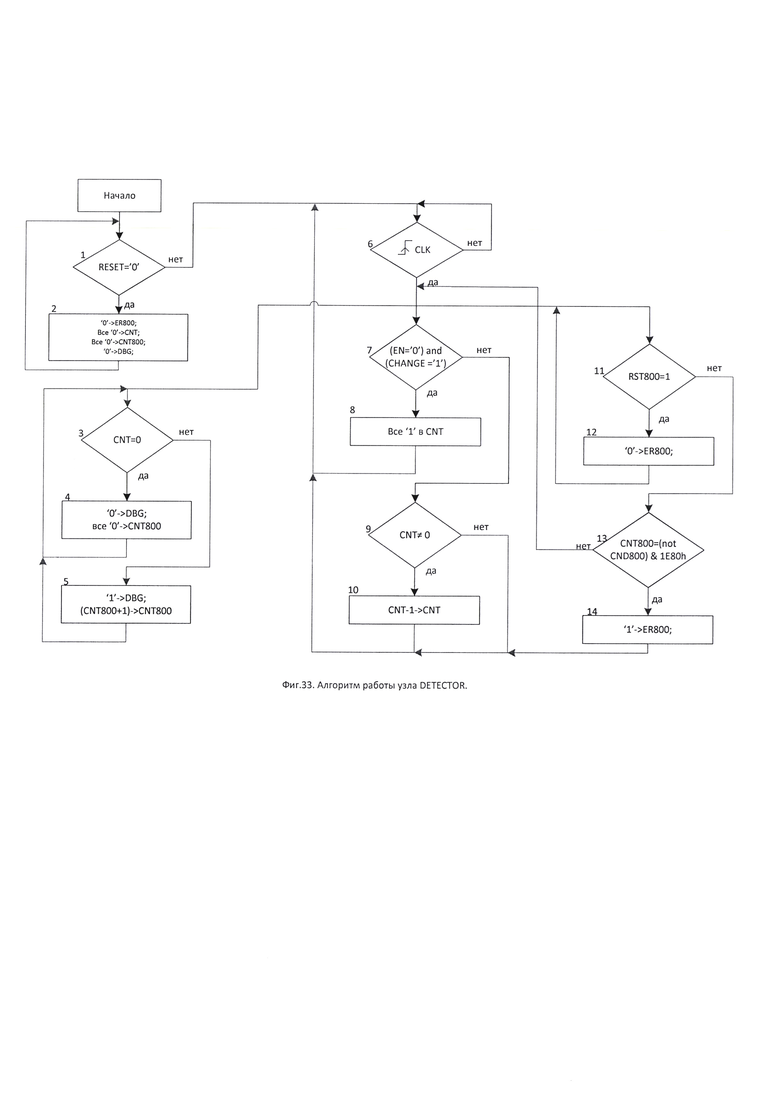

• на фиг.33 представлен алгоритм работы узла DETECTOR;

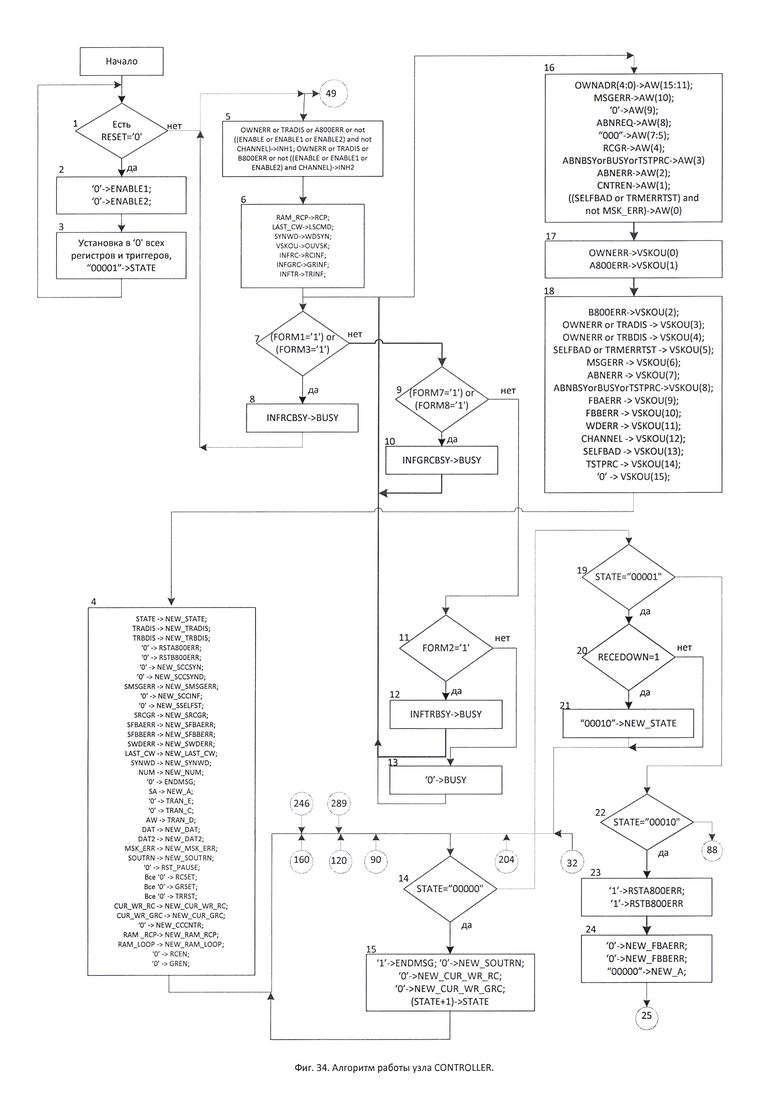

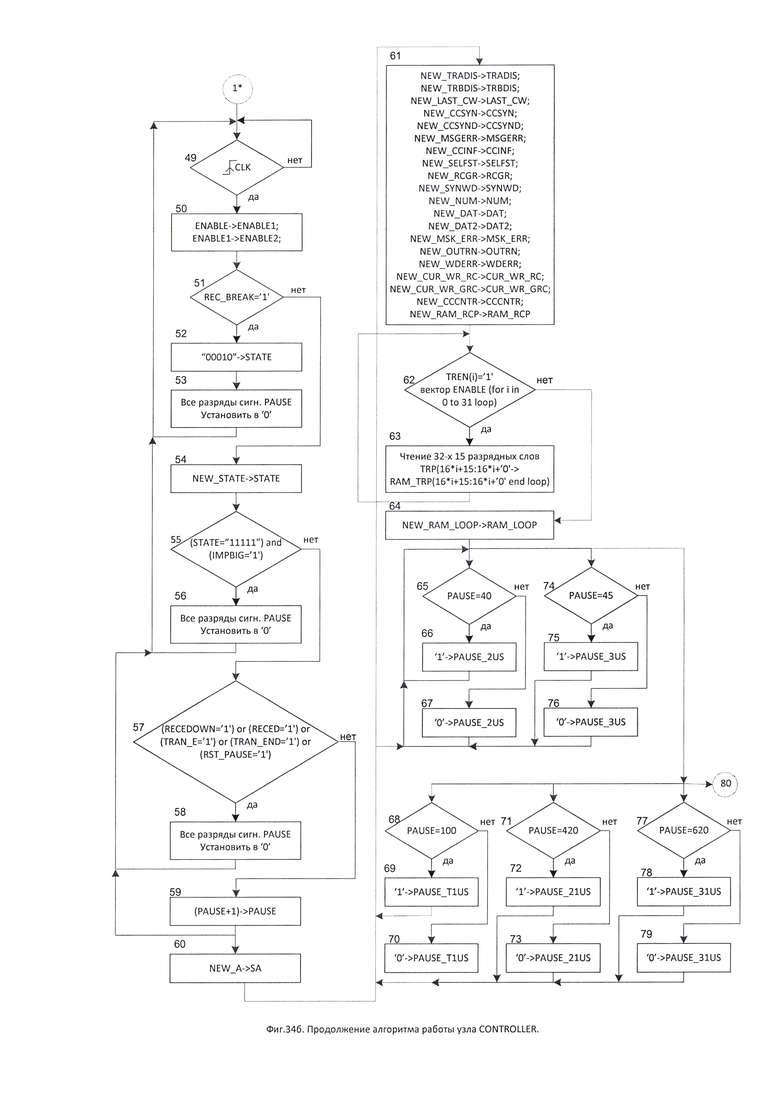

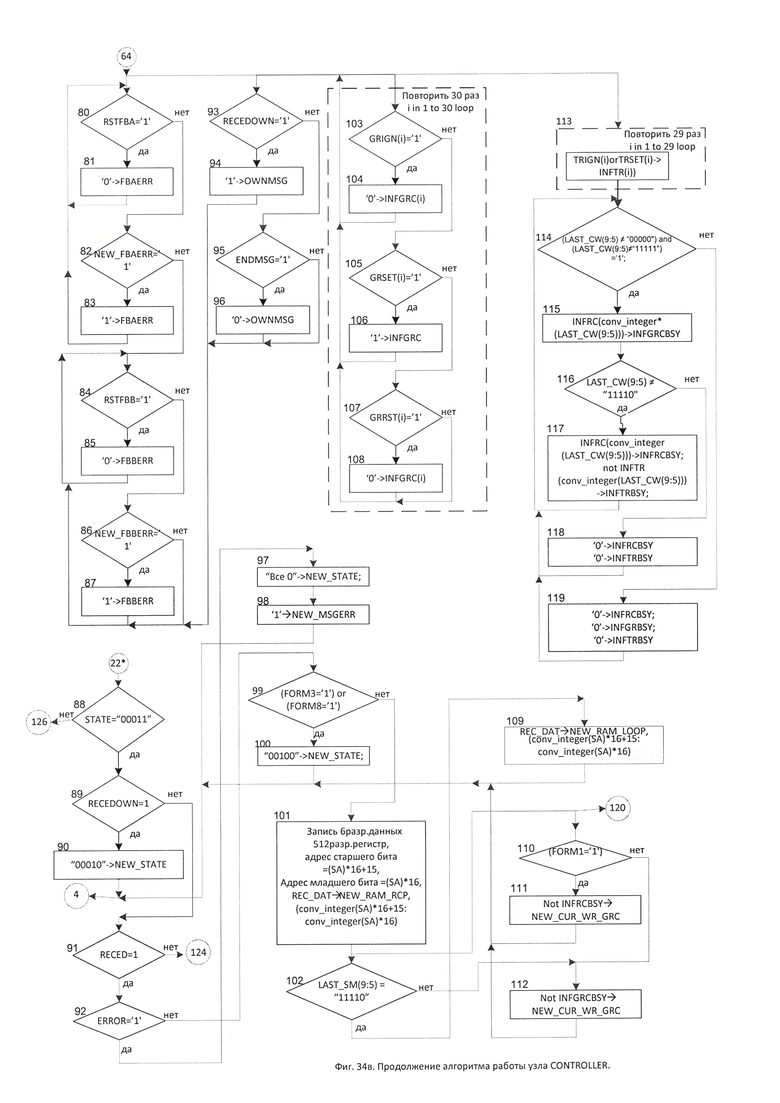

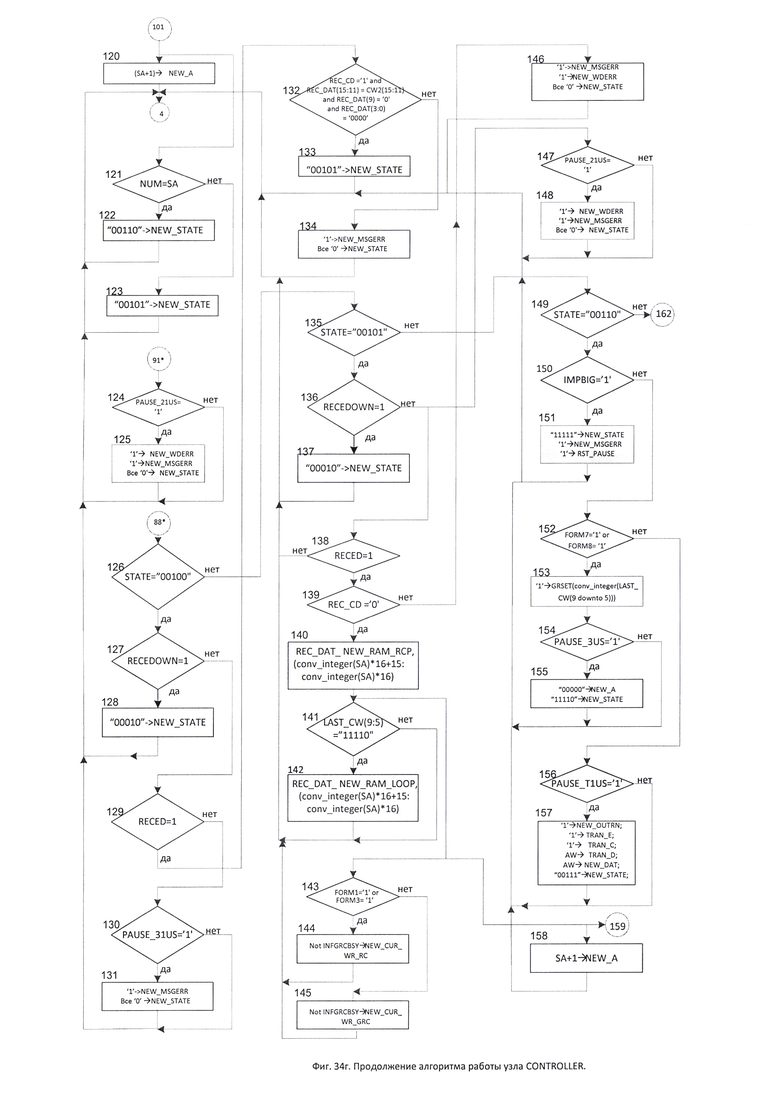

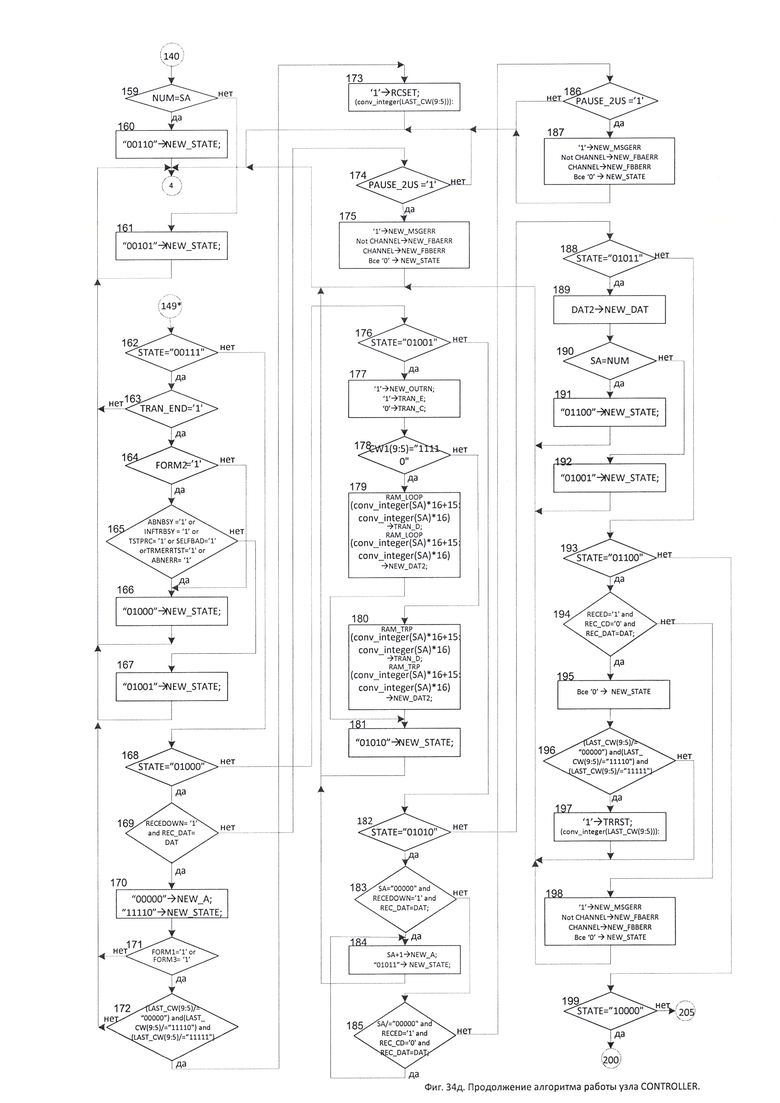

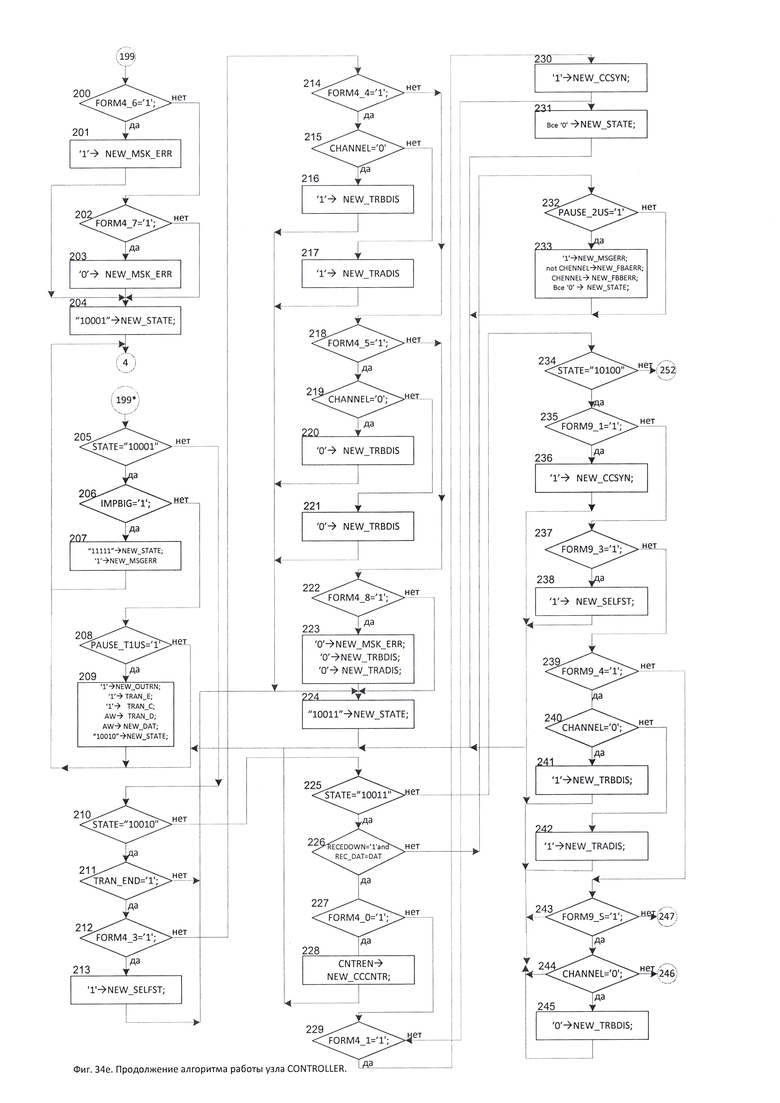

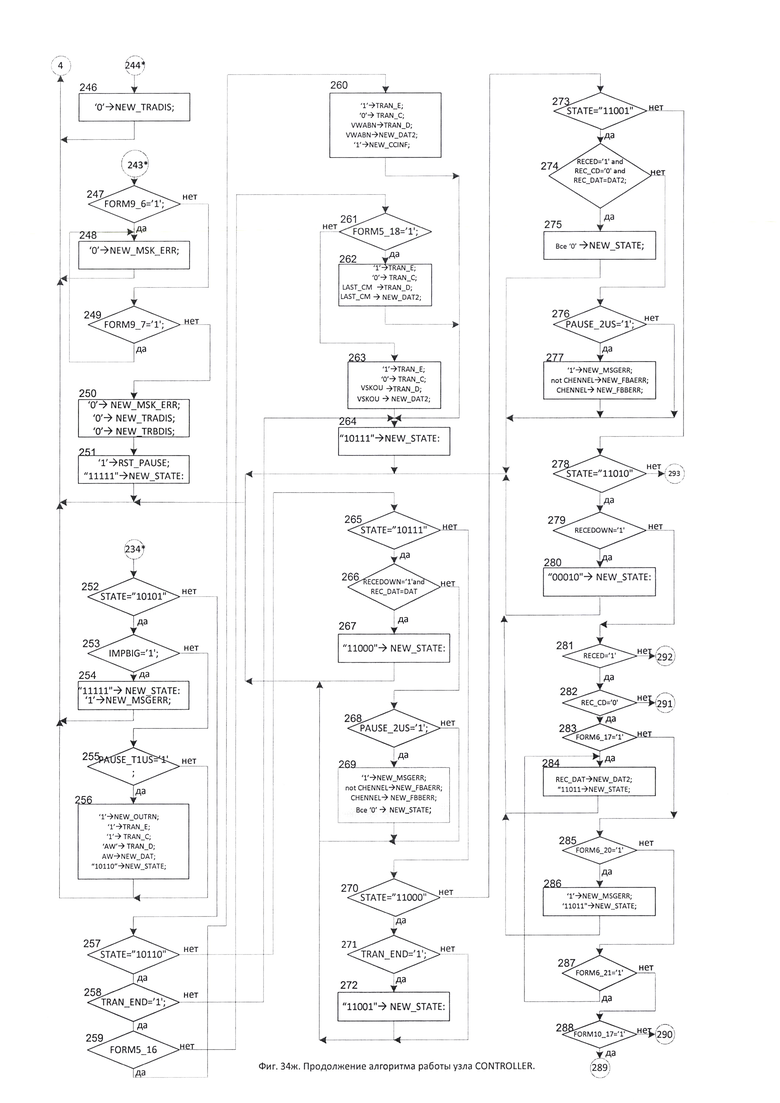

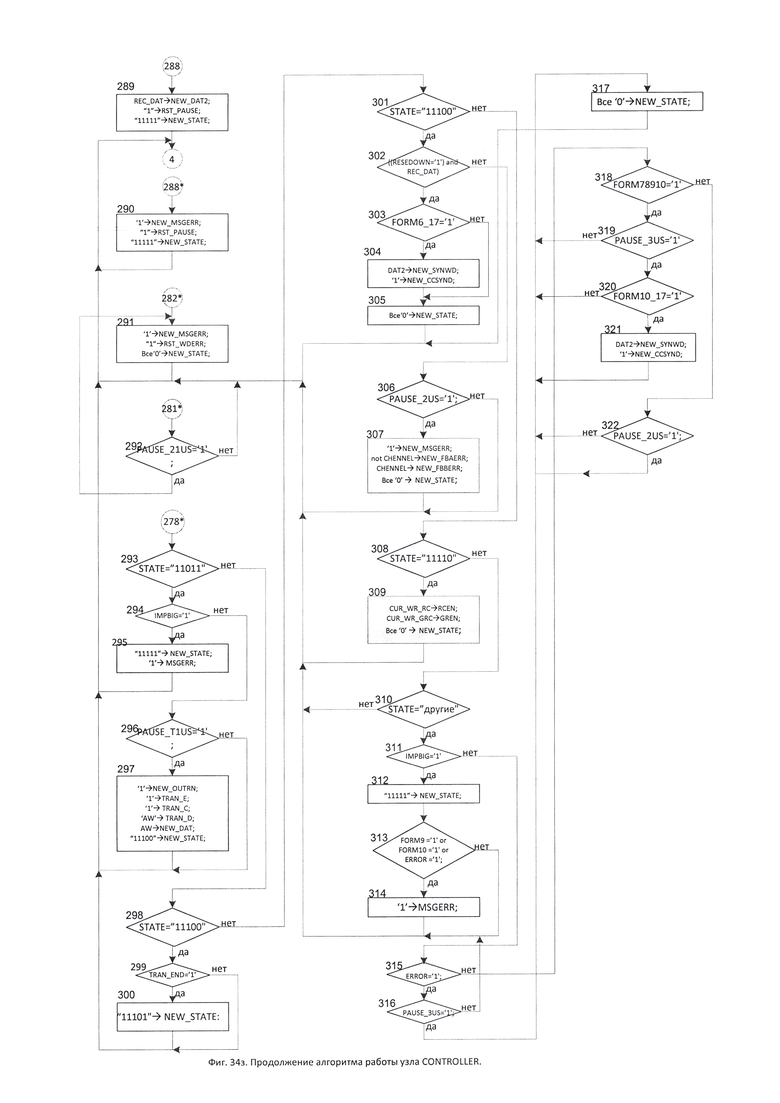

• на фиг.34 представлен алгоритм работы узла CONTROLLER;

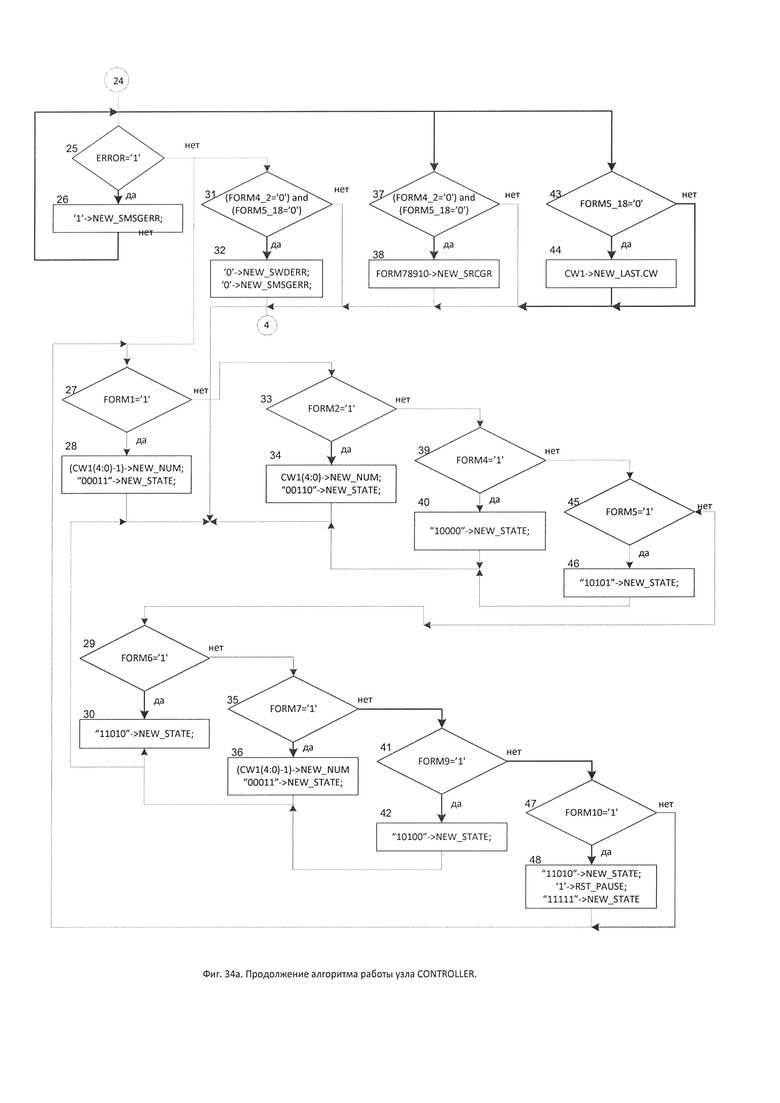

• на фиг.34а представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34б представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34в представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34г представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34д представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34е представлено продолжение алгоритма работы узла CONTROLLER;

• на фиг.34ж представлено продолжение алгоритма работы узла CONTROLLER;

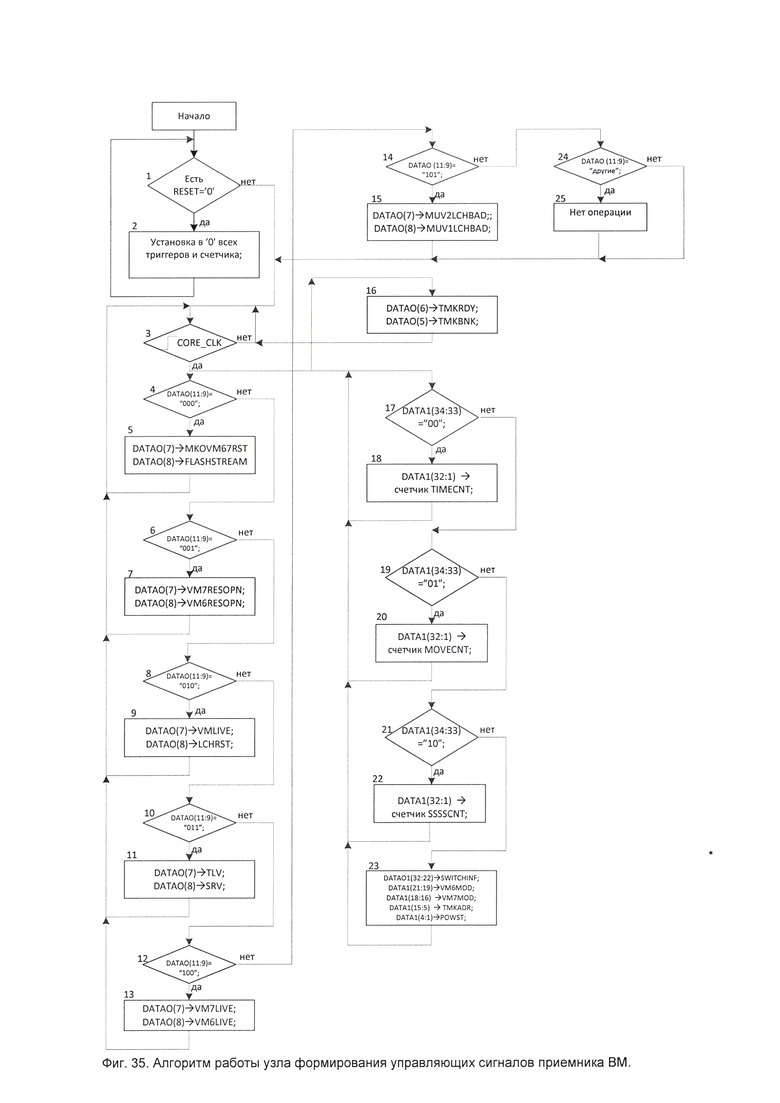

• на фиг.35 представлен алгоритм работы узла формирования управляющих сигналов приемника ВМ;

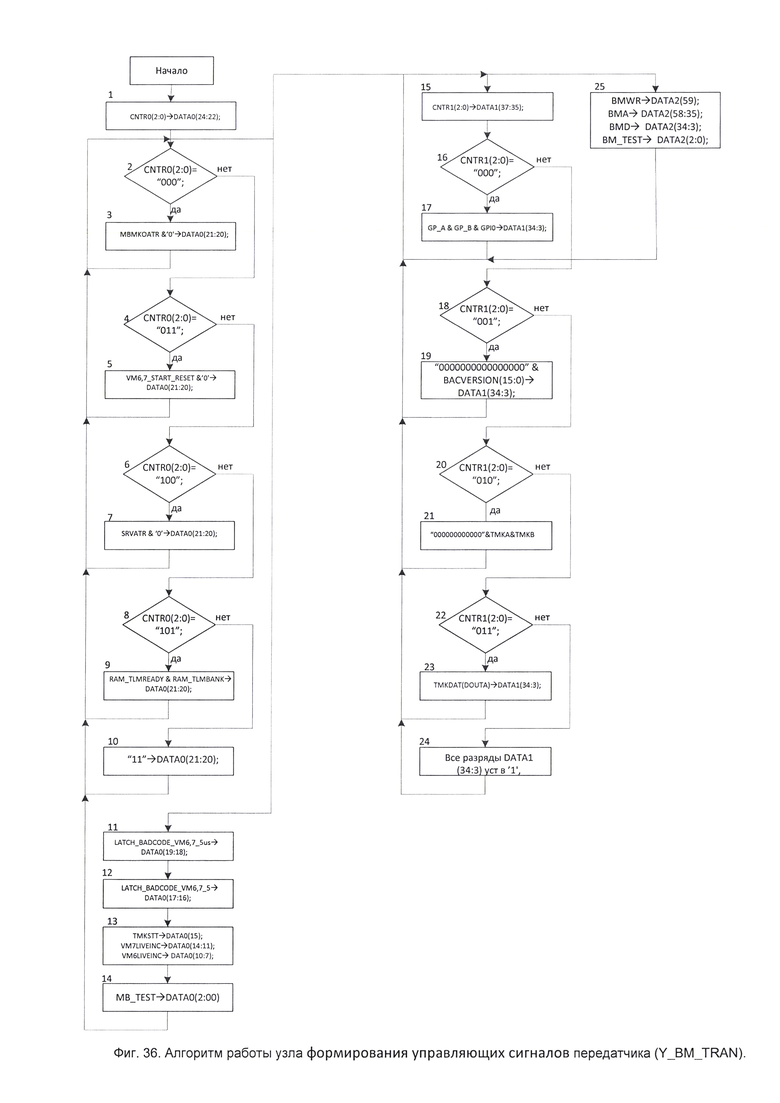

• на фиг.36 представлен алгоритм работы узла формирования управляющих сигналов передатчика (Y_FYS_BM_TRAN);

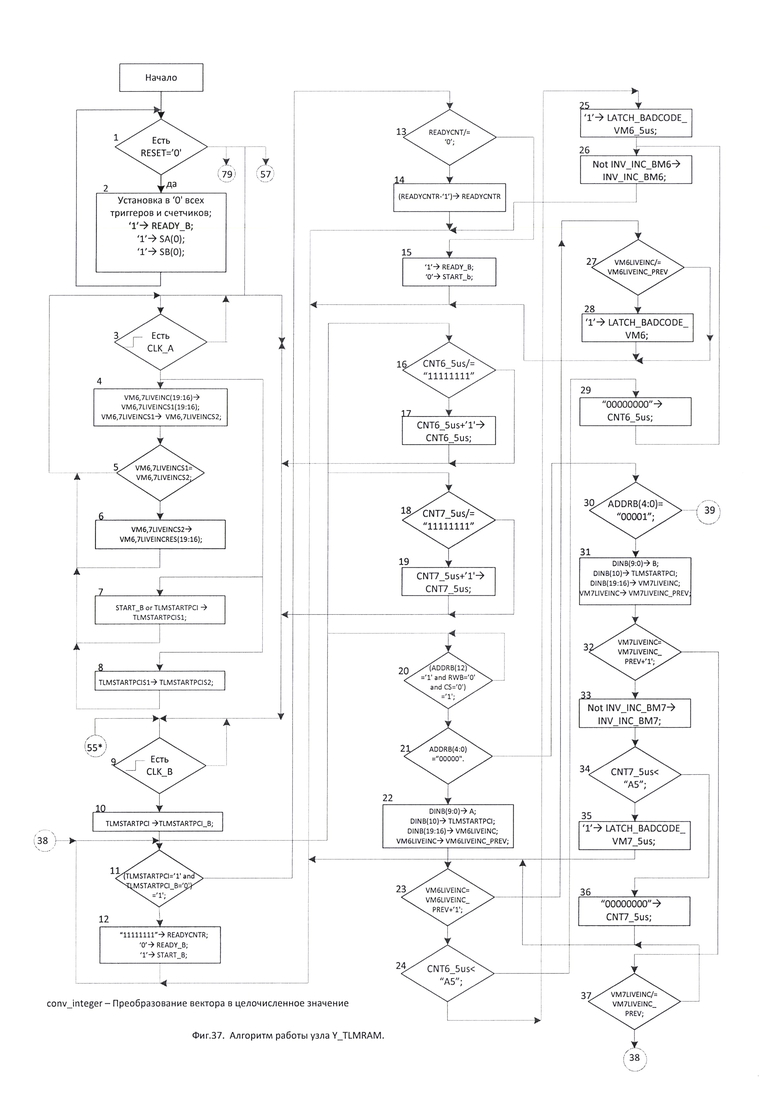

• на фиг.37 представлен алгоритм работы узла памяти телеметрического канала (Y_TLMRAM);

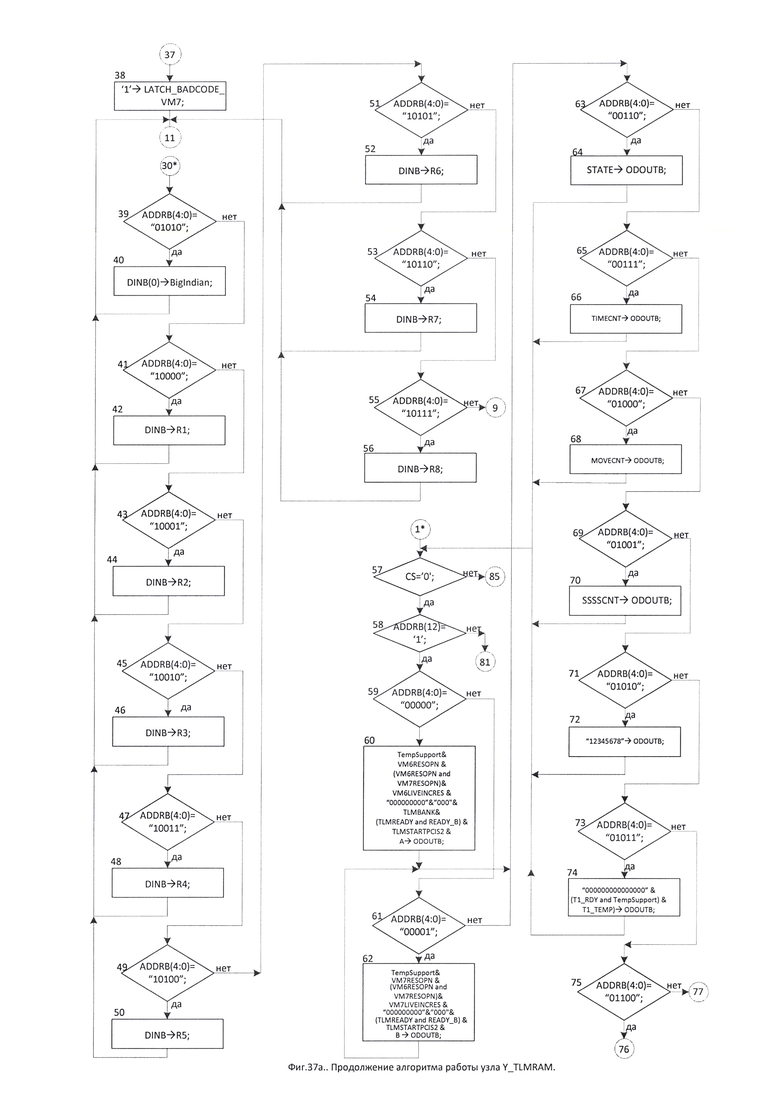

• на фиг.37а представлено продолжение алгоритма работы узла Y_TLMRAM;

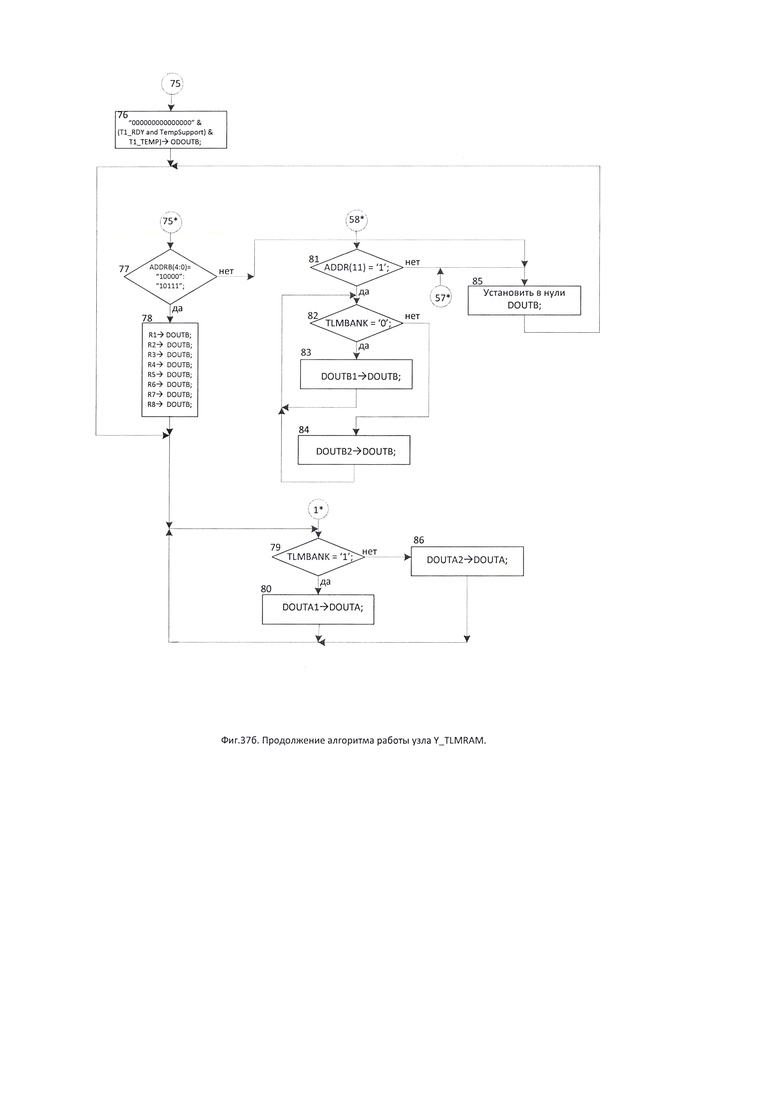

• на фиг.37б представлено продолжение алгоритма работы узла Y_TLMRAM;

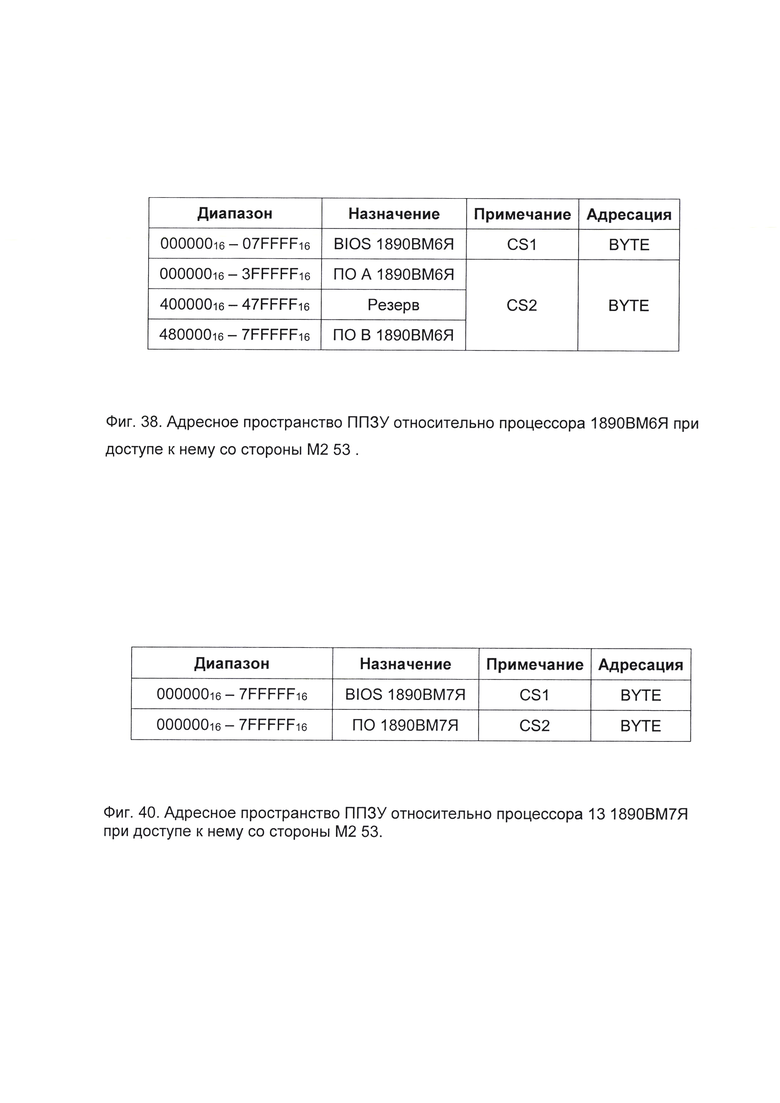

• на фиг.38 представлено адресное пространство ППЗУ 15 процессора 1 1890 ВМ6Я при доступе к нему со стороны канала М2 53;

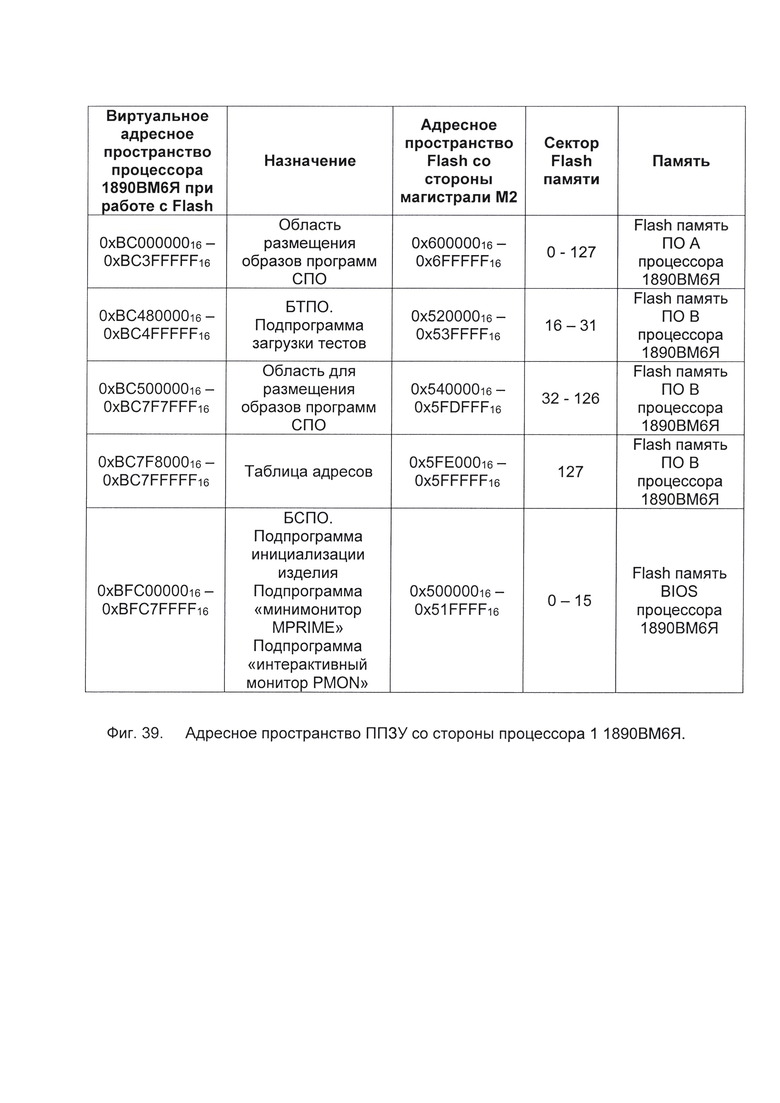

• на фиг.39 представлено адресное пространство ППЗУ 15 со стороны процессора 1 1890 ВМ6Я;

• на фиг.40 представлено адресное пространство ППЗУ 16 процессора 13 1890 ВМ7Я при доступе к нему со стороны канала М2 53;

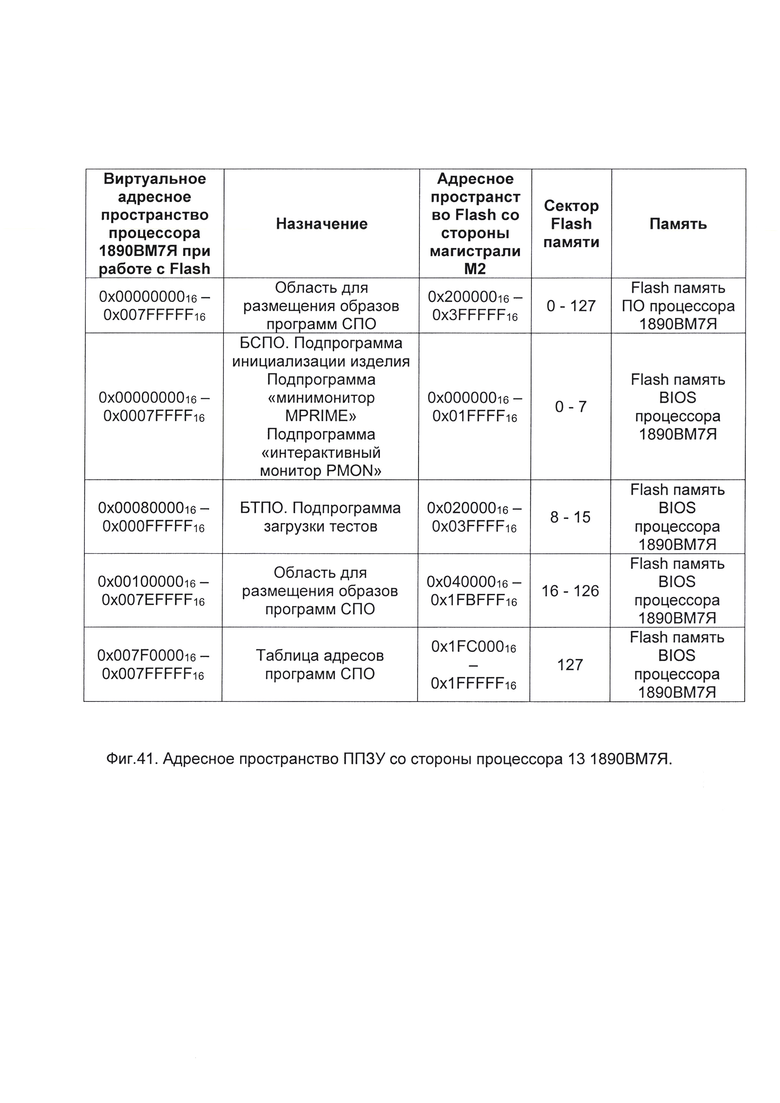

• на фиг.41 представлено адресное пространство ППЗУ 16 со стороны процессора 13 1890 ВМ7Я;

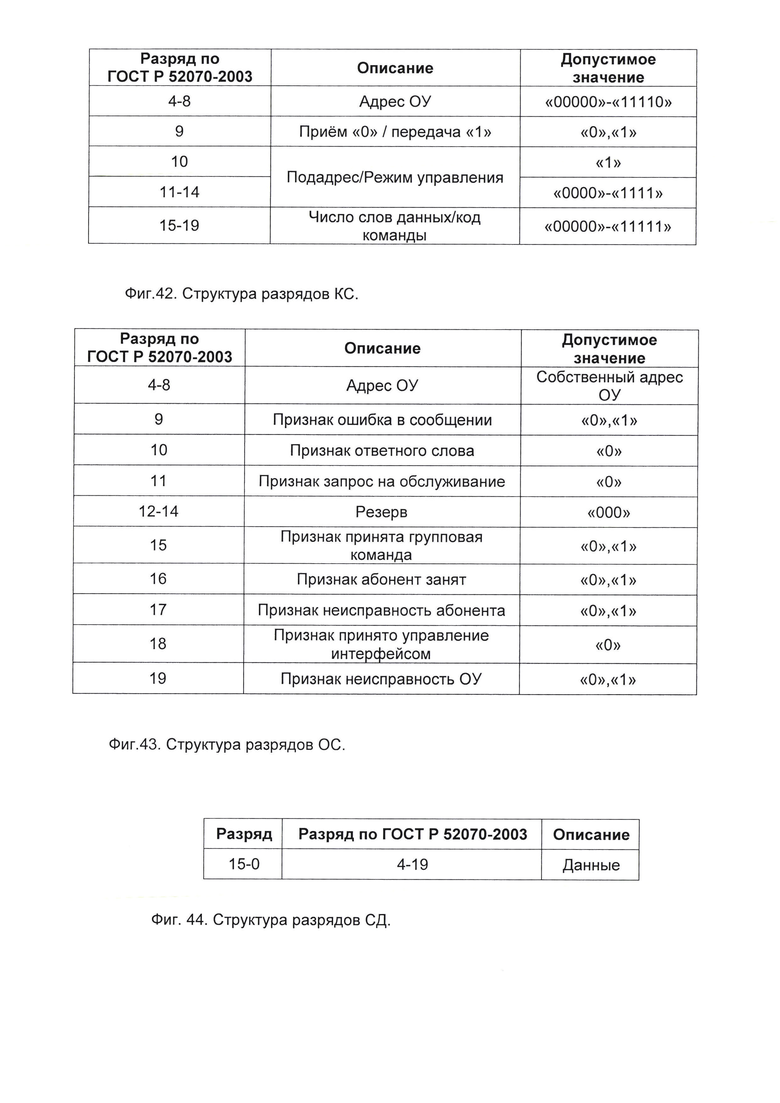

• на фиг.42 представлена структура разрядов КС;

• на фиг.43 представлена структура информационных разрядов ОС;

• на фиг.44 представлена структура информационных разрядов передаваемых и принимаемых слов данных;

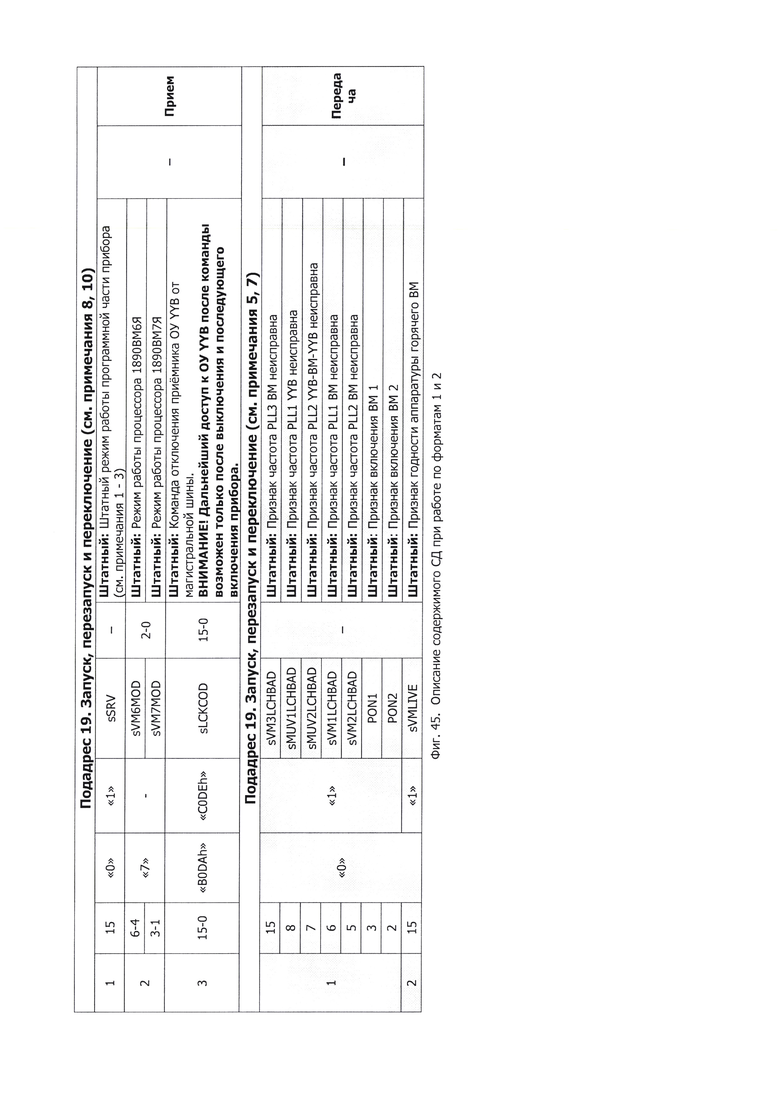

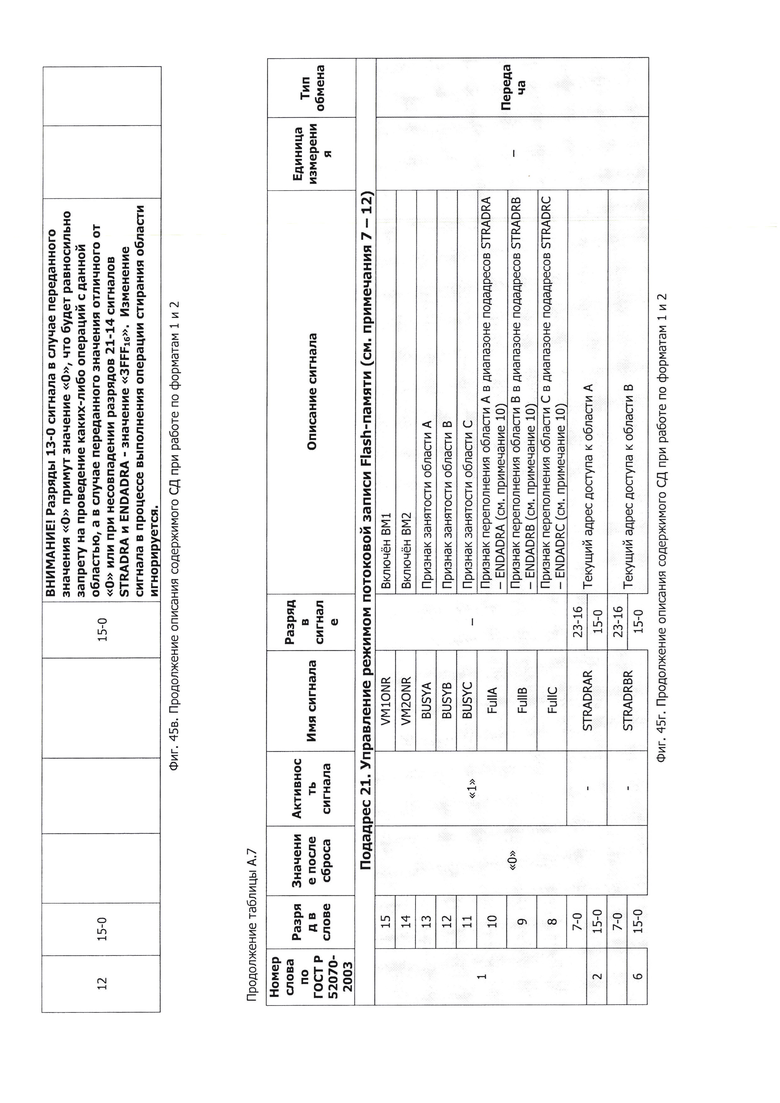

• на фиг.45 представлено описание содержимого СД при работе по форматам 1 и 2;

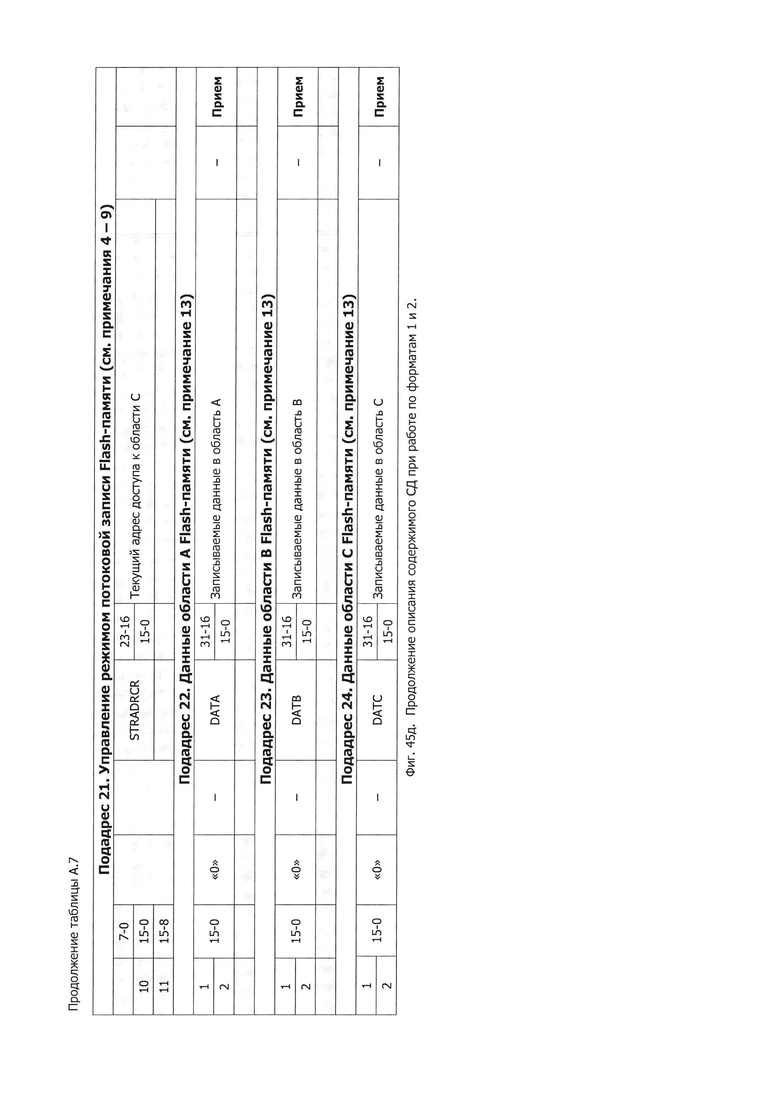

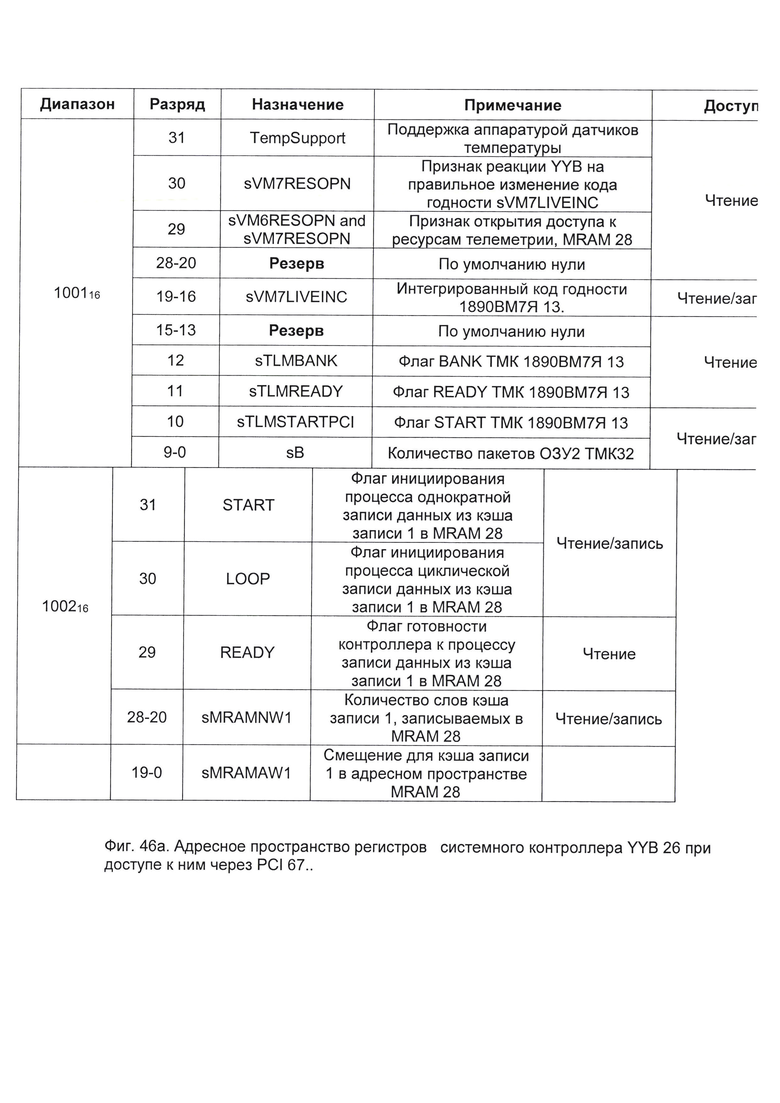

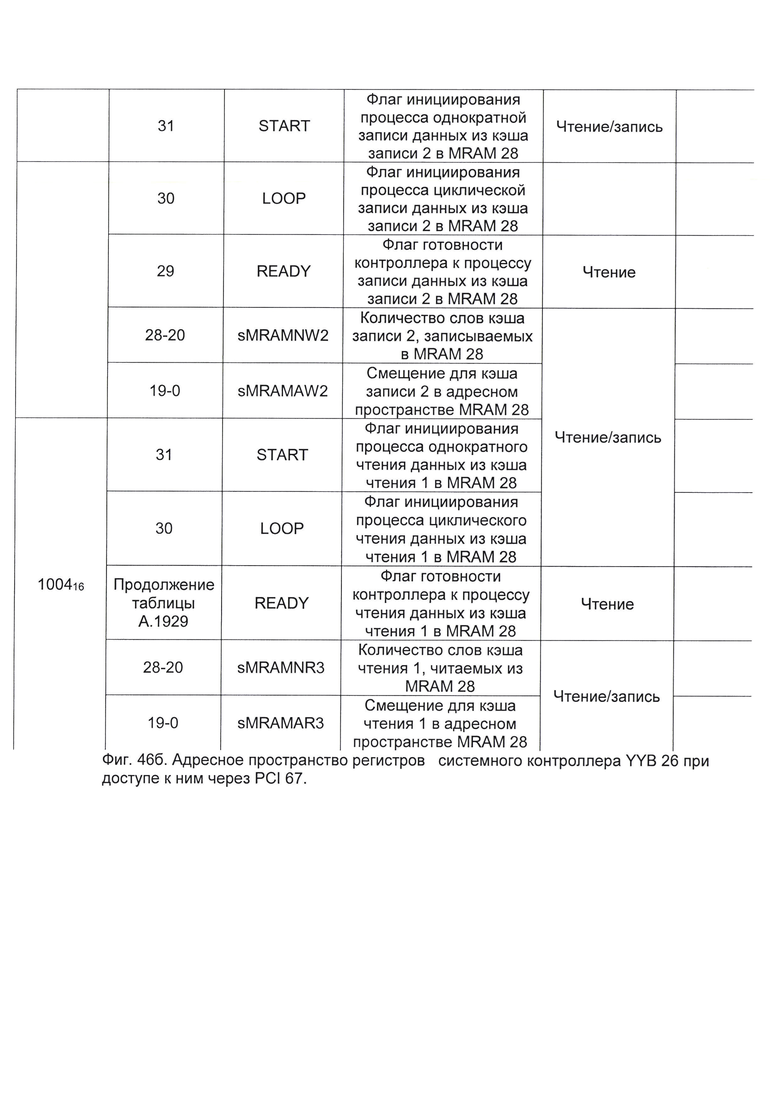

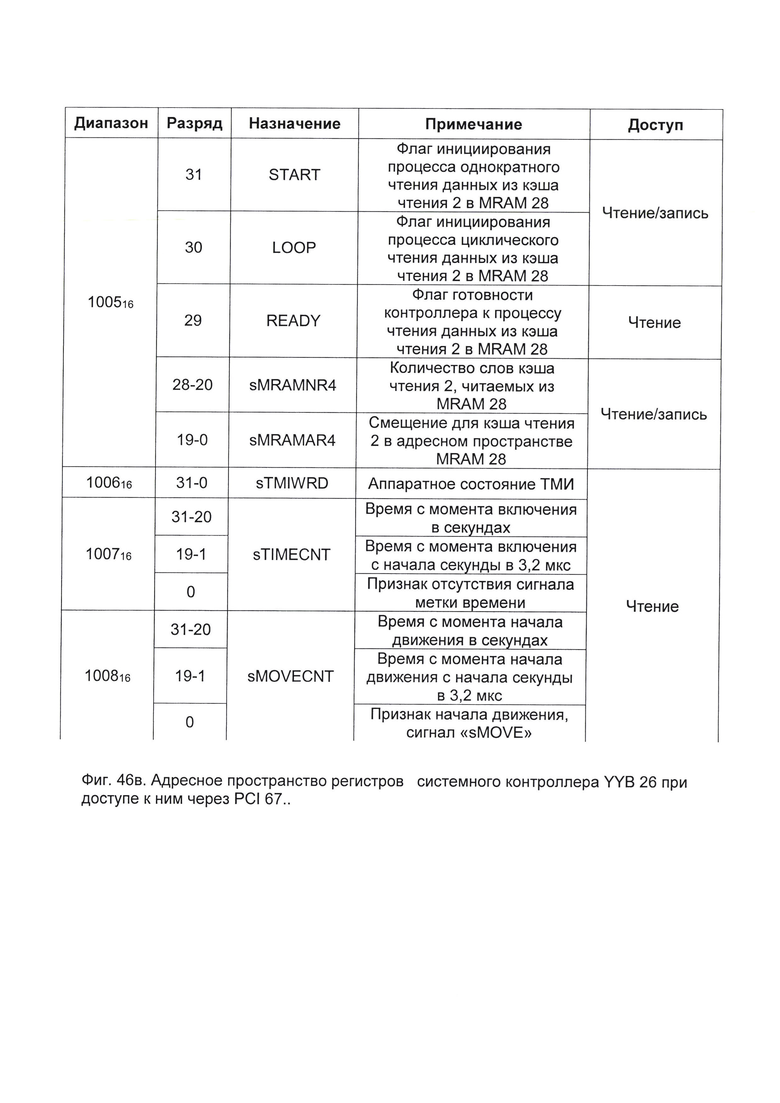

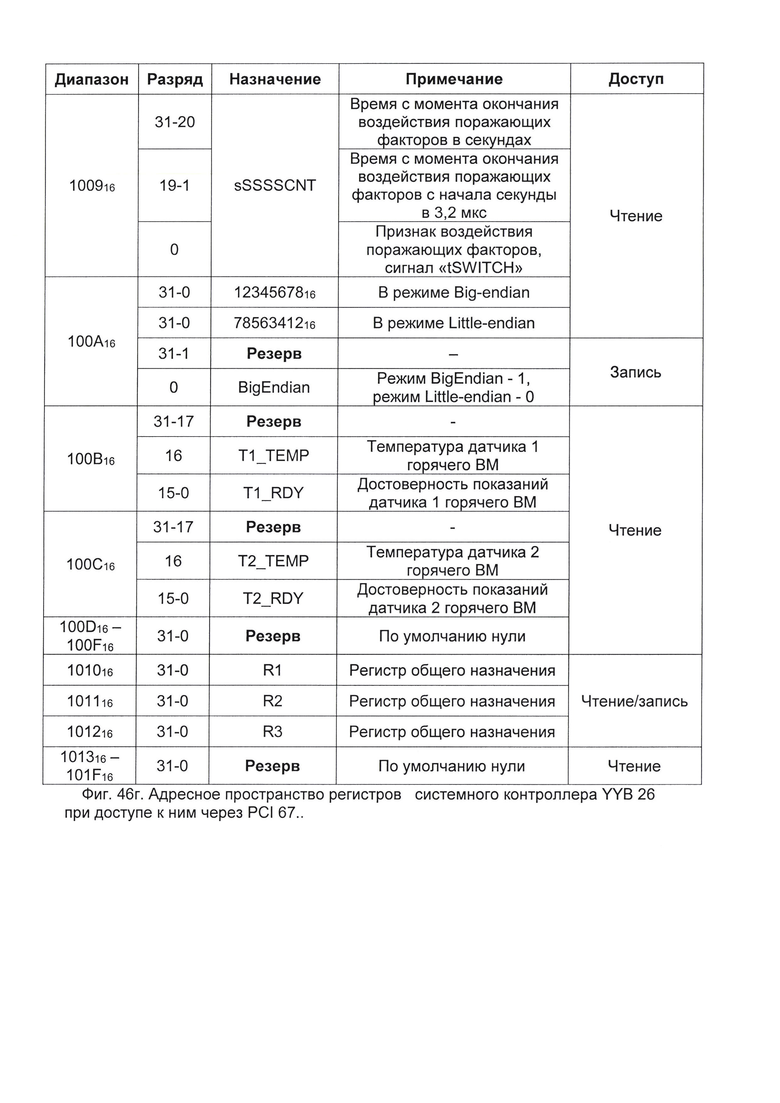

• на фиг.46 представлено адресное пространство регистров системного контроллера YYB 26 при доступе к ним через PCI 67;

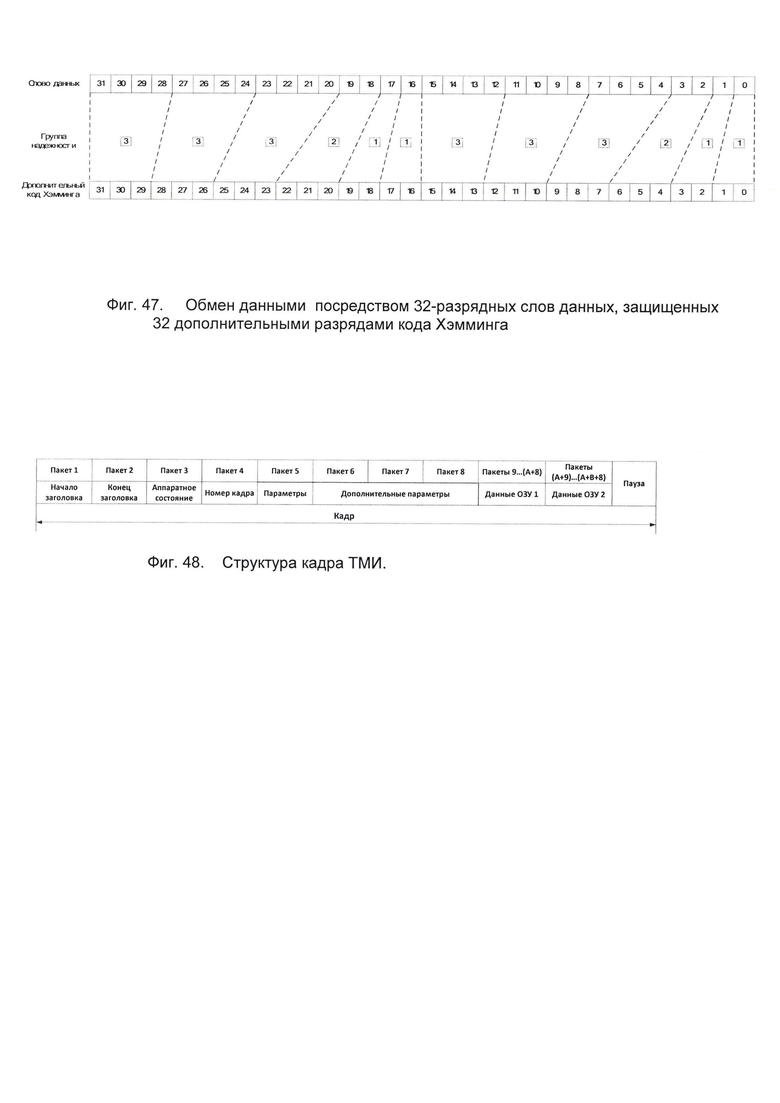

• на фиг.47 представлен обмен данными посредством 32-разрядных слов данных, защищенных 32 дополнительными разрядами кода Хэмминга;

• на фиг.48 представлена структура кадра;

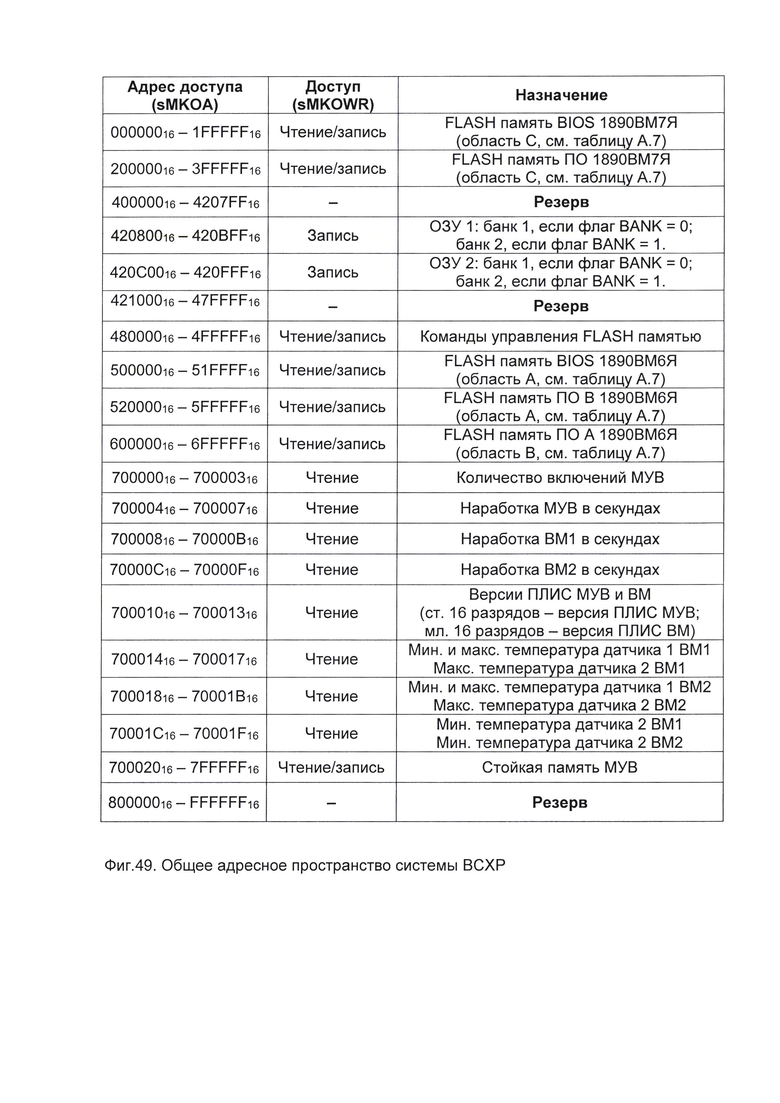

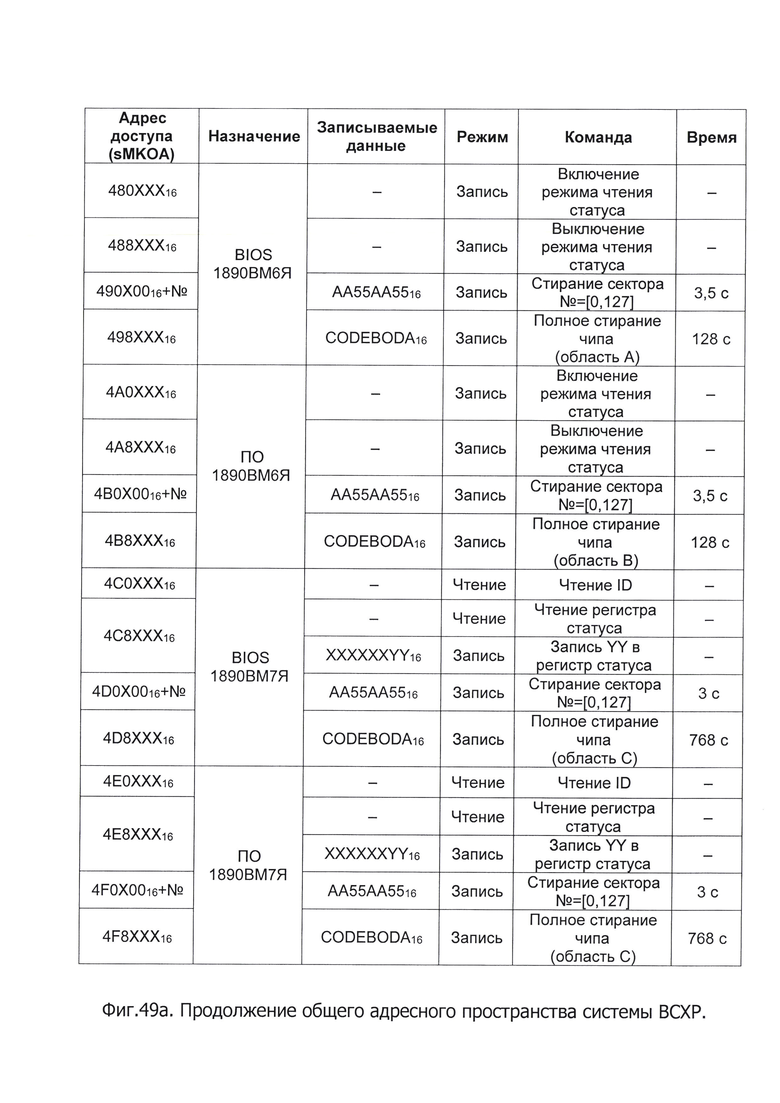

• на фиг.49 представлено общее адресное пространство ППЗУ 15,16, контроллера телеметрии ТМК 32 и стойкой памяти MRAM 28;

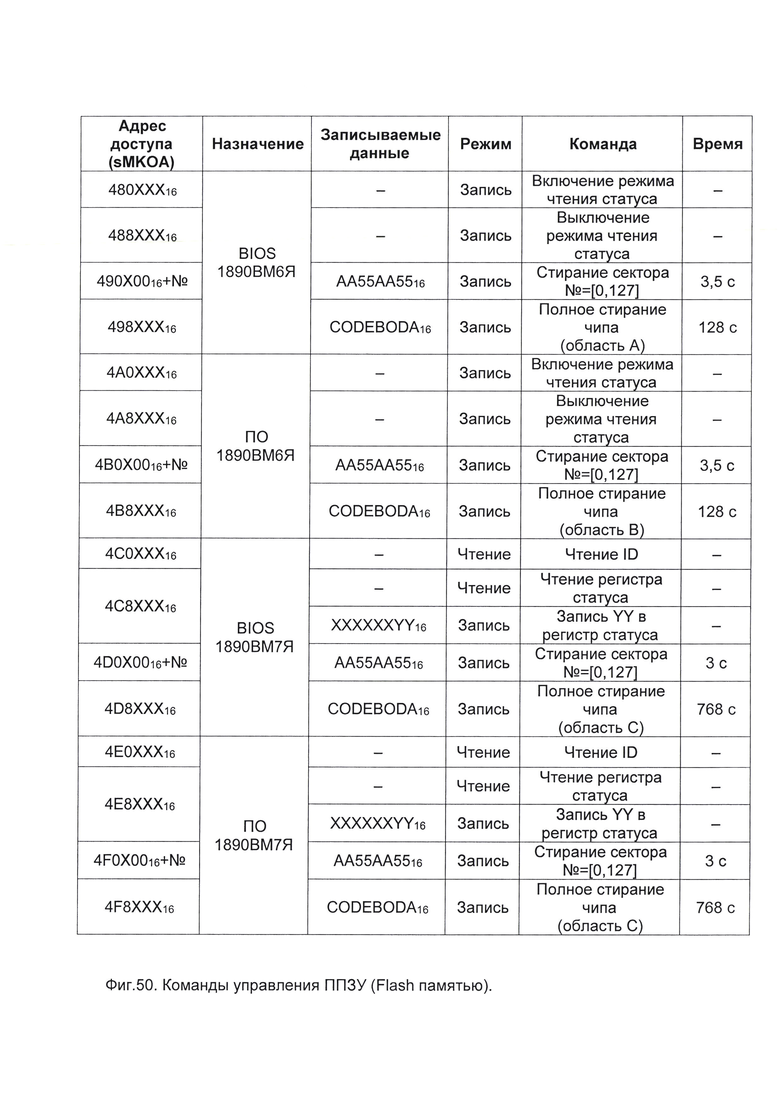

• на фиг.50 представлены команды управления ППЗУ 15, 16;

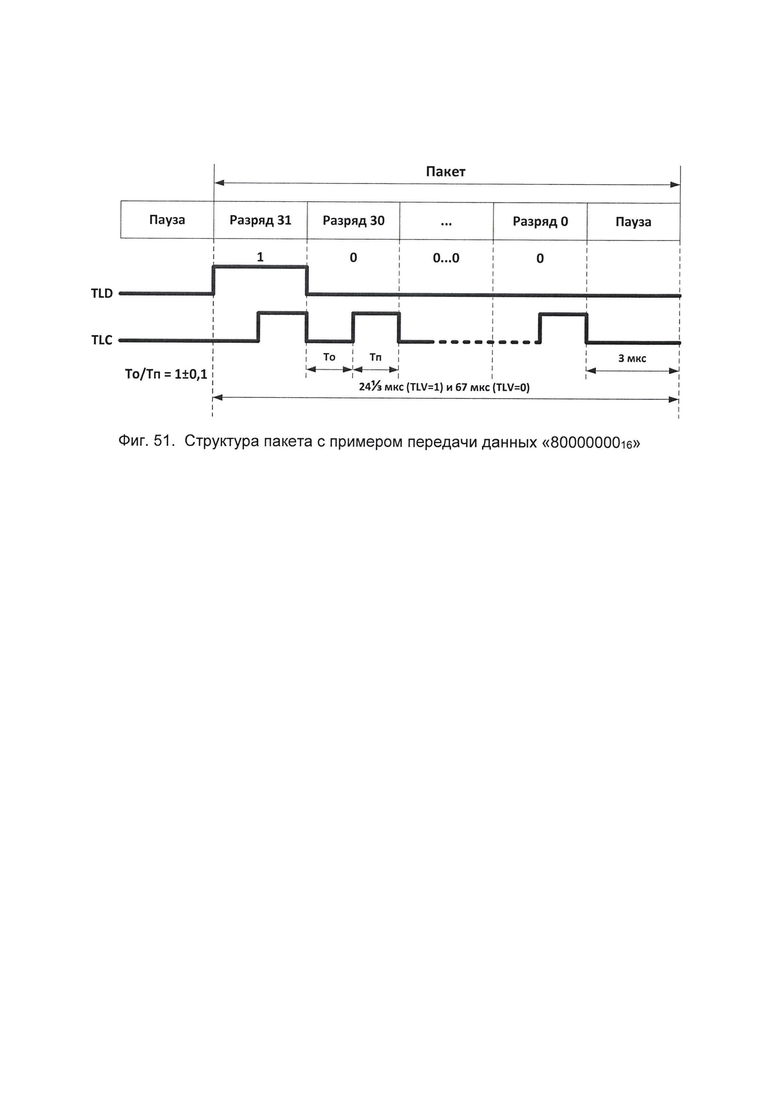

• на фиг.51 представлена структура пакета с примером передачи данных «8000000016»;

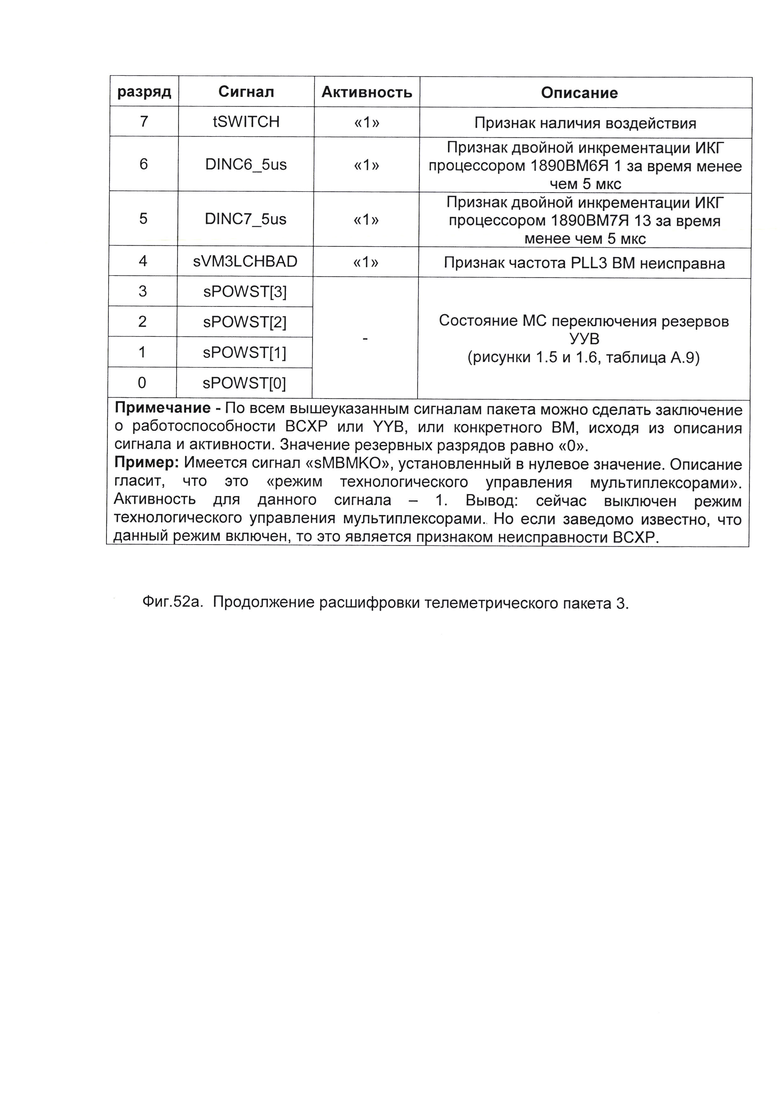

• на фиг.52, 52а представлена расшифровка телеметрического пакета 3;

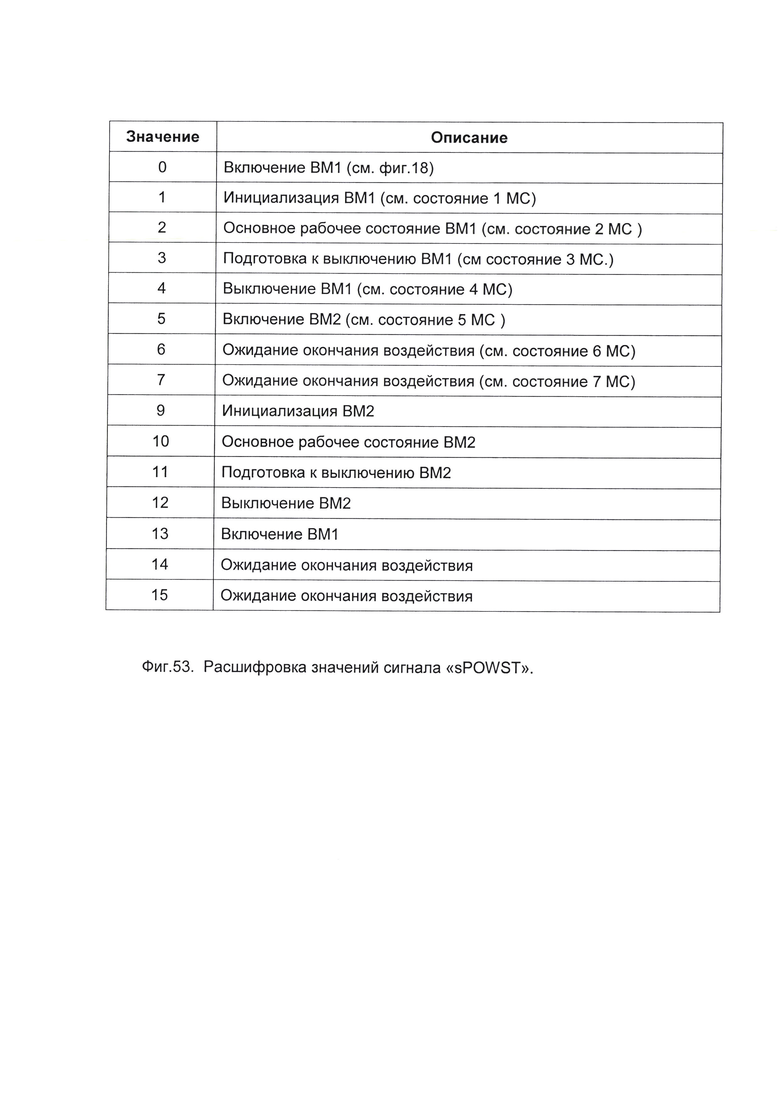

• на фиг.53. представлена расшифровка значений сигнала «sPOWST»;

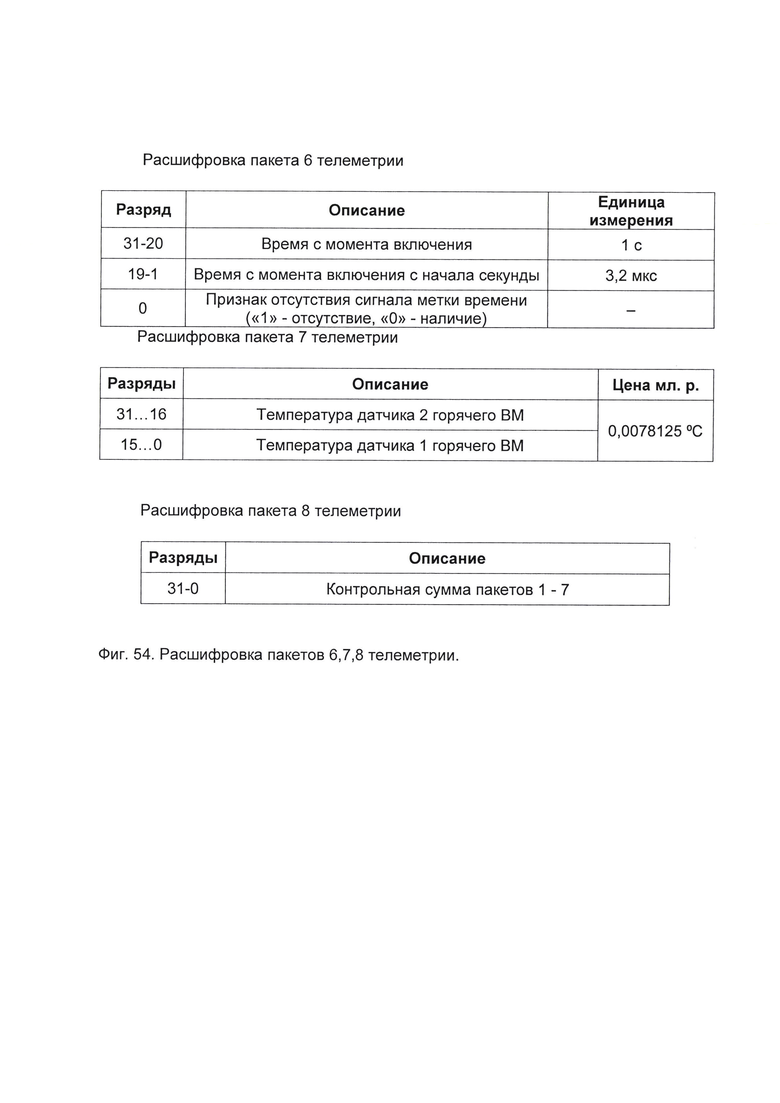

• на фиг.54 представлена расшифровка пакетов 6, 7, 8 телеметрии;

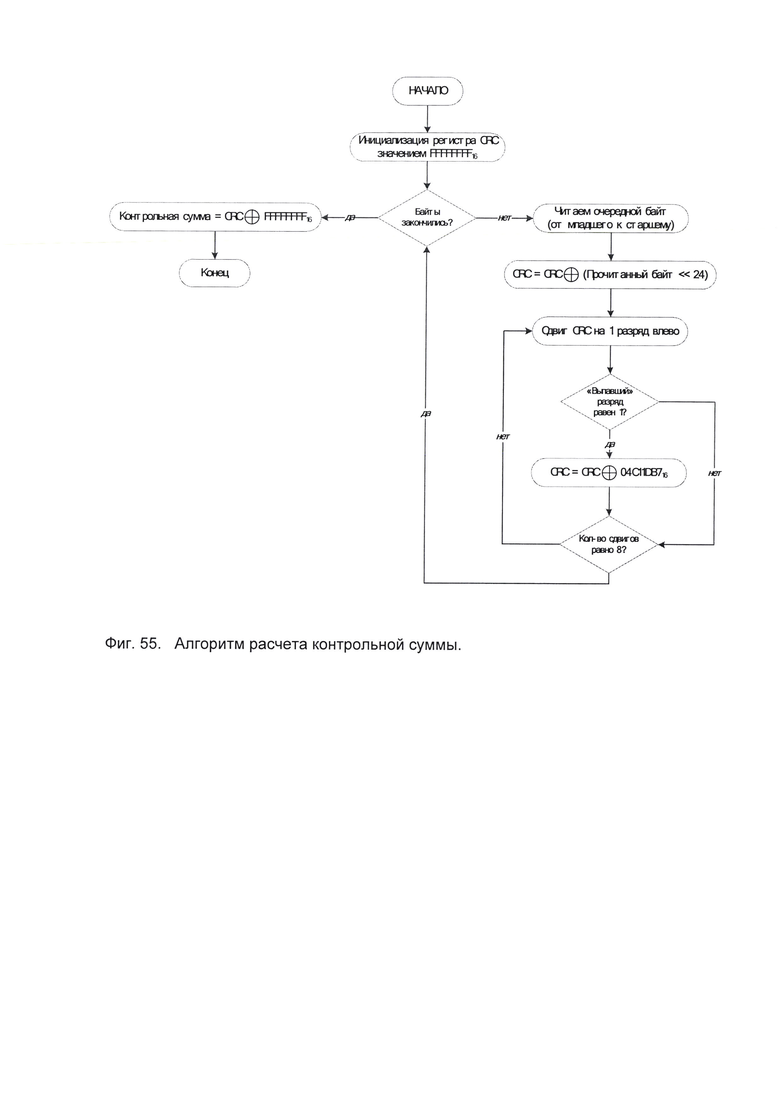

• на фиг.55 представлен алгоритм расчета контрольной суммы пакетов 1-7;

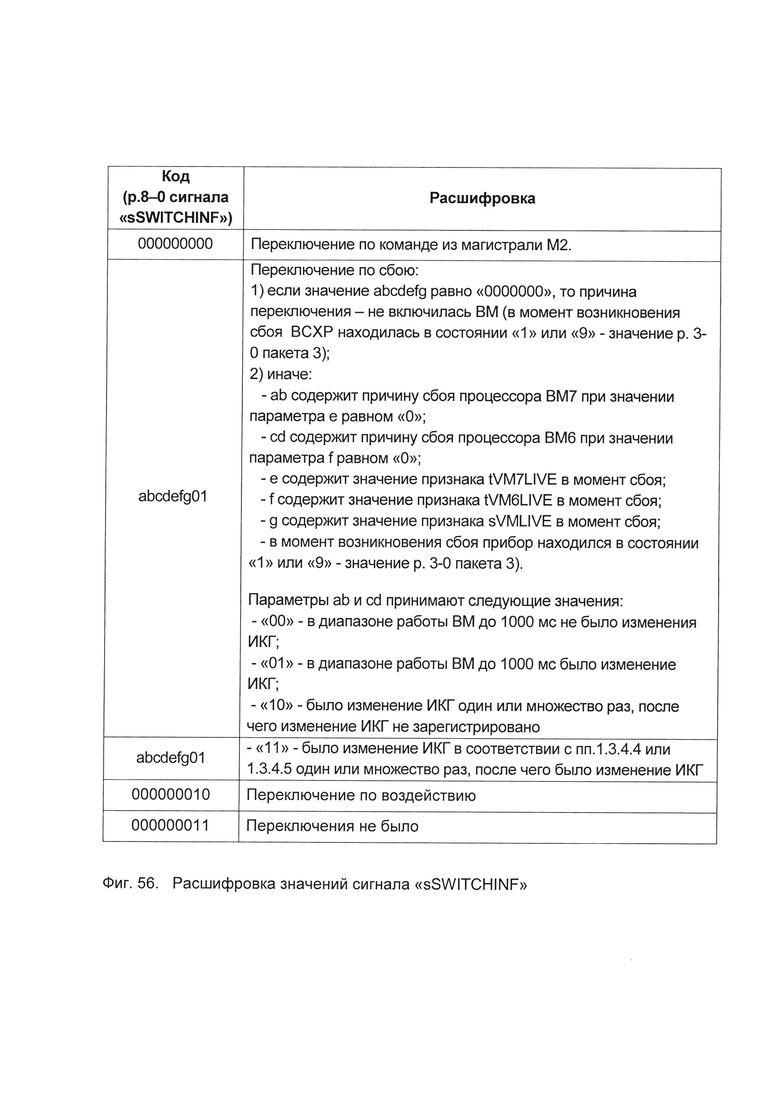

• на фиг.56 представлена расшифровка сигнала «sSWITCHINF»;

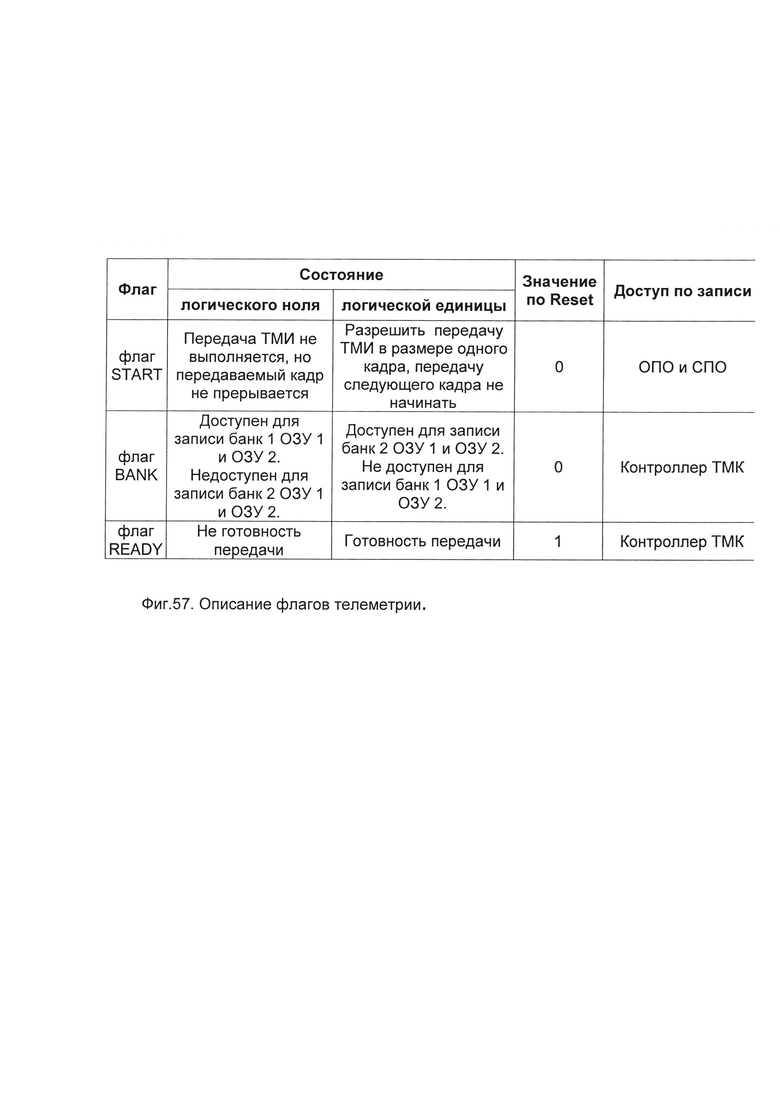

• на фиг.57 представлено описание флагов телеметрии.

Указанные преимущества заявляемой вычислительной системы с холодным резервом (ВСХР) перед прототипом достигаются за счет того, что в нее, содержащую два идентичных канала (ВМ1 и ВМ2), каждый из которых состоит из процессора 1, памяти 2, первого устройства ввода-вывода 3, дополнительно введены первый 4, второй 5, третий 6, четвертый 7, пятый 8, шестой 9, седьмой 10, восьмой 11 и девятый 12 генераторы, второй процессор 13, второе ОЗУ 14, первое ППЗУ 15, второе ППЗУ 16, системный контроллер ВМ 17, второе устройство ввода-вывода 18, третье устройство ввода-вывода 19, четвертое устройство ввода-вывода 20, пятое устройство ввода-вывода 21, узел сброса по питанию (reset power) 22, первый узел гальванической развязки 23, второй узел гальванической развязки 24, вторичный источник питания 25, выходы которого вырабатывают 1.5 В, 1.8 В и 3.3 В, в систему дополнительно введено устройство управления восстановлением (YYB), содержащее системный контроллер YYB 26, узел датчика поражающих факторов (далее - датчик ПФ) 27, внешнюю память MRAM 28, узел управления резервом 29, узел движения 30, узел времени (TIME) 31, узел телеметрии (ТМК) 32, узел сброса по питанию (reset power) 33, шестое устройство ввода-вывода 34, генератор 35, фильтр 36 и узел питания 37, выходы которого вырабатывают 1,5 В и 3,3 В, а вход соединен с выходом 38 фильтра 36 и с первыми входами каналов ВМ1 и ВМ2, первые группы выходов 39, 40 которых соединены с первой и второй группами входов системного контроллера YYB 26, первая 41 и вторая 42 группы выходов которого соединены с группами входов внешней памяти MRAM 28 и узла телеметрии 32 соответственно, группа входов-выходов 43 внешней памяти MRAM 28 и группа выходов 44 узла телеметрии ТМК 32 соединены с группой входов-выходов и третьей группой входов системного контроллера YYB 26, вторая 45 и первая 46 управляющие группы выходов которого соединены с первыми группами входов узлов датчика ПФ 27 и управления резервом 29, первые группы выходов 47,48 которых соединены с четвертой и пятой группами входов системного контроллера YYB 26, третья группа выходов 49 которого соединена с первым входом узла движения 30 и первой группой входов узла времени TIME 31, группа выходов 50 которого соединена с шестой группой входов системного контроллера YYB 26, четвертая 51 и пятая 52 группы выходов которого соединены с первыми группами входов первого и второго каналов ВМ1 и ВМ2, первые выходы которых соединены между собой, со входом шестого устройства ввода-вывода YYB 34, с выходами третьих устройств ввода-вывода 19 и являются первым выходом 53 ВСХР, первая 54 и вторая 55 группы выходов которой соединены с первой и второй группами выходов узлов движения 30 и датчика ПФ 27 соответственно, а первая 56 и вторая 57 группы входов соединены с группой входов узла движения 30 и второй группой входов узла датчика ПФ 27, первый выход которого является вторым выходом 58 ВСХР, первый вход 59 которой соединен с первым входом узла времени TIME 31, третья 61 и вторая 60 группы входов которого соединены со вторыми группами выходов узлов движения 30 и управления резервом 29, первый выход 62 и вход 63 которого соединены со входом и вторым выходом узла датчика ПФ 27, причем первый 64 и второй 65 входы системного контроллера YYB 26 соединены с выходами шестого устройства ввода-вывода 34 и генератора 35, третий 66 выход ВСХР в каждом канале соединен с выходами вторых 18 устройств ввода-вывода, входы-выходы которых соединены с шиной PCI 67, которая соединена с первыми входами-выходами первых 1 и вторых 13 процессоров, со входами - выходами третьих 19, четвертых 20 и пятых 21 устройств ввода-вывода, со входами - выходами системных контроллеров 17 и с выходами генераторов 33 МГц 12, причем вторые 68 и третьи 69 группы входов-выходов первых процессоров 1 соединены со входами-выходами первых ОЗУ2 и первых ППЗУ15, причем группы выходов 70 первых процессоров 1 соединены с первыми группами входов вторых процессоров 13, вторые 71 и третьи 72 группы входов-выходов которых соединены с группами входов-выходов вторых ОЗУ 14 и с группами входов-выходов вторых ППЗУ 16, вторые 73 группы входов-выходов первых ППЗУ 15 соединены с первыми группами входов-выходов первых устройств ввода-вывода 3, вторые 74 группы входов-выходов которых соединены с четвертыми группами входов-выходов первых процессоров 1, первые 75 группы входов которых соединены с первыми группами выходов системных контроллеров ВМ 17, вторые 76 группы выходов которых соединены со вторыми группами входов вторых процессоров 13, группа выходов 77 которых соединена со вторыми группами входов первых процессоров 1, первые 78, вторые 79 и третьи 80 входы которых соединены с выходами генераторов первым 125 МГц 4, вторым 80 МГц 5 и третьим 24 МГц 6 соответственно, а четвертые 81 входы которых соединены с выходами седьмых генераторов 25 МГц 10 и первыми входами первых устройств ввода-вывода 3, вторые входы которых соединены между собой и со вторым 82 входом ВСХР, а третьи входы соединены с первыми 83 выходами первых процессоров, пятые входы которых соединены с первыми выходами 84 системных контроллеров ВМ 17, вторые выходы 85 которых соединены с первыми входами вторых процессоров 13, вторые 86 и третьи 87 входы которых соединены с выходами пятых генераторов 24 МГц 8 и шестых генераторов 25 МГц 9, первые 88 группы входов системных контроллеров ВМ 17 соединены с группами выходов вторых узлов гальванической развязки 24, причем третьи 89 группы выходов системных контроллеров ВМ 17 соединены с группами входов первых узлов гальванической развязки 23, причем первые 90 и вторые 91 входы системных контроллеров ВМ 17 соединены с узлами сброса по питанию 22 и четвертыми генераторами 24 МГц 7, причем выходы 92 восьмых генераторов 12 МГц 11 соединены с первыми входами вторых 18, третьих 19, четвертых 20 и пятых 21 устройств ввода-вывода, причем выходы четвертого 20 и пятого 21 устройств ввода-вывода канала ВМ1 соединены с выходами четвертого 20 и пятого 21 устройств ввода-вывода канала ВМ2 и являются четвертым 93 и пятым 94 выходами системы ВСХР, причем третья 95 группа выходов датчика ПФ 27 соединена с седьмой группой входов системного контроллера YYB 26, тактовый 96 и сбросовый 97 выходы которого соединены с тактовыми и сбросовыми входами узлов датчика ПФ 27, управления резервом 29, движения 30, времени (TIME) 31 и телеметрии (ТМК) 32, причем второй 98 и третий 99 выходы узла управления резервом 29 соединены со вторыми входами вторичных источников питания 25 в каждом канале ВМ1 и ВМ2, третья 100 группа выходов YYR 29 соединена со второй группой входов узла ТМК 32, вторая группа выходов которого является третьей 101 группой выходов ВСХР, третья 102 группа входов которой соединена с восьмой группой входов системного контроллера YYB 26, третий вход 103 которого соединен с выходом узла сброса по питанию 33, а шестая группа выходов 104 соединена с группой входов шестого устройства ввода-вывода 34, причем выход 105 MKORST системного контроллера ВМ 17 соединен со вторыми входами вторых 18, третьих 19, четвертых 20 и пятых 21 устройств ввода-вывода.

Системный контроллер ВМ 17 в каждом канале содержит узел стартовой диаграммы 106 (START), узел сопряжения с шиной PCI 107 (Y_PCI), узел памяти PCI 108 (Y_RAM2), узел приема информации с LVDS 109 (Y_MB_REC), узел памяти телеметрического канала 110 (Y_TLMRAM), узел передачи информации в LVDS 111 (Y_BM_TRAN), узел формирования частоты 112 (PLL), первый элемент И 113, второй элемент И 114, первую группу мультиплексоров 115, вторую группу мультиплексоров 116, группу элементов ИЛИ 117, группа выходов которой соединена в каждом канале с первой и побайтно со второй группами входов первой группы мультиплексоров 115, группа выходов которой соединена с группой входов узла Y_PCI 107, первая группа выходов 118 которого соединена с первыми группами входов узла Y_RAM2 108 и узла Y_TLMRAM 110, первая группа выходов которого соединена с первой группой входов группы элементов ИЛИ 117, вторая группа входов которой соединена с первой группой выходов узла Y_RAM2 108, причем первая группа выходов Y_BM_TRAN 111 является третьей группой выходов 89 системного контроллера ВМ 17, сигнал BMCLK_O которой соединен с первым входом узла Y_BM_TRAN 111 и является первым выходом PLL 112, второй 119 выход которого соединен с первым входом узла Y_MB_REC 109, первая 120, вторая 121, третья 122 и четвертая 123 группы выходов которого соединены со второй, третьей, четвертой и пятой группами входов узла Y_TLMRAM 110, вторая 124, третья 125 и четвертая 126 группы выходов которого соединены с первой, второй и третьей группами входов узла Y_BM_TRAN 111, четвертая группа входов которого соединена с пятой группой выходов 127 узла Y_MB_REC 109, шестая 128 группа выходов которого соединена с пятой группой входов узла Y_BM_TRAN 111, седьмая 129 группа выходов Y_MB_REC 109 соединена со второй и шестыми группами входов узлов Y_RAM2 108, Y_TLMRAM 110 и Y_BM_TRAN 111 соответственно, а восьмая группа выходов соединена с первой и седьмыми группами входов узлов START 106, Y_TLMRAM 110 и Y_BM_TRAN 111 соответственно и является первой 75 и второй 76 группами выходов системного контроллера ВМ 17, которые также соединены с девятой, десятой и одиннадцатой группами выходов узла Y_MB_REC 109, первый вход 90 системного контроллера ВМ 17 соединен с первыми входами узлов START 106, Y_RAM2 108, Y_TLMRAM 110 и Y_BM_TRAN 111, причем группа выходов 130 узла START 106 соединена с восьмой группой входов узла Y_BM_TRAN 111, четвертый сигнал которой соединен с первыми входами PLL 112 и первым элементом И 113, пятый сигнал которой соединен с первым входом узла Y_PCI 107, шестой сигнал которой соединен с прямым входом второго элемента И 114 и со вторым входом узла Y_MB_REC 109, третий вход которого соединен со вторыми входами узлов START 106, Y_RAM2 108, Y_TLMRAM 110, с третьим входом узла Y_BM_TRAN 111 и является вторым входом 91 системного контроллера ВМ 17, группа входов 88 которого соединена с группой входов узла Y_MB_REC 109 и со вторым входом PLL 112, третий выход которого соединен со вторым входом первого элемента И 113, выход которого соединен с инверсным входом второго элемента И 114, выход 131 которого соединен с четвертым входом узла Y_MB_REC 109, причем вторая группа выходов узла Y_PCI 107 соединена с первой группой входов и побайтно со второй группой входов второй группы мультиплексоров 116, группа выходов 132 которой соединена с третьей группой входов узла Y_RAM2 108 и восьмой группой входов узла Y_TLMRAM 110, пятая группа выходов 133 которого соединена с девятой группой входов узла Y_BM_TRAN 111, третий вход узла Y_TLMRAM 110 соединен с третьим входом узла Y_RAM2 108 и выходом 13 узла Y_PCI 107, группа входов-выходов которого соединена с четвертыми входами узлов Y_TLMRAM 110 и Y_RAM2 108 и является группой входов-выходов 67 системного контроллера ВМ 17, причем пятые 135 входы узлов Y_TLMRAM 110 и Y_RAM2 111 соединены с корпусом, шестой вход 136 узла Y_TLMRAM 110 соединен с питанием, выход 137 узла Y_TLMRAM 110 соединен с управляющими входами первой 115 и второй 116 группами мультиплексоров, причем седьмой, восьмой и девятый сигналы группы выходов 130 узла START 106 являются первым 84, вторым 85 и третьим 105 (MKORST) выходами системного контроллера ВМ 17.

Узел приема информации с LVDS 109 (Y_MB_REC) в каждом канале содержит первый узел REC0 138, второй узел REC1 139, третий узел REC2 140, узел формирования управляющих сигналов (Y_FYS) 141, первую группу инверторов 142, вторую группу инверторов 143, инверсная группа выходов которой соединена с первой группой входов узла Y_FYS 141, первая, вторая, третья, четвертая, пятая, шестая, седьмая, восьмая, девятая, десятая, одиннадцатая группы выходов которого соединены с первой 120, второй 121, третьей 122, четвертой 123, пятой 127, шестой 128, седьмой 129, восьмой 75, 76, девятой 75, 76, десятой 75 и одиннадцатой 76 группами выходов узла Y_MB_REC 109, первый, второй и третий сигналы группы входов 88 которого соединены с первыми входами узлов REC0 138, REC1 139, REC2 140 соответственно, вторые входы которых соединены между собой, с первым входом узла Y_FYS 141 и являются первым входом 119 узла Y_MB_REC 109, второй вход 130(6) которого соединен с инверсным входом узла Y_FUS 141, вторая группа входов которого соединена с группой выходов узла REC0 138 и с группой входов первой группы инверторов 142, инверсная группа выходов которой соединена с третьей группой входов узла Y_FYS 141, четвертая группа входов которого соединена с группой выходов узла REC1 139 и с группой входов второй группы инверторов 143, пятая группа входов узла Y_FYS 141 соединена с группой выходов узла REC2 140, третий вход которого соединен со вторым входом узла Y_FYS 141, с третьими входами узлов REC0 138, REC1 139 и является третьим входом 91 узла Y_MB_REC 109, четвертый вход 131 которого соединен с третьим входом узла Y_FYS 141 и с четвертыми входами узлов REC0 138, REC1 139 и REC2 140.

Узел передачи информации в LVDS 110 Y_BM_TRAN в каждом канале содержит первый узел TRAN 0 144, второй узел TRAN 1 145, третий узел TRAN 2 146, узел формирования управляющих сигналов передатчика Y_FYS_BM_TRAN 147, группа выходов 89 узла Y_BM_TRAN 110 соединена с выходами узлов TRAN 0 144, TRAN 1 145, TRAN 2 146, группы входов которых соединены с первой, второй и третьей группами выходов узла Y_FYS_ BM_TRAN 147, первая группа входов которого соединена с группой выходов первого узла TRAN 0 144, первый вход которого соединен с первыми входами узлов TRAN 1 145, TRAN 2 146 и является первым входом 89 узла Y_BM_TRAN 110, первая 124, вторая 125, третья 126, четвертая 127, пятая 128, шестая 129, седьмая 75, 76, восьмая 130 и девятая 133 группы входов которого соединены со второй, третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой и десятой группами входов узла Y_FYS_TRAN 147, причем первый сигнал восьмой 130 группы входов которого соединен со вторыми входами узлов TRAN 0 144, TRAN 1 145, TRAN 2 146, третьи входы которых соединены между собой и являются третьим 91 входом узла Y_MB_TRAN 110, второй вход 90 которого соединен с четвертыми входами узлов TRAN 0 144, TRAN 1 145, TRAN 2 146, причем группа выходов узла TRAN 1 145 соединена с одиннадцатой группой входов узла Y_FYS_BM_TRAN 147.

Системный контроллер YYB 26 содержит узел приема данных (YYB_REC) 148, узел управления внешней памятью (Y_MRAM) 149, узел передачи данных (YYB_TRAN) 150, узел YMKO 151, первый PLL 152, второй PLL 153, первый мультиплексор 154, второй мультиплексор 155, первый триггер 156, второй триггер 157, первый элемент И 158, второй элемент И 159, третий элемент И 160, четвертый элемент И 161, пятый элемент И 162, элемент 3И-ИЛИ 163, первый элемент ИЛИ 164, второй элемент ИЛИ 165, первую группу мультиплексоров 166, вторую группу мультиплексоров 167, группа выходов которой является пятой группой выходов 52 системного контроллера YYB 26, а сигнал MBCLK2 которой соединен с выходом второго мультиплексора 155, первый вход которого соединен с корпусом, а второй вход соединен с первым входом первого мультиплексора 154 и первым выходом первого PLL 152, инверсный выход 168 которого соединен с первым входом узла Y_MKO 151, группа выходов Upr2_MKO которого и сигнал TLV являются первой управляющей группой выходов 45 системного контроллера YYB 26, вторая управляющая группа выходов 46 которого состоит из первой и третьей групп выходов узла YYB_REC 148, из первой группы выходов узла Y_MKO 151 и из выхода второго триггера 157, информационный вход которого соединен с первым входом третьего элемента И 160 и выходом первого элемента И 158, вход которого является первым сигналом пятой группы входов 48 системного контроллера YYB 26, второй и третий сигналы которой соединены с первым и вторым входами четвертого элемента И 161, выход 169 которого соединен с первым входом узла Y_MRAM 149, группа входов-выходов которого является группой входов-выходов 43 системного контроллера YYB 26, первая группа выходов 41 которого соединена с первой и второй группами выходов узла Y_MRAM 149, третья группа выходов 170 которого соединена со второй группой входов узла Y_MKO 151, вторая группа выходов которого соединена со второй группой выходов 42 системного контроллера YYB 26, третья группа выходов которого соединена с первой группой входов узла YYB_TRAN 150, с третьим входом узла YYB_REC 148, с третьей группой выходов узла Y_MKO 151, со вторым входом узла Y_MRAM 149, причем четвертая группа выходов 51 системного контроллера YYB 26 соединена с группой выходов первой группы мультиплексоров 166, а сигнал MBCLK1 которой соединен с выходом первого мультиплексора 154, второй вход которого соединен с корпусом, причем четвертый сигнал пятой группы входов 48 системного контроллера YYB 26 соединен с инверсным входом второго элемента И 159, с первыми входами элемента 3И-ИЛИ 163 и первого элемента ИЛИ 164, с управляющими входами первого мультиплексора 154 и первой группы мультиплексоров 166, первая группа входов которого соединена с первой группой входов второй группы мультиплексоров 167 и первой группой выходов 171 узла YYB_TRAN 150, вторая группа выходов 172 которого соединена с первой группой входов узла Y_MKO 151, третья, четвертая, пятая, шестая, седьмая, восьмая, девятая группы входов которого соединены с четвертой 173, пятой 174, шестой 175, седьмой 176, восьмой 177, девятой 178, десятой 179 группами выходов узла YYB_REC 148, первый выход которого соединен с третьим входом четвертого элемента И 161 и является первым сигналом одиннадцатой группы выходов 180, которая соединена со второй группой входов узла YYB_TRAN 150 и десятой группой входов узла Y_MKO 151, четвертая группа выходов которого является шестой группой выходов 104 системного контроллера YYB 26, вторая группа выходов 42 которого соединена со второй группой выходов узла Y_MKO 151, с двенадцатой и второй группами выходов узла YYB_REC 148, вторая и третья группы входов которого соединены с первой 39 и второй 40 группами входов системного контроллера YYB 26, третья группа входов 7 которого соединена с третьей группой входов узла YYB_TRAN 150, четвертая группа входов которого соединена с одиннадцатой группой входов узла Y_MKO 151 и является пятой группой входов 48 системного контроллера YYB 26, четвертая группа входов 47 которого соединена с двенадцатой группой входов узла Y_MKO 151, пятая группа выходов 181 которого соединена с пятой группой входов узла YYB_TRAN 150, шестая и седьмая группы входов которого соединены с шестой 182 и седьмой 183 группами выходов узла Y_MKO 151, тринадцатая группа входов которого соединена с восьмой группой входов узла YYB_TRAN 150 и является шестой группой входов 50 системного контроллера YYB 26, первый вход 64 которого соединен со вторым входом узла Y_MKO 151, первый и второй выходы которого соединены с первым и вторым входами пятого элемента И 162, выход которого соединен с третьим входом узла Y_MKO 151 и первым входом узла YYB_TRAN 150, девятая и десятая группы входов которого соединены с пятой 173 и четвертой 172 группами выходов узла YYB_REC 148, первый вход которого соединен с первым выходом второго PLL 153 и является первым сигналом второй группы выходов 42 системного контроллера YYB 26, второй сигнал которой соединен со вторым выходом второго PLL 153 и инверсным входом первого элемента И 158, причем второй вход узла YYB_REC 148 соединен с выходом 184 третьего элемента И 160, второй вход которого соединен с инверсным входом второго триггера 157, входом первого PLL 152, выходом первого триггера 156 и является сбросовым сигналом 97 системного контроллера YYB 26 и узлов Y_MRAM 149, YYB_TRAN 150 и Y_MKO 151, тактовые входы которых соединены с тактовым входом второго триггера 157, узла YYB_REC 148 и выходом первого PLL 152 и является тактовым выходом 96 системного контроллера YYB 26, причем управляющий вход второго мультиплексора 155 соединен с управляющими входами второй группы мультиплексоров 167, с прямым входом второго элемента И 159, вторым входом первого элемента ИЛИ 164 и является пятым сигналом пятой группы входов 48 системного контроллера YYB 26, сигналы BMCLK1 и BMCLK2 первой 39 и второй 40 групп входов которых соединены со вторым и третьим входами элемента 3И-ИЛИ 163, выход которого соединен со входом второго PLL 153, а четвертый, пятый и шестой входы которого соединены с выходом второго элемента И 159, инверсным выходом первого элемента ИЛИ 164 и корпусом соответственно, причем второй 65 и третий 103 входы системного контроллера YYB 26 соединены с тактовым и инверсным сбросовым входами первого триггера 156 соответственно, информационный вход которого соединен с питанием, причем шестой и седьмой сигналы пятой группы входов 48 системного контроллера YYB 26 соединены с первым и вторым входами второго элемента ИЛИ 165, выход 185 которого соединен со вторым входом узла YYB_TRAN 150, третий вход которого соединен с первым выходом 186 первого PLL1 52, причем вторые группы входов первой 166 и второй 167 групп мультиплексоров являются константой «7», причем первая группа входов узла YYB_REC 148 соединена с пятой группой входов 48 системного контроллера YYB 26, седьмая 95 и восьмая 102 группы входов которого соединены с четырнадцатой и пятнадцатой группами входов узла У_МКО 151.

Узел управления резервом (YYR) 29 содержит узел переключения резервов (ASR) 187, машину состояний (MS) 188, первый узел определения годности (GOOD1) 189, второй узел определения годности (GOOD2) 190 и узел определения режима реакции (YORR) 191, первая и вторая группы выходов которого являются первой группой выходов 48 узла YYR 29, которая также состоит из первой группы выходов узла ASR 187, из первых групп выходов и первых выходов узлов GOOD1 189 и GOOD2 190, первые группы входов которых соединены со второй группой выходов узла ASR 187, первый выход которого и второй сигнал группы выходов MS 188, который также соединен с первым входом узла ASR 187, являются второй группой выходов 60 узла YYR 29, третья и четвертая группы выходов узла ASR 187 соединены с первой и второй группами входов узла YORR 191, третья группа выходов которого соединена с третьей группой выходов 100 YYR 29, выход 62 которого соединен с первым сигналом группы выходов MS 188, вход которой соединен со входом 63 узла YYR 29, первая группа входов 46 которого состоит из группы UPR_MKO, которая соединена с первой группой входов узла ASR 187, со вторыми группами входов узлов GOOD1 189 и GOOD2 190 и с третьей группой входов узла YORR 191, и из группы UPR_REC, которая соединена с третьими группами входов узлов GOOD1 189 и GOOD2 190, с четвертой, пятой и шестой группами входов узла YORR 191, седьмая группа входов которого соединена со второй группой выходов узла GOOD1 189, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами узлов ASR 187, GOOD2 190, YORR 191, MS 188 и являются тактовым 96 и сбросовым 97 входами узла YYR 29, причем выход узла YORR 191 соединен со вторым входом узла ASR 187, вторая и третья группы выходов узла GOOD2 190 соединены с восьмой и девятой группами входов узла YORR 191, причем второй и третий выходы узла ASR 187 соединены со вторым и третьим выходами узла YYR 29.

Узел движения (Y_D) 30 содержит первый анализатор импульсов (A_RCIMP1) 192, второй анализатор импульсов (A_RCIMP2) 193, первый генератор импульсов (G_TRIMP1) 194, второй генератор импульсов (G_TRIMP2) 195, выход которого является вторым сигналом первой группы выходов 54 узла Y_D 30, а первый сигнал которой соединен с выходом первого генератора G_TRIMP1 194, инверсный разрешающий вход которого соединен с инверсным разрешающим входом второго генератора G_TRIMP2 195 и является входом 49 узла Y_D 30, вторая группа выходов 61 которого соединена с выходами первого и второго анализаторов импульсов G_RCIMP1 192, G_RCIMP2 193, информационные входы которых являются первой группой входов 56 узла Y_D 30, тактовый 96 и сбросовый 97 входы которого соединены с тактовыми и сбросовыми входами A_RCIMP1 192, A_RCIMP2 193, G_TRIMP1 194, G_TRIMP 195.

Узел управления внешней памятью (Y_MRAM) 149 содержит кодер_L (K_L) 196, кодер_Н (K_Н) 197, узел управления (Y_Y) 198, узел формирования временной диаграммы MRAM (Y_DMRAM) 199, декодер_L (DK_L) 200, декодер_Н (DK_H) 201, группа выходов которого объединяется с группой выходов DK_L 200 и является первой группой входов узла Y_Y 198, первая группа выходов которого соединена с третьей группой выходов 170 Y_MRAM 149, первая группа выходов 41 которого является первыми, вторыми и третьими выходами узлов Y_Y 198 и Y_DMRAM 199 и первой группой выходов узла Y_DMRAM 199, которая также соединена со второй группой входов узла Y_Y 198, вторая группа выходов которого соединена с первой группой входов узла Y_DMRAM 199, вторая группа выходов которого соединена с группами входов DK_L 200, DK_H 201 и с третьей группой входов узла Υ_Υ 198, Υ которого соединена со второй группой входов узла Y_DMRAM 199 и является первой группой входов 173 узла Y_MRAM 149, вторая группа входов 174 которого соединена с группами входов узлов K_L 196, K_Н 197 и пятой группой входов узла Υ_Υ 198, четвертый выход которого соединен с первым входом узла Y_DMRAM 199, четвертый выход которого соединен с первым входом узла Y_Y 198, второй и третий входы которого соединены с первым 169 и вторым 49(1) входами узла Y_MRAM 148 соответственно, тактовый вход 96 которого соединен с тактовым входом узла Y_DMRAM 199, второй вход которого соединен с «питанием», а сбросовый вход которого соединен со сбросовым входом узла Y_Y 198 и является сбросовым входом 97 узла Y_MRAM 149, двунаправленный вход-выход 43 которого является двунаправленным входом-выходом узла Y_DMRAM 199, причем шестая группа входов узла Y_Y 198 соединена с группами выходов K_L 196, K_Н 197.

Узел приемника YYB (YYB_REC) 148 содержит первый узел приема данных (MB_REC0) 202, второй узел приема данных (MB_REC1) 203, третий узел приема данных (MB_REC2) 204, узел формирования управляющих сигналов (У_ФУС) 205, первую группу инверторов 206 и вторую группу инверторов 207, группа выходов которой соединена с первой группой входов узла формирования управляющих сигналов 205, группы выходов с первой по двенадцатую которого являются группами выходов с первой по двенадцатую (42,46,173:180) узла приемника YYB_REC 148, первая группа входов 48 которого соединена со второй группой входов узла формирования управляющих сигналов 205, тринадцатая группа выходов которого соединена с информационными входами первого 202 MB_REC0, второго 203 MB_REC1 и третьего 204 MB_REC2 узлов приема данных, группы первых выходов которых соединены с третьей, четвертой и пятой группами входов узла формирования управляющих сигналов 205, а вторые группы выходов которых являются седьмой 176 группой выходов узла приемника YYB_REC 148 соответственно, шестая и седьмая группы входов узла формирования управляющих сигналов 205 являются второй 39 и третьей 40 группами входов узла приемника YYB_REC 148, первый вход 42(1) которого соединен с первыми входами первого 202 MB_REC0, второго 203 MB_REC1 и третьего 204 MB REC2 узлов приема данных, тактовые входы которых соединены между собой, с тактовым входом узла формирования управляющих сигналов 205 и являются тактовым входом 96 узла приемника YYB_REC 148, сбросовый вход 184 которого соединен со сбросовыми входами первого 202 MB_REC0, второго 203 MB_REC1 и третьего 204 MB_REC2 узлов приема данных и сбросовым входом узла формирования управляющих сигналов 205, восьмая группа входов которого соединена с группой выходов первой группы инверторов 206, группа входов которой соединена с группой выходов первого 202 узла приема данных MB_REC0, причем группа входов второй группы инверторов 207 соединена с группой выходов второго 203 узла приема данных MB_REC1, первый вход узла формирования управляющих сигналов 205 является третьим входом 49(2) узла приемника YYB_REC 148, вторые группы выходов узлов приема данных MR_REC0, MR_REC1, MR_REC2 являются седьмой группой выходов приемника YYB_REC.

Узел передатчика YYB (YYB_TRAN) 150 содержит первый узел передачи данных (TRAN0) 208, второй узел передачи данных (TRAN1) 209, третий узел передачи данных (TRAN2) 210, узел формирования управляющих сигналов передатчика (Y_FYS_TRAN) 211, первая, вторая и третья группы выходов которого соединены с информационными группами входов первого TRAN0 208, второго TRAN1 209 и третьего TRAN2 210 узлов передачи данных, выходы которых являются группой выходов 171 узла YYB_TRAN 150, группы входов с первой по десятую (49,180,44,48,181-183,50,174,173) которого соединены с группами входов с первой по десятую узла Y_FYS_TRAN 211, одиннадцатая и двенадцатая группы входов которого соединены с группами выходов первого TRAN0 208 и второго TRAN1 209 узлов передачи данных, разрешающие входы которых соединены между собой, с разрешающим входом третьего TRAN2 210 узла передачи данных и являются вторым 182 входом узла YYB_TRAN 150, третий 183 вход которого соединен с TCLK первого TRAN0 208, второго TRAN1 209 и третьего TRAN2 210 узлов передачи данных, тактовые и сбросовые входы которых соединены с тактовым 96 и сбросовым 97 входами узла YYB_TRAN 150, первый вход 45(1) которого соединен с первым входом узла Y_FYS_TRAN 211.

Узел Y_MKO 151 содержит узел формирования данных подадресов (Y_FDP) 212, узел управления оконечным устройством (Y_YOU) 213, узел приема данных (REC_OU) 214, кодирующий узел (CODER) 215, декодирующий узел (DECODER) 216, узел обнаружения ошибок (DETECTOR) 217 и контроллер 218, первая группа выходов которого является второй управляющей группой выходов 46 системного контроллера 26 и соединена с первым и вторым входами узла CODER 215 и с первыми группами входов узлов Y_YOU 213 и CODER 215, первая группа выходов Upr_coder которого соединена со второй группой входов узла Y_YOU 213, первая группа выходов 219 которого соединена с первыми группами входов узла приема данных REC_OU 214, узла обнаружения ошибок 217 и контроллера 218, а вторая группа выходов является четвертой группой выходов 104 узла МКО 151, первый вход 64 которого соединен с первым входом узла DECODER 216, первая группа выходов 220 которого соединена со второй группой входов узла REC_OU 214, первая 221, вторая 222 и третья 223 группы выходов которых соединены со второй, третьей и четвертой группами входов контроллера 218, вторая, третья, четвертая, пятая группы выходов и инверсный выход которого являются первой управляющей группой выходов 45 Upr2_contr системного контроллера YYB 26, которая также соединена с первой группой входов узла Y_FDP 212, первая группа выходов которого соединена с пятой группой входов контроллера 218, первый выход 224 которого соединен с первым входом узла REC_OU 214, четвертая группа выходов 225 которого соединена с шестой группой входов контроллера 218 и с третьей группой входов узла Y_YOU 213, четвертая группа входов которого соединена с третьей группой входов узла REC_OU 214 и второй группой выходов 226 узла DECODER 216, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами узлов Y_YOU 213, REC_OU 214, CODER 215, DECODER 216, обнаружения ошибок 217, контроллера 218 и являются тактовым 96 и сбросовым 97 входами узла Y_MKO 151, вторая 170, третья 173, четвертая 174 и десятая 180 группы входов которого соединены со второй, третьей, четвертой и пятой группами входов узла Y_FDP 212 соответственно, вторая и третья группы выходов которого соединены с седьмой и восьмой группами входов контроллера 218, второй и третий выходы которого соединены с первым и вторым входами узла обнаружения ошибок 217, выход которого соединен с первым входом контроллера 218, второй вход которого соединен с «питанием», группы входов с девятой по тринадцатую контроллера 218 соединены с «корпусом», а четырнадцатая группа входов соединена со второй и третьей группами выходов узла CODER 215, третий вход которого соединен с «корпусом», причем четырнадцатая группа входов узла Y_MKO 151 соединена с инверсными группами входов узлов Y_YOU 213, REC_OU 214, контроллера 218 и является восьмой группой входов 102 системного контроллера YYB 26, причем пятая группа выходов контроллера 218 соединена с пятой группой входов узла Y_YOU 213, третья, четвертая, пятая и шестая группы выходов которого являются группами выходов VM6,7MOD(2:0) 183, MB_TEST(2:0) 182, Upr_MKO, FSH1,2VM6,7REN 181 узла Y_MKO 151, пятая группа входов 175 которого соединена с шестой группой входом узла Y_YOU 213, причем первая 172, шестая 176, седьмая 177, восьмая 178, девятая 179, двенадцатая 47, тринадцатая 50 и четырнадцатая 95 группы входов узла Y_MKO 151 соединены с шестой, седьмой, восьмой, девятой, десятой одиннадцатой, двенадцатой и тринадцатой группами входов узла Y_FDP 212, причем седьмая группа выходов узла Y_YOU 213 соединена со второй группой выходов 42 узла Y_MKO 151.

Узел приемника REC_OU 214 содержит узел определения начала формата обмена с выделением командных слов и слов данных (Y_ONFO) 227 и дешифратор 228, группы выходов с первой по седьмую которого являются четвертой группой выходов 225 узла REC_OU 214, в состав которой также входят сигналы, соединенные с выходом дешифратора 228 и с первой группой выходов узла Y_ONFO 227, вторая группа выходов которого соединена с первой группой входов дешифратора 228 и является первой группой выходов 221 узла REC_OU 214, вторая группа выходов 222 которого соединена с третьей группой выходов узла Y_ONFO 227, четвертая группа выходов которого соединена со второй группой входов дешифратора 228 и является третьей группой выходов 223 узла REC_OU 214, первая 220, вторая 226 и третья 219 группы входов которого соединены с первой, второй и третьей группами входов узла Y_ONFO 227, инверсная группа входов которого соединена с инверсной группой входов 102 узла REC_OU 214, первый вход 224 которого соединен со входом узла Y_ONFO 227, тактовый и сбросовый входы которого соединены с тактовым и сбросовым входами дешифратора 228 и являются тактовым 96 и сбросовым 97 входами узла REC_OU 214, причем первый и второй входы дешифратора 228 соединены с «корпусом».

Работа вычислительной системы с холодным резервом.

ВСХР предназначена для решения информационно-расчетных задач, повышенной надежности в случае воздействия внешнего разрушительного потока частиц и излучений, реализованных в составе бортового программного обеспечения (далее - БПО), состоящего из специального программного обеспечения (далее - СПО), и общего программного обеспечения (далее - ΟΠΟ).

В зависимости от индекса варианта использования (вид СПО) ВСХР может быть использована в качестве:

- центральной бортовой вычислительной машины;

- вычислительной многоканальной системы обнаружения и самонаведения.

Структурная схема ВСХР представлена на фиг.1.

В состав ВСХР входят:

- устройство управления восстановлением (далее - YYB);

- два канала резервирования вычислительных машин (далее - ВМ), функционирующих в холодном резерве;

- БПО ВМ.

ΥΥΒ обеспечивает решение следующих задач:

- включение только одной ВМ в конкретный момент времени;

- функционирование в качестве оконечного устройства 34 (далее - ОУ) по мультиплексному каналу информационного обмена ГОСТ Ρ 52070-2003 (далее - МКИО);

- потоковая запись и хранение результатов работы ΟΠΟ и СПО;

- тестирование датчика ПФ;

- прием сигналов: метка времени 59, начало движения 56, внешнее воздействие 57 (данные от датчика ПФ);

- анализ результатов фонового контроля работы ВМ;

- переключение с одной ВМ на другую при отрицательных результатах фонового контроля работы ВМ;

- переключение с одной ВМ на другую по сигналам датчика ПФ;

- введение единой шкалы бортового времени работы с момента включения, с момента начала движения и с момента окончания последнего воздействия, регистрируемого датчиком ПФ;

- формирование и выдачу данных по телеметрическому каналу (далее - ТМК);

ΥΥΒ состоит из следующих основных узлов:

- узел движения 30 обеспечивает фиксацию факта начала движения ВСХР по сигналу начало движения;

- узел датчика ПФ 27 обеспечивает тестирование и регистрацию сигналов датчика ПФ;

- узел времени 31 обеспечивает прием сигнала метка времени;

- узел управления резервом 29 обеспечивает выключение и включение узлов питания ВМ;

- узел RESET POWER 33 обеспечивает формирование сигнала RST 103 (сброс по питанию);

- узел MRAM 28 обеспечивает хранение результатов работы ΟΠΟ и СПО в стойкой памяти MRAM;

- узел ТМК 32 обеспечивает трансляцию телеметрических данных по телеметрическому интерфейсу (TID, TIR) 101;

- системный контроллер YYB 26 обеспечивает обмен служебной, телеметрической информацией между YYB и ВМ по интерфейсу LVDS (узлы YYB_REC, Y_TRAN, Y_MRAM);

- УВВ 34 обеспечивает работу по ГОСТ Ρ 520-2003 одного устройства интерфейса в режиме ОУ с подключением ответвителя к магистральной шине без согласующего трансформатора для связи с наземной аппаратурой;

- генератор 12 МГц 35 задает рабочую частоту для системного контроллера ΥΥΒ 26;

- узел фильтрации 36 обеспечивает электромагнитную совместимость по цепям первичного питания;

- узел питания 37, обеспечивающий цифровое питание 3,3 В YYB из цепей первичного питания;

ВМ обеспечивает решение следующих задач:

- функционирование в качестве ОУ по ГОСТ Ρ 52070-2003;

- функционирование в качестве четырех контроллеров шины (далее - УВВ) по ГОСТ Ρ 070-2003;

- формирование телеметрических данных;

- функционирование в качестве контроллера Ethernet УВВ 3;

- выполнение алгоритмов, реализованных в составе ΟΠΟ и СПО в ППЗУ 15 и в ППЗУ 16;

- регулярное сохранение результатов работы ΟΠΟ и СПО в стойкой памяти MRAM YYB 28;

- загрузка ранее сохраненных результатов работы ΟΠΟ и СПО при переключении на другой резерв из стойкой памяти MRAM УУВ 28.

ВМ состоит из следующих основных узлов:

- УВВ 19 обеспечивает работу по ГОСТ Ρ 52070-2003 одного устройства интерфейса в режиме ОУ с подключением ответвителя к магистральной шине с согласующими трансформаторами, трех устройств интерфейса в режиме контроллера шины (КШ) (с аппаратурой верхнего уровня (АВУ)) с подключением ответвителя к магистральной и резервной магистральной шине с согласующим трансформатором;

- узел управления движением и коммуникацией включается в себя процессор 1-1, ОЗУ 2 и ППЗУ 15 и интерфейсы DDR, Flash, RapidIO, РК (разовые команды), PCI, которые обеспечивают выполнение алгоритмов, реализованных в ΟΠΟ и СПО.

Интерфейс DDR 68 обеспечивает взаимодействие процессора 1 1890 ВМ6Я с ОЗУ 2 типа SDRAM DDR ЕСС объемом 256 Мбайт и организацией 32Мх72 (8 разрядов шины данных используются для обнаружения и корректировки одиночных ошибок) со следующими параметрами:

- Частота работы - 100 МГц.

- Пропускная способность - 200 Мбит/с.

- Ширина шины данных м/сх памяти - 16 бит.

Интерфейс Flash 69 обеспечивает взаимодействие процессора 1 1890 ВМ6Я с ППЗУ 15 типа Flash объемом 8 Мбайт и организацией 8Мх8.

Адресное пространство ППЗУ 15 относительно процессора 1890 ВМ6Я 1 описано на фиг.38, а внутреннее адресное пространство на фиг.39.

- Интерфейс RapidIO 70 обеспечивает взаимодействие процессоров 1,13 1890 ВМ6Я и 1890 ВМ7Я.

- Интерфейс РК 75 обеспечивает взаимодействие процессора 1 1890 ВМ6Я с системным контроллером 17 и с узлами УУR 29, датчика ПФ 27 и движения 30 через СК YYB 26 и СК 17.

- Интерфейс PCI 67 обеспечивает взаимодействие между процессорами 1,13 1890 ВМ6Я и 1890 ВМ7Я, контроллерами УВВ (18-21) ГОСТ Ρ 52070-2003 и системным контроллером 17, который содержит регистры для работы с MRAM УУВ 28, телеметрическим каналом ТМК 32, узлами времени 31, движения 30, датчика ПФ 27, управление резервом 29, регистрами общего назначения.

- узел обнаружения включает в себя процессор 13, ОЗУ14 и ППЗУ 16, интерфейсы DDRII, SPI, RapidIO, РК и PCI, которые обеспечивают выполнение алгоритмов, реализованных в ΟΠΟ и СПО.

Интерфейс DDRII 71 обеспечивает взаимодействие процессора 13 1890 ВМ7Я с ОЗУ 14 типа SDRAM DDRII объемом 256 Мбайт и организацией 32Мх64 со следующими параметрами:

Частота работы - 125 МГц.

Пропускная способность - 500 Мбит/с.

Ширина шины данных м/сх памяти - 16 бит.

Интерфейс SPI 72 обеспечивает взаимодействие процессора 13 1890 ВМ7Я с ППЗУ 16 типа Flash объемом 16 Мбайт и организацией 128Мх1.

Адресное пространство ППЗУ 16 относительно процессора 13 1890 ВМ7Я описано на фиг.40, а внутреннее адресное пространство процессора 1890 ВМ7Я 13 при работе с Flash - на фиг.41.

Интерфейс RapidIO 70 обеспечивает взаимодействие процессоров 1,13 1890 ВМ6Я и 1890 ВМ7Я.

Интерфейс РК 76 обеспечивает взаимодействие процессора 13 1890 ВМ7Я с системным контроллером 17 и с узлами WR 29, датчика ПФ 27 и движения 30 через СК YYB26 и СК17.

Интерфейс PCI 67 обеспечивает взаимодействие между процессорами 1,13 1890 ВМ6Я и 1890 ВМ7Я, контроллерами УВВ (18-21) ГОСТ Ρ 52070-2003 и системным контроллером 17, который содержит регистры для работы с MRAM YYB 28, телеметрическим каналом ТМК 32, узлами времени 31, движения 30, датчиком ПФ 27, управления резервом YYR 29 регистрами общего назначения.

- узел УВВ 3 обеспечивает коммуникации по интерфейсу Ethernet 82;

Интерфейс обеспечения доступа к процессору 1 (1890 ВМ6Я) со стороны внешних абонентов. Тип интерфейса: Ethernet 100BASE-T.

- системный контроллер 17 обеспечивает управление движением АВУ, синхронизацию взаимодействия вышеописанных узлов согласно алгоритму работы и участвует в обмене служебной и телеметрической информацией с YYB по интерфейсу LVDS (Y_BM_REC, Y_BM_TRAN, Y_TLMRAM);

- узел RESET POWER 22 обеспечивает формирование сброса по питанию;

- генераторы 4-12 задают рабочие частоты для различных устройств и узлов;

- узел гальванически развязанных соединителей 23,24-представляет собой подключение гальванически развязанных интерфейсов МКИО и Ethernet через монтажное «ИЛИ» к внешним соединителям;

- узел питания 25 обеспечивает цифровое питание 3,3 В; 1,5 В; 1,8 В ВМ.

ВСХР на магистрали М2 53 функционирует в режиме трех оконечных устройств ОУ ВМ1 19, ОУ ВМ2 19, ОУ YYB 34.

Собственные адреса ОУ УУВ 34, ОУ ВМ1 19 и ОУ ВМ2 19 определяются индексом варианта использования системы и задаются внешними перемычками. Для предотвращения реакции на командное слово (КС) при недостоверном собственном адресе в ОУ YYB 34 реализован контроль по нечетности собственного адреса ОУ, использующий внешнюю перемычку.

ОУ YYB 34 подключается к магистральной шине М2 53 через ответвитель без согласующего трансформатора. Резервная магистральная шина отсутствует. ОУ ВМ подключаются к магистральной шине через ответвитель с согласующим трансформатором. Резервная магистральная шина отсутствует.

Для ОУ YYB 34 разряд 10 командного слова (КС) используется в качестве признака передачи КС (в соответствии с разделом 4 ГОСТ Ρ 52070-2003). Таким образом, количество доступных подадресов сокращается с 30 до 15, а коду команды управления (КУ) соответствует только код «111112». Положительным моментом от такого использования данного разряда является четкое разделение КС от ответного слова (ОС), что существенно упрощает разбор нештатных ситуаций.

ОУ YYB 34 реагирует на сообщения всех форматов. Разряд «принято управление интерфейсом» в ОС всегда установлен в «0». КУ «Блокировать i-передатчик» и «Разблокировать i-передатчик» обрабатываются как достоверные недопустимые команды в соответствии с разделом 5 ГОСТ Ρ 52070-2003.

В ОС ОУ ΥΥΒ 34 используются признаки «передача ОС», «ошибка в сообщении», «абонент занят», «неисправность ОУ», «неисправность абонента», «принята групповая команда» в соответствии с ГОСТ Ρ 52070-2003. Признаки «запрос на обслуживание» и «принято управление интерфейсом» не используются и установлены в логический ноль.

Структура информационных разрядов КС, принимаемых ОУ ΥΥΒ 34, представлена на фиг.42 и соответствует ГОСТ Ρ 52070-2003.

Структура информационных разрядов ОС, передаваемых ОУ ΥΥΒ, представлена на фиг.43 и соответствует ГОСТ Ρ 52070-2003.

Структура информационных разрядов передаваемых и принимаемых слов данных (СД) представлена на фиг.44 и соответствует ГОСТ Ρ 52070-2003.

Штатная работа контроллера шины (КШ) интерфейса ГОСТ Ρ 52070-2003 с ОУ УУВ 34 осуществляется по подадресам с «100002» по «101002» и с «101012» по «110002». При работе КШ по подадресам с «000012» по «011112» и с «110012» по «111012» ОУ УУВ выдает ОС с взведенным признаком «абонент занят» и не передает СД в формате 2.

Подадрес «111102» является признаком режима тестирования ОУ УУВ 34 и реализован в соответствии с разделом 4 ГОСТ Ρ 52070-2003.

Описание содержимого СД при работе по форматам 1 и 2 представлено на фиг.45.

ОУВМ 19 не функционирует в качестве ОУ по ГОСТ Ρ 52070-2003 до момента инициализации программным обеспечением процессоров 1,13 1890 ВМ6Я или 1890 ВМ7Я ВМ.

Узел датчика ПФ 27 предназначен для оперативной реакции на теоретически возможные сбои горячей ВМ методом переключения на другую ВМ, внешнее воздействие, регистрируемое датчиком ПФ 27 методом выключения горячей ВМ, выжиданием слепой зоны датчика ПФ 27 и последующего включения другой ВМ.

Регистры узла датчика ПФ представлены в адресном пространстве «100916».

С трех датчиков на датчик ПФ 27 поступают сигналы внешних воздействий 57 DPFVOZ1, DPFVOZ2, DPFVOZ3 данные сигналы мажорируются в узле датчика ПФ 27, формируя выходной сигнал DRFVOZO 58, затем если сигнал TLV равен '0' (факт наличия перемычек), то формируется сигнал SWITCH 63 (признак воздействия поражающих факторов), который поступает в узел YYR 29.

По команде, поступающей из МКО по второй группе управляющих выходов 45 системного контроллеры YYB, и по сигналу TEST, поступающему из машины состояний 188 YYR 29, запускается тест датчика ПФ.

По окончании сигнала сброс RESET счетчик состояния STATE находится в "00", устанавливая в '0' счетчик TIMER и сигнал TEST_OUT. При наличии сигнала TEST 62, содержимое счетчиков состояния и TIMER увеличивается на '1' и устанавливается в '1' сигнал TEST_OUT. По истечении 22 мсек (момент считывания показаний с датчиков) сигналы NORM, NOTNORM, NOTNORMRES переписываются в регистр MN, MNN, MNNR, которые вместе с внешним воздействием 57 по третьей группе выходов 95 поступают в системный контроллер YYB 26 для передачи в мультиплексный канал М2 53, узел ТМК 32 и в процессоры 1 и 13 по интерфейсу PCI 67. Вторая 55 группа выходов датчика ПФ 27 (VRR1, VRR2, VRR3) используется для наращивания системы.

Регистр узла датчика ПФ 27 доступен узлам движения 30 и управления резервом 29 через интерфейс PCI 67 по адресу «100916» фиг.46. Регистр содержит разряды счетчика времени с момента окончания воздействия поражающих факторов, регистрируемых датчиком ПФ 27. Разряды счетчика соответствуют разрядам сигнала «sSSSSCNT». Младший разряд счетчика содержит признак воздействия поражающих факторов (сигнал «tSWITCH»), вычисляемый по сигналам датчика ПФ 27, разряды с 19 по 1 определяют время с момента окончания воздействия датчика ПФ 27 с начала секунды (цена младшего разряда равна 3,2 мкс), разряды с 31 по 20 определяют время с момента окончания воздействия датчика ПФ 27 поражающих факторов в секундах. При возникновении признака воздействия поражающих факторов счетчик времени переходит в состояние ожидания снятия данного признака. После этого счетчик времени запоминает время снятия признака воздействия поражающих факторов и считает время методом вычисления разницы между текущим временем и запомненным. При отсутствии метки времени 59 текущее время вычисляется по внутреннему генератору, а при наличии - по внешнему сигналу метки времени 59.

Узел управления резервом 29 предназначен для управления переключением ВМ1 и ВМ2. YYR 29 состоит из машины состояний (МС) 188, узла переключения резервов (ASR) 187, узла определения годности 1 189, узла определения годности 2 190, узла определения режима реакции YYR 191.

Функциональная схема YYR 29 представлена на фиг.6.

Диаграмма работы МС 188 для управления ВМ1 и ВМ2 представлена на фигурах 23 и 24, где «sMKOLIVE» - искусственная годность, «sMKOSTRT» - обмен по подадресу 19 МКО, «ΡΟΝ1» - включение вторичного источника питания (ВИП) ВМ1, «ΡΟΝ2» - включение ВИП ВМ2, «CON1» - подача частоты в ВМ1, «CON2» - подача частоты в ВМ2, «ТОМ» - передача данных в ВМ1, «ΤΟΝ2» - передача данных в ВМ2, «sT» - счетчик времени, «sPOWST» - состояние автомата, «sVMLIVE» - аппаратная годность ВМ, «sS» - признак воздействия поражающих факторов ядерного взрыва (из МС 188), «sL» - признак годности резерва (из узла определения режима реакции 191), «V» - признак воздействия поражающих факторов ядерного взрыва во время штатной работы, «sT1» - счетчик времени включения ВМ1, «sT2» - счетчик времени включения ВМ2, и состоит из 15 состояний.

В состояние 0 МС 188 попадает при включении УУВ по сигналу «RESET». В этом состоянии ВМ1 и ВМ2 выключены, счетчики, кроме счетчика времени, сброшены в «0». МС 188 находится в этом состоянии до тех пор, пока по шине UPR1_MKO 46 из системного контроллера YYB 26 не придет параметр «sSRV», определяющий режим работы прибора (штатный или технологический). После того, как параметр «sSRV» будет получен, МС 188 подает сигнал 62(1) на ASR 187, по которому формируется сигнал PON1 98, включающий ВИП 25 ВМ1, подает опорную частоту CLK 96, сбрасывает счетчик времени в «0» и перейдет в состояние 1.

Состояние 1 предназначено для ожидания окончания аппаратных процессов, связанных с включением и инициализацией ВМ1. В этом состоянии автомат запускает счетчик времени. Если пришло воздействие 57, то МС 188 выключит ВМ1, снимет опорную частоту CLK 96 и перейдет в состояние 6. Если воздействия нет, то счетчик времени продолжает считать до 200 мс. В этом случае, если аппаратная годность ВМ1 зафиксирована до достижения счетчика времени 200 мс, то МС 188 начнет передавать данные в ВМ1 и перейдет в состояние 2. Если счетчик времени досчитал до 200 мс и аппаратная годность ВМ1 не зафиксирована, то ASR 187 фиксирует аппаратный отказ ВМ1 и МС 188 переходит в состояние 5.

Состояние 2 является основным рабочим состоянием ВМ1. В этом состоянии включена только ВМ1, а МС 188 анализирует признак годности (sL) ВМ1. Если признак годности не зафиксирован, то МС 188 остается в этом состоянии. Если же в процессе основной работы будет зафиксировано воздействие 57, то МС 188 перейдет в состояние 3 (по сигналу SWITCH 63 из узла ДПФ 27).

В состоянии 3 МС 188 в течение 1,7 мкс запрещает передачу данных и опорной частоты в ВМ1, после чего перейдет в состояние 4.

В состоянии 4 МС 188 в течение 4 мкс ожидает выключения опорной частоты и определяет причину переключения - воздействие или нет. В случае переключения по воздействию МС 188 выключит ВМ1 и перейдет в состояние 7. Если же переключение произошло по причине отсутствия сигнала годности ВМ1, то МС 188 выключит ВМ1, запустит счетчик времени на 10 мс, установив значение «88» в него, чтобы обеспечить паузу в 10 мс, и перейдет в состояние 5.

Состояние 5 предназначено для формирования корректной паузы перед включением ВМ2. Как только счетчик времени досчитал до значения равного или большего 98 мс, и, при этом, ВМ2 была выключена более, чем на 500 мс, то МС 188 включит ВМ2, подаст опорную частоту, сбросит счетчик времени в «0» и перейдет в состояние 9.

В состоянии 6 МС 188 находится до окончания воздействия 57. По окончанию воздействия 57 МС 188 сбросит счетчик времени и перейдет в состояние 5.

Состояние 7 по алгоритму работы аналогично состоянию 6.

Состояния 8-14 предназначены для работы с ВМ2 и по алгоритмам работы они аналогичны состояниям 1-7 соответственно, с той лишь разницей, что ВМ1 заменен на ВМ2, а ВМ2 - на ВМ1.

Примечание: Для состояний 1-7 постоянно декрементируется счетчик времени включения ВМ2, а для состояний 8 - 14 - счетчик времени включения ВМ1. Данные счетчики необходимы для исключения ситуаций, при которых одна и та же ВМ выключалась бы, а затем включалась менее чем через 500 мс.

Признак годности включенной ВМ (сигнал «sL») состоит из признаков годности аппаратуры LIVEBM и двух признаков годности узлов управления и коммуникаций (сигнал LIVEGOOD1 (UPR_G1)) и обнаружения (сигнал LIVEGOOD2 (UPR_G2)) и необходим для оперативной реакции системы на сбой методом переключения на другой заведомо годный резерв, а не попыткой (сериями попыток) восстановления сбившихся данных. В случае деградации элементной базы системы в результате воздействия поражающих факторов ядерного взрыва данный подход использует свойство «отжига» элементной базы, что продляет время успешной работы системы в целом.

Если YYB зарегистрировал аппаратный сбой, то сигнал «sL»=0.

С момента включения ВМ, в течение времени 1000 мс происходит включение питания, установка и снятие сигналов сброса процессоров (1890 ВМ6Я) 1 и (1890 ВМ7Я) 13 и загрузка первичного программного обеспечения. Сигнал «sL» в течение всего этого времени равен «1» до тех пор, пока процессор (1890 ВМ6Я) 1 не начал работать.

Процессоры работают независимо. Если хотя бы в одном из них зарегистрирован сбой, то «sL»=0, что свидетельствует о негодности ВМ и доступ к ресурсам стойкой памяти MRAM 28 закрыт.

«Момент запуска» процессора (1890 ВМ6Я) 1 определяется фактом первого увеличения счетчика интегрированного кода годности (ИКГ) «sVM6LIVEINC» на «1». «Момент запуска» процессора (1890 ВМ7Я) 13 определяется фактом первого увеличения счетчика интегрированного кода годности «sVM7LIVEINC» на «1».

Алгоритм работы узла переключения резерва 187 представлен на фиг.14,14а.

Узел переключения резерва 187 определяет диаграмму вкл/выкл внутренних узлов системы на фоне переключения ВМ.

Алгоритм работы узла определения режима реакции 191 представлен на фиг.13 и 13а.

Узел определения режима реакции 191 предназначен для определения режима реакции на воздействия и определения ВМ, передающих телеметрическую информацию в зависимости от годности процессоров.

Узел определения режима реакции 191 определяет наличие достоверных данных от ВМ на основе признаков их годности.

Узел определения режима реакции 191 определяет режим реакции УУВ в зависимости от режима работы узла датчика ПФ.

Определены три режима:

режим ожидания Tstest="00";

режим воздействия Tstest="01";

режим датчика ПФ Tstest="10";

Узел движения 30 предназначен для фиксации начала движения

Функциональная схема узла движения 30 представлена на фиг.7.

Узел движения 30 состоит из первого 192 и второго 193 анализаторов импульсов, первого 194 и второго 195 генераторов.

Алгоритмы работы узла движения схем Y_TRIMP и Y_RCIMP представлены на фиг.16, 17, 17а.

Анализаторы импульсов (192, 193) предназначены для контроля и наличия импульсов заданной длительности. Генераторы импульсов (194, 195) предназначены для генерации этих импульсов.

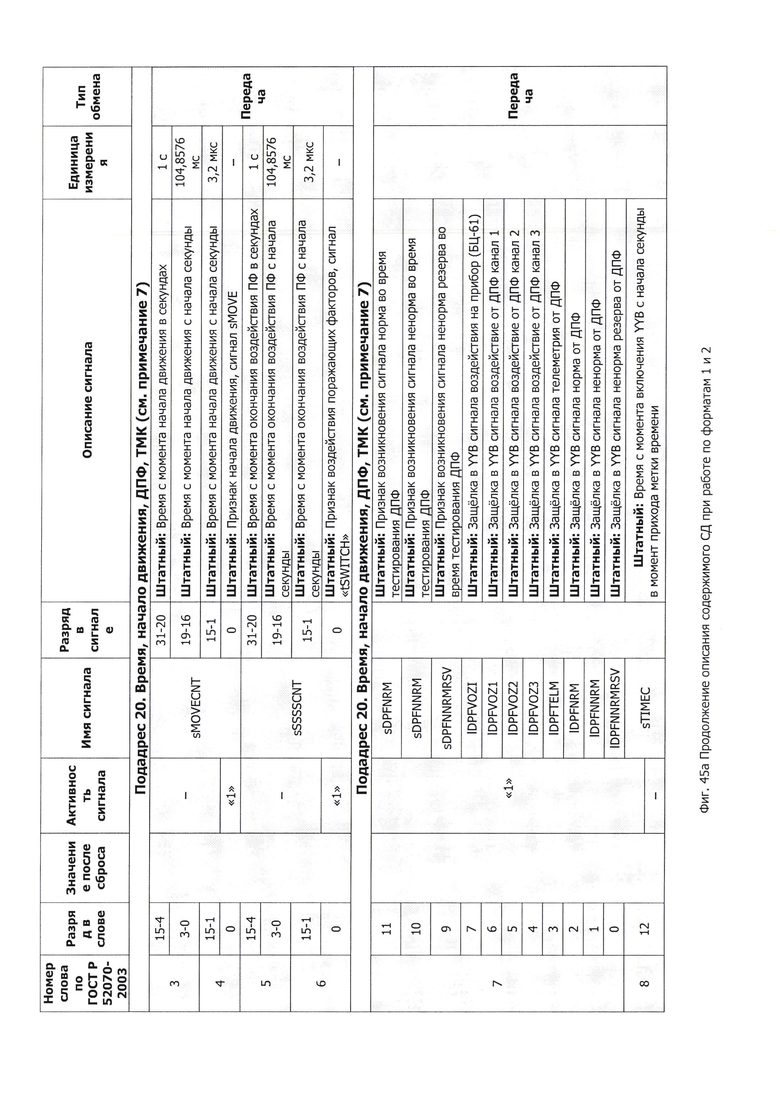

Регистр узла движения 30 доступен узлам «управления движением и коммуникацией» и «обнаружения» через интерфейс PCI 67 по адресу «100816» см. фиг.46, 46а, 46б. Регистр содержит разряды счетчика времени и доступен по чтению. Разряды счетчика соответствуют разрядам сигнала «sMOVECNT», описанным на фиг.45, 45а. Младший разряд счетчика содержит признак начала движения (сигнал «sMOVE»), возникающий при появлении сигнала «Начало движения» 56.

Признак устанавливается в ноль только при включении УУВ. После возникновении признака счетчик времени запоминает время возникновения признака и считает время методом вычисления разницы между текущим временем и запомненным. При отсутствии метки времени 59 текущее время вычисляется по внутреннему генератору, а при наличии - по внешнему сигналу метки времени 59.

Узел времени 31 предназначен для подсчета времени с момента включения прибора, начала движения объекта и с момента окончания воздействия.

Алгоритм работы узла времени 31 представлен на фиг.15, 15а, 15б.

Регистр узла времени 31 доступен узлам «управления движением и коммуникацией» и «обнаружения» через интерфейс PCI 67 по адресу «100716» см. фиг.46в.

Регистр содержит разряды счетчика, которые соответствуют разрядам сигнала «sTIMECNT», описанным на фиг.45, 45а. Младший разряд счетчика содержит признак отсутствия сигнала метки времени 59, возникающий, если в течение 1,5 с не приходит фронт внешнего сигнала метки времени 59. Разряд сбрасывается в ноль сразу же после появления фронта внешнего сигнала метки времени 59. В период, когда внешний сигнал метки времени 59 отсутствует, подсчет времени осуществляется по внутреннему генератору YYB 35. Какой-либо коррекции разрядов сигнала «sTIMECNT» при появлении или пропадании внешнего сигнала метки времени 59 не требуется, однако, следует учитывать различия в точности подсчета времени. Значение сигнала «sTIMECNT» также транслируется по интерфейсу ТМИ 101 (TID, TIC).

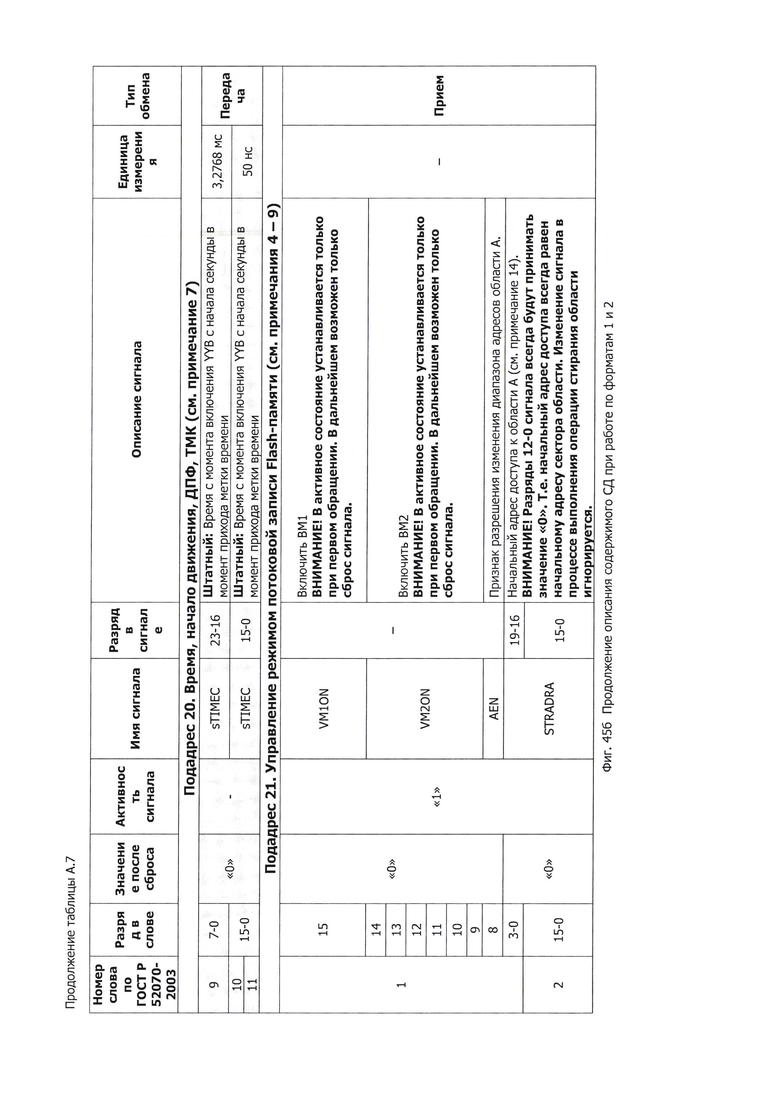

Узел стойкой памяти MRAM 28 YYB предназначен для хранения информации, требующей защиты от специальных воздействующих факторов.

Узел стойкой памяти MRAM 28 YYB доступен внешним абонентам по магистрали М2 53 и узлам «управления движением и коммуникацией» и «обнаружения» через интерфейс PCI 67.

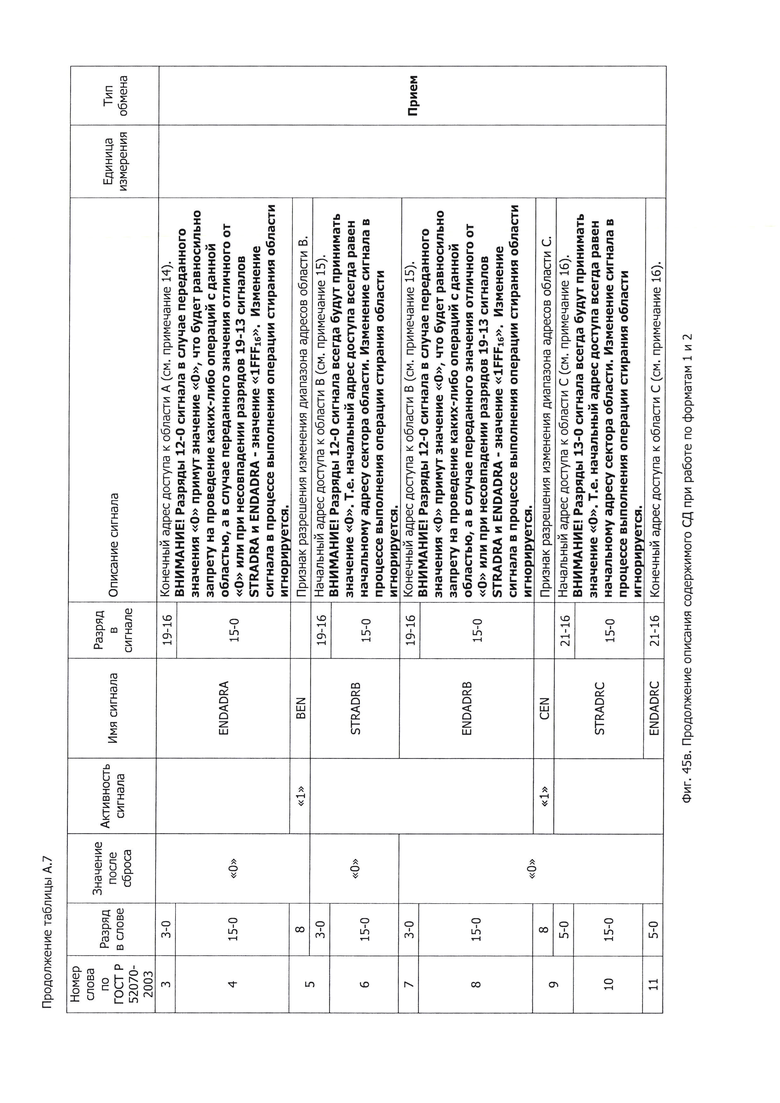

Регистры и флаги интерфейса MRAM YYB узла управления представлены в адресном пространстве «100216», «100316», «100416», «100516» (см. фиг.46а, 46б, 46в) и предназначены для управления кэшами чтения и кэшами записи, с помощью которых осуществляется чтение данных из памяти MRAM 28 и запись данных в память MRAM 28 соответственно. Кэши записи памяти MRAM 28 расположены в адресном пространстве «000016» - «01FF16» и «020016» - «03FF16». Кэши чтения памяти MRAM 28 расположены в адресном пространстве «040016» - «05FF16» и «060016» - «07FF16». (см. фиг.46) Кэши чтения и кэши записи памяти MRAM 28 являются независимыми, а работа с ними может осуществляться параллельно.

Регистры общего назначения R1 - R3 доступные как процессору 1 (1890 ВМ6Я), так и процессору 13 (1890 ВМ7Я) расположены в адресном пространстве «101016» - «101216» (см. фиг.46 г).

Узел стойкой памяти 28 YYB поддерживает как обычный (незащищенный) режим работы, так и защищенный (в режиме использования кода Хэмминга для защиты данных).

Абонент ОУ YYB 34 имеет доступ к ППЗУ 15, 16 ВМ, MRAM 28 (стойкой памяти) объемом 4МБ в режиме Хэмминга и 8МБ без режима Хэмминга и ОЗУ узла ТМК. Общее адресное пространство системы ВСХР при доступе к ней через ОУ YYB 34 (канал М2) представлено на фиг.49. Каждый адрес оперирует 32 разрядами данных (сигналы «sMKODW», «sMRAMDR», «sBMD»). При работе со стойкой памятью в режиме Хэмминга (сигнал «sHAMMING»=1) каждый адрес оперирует 32 разрядами данных, а без режима Хэмминга - 64 разрядами данных. Примечание - Процессоры 1,13 (1890 ВМ6Я или 1890 ВМ7Я) ВМ работают со стойкой памятью только в режиме Хэмминга.

При включении, абонент ОУ YYB 34 проводит анализ текущих версий ПЛИС YYB и ПЛИС ВМ с версиями, записанными в MRAM 28 (стойкую память) по адресу «70001016». При несовпадении, версии в MRAM 28 (стойкой памяти) заменяются текущими версиями, а параметры наработки системы, находящиеся в MRAM 28 (стойкой памяти) по адресам «70000016» - «70000F16», сбрасываются в «0».

Команды управления ППЗУ представлены на фиг.50.

ОУ ВМ не функционирует в качестве ОУ по ГОСТ Ρ 52070-2003 до момента инициализации программным обеспечением процессоров 1,13 1890 ВМ6Я или 1890 ВМ7Я ВМ.

В защищенном режиме работы (сигнал «sHAMMING»=1), используется код Хэмминга, а обмен данными происходит посредством 32-разрядных слов данных, защищенных 32 дополнительными разрядами кода Хэмминга (см. фиг.47). В штатном режиме работы системы (сигнал «sSRV»=1, см. фиг.45) для обмена данными между узлами «управления движением и коммуникацией» и «обнаружения» и узлом стойкой памяти MRAM 28 УУВ используется только защищенный режим.

Все 32 разряда слова данных условно разделены на 12 групп, каждая из которых отнесена к одной из трех групп надежности.

Первая группа надежности характеризуется тем, что 1 разряд слова данных кодируется с использованием 2 разрядов дополнительного кода Хэмминга. Таким образом, данная группа допускает появление и исправление одной ошибки на 3 разряда защищенного кодом Хэмминга слова.

Вторая группа надежности характеризуется тем, что 2 разряда слова данных кодируются с использованием 3 разрядов дополнительного кода Хэмминга. Таким образом, данная группа допускает появление и исправление одной ошибки на 5 разрядов защищенного кодом Хэмминга слова.

Третья группа надежности характеризуется тем, что 4 разряда слова данных кодируются с использованием 3 разрядов дополнительного кода Хэмминга. Таким образом, данная группа допускает появление и исправление одной ошибки на 7 разрядов защищенного кодом Хэмминга слова.

Защищенное кодом Хэмминга слово имеет 4 первых группы надежности, 2 вторых группы надежности и 6 третьих групп надежности (см. фиг.47) и допускает исправление до 12 ошибок, при условии их возникновения в разных группах.

Узел ТМК 32 предназначен для передачи телеметрической информации (ТМИ 101).

Процесс передачи ТМИ 101 состоит из посылки кадров.

Процесс передачи ТМИ осуществляется только в одном направлении без гарантии доставки, т.е. ВСХР не формирует ответов на передаваемые из нее кадры.

Для хранения и передачи ТМИ 101 в ВСХР организовано два ОЗУ, в каждом по 2 банка емкостью 4 КБ каждый. Первое ОЗУ (ОЗУ1) предназначено для записи ТМИ, формируемой процессором 1 1890 ВМ6Я. Второе ОЗУ (ОЗУ2) предназначено для записи информации, формируемой процессором 13 1890 ВМ7Я. При этом в общем программном обеспечении (ΟΠΟ) и специальном программном обеспечении (СПО) ВСХР предусмотрена возможность заполнения банков ОЗУ 1 и ОЗУ 2 как средствами процессора 1 1890 ВМ6Я, так и процессора 13 1890 ВМ7Я.

ТМИ из ВСХР передается в виде набора кадров. Структура кадра приведена на фиг.48. Каждый кадр представляет собой последовательность пакетов (восемь обязательных пакетов, А пакетов (от 1 до 1024) с данными ОЗУ 1 и В пакетов (от 1 до 1024) с данными ОЗУ 2, заканчивающихся межкадровой паузой. Общее число пакетов в кадре - от 10 до 2056. Минимальное значение межкадровой паузы должно быть равно времени передачи одного пакета. Максимальное значение межкадровой паузы определяется оперативностью работы инициатора передачи.

При включении системы или при переключении на резерв инициатором передачи кадров является контроллер телеметрического канала ТМК 32 до момента запуска процессоров 1,13 1890 ВМ6Я или 1890 ВМ7Я (аппаратная телеметрия с параметрами А=1 и В=1, пакеты 9 и 10 содержат «мусорные» значения), после чего инициатором передачи кадров становится либо процессор 1 1890 ВМ6Я, либо процессор 13 1890 ВМ7Я (программная телеметрия с программным управлением параметрами А и В). При переключении на резерв передаваемый кадр может быть прерван, а межкадровая пауза может достигать значения, равного времени переключения на резерв. «Момент запуска» процессора 1890 ВМ6Я определяется фактом первого увеличения счетчика интегрированного кода годности «sVM6LIVEINC» на «1». «Момент запуска» процессора 13 1890 ВМ7Я определяется фактом первого увеличения счетчика интегрированного кода годности «sVM7LIVEINC» на «1».

Пакет телеметрических данных кодируется двумя сигналами «TLD» (данные) и «TLC» (частота) 101 (третья группа выходов системы). Частота выдачи сигнала «TLC» и, соответственно, длительность пакета во времени зависят от значения сигнала «TLV» (вторая управляющая группа выходов 45 системного контроллера YYB 26) (при «TLV»=1 это соответствует частоте передачи равной (1,5±0,0225) Мб/с, при «TLV»=0 это соответствует частоте передачи равной (0,5±0,0075) Мб/с). Пакет состоит из 32 разрядов данных и паузы в 3 мкс. Структура пакета с примером передачи данных «8000000016» представлена на фиг.51. Значения сигналов «TLC» и «TLD» в момент паузы и межкадровой паузы равны нулю.

Пакет 1 и пакет 2 идентичны и содержат значение данных «ΒΒΒΒ555516», определяемое как заголовок кадра. Пакет 3 содержит аппаратное состояние, расшифровка которого представлена на фиг.52, 52а и 53.

Пакет 4 содержит номер передаваемого кадра. При включении ВСХР начальное значение номера передаваемого кадра станет равным единице, а при переключении резерва - продолжит нумерацию.

Пакет 5 содержит параметры А, В. Значение параметра А соответствует количеству пакетов ТМИ в ОЗУ1 (количество 1024 кодируется кодом «00000000002»). Значение параметра В соответствует количеству пакетов ТМИ в ОЗУ2 (количество 1024 кодируется кодом «00000000002»).

Пакет 6 содержит сигнал «sTIMECNT», пакет 8 - контрольную сумму информации, представленной в пакетах 1 - 7. Расшифровка пакетов 6-8 представлена на фиг.54.

Примечание - Алгоритм расчета контрольной суммы пакетов 1-7 представлен на фиг.55.

Разряд 31 пакета 3 обозначает режим работы программной части ВСХР: штатный (значение «1») или технологический (значение «0»). По умолчанию ВСХР включается в технологическом режиме.

Разряд 30 пакета 3 обозначает открытие доступа к ресурсам MRAM 28 и телеметрии со стороны процессоров 1,13 1890 ВМ6Я и 1890 ВМ7Я. Если значение равно «1», то доступ открыт, если «0» - то закрыт. Формирование разряда происходит на основе правильного изменения кодов годности обоих процессоров 1,13. После первого правильного изменения кодов годности доступ к ресурсам MRAM 28 и телеметрии открывается не позднее чем через 20 мкс.

Разряды 29 и 28 пакета 3 обозначают статус переключения. При первом включении ВМ с момента последнего выключения ВСХР р. 29 и 28 принимают значение «3». В случае переключения с одной ВМ на другую данные p изменят свое значение, которое скажет о причине переключения: «0» - переключение по команде из магистрали М2 53, «1» - переключение в случае неисправности ВМ, «2» - переключение в случае срабатывания датчика ПФ.

Разряд 26 пакета 3 обозначает режим технологического управления мультиплексорами. В данном режиме происходит перехват управления стойкой памятью MRAM 28 магистралью М2 53. Значение «1» означает, что данный режим включен, «0» - что выключен. Включение и выключение режима происходит путем записи «1» и «0» соответственно в сигнал «sMBMKO» в соответствии с фиг.45. Режим может быть включен только в технологическом режиме системы и используется только при работе со стойкой памятью MRAM 28 через магистраль М2 53.

Разряд 25 пакета 3 обозначает режим записи. При значении сигнала «sMBMKO» «0» данный режим указывает на осуществление записи данных в стойкую память MRAM 28 процессорами 1,13 1890 ВМ6Я и 1890 ВМ7Я. Разряды (24:22), (11:14) пакета 3 обозначает признак переключения и описан ниже.

Осуществить прием ТМИ от системного контроллера УУВ 26.

Если ВСХР функционирует штатно по записанной в нее программе с учетом работы алгоритмов работы процессоров 1,13 с интегрированным кодом годности PCI 67, то пакет 3 будет содержать двоичный код x1ab_c0xx_xx00_1000_0xxx_x11x_xxx0_xxxx, где x - произвольные данные, ab - соответствуют р. 29 и 28 соответственно и не должны быть равны коду «012».

Расшифровка сигнала «sSWITCHINF» (информация о причинах переключения, р. 29, 28 пакета 3 соответствуют р. 1, 0 сигнала «sSWITCHINF» соответственно, р. 24-22 пакета 3 - р. 4-2, р. 14-11 пакета 3 - р. 8-5) представлена на фиг.56.

Разряд 21 пакета 3 обозначает режим подачи сигнала сброса на процессоры 1,13 1890 ВМ6Я и 1890 ВМ7Я. Значение «1» означает, что сигнал сброса подан, «0» - снят.Включение и выключение режима происходит путем записи «1» и «0» соответственно в сигнал «sMKOVM67RST» в соответствии с фиг.45. Режим может быть включен только в технологическом режиме ВСХР и использоваться для перезапуска процессора без операции выключение-включение ВСХР.

Разряд 19 пакета 3 обозначает признак годности аппаратуры горячей ВМ и вычисляется на основе сигнала, выдаваемого из YYB в ВМ и ретранслируемого обратно в YYB. Если пришедший обратно в YYB сигнал достоверный, то аппаратура горячей ВМ считается годной. Значение «1» означает, что аппаратура горячей ВМ годна, «0» - негодна. В случае негодности аппаратуры горячей ВМ YYB инициирует переключение резерва.

Разряд 16 пакета 3 возникает в случае неисправности блока PLL1 YYB 152. Если входная частота на блок соответствует 12 МГц с коэффициентом заполнения (50±5) %, то внутренний сигнал негодности входной частоты в неактивном уровне, а значение р. 16 равно «0». Если же входная частота не соответствует указанным требованиям, то сигнал негодности входной частоты переходит в активный уровень, а значение р. 16 равно «1». р. 16 является признаком возникновения неисправности и не отражает текущее состояние. Используется для регистрации возникновения сбоя.

Разряд 15 пакета 3 возникает в случае неисправности блока PLL2 YYB 153. Если входная частота на блок соответствует заданной с коэффициентом заполнения (50±5) %, то внутренний сигнал негодности входной частоты в неактивном уровне, а значение р. 15 равно «0». Если же входная частота не соответствует указанным требованиям, то сигнал негодности входной частоты переходит в активный уровень, а значение р. 15 равно «1». р. 15 является признаком возникновения неисправности и не отражает текущее состояние. Используется для регистрации возникновения сбоя.

Разряд 10 пакета 3 обозначает годность процессора 1 1890 ВМ6Я. Значение «1» означает, что процессор штатно изменяет счетчик годности, «0» - что процессор некорректно работает.