Область изобретения

Настоящее изобретение относится к компьютерным системам, в частности к механизмам обработки прерываний в компьютерных системах, которые поддерживают одновременное выполнение множества потоков.

Предшествующий уровень техники

Современные высокопроизводительные процессоры разрабатываются так, чтобы исполнять множество команд за каждый временной такт. Для этого они обычно включают в себя обширные ресурсы исполнения, чтобы облегчать параллельную обработку команд. Эффективное использование этих ресурсов может быть ограничено доступностью команд, которые могут выполняться параллельно. Доступность команд для параллельного исполнения называется параллелизмом на уровне команд (ПУК) (ILP). Зависимости команд ограничивают доступный ПУК в едином потоке исполнения. Если одновременно может обрабатываться только один поток исполнения, производительность команд заметно ухудшается.

Один подход к увеличению производительности команд заключается в разработке процессоров таким образом, чтобы они были способны исполнять команды одновременно из двух или более потоков команд. Поскольку команды из различных потоков независимы, одновременно исполнение двух или более потоков команд увеличивает производительность команд.

Множество конструкций реализовано так, чтобы поддерживать одновременное выполнение множества потоков в одной совокупности процессоров. Например, процессоры со множеством ядер включают в себя множество ядер исполнения в единой процессорной микросхеме. Каждое ядро исполнения может быть назначено отличному от других потоку команд, хотя различные ресурсы могут использоваться совместно, чтобы сократить мертвую (неиспользуемую) площадь или чтобы обеспечить некоторую связь между исполняемыми потоками. Множество процессорных микросхем также могут объединяться в модуль из множества микросхем, который обеспечивает единый интерфейс для остальной системы.

Многопоточные процессоры включают в себя ресурсы для управления исполнением множества потоков команд в едином ядре исполнения. Блоки управления потоками обеспечивают хранение данных состояния для множества потоков прямо на микросхеме и обновление данных, когда команды из различных потоков обрабатываются совместно используемым ядром.

Многопоточный процессор крупномодульной структуры в один момент времени исполняет команды только из одного потока, но хранение данных состояния для множества потоков на микросхеме уменьшает количество служебных данных (накладных расходов), связанных с выполнением команд переключения между различными потоками (контекстные переключатели). Переключение потоков может запускаться, когда исполняемый в текущий момент поток наталкивается на событие с высокой задержкой (множество потоков, переключаемых по событию, МПППС, SOEMT).

Многопоточный процессор мелкомодульной структуры позволяет одновременно исполнять команды из разных потоков. Например, команды могут исходить из многих потоков в каждый период тактирования, либо команды могут исходить от различных потоков в разные периоды тактирования. В обоих случаях команды от множества потоков могут обрабатываться «на лету» внутри ядра исполнения в одно и то же время.

В общем случае, как многопоточные процессоры, так и процессоры со множеством ядер позволяют более чем одному контексту потока быть активным в процессоре в одно и то же время. Для процессоров со множеством ядер некоторые или все из ядер могут быть многопоточными. Здесь контекст относится к регистрам, которые хранят архитектурное состояние потока для конкретной архитектуры процессора, и могут включать в себя регистры общего назначения, управляющие регистры и регистры приложений. Преимущества в производительности этих и других процессоров, поддерживающих многопоточные контексты ("процессоры со множеством контекстов") зависят, в частности, от способности этих процессоров действовать как множество эквивалентных логических процессоров. Эта эквивалентность заметно облегчает поиск баланса рабочих нагрузок среди логических процессоров и упрощает операционной системе управление потоками. Цель, в действительности, заключается в том, чтобы заставить процессор со множеством контекстов действовать как симметричная многопроцессорная система (СМС).

Для увеличения симметрии среди множества потоков некоторые ресурсы для каждого логического процессора дублируются в процессоре со множеством контекстов. Например, блок прерываний обычно связан с каждый логическим процессором, чтобы обеспечить интерфейс между логическим процессором и ресурсами уровня системы или совместно используемыми ресурсами процессора со множеством контекстов. Блок прерываний определяет, должно ли прерывание обрабатываться, и перемещает указатель на код подпрограммы обработки прерываний, если прерывание принимается.

Один недостаток обеспечения блока прерываний для каждого логического процессора заключается в том, что прерывания, в особенности связанные с ресурсами, которые совместно используются логическими процессорами, зачастую видны всем логическим процессорам. Например, процессор со множеством контекстов может обеспечить единственный вывод прерываний, чтобы поддержать совместимость на уровне сборки с однопоточными конструкциями. Прерывания, подаваемые на этот вывод, видны блокам прерывания всех логических процессоров. Такое прерывание может вызвать поломка вентилятора системы. Из-за их эквивалентности каждый блок прерываний регистрирует прерывание, а связанный с ним логический процессор исполняет подпрограмму обработки прерываний. Прерывания, выработанные совместно используемыми ресурсами на микросхеме или принятые по системным шинам или выделенным шинам прерываний, могут быть видны и обрабатываться аналогичным образом. Во многих случаях прерывание может обрабатываться одним из логических процессоров, но симметричная конфигурация логических процессоров заставляет каждый из них исполнять код прерывания.

Настоящее изобретение направлено на решение этих и других проблем, связанных с обработкой прерываний в процессорах, поддерживающих одновременное исполнение множества потоков.

Краткое описание чертежей

Настоящее изобретение может быть понято со ссылками на сопровождающие чертежи, на которых одинаковые элементы обозначены одинаковыми позициями. Эти чертежи предназначены проиллюстрировать избранные варианты выполнения настоящего изобретения, а не ограничить объем изобретения.

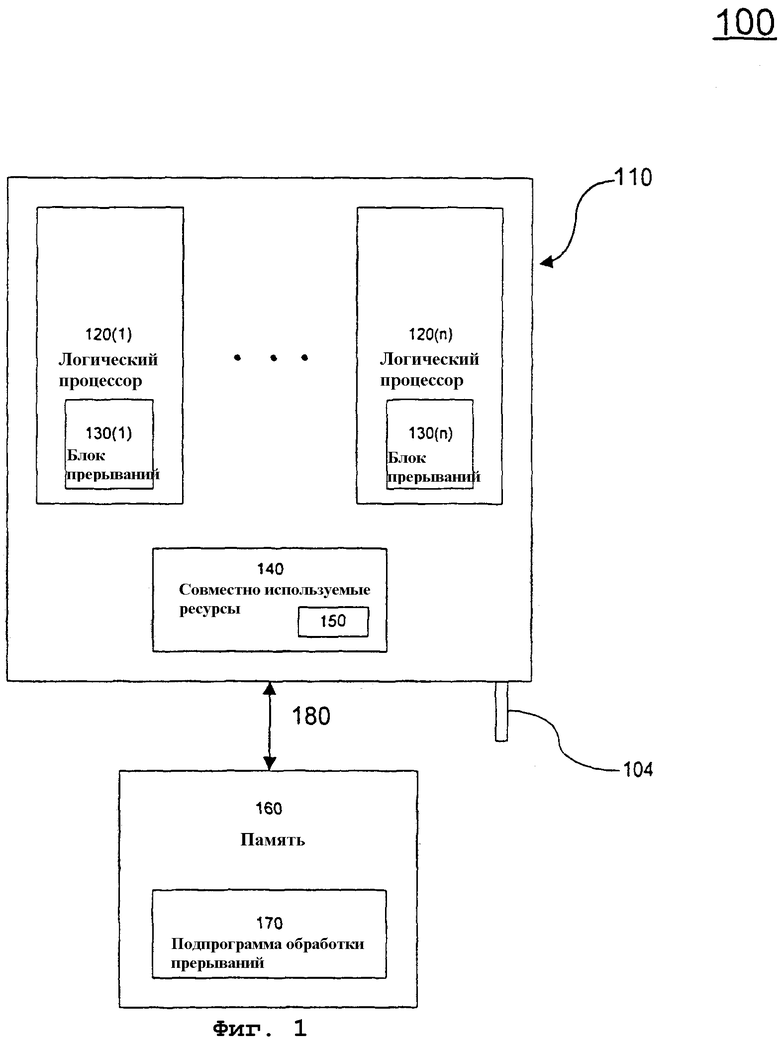

Фиг.1 является блок-схемой компьютерной системы, в которой может быть воплощено настоящее изобретение.

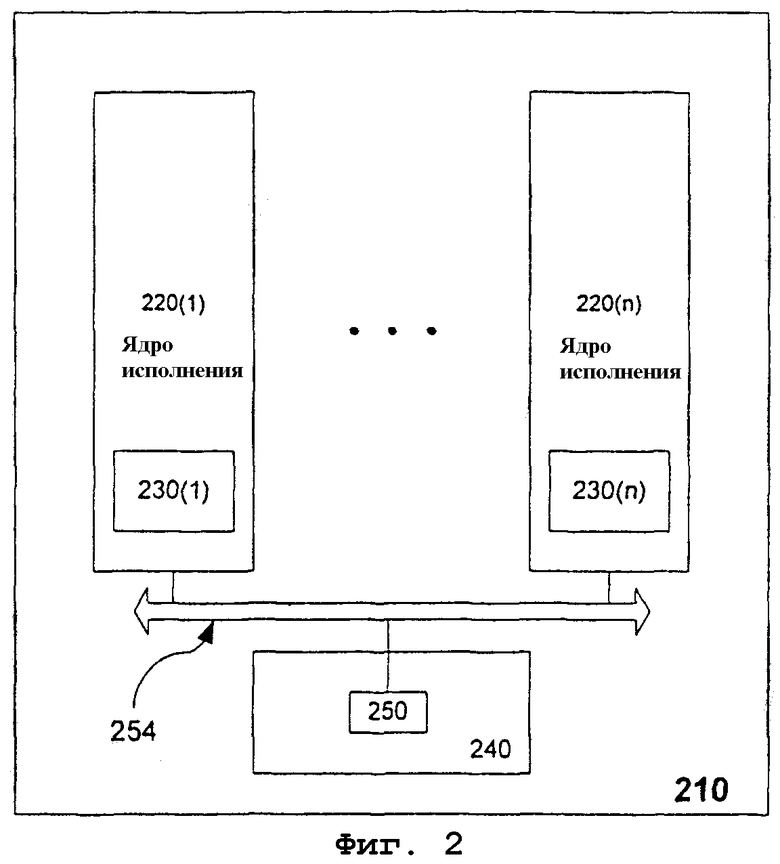

Фиг.2 является блок-схемой процессора со множеством ядер в соответствии с настоящим изобретением.

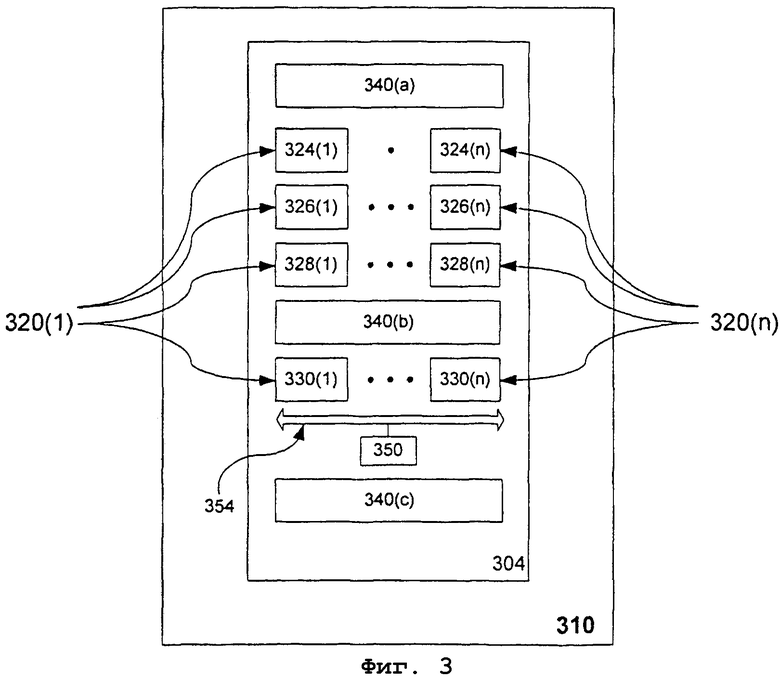

Фиг.3 является блок-схемой многопоточного процессора в соответствии с настоящим изобретением.

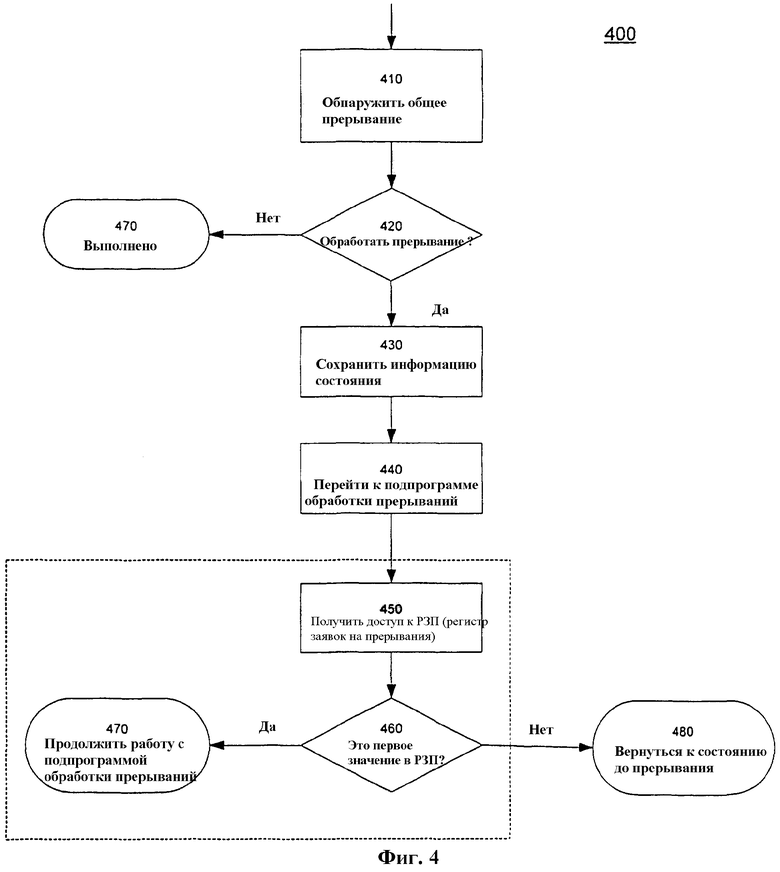

Фиг.4 является блок-схемой алгоритма, представляющей один вариант выполнения способа управления прерываниями в соответствии с настоящим изобретением.

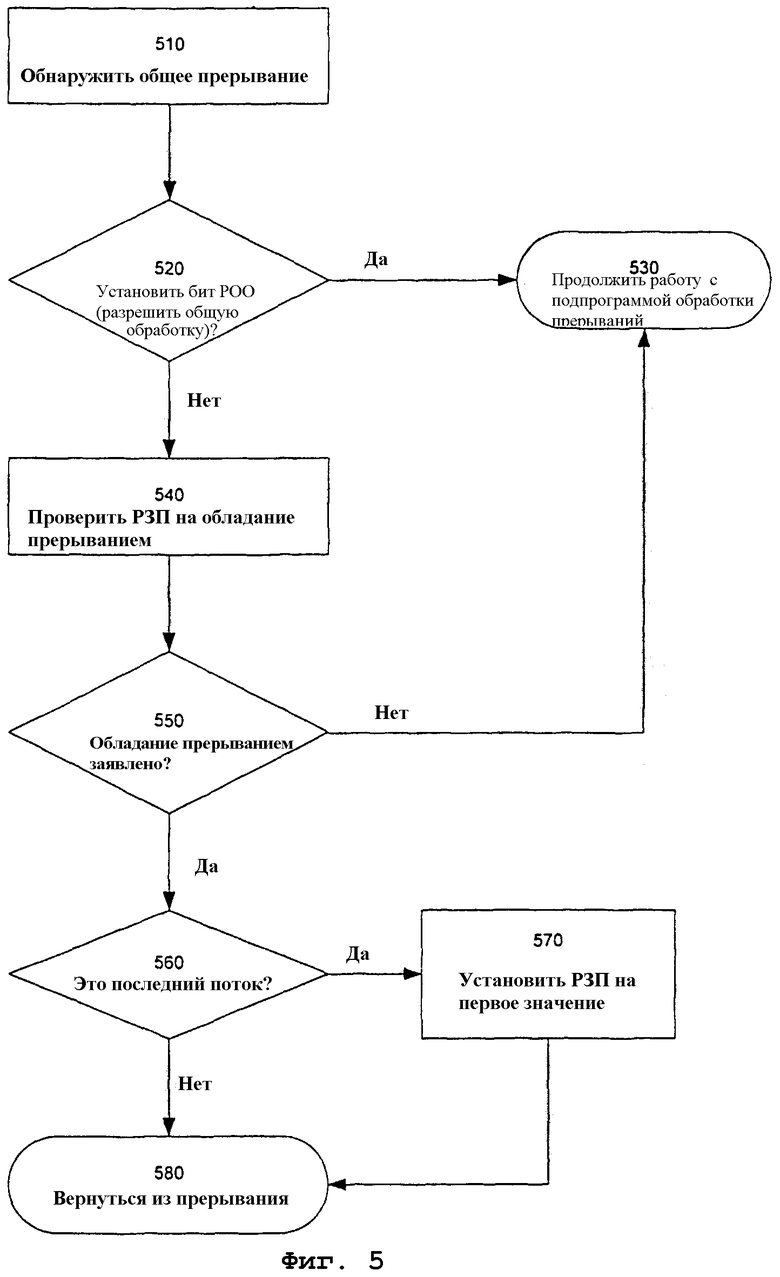

Фиг.5 является блок-схемой алгоритма другого варианта выполнения способа обработки прерываний в соответствии с настоящим изобретением.

Подробное описание изобретения

Нижеследующее описание излагает множество конкретных подробностей, чтобы обеспечить глубокое понимание изобретения. Однако специалисты на основании этого описания поймут, что изобретение может реализовываться на практике без этих конкретных подробностей. Кроме того, чтобы сфокусировать внимание на признаках настоящего изобретения, подробно не описываются различные известные способы, процедуры, компоненты и схемы.

Фиг.1 является блок-схемой одного варианта выполнения компьютерной системы 100, в которой может быть воплощено настоящее изобретение. Компьютерная система 100 включает в себя процессор 110 со множеством контекстов для выполнения команд, хранящихся в памяти 160. Данные и команды передаются между процессором и памятью через канал 180. Канал 180 может включать в себя одну или более шин под управлением набора микросхем или системной логики (не показаны).

Для системы 100 память 160 хранит подпрограмму 170 обработки прерываний, которая исполняется ресурсами на процессоре 110 со множеством контекстов в ответ на прерывание. Память 160 может представлять собой структуры энергозависимой памяти, такой как кэш-память и основная память, а также структуры энергонезависимой памяти, такой как флэш-память, жесткие и гибкие диски и т.п. Для одного варианта выполнения изобретения часть подпрограммы 170 обработки прерываний может быть воплощена в аппаратно-программном обеспечении, тогда как другие части могут храниться в основной памяти.

Логика (логические схемы) процессора 110 со множеством контекстов представлена логическими процессорами 120(1)-120(n) (в общем случае логическим процессором 120), включая связанные с ними блоки 130(1)-130(n) обработки прерываний соответственно (в общем случае блок 130 прерываний) и совместно используемые ресурсы 140. Например, каждый логический процессор 120 может представлять ресурсы, которые назначены конкретному потоку, а совместно используемые ресурсы 140 могут представлять те ресурсы процессора 110, которые доступны потокам на всех логических процессорах 120.

Для описанного выполнения системы 100 совместно используемые ресурсы 140 включают в себя регистр 150 заявок на прерывания (РЗП) (ICR), который доступен для каждого логического процессора 120. Как будет подробно описано ниже, регистр 150 заявок на прерывания обеспечивает механизм, с помощью которого один логический процессор 120 сигнализирует остальным логическим процессорам, что он будет обрабатывать прерывание. Совместно используемые ресурсы 140 могут также включать в себя кэш более высокого уровня или шинные логические схемы, используемые для связи с памятью 160 или периферийными устройствами (не показаны).

Блок 130 обработки прерываний представляет собой функциональный блок, связанный с логическими процессором 120 для обработки прерываний. Некоторые прерывания могут обрабатываться любым из логических процессоров 120. Например, некоторые прерывания, которые возникают в совместно используемых ресурсах 140 на уровне процессора, или прерывания на уровне системы или платформы, которые выработаны ресурсами вне совокупности процессоров, обычно могут обрабатываться любым логическим процессором 120. С ними можно установить связь через внешний вывод 104 на корпусе процессора, через шину или через схему, внутреннюю для процессора 110. В последующем обсуждении такие прерывания называются общими прерываниями, чтобы отличать их от прерываний, которые предназначены для конкретного логического процессора.

Блоки 130(1)-130(n) обработки прерываний регистрируют общие прерывания для логических процессоров 120(1)-120(n) соответственно. Например, каждый блок 130 прерываний определяет приоритет, назначенный прерыванию совместно с любыми условиями маски, чтобы определить, требует ли прерывание немедленной обработки, например, должно ли событие, которое инициировало прерывание, получить приоритет над потоком, исполняемым в настоящее время. Если блок 130 обработки прерываний определяет, что у прерывания имеется приоритет, он предписывает связанному с ним логическому процессору 120 обработать прерывания должной процедурой. Настоящее изобретение обеспечивает механизм, который позволяет одному логическому процессору 120 исполнять полную процедуру обработки прерывания для прерывания, которое зарегистрировано всеми логическими процессорами 120. Это делается без внесения каких-либо асимметрий в логические процессоры 120, то есть произвольным образом назначая прерывания логическим процессорам 120.

Для одного варианта выполнения системы 100 блоки 130(1)-130(n) обработки прерываний регистрируют общее прерывание для логических процессоров 120(1)-120(n). Если у прерывания имеется приоритет, блоки 130(1)-130(n) обработки прерываний передают логическим процессорам 120(1)-120(n) соответственно адрес подпрограммы 170 обработки прерываний. Каждый из логических процессоров 120(1)-120(n) исполняет первый кодовый сегмент подпрограммы 170 обработки прерываний, который направляет его для получения доступа к РЗП 150. Первый из логических процессоров, который успешно получает доступ к РЗП 150, исполняет обработку прерывания, а оставшиеся логические процессоры 120 продолжают выполнение своих потоков.

Для одного варианта выполнения изобретения РЗП 150 инициализируется первым значением, и после общего прерывания устанавливается равным первому значению. Начальный кодовый сегмент подпрограммы 170 обработки прерываний предписывает каждому логическому процессору 120 считывать значения, находящиеся на текущий момент в РЗП 150, и записывать второе значение в РЗП 150. При условии, что второе значение отличается от первого значения, первый логический процессор 120, получивший возможность считывать из РЗП 150, видит первое значение. Все остальные логические процессоры 120 видят второе значение. Логический процессор, который считывает первое значение, продолжает исполнять подпрограмму обработки прерываний. Оставшиеся логические процессоры считывают второе значение, которое сигнализирует им вернуться от прерывания, например продолжить выполнение их прерванных потоков.

Логические процессоры 120 необязательно отвечают на общее прерывание в операции блокировки. Тип исполняемого потока, когда происходит прерывание, его приоритет или даже тип команд, действующих в текущий момент, могут определять то, как быстро логический процессор 120 получает доступ в РЗП 150. В зависимости от варианта выполнения, подпрограмма 170 обработки прерываний может исполняться одновременно только одним процессором, и в этом случае первый логический процессор для выполнения подпрограммы 170 обработки прерываний будет первым, который получит доступ к РЗП 150.

Различные варианты выполнения процессора 110 со множеством контекстов реализуют логические процессоры 120 различными путями. В варианте выполнения со множеством ядер для процессора 110 со множеством контекстов каждый логический процессор 120 соответствует ядру исполнения. Вариант выполнения со множеством ядер для процессора 110 со множеством контекстов описан со ссылками на фиг.2. Для многопоточного варианта выполнения процессора 110 со множеством контекстов каждый логический процессор 120 соответствует ресурсам единственного ядра исполнения, которое назначено конкретному потоку. Многопоточный вариант выполнения процессора 110 со множеством контекстов описан со ссылками на фиг.3. Другие варианты выполнения процессора 110 со множеством контекстов могут включать в себя, например, варианты выполнения со множеством ядер, некоторые из которых или все являются многопоточными. Настоящее изобретение не зависит от конкретного способа, с помощью которого в процессоре реализуются логические процессоры.

Фиг.2 является блок-схемой, представляющей вариант выполнения 210 со множеством ядер процессора 110 со множеством контекстов. Процессор 210 со множеством ядер обеспечивает ядра 220(1)-220(n) исполнения и их соответствующие блоки 230(1)-230(n) обработки прерывания соответственно, чтобы поддерживать одновременное выполнение вплоть до n потоков. Также показаны совместно используемые ресурсы 240, которые включают в себя регистр 250 заявок на прерывания (РЗП). Для описываемого варианта выполнения процессора 210 со множеством ядер ядра 220(1)-220(n) исполнения получают доступ к РЗП 250 через шину 254.

В ответ на общее прерывание каждый блок 230 обработки прерываний определяет, имеется ли у прерывания приоритет, и если имеется, то своему соответствующему ядру 220 исполнения передает адрес подпрограммы обработки прерываний. Под управлением первой части подпрограммы обработки прерываний, ядра 220 исполнения соперничают за доступ к РЗП 250. Первое ядро, получившее доступ к РЗП 250, завершает подпрограмму обработки прерываний. Оставшиеся ядра исполнения продолжают свои прерванные потоки. Для другого варианта выполнения процессора 210 со множеством ядер одно или более ядер 220(1)-220(n) исполнения также могут быть многопоточными, и в этом случае каждый поток каждого ядра пытается первым получить доступ к РЗП 250.

В одном варианте выполнения изобретения первый кодовый сегмент заставляет логический процессор 220 считывать из РЗП 250. Если логический процессор 220 считывает первое значение из РЗП 250, он продолжает исполнять остаток подпрограммы обработки прерываний. Если логический процессор 220 считывает второе значение из РЗП 250, то он может продолжить выполнение команд потока, которые он исполнял до прерывания. Чтобы гарантировать, что только один логический процессор 220 считывает первое значение, начальный кодовый сегмент может использовать неделимую операцию считывания-изменения-записи, такую как операцию "проверить и установить". Например, если первое значение в РЗП 250 равно нулю, подпрограмма 170 обработки прерываний может считать значение из РЗП 250 и сразу записать единицу в РЗП 250. Таким образом, операции считывания-изменения-записи исполняются так, чтобы не оставлять РЗП 250 другому логическому процессору. Для этого варианта выполнения только первый логический процессор, который будет считывать из РЗП 250, считывает нулевое значение. Все остальные логические процессоры будут считывать единицу, записанную в РЗП 250 первым логическим процессором, который получил доступ к РЗП 250.

Вариант осуществления, описанный выше, является примером механизма "гонки за флагом" для определения того, какой логический процессор будет обрабатывать общее прерывание. Флаг, т.е. переменная блокировки или аналогичным образом хранящиеся бит(ы), может содержаться в регистре, к которому может получить доступ каждый логический процессор. Правила считывания/записи, управляющие таким флагом, позволяют каждому логическому процессору, действуя независимо, определять, отвечает он или нет за обработку общего прерывания.

Фиг.3 является блок-схемой, представляющей многопоточный вариант выполнения 310 процессора 110 со множеством контекстов. Многопоточный процессор 310 включает в себя ядро 304 исполнения, которое допускает одновременную обработку команд вплоть до n различных потоков. Ядро 304 исполнения представляет собой конвейер, на котором различные уровни назначены одному из n потоков (блоки 324(1)-324(n), 326(1)-326(n), 328(1)-328(n), 330(1)-330(n)), или совместно используются n потоками (блоки 340(1)-340(n) и РЗП 350). Например, блоки 340(а), 340(b) и 340(с) могут представлять совместно используемый кэш команд, совместно используемый блок переименования регистров и совместно используемый кэш данных. Блоки 324(1)-324(n), блоки 326(1)-326(n), блоки 328(1)-328(n) и блоки 330(1)-330(n) могут представлять части блока выборки, блока декодирования, блока исполнения и блока прерывания соответственно, которые назначены потокам 1-n. Ресурсы, назначенные данному логическому процессору, показаны на одной линии по вертикали только для упрощения фиг.3. В этом нет намерения указать на какое бы то ни было упорядочивание ресурсов, назначенных потоку.

Для описываемого варианта выполнения процессора 310 логический процессор 320(1) представлен назначенными ресурсами 324(1), 326(1), 328(1) и 330(1), а логический процессор 320(n) представлен назначенными ресурсами 324(n), 326(n), 328(n) и 330(n). Это сделано в иллюстративных целях. Другие представления могут включать в себя части совместно используемых ресурсов 340(а)-340(с), используемых в текущий момент соответствующим потоком.

Блоки 330 прерываний, как и другие назначенные ресурсы в процессоре 310, не обязательно должны быть физически отдельными блоками. Например, они могут представлять части единого блока прерываний, который назначен отдельным потокам, исполняемым в процессоре 310. В ответ на общее прерывание блоки 330(1)-330(n) обработки прерываний регистрируют прерывание и определяют, должно ли оно обрабатываться. Если у прерывания имеется приоритет, блоки 330(1)-330(n) обработки прерываний передают логическим процессорам 320(1)-320(n) адрес процедуры обработки прерываний, например подпрограммы 170 обработки прерываний. Каждый логический процессор 320 исполняет первый кодовый сегмент процедуры обработки прерываний, который заставляет его получать доступ к РЗП 350. Первый логический процессор 320, который получает доступ к РЗП 350, исполняет остаток процедуры обработки прерывания. Остальные логические процессоры 320 возвращаются к своим прерванным потокам.

Конфигурации процессора 210 со множеством ядер и многопоточного процессора 310 приведены только в иллюстративных целях. Другие варианты выполнения процессоров со множеством контекстов, пригодных для использования с настоящим изобретением, могут использовать другие конфигурации. Например, потоки многопоточного процессора могут совместно использовать ресурсы препроцессора и ресурсы исполнения и лишь дублировать файлы регистра. Специалисты в разработке процессоров на основании этого описания поймут, что в настоящем изобретении могут использоваться другие конфигурации процессоров со множеством контекстов.

Фиг.4 является блок-схемой алгоритма, представляющего один вариант выполнения способа 400, исполняемого каждым логическим процессором в процессоре со множеством контекстов в ответ на общее прерывание. Общее прерывание обнаруживается на этапе 410, логический процессор на этапе 420 определяет, должно ли это прерывание обрабатываться. Например, блок обработки прерываний логического процессора может проверять приоритет и маскирующие биты, чтобы определить, должно ли обнаруженное прерывание получить преимущество над исполняемым в текущий момент потоком команд. Если прерывание не имеет приоритета, способ 400 завершается на этапе 470. Если у прерывания имеется приоритет, как определено на этапе 420, то на этапе 430 информация об определенном состоянии сохраняется в соответствующей точке исполняемого в текущий момент потока, и логическому процессору на этапе 440 предписывается выполнение процедуры обработки прерываний по указанному адресу. Блок обработки прерываний обычно предоставляет адрес подпрограммы обработки прерываний, если он обнаруживает, что у прерывания имеется приоритет.

Информация о состоянии, сохраненная перед передачей управления в подпрограмму обработки прерываний, обычно является наименьшим количеством информации о состоянии, которое может возвратить логический процессор в прерванный поток команд по завершении подпрограммы обработки прерываний. Это сокращает накладные расходы, связанные с подпрограммой обработки прерываний.

При вхождении в процедуру обработки прерываний логический процессор исполняет первый кодовый сегмент, который предписывает ему на этапе 450 получить доступ к регистру заявок на прерывания (РЗП), на этапе 460 сравнивать значение, хранящееся с РЗП, с первым значением. Если считанное значение равно первому значению, логический процессор в операции 470 продолжает исполнять процедуру обработки прерываний. Если хранящееся значение не равно первому значению, то на этапе 480 логический процессор возвращается от прерывания.

Чтобы гарантировать, что только один процессор получает доступ к РЗП в любое время, варианты выполнения настоящего изобретения могут защищать РЗП или кодовый сегмент, используемый для доступа к РЗП. В первом случае подпрограмма обработки прерываний может использовать неделимую операцию считывания-изменения-записи, чтобы модифицировать РЗП. Для этого варианта выполнения, если логический процессор считал первое значение из РЗП, то он затем записывает в РЗП второе значение, не прекращая управления над РЗП между операциями считывания и записи. При условии, что РЗП устанавливается равным первому значению между прерываниями, первый логический процессор, который должен считывать из РЗП, будет считывать из РЗП первое значение и заменять его на второе значение. Любой логический процессор, который считывает из РЗП после первого логического процессора в ответ на то же самое прерывание, будет считывать второе значение и возвращаться к своим действиям до прерывания.

Во втором случае доступ к первому кодовому сегменту подпрограммы обработки прерываний стробируется битом критического участка. Первый логический процессор, который достигает первого кодового сегмента, исполняет неделимую операцию считывания-изменения-записи бита критического участка, считывая значение бита и записывая второе значение в бит, не прекращая управления над битом между операциями считывания и записи. Если считанное значение показывает, что первый кодовый сегмент разблокирован, логический процессор исполняет код, чтобы считать значение из РЗП. Второе значение, записанное в бит критического участка, гарантирует, что никакой другой логический процессор не может исполнять первый кодовый сегмент в то же самое время. Если считанное значение показывает, что первый кодовый сегмент блокирован, логический процессор может вернуться к потоку, который он исполняет. Поскольку только один логический процессор может одновременно исполнять первый кодовый сегмент, считывание и запись в РЗП не требует неделимой операции. Специалисты на основании этого описания поймут различные другие механизмы, чтобы гарантировать, что только один логический процессор заявил об обладании общим прерыванием.

Когда к флагу (РЗП, переменной блокировки и т.п.) в ответ на общее прерывание обращаются все логические процессоры, флаг должен быть установлен равным первому значению для следующего прерывания. Для одного варианта выполнения изобретения последний логический процессор, считывавший флаг в ответ на общее прерывание, устанавливает этот флаг равным первому значению. Например, может быть задано, что флаг включает в себя бит для каждого логического процессора, поддерживаемого процессором со множеством контекстов. Когда каждый логический процессор получает доступ к флагу, он устанавливает соответствующий бит флага. Последний логический процессор устанавливает соответствующий бит флага, а затем устанавливает все биты флага на первое значение.

Для другого варианта выполнения начальный кодовый сегмент подпрограммы обработки прерываний может командовать логическому процессору прирастить значение счета (например, флаг) и считывать приращенное значение счета. Если приращенное значение счета равно числу логических процессоров, активных в процессоре в текущий момент, логический процессор устанавливает значение счета равным первому значению. Если приращенное значение счета меньше числа логических процессоров, действующих в процессоре в текущий момент, логический процессор возвращается от прерывания.

Эти механизмы установки флага предполагают, что время между общими прерываниями обычно больше, чем время, необходимое всем логическим процессорам для выполнения подпрограммы обработки прерываний (или ее части) и получения доступа к флагу. Специалисты в разработке процессоров на основании этого описания поймут и другие механизмы установки флага, после того как было определено обладание общим прерыванием.

Фиг.5 является блок-схемой алгоритма одного варианта выполнения способа 500 обработки прерываний в соответствии с настоящим изобретением. Способ 500 позволяет активировать или отключать дублирование обработки общих прерываний. Например, может быть необходимо, чтобы все логические процессоры отвечали на общее прерывание, такое как проверка системы или тепловое воздействие. Для этих и других общих прерываний, которые требуют отклика всех логических процессоров, дублирование обработки прерываний может быть активировано с помощью ссылки на бит РОО (разрешение общей обработки). Этот бит может быть установлен для выбранных общих прерываний, когда система загружается первый раз, или изменен позже, для настройки конкретного окружения системы.

Способ 500 начинается на этапе 510 в ответ на обнаружение общего прерывания. Логический процессор на этапе 520 проверяет бит, чтобы определить, активировано ли дублирование обработки прерываний. Если оно активировано, логический процессор продолжает на этапе 530 подпрограмму обработки прерываний независимо от того, что делают другие логические процессоры. Если на этапе 520 бит указывает, что дублирование обработки прерываний отключено, то логический процессор на этапе 540 проверяет РЗП, чтобы определить, не заявлено ли уже обладание прерыванием. Если на этапе 550 обладание прерыванием еще не заявлено, то логический процессор продолжает на этапе 530 подпрограмму обработки прерываний. Описанные выше механизмы управления доступом к РЗП применимы и к способу 500. Если на этапе 550 заявлено обладание прерыванием, то логический процессор на этапе 560 определяет, является ли он последним потоком, чтобы ответить на общее прерывание. Если является, логический процессор на этапе 570 устанавливает РЗП равным первому значению и на этапе 580 возвращается из подпрограммы обработки прерываний к продолжению исполнения потока, который он обрабатывал в тот момент, когда появилось прерывание. Если это не последний поток, чтобы отвечать на общее прерывание, то на этапе 580 процессор возвращается из подпрограммы обработки прерываний без установки РЗП. Механизмы способа 400, описанные для определения того, является ли логический процессор последним потоком, чтобы ответить на общее прерывание и соответственно сбросить РЗП (например, флаг), применимы и к способу 500.

Таким образом, раскрыт механизм обработки некоторых прерываний в компьютерных системах, которые включают в себя процессоры со множеством контекстов. Логические процессоры в процессоре со множеством контекстов соперничают за получение доступа к совместно используемому регистру в ответ на общее прерывание. Первый из логических процессоров, который получил доступ к совместно используемому регистру, обрабатывает прерывание.

Остальные логические процессоры обнаруживают, что заявлено обладание прерыванием, и возвращаются из подпрограммы обработки прерываний. Для одного варианта выполнения изобретения подпрограмма обработки прерываний включает в себя первый кодовый сегмент, который исполняется всеми логическими процессорами модуля в ответ на общее прерывание. Совместно используемый регистр инициализируется первым значением, а первый кодовый сегмент предписывает каждому логическому процессору считывать совместно используемый регистр. Первый логический процессор, получивший доступ к совместно используемому регистру, следуя общему прерыванию, считывает первое значение, записывает второе значение и продолжает выполнять подпрограмму обработки прерываний. Остальные логические процессоры считывают второе значение, которое предписывает им покинуть подпрограмму обработки прерываний.

Для другого варианта выполнения изобретения предусмотрен бит включения/выключения, чтобы сигнализировать о том, должны ли общие прерывания обрабатываться избыточно. Если регистр находится в состоянии отключения, обладание прерыванием заявляется первым логическим процессором, получившим доступ к совместно используемому регистру путем выполнения первого сегмента процедуры обработки прерываний. Если бит находится в состоянии включения, то первый кодовый сегмент пропускают, а все логические процессоры исполняют процедуру обработки прерываний до завершения.

Раскрытые варианты выполнения приведены, чтобы проиллюстрировать различные признаки настоящего изобретения. Настоящее изобретение может найти применение в компьютерах и других основанных на процессорах системах, которые используют процессоры со множеством контекстов. Специалисты на основании этого описания поймут варианты и изменения описанных вариантов выполнения, которые тем не менее будут попадать в сущность и объем прилагаемой формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМЫ И СПОСОБЫ ОТСЛЕЖИВАНИЯ ФЛАГА В ОПЕРАЦИЯХ УСТРАНЕНИЯ ПЕРЕМЕЩЕНИЯ | 2014 |

|

RU2628156C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПРИОСТАНОВКИ ИСПОЛНЕНИЯ ПОТОКА ДО МОМЕНТА ОСУЩЕСТВЛЕНИЯ ОПРЕДЕЛЕННОГО ДОСТУПА К ПАМЯТИ | 2002 |

|

RU2308754C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЛОКИРОВКИ СИГНАЛА СИНХРОНИЗАЦИИ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ | 2000 |

|

RU2233470C2 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

| ЭФФЕКТИВНАЯ МАРШРУТИЗАЦИЯ ПРЕРЫВАНИЙ ДЛЯ МНОГОПОТОЧНОГО ПРОЦЕССА | 2015 |

|

RU2678513C2 |

| СИСТЕМА И СПОСОБ ДЛЯ ЗАЩИТЫ ОТ НЕДОВЕРЕННОГО КОДА РЕЖИМА УПРАВЛЕНИЯ С СИСТЕМОЙ С ПОМОЩЬЮ ПЕРЕАДРЕСАЦИИ ПРЕРЫВАНИЯ РЕЖИМА УПРАВЛЕНИЯ СИСТЕМОЙ И СОЗДАНИЯ КОНТЕЙНЕРА ВИРТУАЛЬНОЙ МАШИНЫ | 2003 |

|

RU2313126C2 |

| ВОССТАНОВЛЕНИЕ КОНТЕКСТА ПОТОКА В МНОГОПОТОЧНОЙ КОМПЬЮТЕРНОЙ СИСТЕМЕ | 2015 |

|

RU2670909C9 |

| ДИНАМИЧЕСКОЕ АКТИВИРОВАНИЕ МНОГОПОТОЧНОСТИ | 2015 |

|

RU2662403C2 |

| РАСШИРЕНИЕ И СОКРАЩЕНИЕ АДРЕСА В МНОГОПОТОЧНОЙ КОМПЬЮТЕРНОЙ СИСТЕМЕ | 2015 |

|

RU2661788C2 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПОВЕДЕНИЯ ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ ЯВНОГО ВЫЗОВА ПОДПРОГРАММЫ | 2007 |

|

RU2417407C2 |

Изобретение относится к механизмам обработки прерываний в компьютерных системах. Техническим результатом является повышение производительности системы. Система включает в себя процессор со множеством контекстов для выполнения команд, хранящихся в памяти. В ответ на общее прерывание логические процессоры со множеством контекстов соревнуются за получение доступа к совместно используемому регистру. Первый логический процессор, получивший доступ к совместно используемому регистру, обрабатывает общее прерывание. Оставшиеся логические процессоры возвращаются из прерывания. 4 н. и 18 з.п. ф-лы, 5 ил.

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| US 5396602 A, 07.03.1995 | |||

| US 4992938 A, 12.02.1991. | |||

Авторы

Даты

2006-07-20—Публикация

2002-08-01—Подача