Область техники, к которой относится изобретение

Настоящее раскрытие, в общем, относится к вычислительным системам, и, в частности, относится к улучшению эффективности выполнения операций с манипуляцией данными компьютерными системами.

Уровень техники

Операции манипуляции с данными представляют существенную часть операций, выполняемых процессором. Следовательно, оптимизация их выполнения может улучшать общие рабочие характеристики процессора.

Настоящее раскрытие представлено в качестве примера, а не для ограничения, и его будет легче понять при ссылке на следующее подробное описание изобретения, которое следует рассматривать совместно с чертежами, на которых:

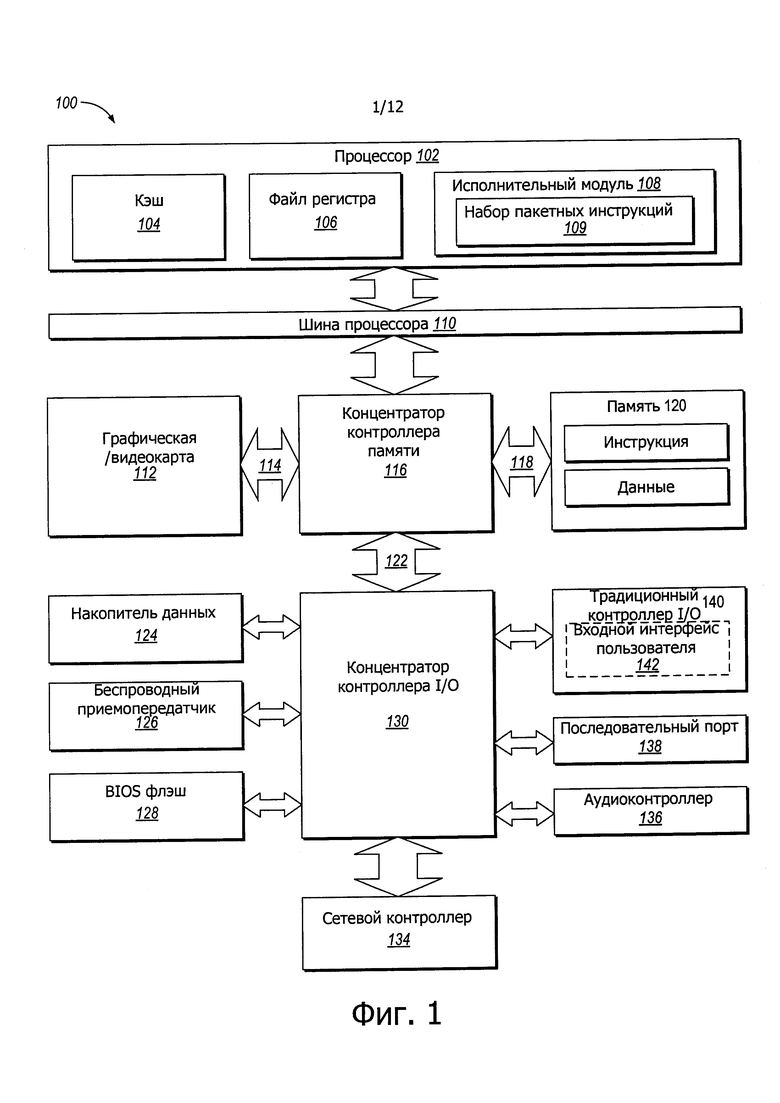

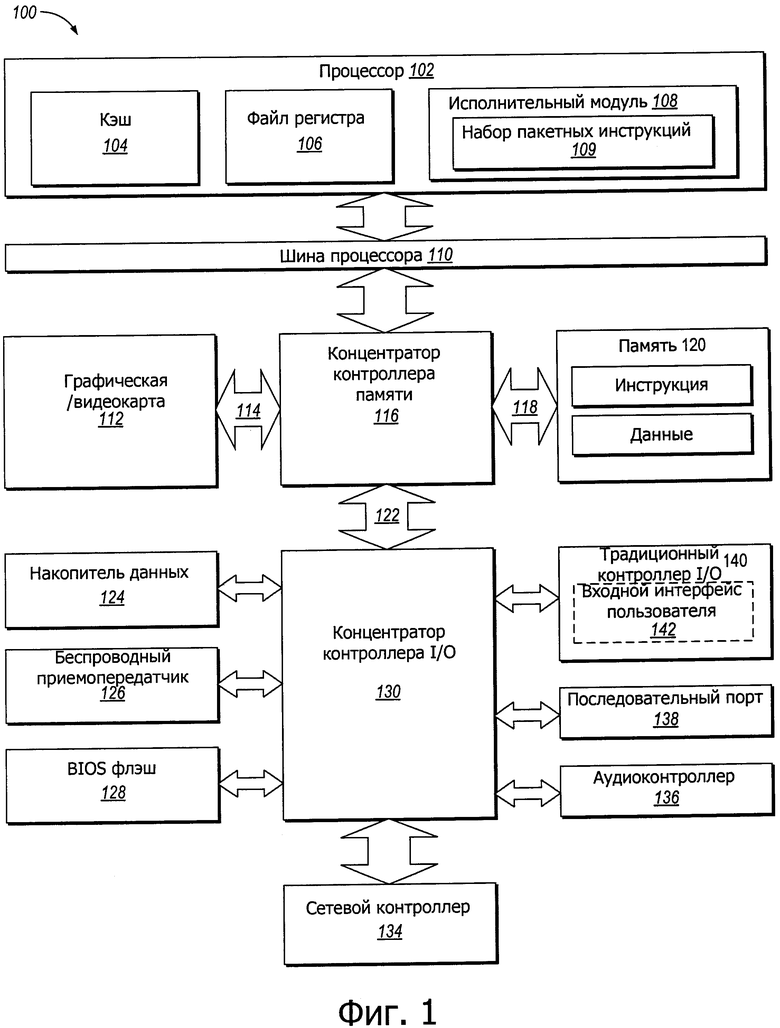

на фиг. 1 представлена схема компонентов высокого уровня примера компьютерной системы в соответствии с одним или более аспектами настоящего раскрытия;

на фиг. 2 представлена блок-схема процессора в соответствии с одним или более аспектами настоящего раскрытия;

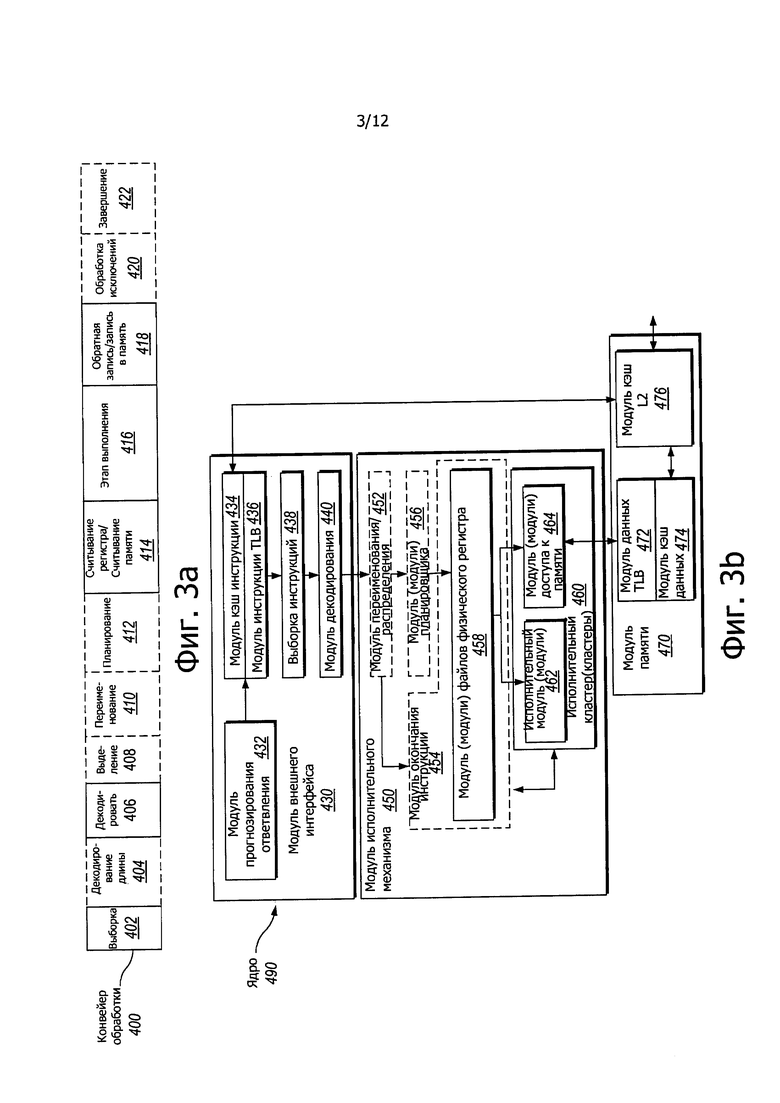

на фиг. 3a-3b схематично иллюстрируются элементы микроархитектуры процессора в соответствии с одним или более аспектами настоящего раскрытия;

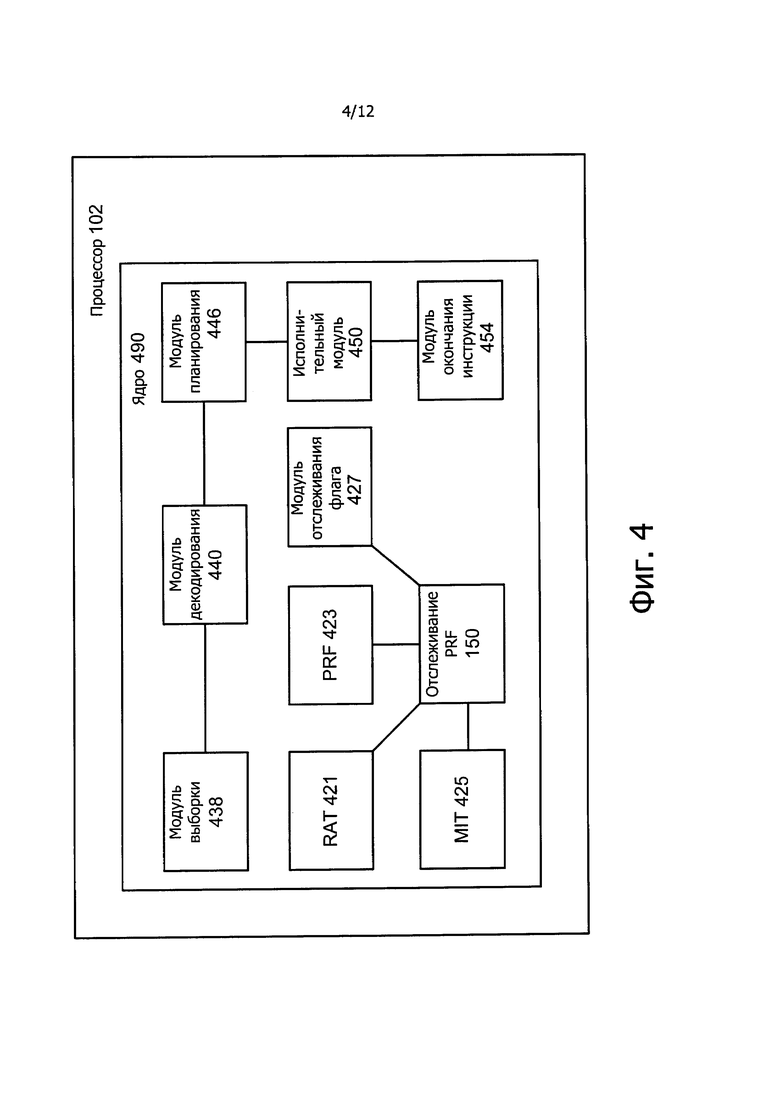

на фиг. 4 схематично иллюстрируются ряд аспектов примерного процессора и других компонентов компьютерной системы 100 по фиг. 1 в соответствии с одним или более аспектами настоящего раскрытия;

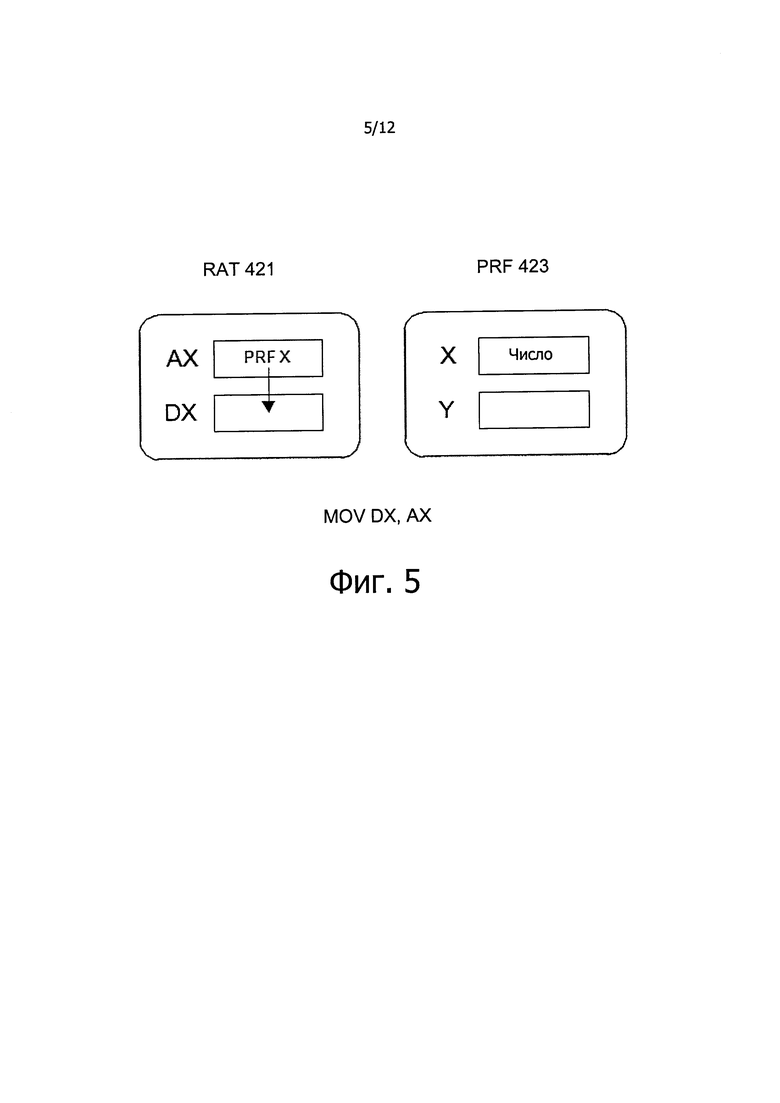

на фиг. 5 схематично иллюстрируется пример выполнения операции перемещения с использованием замещения регистра, в соответствии с одним или более аспектами настоящего раскрытия;

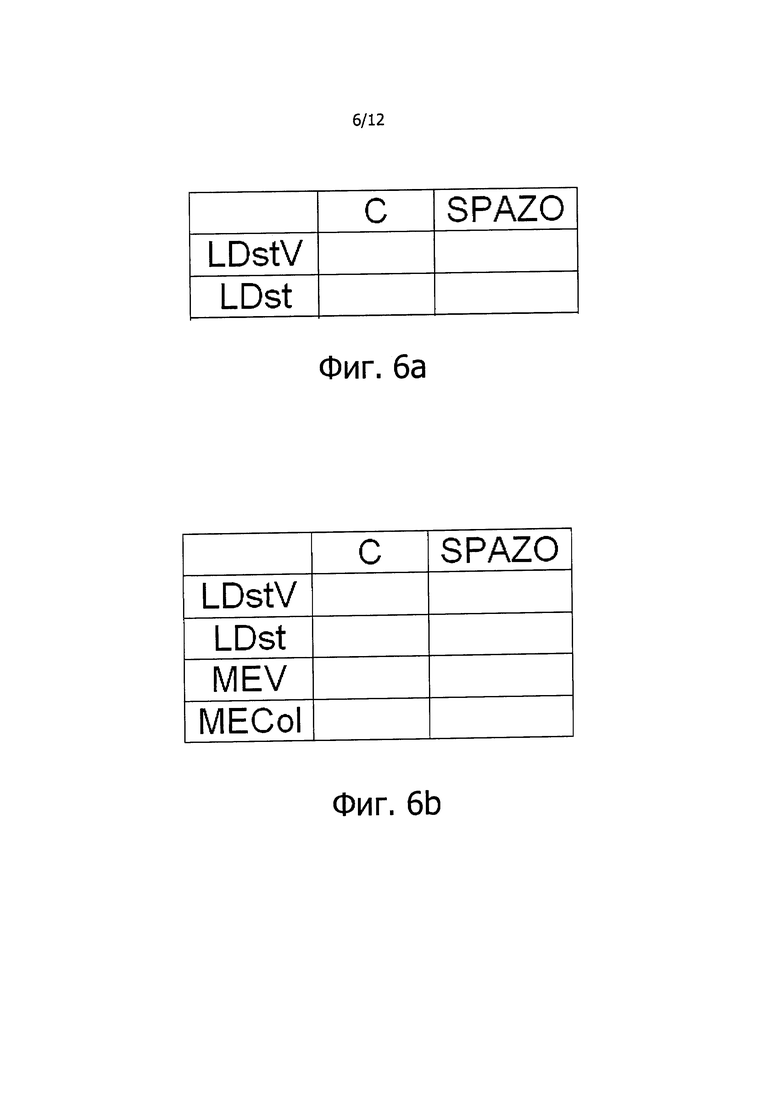

на фиг. 6a-6b схематично иллюстрируются примеры структуры данных модуля отслеживания флага, в соответствии с одним или более аспектами настоящего раскрытия;

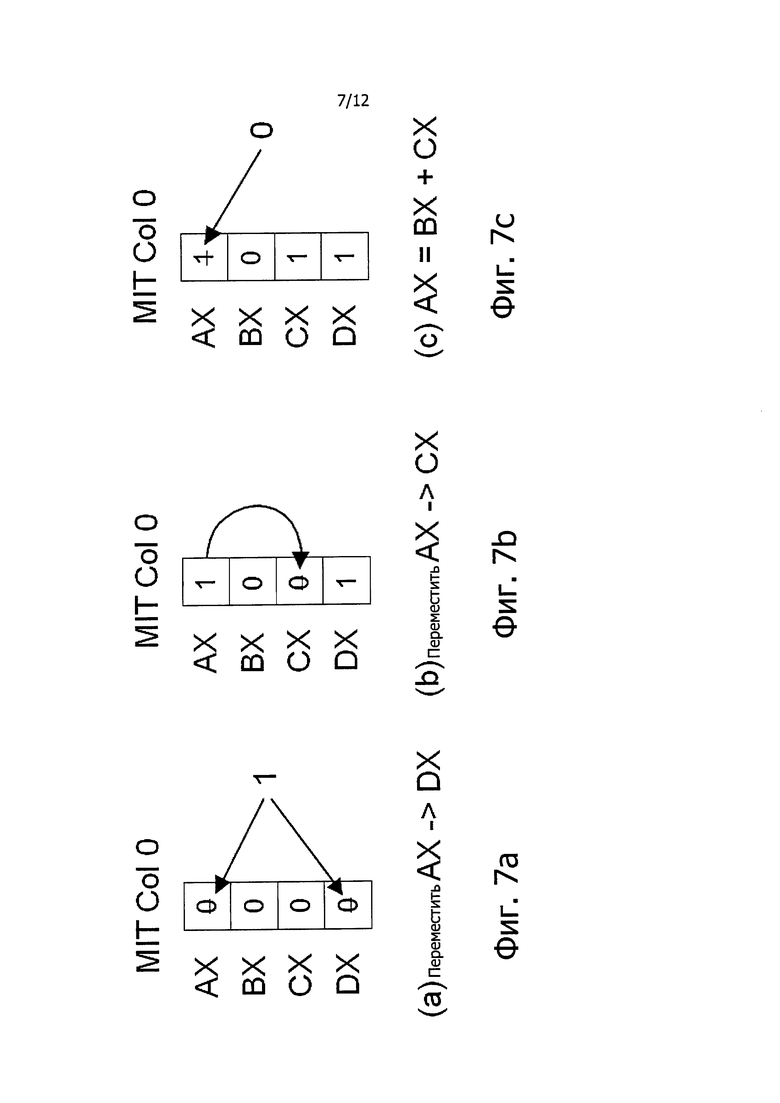

на фиг. 7a-7c схематично иллюстрируются несколько примеров, используя таблицу множественной инстанциации (MIT) для отслеживания входа файла физического регистра (PRF), в соответствии с одним или более аспектами настоящего раскрытия;

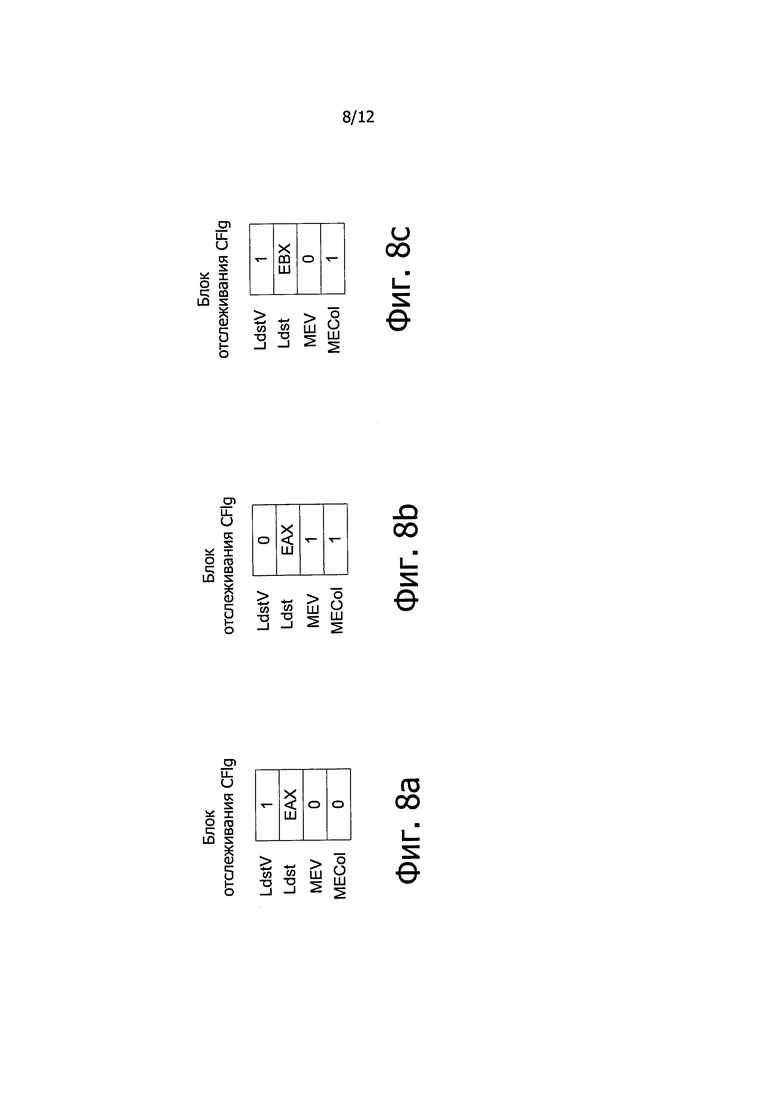

на фиг. 8a-8c схематично иллюстрируется один пример использования структуры данных модуля отслеживания флага для отслеживания входа в MIT, в соответствии с одним или более аспектами настоящего раскрытия;

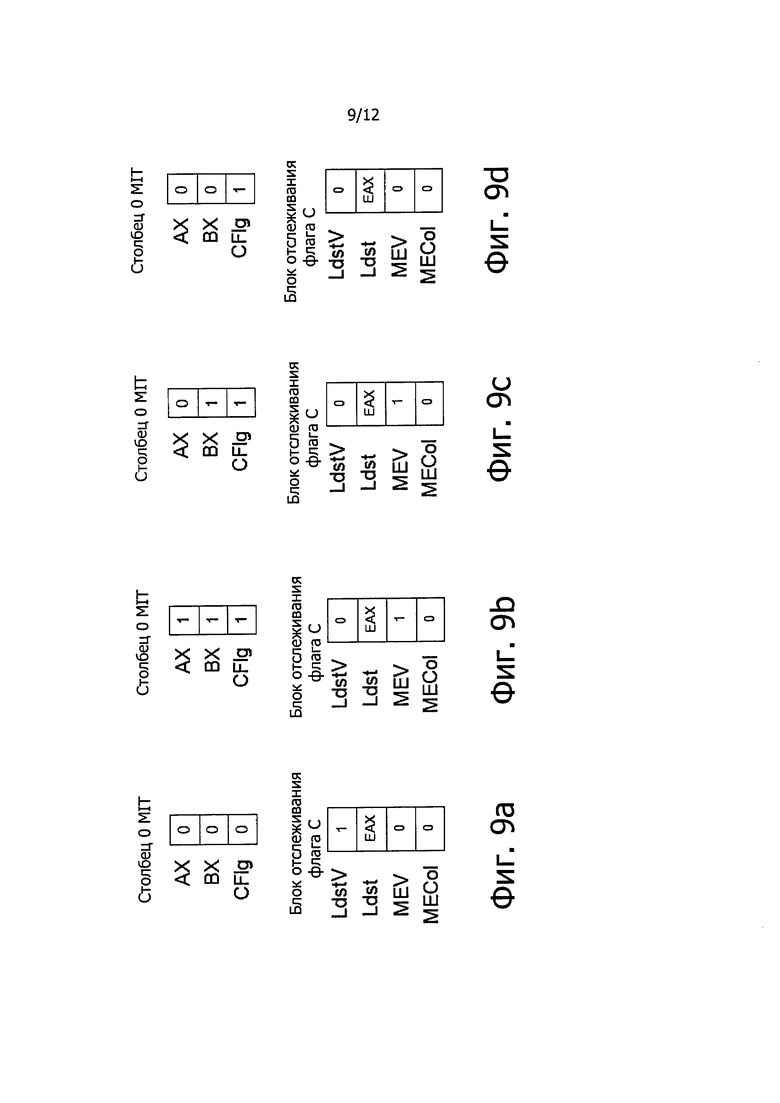

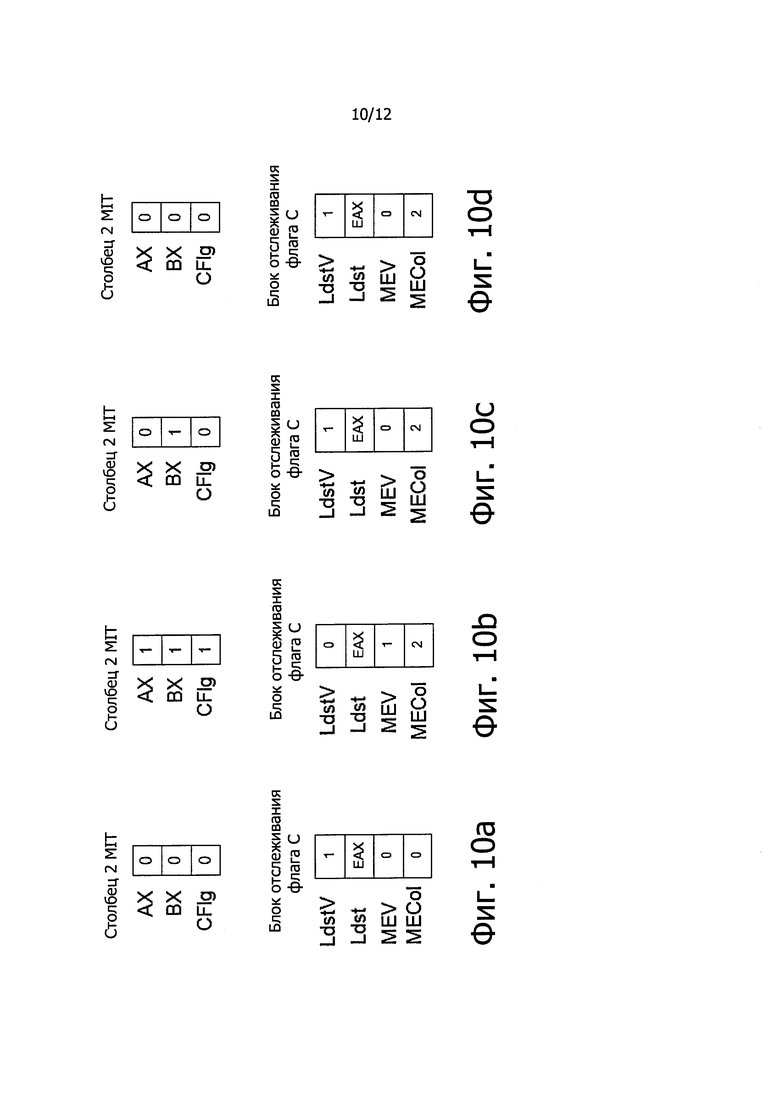

на фиг. 9a-9d и 10a-10d схематично иллюстрируются примеры логики отслеживания флага в операциях устранения перемещения в соответствии с одним или более аспектами настоящего раскрытия;

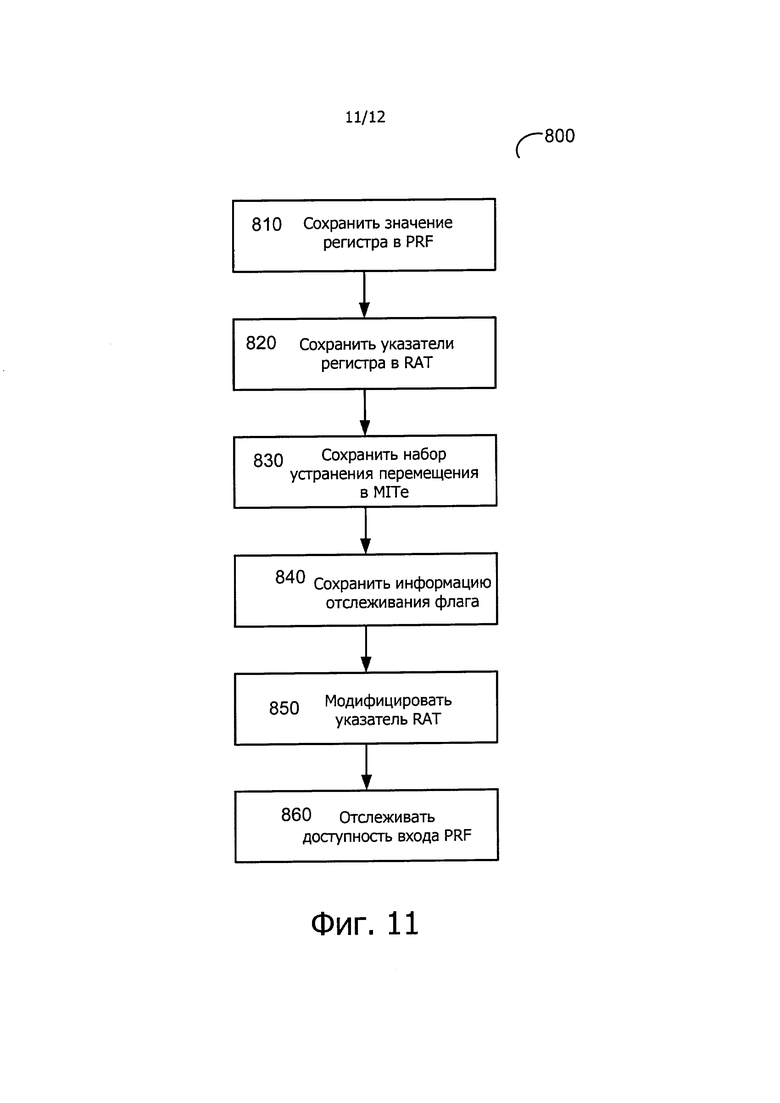

на фиг. 11 представлена блок-схема последовательности операций примерного способа для отслеживания флага в операциях устранения перемещения в соответствии с одним или более аспектами настоящего раскрытия; и

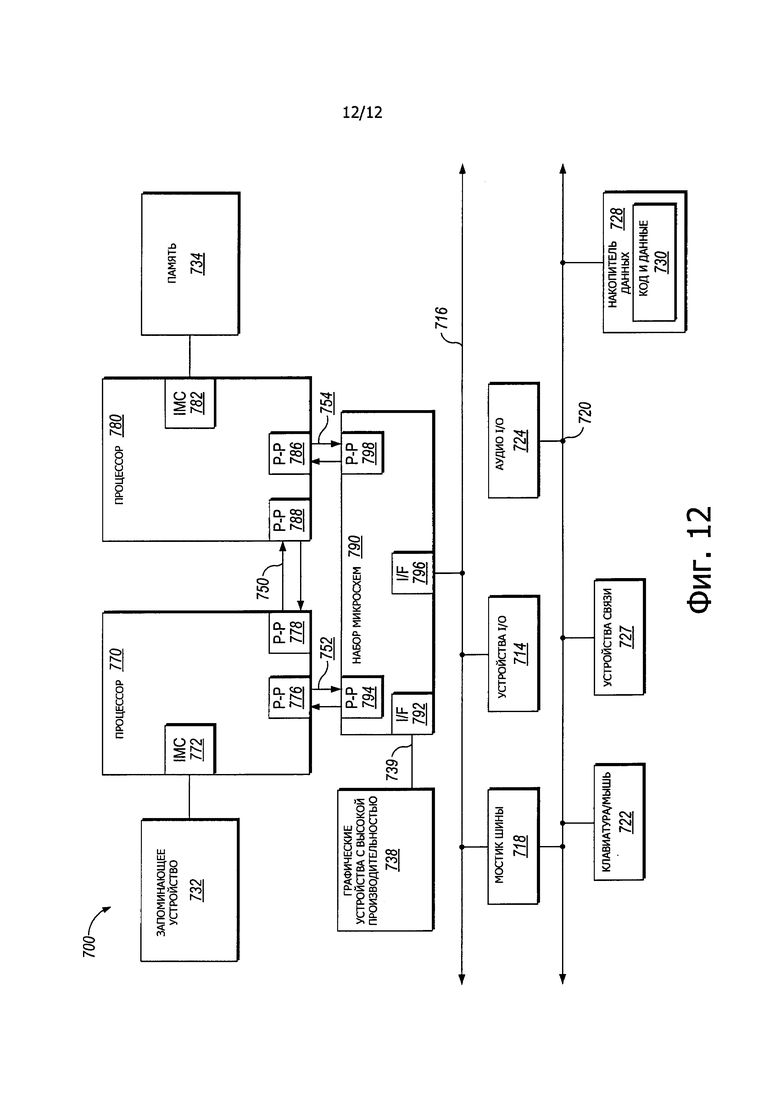

на фиг. 12 представлена блок-схема примерной компьютерной системы в соответствии с одним или более аспектами настоящего раскрытия.

Осуществление изобретения

Здесь описаны компьютерная система и соответствующие технологии для отслеживания флага в операциях манипуляций с данными, включающих в себя устранение перемещения. “Устранение перемещения” здесь должно означать выполнение операции копирования регистра без использования исполнительного модуля, для улучшения эффективности выполнения.

В некоторых вариантах осуществления устранение перемещения может быть воплощено путем замещения регистра: первая структура данных, называемая файлом физического регистра (PRF), может использоваться для сохранения значений физического регистра и вторая структура данных, называемая таблицей замещения регистра (RAT), может использоваться для сохранения указателей, отображающих идентификаторы логического регистра на входы PRF. Замещение регистра позволяет выполнять определенные инструкции путем модификации одного или более указателей в RAT, без передачи этих инструкций в исполнительные модули. Примеры таких инструкций включают в себя инструкции обнуления регистра (такие как, например, XOR, AX, AX) и инструкции копирования регистра (такие как инструкции MOV). Поскольку инструкция копирования регистра не создает новое значение, исходный указатель регистра может быть скопирован в указатель назначения регистра в RAT, таким образом, что для инструкции может не потребоваться использовать исполнительный модуль и другой вход PRF. Эта обработка называется “устранением перемещения”, поскольку инструкция перемещения устраняется из потока, передаваемого в исполнительные модули.

Целочисленная инструкция может модифицировать не только значение места назначения регистра, но также один или более флагов статуса процессора. Для сохранения значения флага каждый вход PRF может включать в себя, вместе с полем для значения регистра данных, одно или более полей для значений флага.

Может потребоваться отслеживание использование входов таблицы PRF физическими регистрами и флагами для определения, когда вход PRF может быть высвобожден для использования новой инструкцией. Ниже здесь описаны системы и способы для эффективного отслеживания флага в операциях устранения перемещения.

Различные аспекты упомянутых выше способов и систем описаны подробно здесь ниже в виде примеров, а не для ограничений.

В следующем описании представлены различные конкретные детали, такие как примеры определенных типов процессоров и конфигураций систем, конкретные структуры аппаратных средств, конкретные детали архитектуры и микро-архитектуры, конкретные конфигурации регистра, конкретные типы инструкций, конкретные компоненты системы, конкретные измерения/высоты, конкретные каскады процессорного конвейера и операции, и т.д., для обеспечения полного понимания настоящего изобретения. Однако, для специалиста в данной области техники будет понятно, что эти конкретные детали не обязательно должны использоваться для выполнения на практике настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретная и альтернативная архитектура процессора, конкретные логические схемы/коды для описанных алгоритмов, конкретный код встроенного программного обеспечения, конкретная операция взаимного соединения, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные варианты воплощения компилятора, конкретное выражение алгоритмов в коде, конкретная технологии/логика отключения питания и выполнения логических операций, и другие конкретные детали операций компьютерной системы не были подробно описаны для исключения ненужного усложнения настоящего изобретения.

Хотя следующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы для других типов интегральных микросхем и логических устройств. Аналогичные технологии и описания вариантов осуществления настоящего изобретения могут применяться для других типов схем или полупроводниковых устройств, работа которых может быть улучшена в результате более высокой пропускной способности конвейера и улучшенных рабочих характеристик. Описания вариантов осуществления настоящего изобретения применимы для любого процессора или устройства, в которых выполняются манипуляции с данными. Однако настоящее изобретение не ограничено процессорами или устройствами, которые выполняют операции с данными длиной 512 битов, 256 битов, 128 битов, 64 бита, 32 бита или 16 битов, и могут быть применено в любом процессоре и устройстве, в котором выполняется манипуляция или администрирование данными. Кроме того, в следующем описании представлены примеры, и на приложенных чертежах показаны различные примеры с целью иллюстрации. Однако эти примеры не следует рассматривать в ограничительном смысле, поскольку они просто предназначены для предоставления примеров вариантов осуществления настоящего изобретения, а не для предоставления исчерпывающего списка всех возможных выполнений вариантов осуществления настоящего изобретения.

Хотя в представленных ниже примерах описана обработка и распределение инструкций в контексте исполнительных модулей и логических схем, в другие варианты осуществления настоящего изобретения могут быть выполнены с использованием данных или инструкций, сохраненных на считываемом устройством вещественном носителе информации, которые при их выполнении устройством обеспечивают выполнение устройством функций, соответствующих, по меньшей мере, одному варианту осуществления изобретения. В одном варианте осуществления функции, ассоциированные с вариантами осуществления настоящего изобретения, воплощены в виде используемых устройством инструкций. Инструкции могут использоваться для обеспечения выполнения процессором общего назначения или специального назначения, который запрограммирован такими инструкциями, этапов настоящего изобретения. Варианты осуществления настоящего изобретения могут быть предусмотрены, как компьютерный программный продукт или программное обеспечение, которое может включать в себя считываемый устройством или считываемый компьютером носитель информации, на котором содержатся инструкции, которые могут использоваться для программирования компьютера (или других электронных устройств), для выполнения одной или более операций, в соответствии с вариантами осуществления настоящего изобретения. В качестве альтернативы, операции вариантов осуществления настоящего изобретения могут быть выполнены конкретными аппаратными компонентами, которые содержат логическую схему с фиксированной функцией для выполнения операций, или используют любую комбинацию программируемых компьютерных компонентов и аппаратных компонентов с фиксированной функцией.

Инструкции, используемые для программирования логики для выполнения вариантов осуществления изобретения могут быть сохранены в запоминающем устройстве, в системе, такой как DRAM, кэш, памяти типа флэш или в другом накопителе. Кроме того, инструкции могут быть распределены через сеть или используя другой считываемый компьютером носитель информации. Таким образом, считываемый устройством носитель информации может включать в себя любой механизм для сохранения или передачи информации в форме, считываемой устройством (например, компьютером), но не ограничен гибкими дисками, оптическими дисками, компакт-диском, постоянным запоминающим устройством (CD-ROM), и магнитооптическими дисками, постоянным запоминающим устройством (ROM), оперативным запоминающим устройством (RAM), стираемым программируемым постоянным запоминающим устройством (EPROM), электрически стираемым программируемым постоянным запоминающим устройством (EEPROM), магнитными или оптическими картами, памятью флэш или вещественным, считываемым устройством накопителем, используемым при передаче информации через Интернет, используя электрические, оптические, акустические или другие формы распространяемых сигналов (например, несущие волны, инфракрасные сигналы, цифровые сигналы и т.д.). В соответствии с этим, считываемый компьютером носитель информации включает в себя любой тип вещественного считываемого устройством носителя информации, пригодного для сохранения или передачи электронных инструкций или информации в форме, считываемой устройством (например, компьютером).

“Процессор” здесь относится к устройству, выполненному с возможностью выполнения инструкций, кодирования арифметических, логических операций или операций I/O. В одном иллюстративном примере процессор может следовать архитектурной модели фон Неймана и может включать в себя арифметический-логический модуль (ALU), модуль управления и множество регистров. В дополнительном аспекте процессор может включать в себя одно или более ядер процессора и, следовательно, может представлять собой одноядерный процессор, который обычно выполнен с возможностью обработки одного конвейера инструкций, или многоядерный процессор, который может одновременно обрабатывать множество конвейеров инструкций. В другом аспекте процессор может быть воплощен, как одиночная интегральная схема, две или более интегральных схемы, или может представлять собой компонент многокристального модуля (например, в котором отдельные кристаллы микропроцессора включены в один пакет интегральной схемы и, следовательно, совместно используют одно гнездо).

На фиг. 1 представлена схема компонента высокого уровня одного примера компьютерной системы в соответствии с одним или более аспектами настоящего раскрытия. Компьютерная система 100 может включать в себя процессор 102, в котором используются исполнительные модули, включающие в себя логику для выполнения алгоритмов для обработки данных в соответствии с вариантом осуществления, описанным здесь. Система 100 может быть представлена процессорными системами на основе микропроцессоров PENTIUM™, PENTIUM 4™, Xeon™, Itanium, XScale™ и/или StrongARM™, представляемых компанией Intel Corporation Санта-Клара, Калифорния, хотя другие системы (включая в себя PC, имеющие другие микропроцессоры, инженерные рабочие станции, телевизионные приставки и т.п.) также могут использоваться. В одном варианте осуществления, примерная система 100 выполняет версию операционной системы WINDOWS™, поставляемую компанией Microsoft Corporation Редмонд, Вашингтон, хотя также могут использоваться другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические интерфейсы пользователя.

Таким образом, варианты осуществления настоящего изобретения не ограничены какой-либо конкретной комбинацией аппаратных схем и программного обеспечения.

Варианты осуществления не ограничены компьютерными системами. Альтернативные варианты осуществления настоящего изобретения могут использоваться в других устройствах, таких как переносные устройства и встраиваемые приложения. Некоторые примеры переносных устройств включают в себя сотовые телефоны, устройства протокола Интернет, цифровые камеры, карманные персональные компьютеры (PDA) и портативные ПК. Встраиваемые приложения могут включать в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на кристалле, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любую другую систему, которая может выполнять одну или более инструкций в соответствии с, по меньшей мере, одним вариантом осуществления.

В этом представленном варианте осуществления процессор 102 включает в себя один или более исполнительных модулей 108 для воплощения алгоритма, который предназначен для выполнения, по меньшей мере, одной инструкции. Один вариант осуществления может быть описан в контексте настольного компьютера или серверной системы с одним процессором, но альтернативные варианты осуществления могут быть включены в многопроцессорную систему. Система 100 представляет собой пример архитектуры системы “концентратора”. Компьютерная система 100 включает в себя процессор 102 для обработки сигналов данных. Процессор 102, в качестве одного иллюстративного примера, включает в себя микропроцессор компьютера со сложным набором команд (CISC), микропроцессор архитектуры с сокращенным набором команд (RISC), микропроцессор со словом инструкции очень большой длины (VLIW), процессор, воплощающий комбинацию набора инструкций, или любое другое устройство процессора, такое как, например, цифровой сигнальный процессор. Процессор 102 соединен с шиной 110 процессора, по которой передают сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 (например, графический ускоритель 112, концентратор 116 контроллера памяти, память 120, концентратор 124 контроллера I/O, приемопередатчик 126 беспроводной передачи данных, флэш-BIOS 128, сетевой контроллер 134, аудиоконтроллер 136, последовательный порт 138 расширения, I/O контроллер 140 и т.д.) выполняют свои обычные функции, которые хорошо известны специалисту в данной области техники.

В одном варианте осуществления процессор 102 включает в себя внутренний кэш 104 уровня 1 (L1). В зависимости от архитектуры процессор 102 может иметь один внутренний кэш или множество уровней внутреннего кэш. Другие варианты осуществления включают в себя комбинацию, как внутреннего, так и внешнего кэш, в зависимости от конкретного воплощения и потребностей. Файл 106 регистра предназначен для сохранения различных типов данных в различных регистрах, включая в себя регистры для целых чисел, регистры для чисел с плавающей точкой, векторные регистры, сгруппированные регистры, теневые регистры, регистры контрольных точек, регистры статуса и регистр указателя инструкций.

Исполнительный модуль 108, включающий в себя логику для выполнения операций с целыми числами и с плавающей точкой, также находится в процессоре 102. Процессор 102, в одном варианте осуществления, включает в себя ROM микрокода (ucode), для сохранения микрокода, который при его исполнении должен выполнять алгоритмы для определенных макроинструкций или обрабатывать сложные сценарии. Здесь микрокод потенциально может быть обновлен для обработки логических ошибок/исправлений для процессора 102. В одном варианте осуществления исполнительный модуль 108 включает в себя логику для обработки пакетного набора 109 инструкций. Благодаря включению пакетного набора 109 инструкций в набор инструкций процессора 102 общего назначения, вместе с соответствующей схемой для выполнения этих инструкций, операции, используемые множеством мультимедийных приложений, могут быть выполнены, используя пакетные данные в процессоре 102 общего назначения. Таким образом, множество мультимедийных приложений ускоряются и выполняются более эффективно, используя полную ширину шины данных процессора для выполнения операций с пакетными данными. Это потенциально устраняет необходимость передачи меньших модулей данных через шину данных процессора для выполнения одной или более операций по одному элементу данных одновременно.

Альтернативные варианты осуществления исполнительного модуля 108 также могут использоваться в микроконтроллерах, встроенных процессорах, графических устройствах, DSP и в других типах логических схем. Система 100 включает в себя запоминающее устройство 120. Запоминающее устройство 120 включает в себя динамическое оперативное запоминающее устройство (DRAM), статическое оперативное запоминающее устройство (SRAM), устройство памяти флэш или другое запоминающее устройство. Запоминающее устройство 120 содержит инструкции и/или данные, представленные сигналами данных, которые должны быть выполнены процессором 102.

Системная логическая микросхема 116 соединена с шиной 110 процессора и запоминающим устройством 120. Системная логическая микросхема 116 в представленном варианте осуществления представляет собой концентратор контроллера памяти (МСН). Процессор 102 может связываться с МСН 116 через шину 110 процессора. МСН 116 обеспечивает канал 118 передачи памяти большой ширины для запоминающего устройства 120, для сохранения инструкций и данных и для сохранения графических команд, данных и текстур. МСН 116 предназначен для направления сигналов данных между процессором 102, запоминающим устройством 120 и другими компонентами в системе 100 и для соединения через мостики сигналов данных между шиной ПО процессора, запоминающим устройством 120 и системным I/O 122. В некоторых вариантах осуществления системная логическая микросхема 116 может обеспечивать графический порт для соединения с графическим контроллером 112. МСН 116 соединен с запоминающим устройством 120 через интерфейс 118 памяти. Графическая карта 112 соединена с МСН 116 через взаимное соединение 114 ускоренного графического порта (AGP).

В системе 100 используется собственная шина 122 интерфейса концентратора для соединения МСН 116 с концентратором контроллера I/O (ICH) 130. ICH 130 обеспечивает непосредственное соединение с некоторыми устройствами I/O через локальную шину I/O. Локальная шина I/O представляет собой высокоскоростную шину I/O для соединения периферийных устройств с запоминающим устройством 120, набором микросхем и процессором 102. Некоторые примеры представляют собой аудиоконтроллер, концентратор (флэш-BIOS) 128 встроенного программного обеспечения, беспроводный приемопередатчик 126, накопитель 124 данных, контроллер унаследованного I/O, содержащий интерфейсы для ввода данных пользователем и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB), и сетевой контроллер 134. Устройство 124 сохранения данных может содержать привод жесткого диска, привод гибкого диска, устройство CD-ROM, устройство памяти флэш или другое устройство хранения большой емкости.

В другом варианте осуществления системы инструкция в соответствии с одним вариантом осуществления может использоваться с системой на микросхеме. В одном варианте осуществления система на микросхеме содержит процессор и запоминающее устройство. Запоминающее устройство для одной такой системы представляет собой запоминающее устройство флэш. Запоминающее устройство флэш может быть размещено на том же кристалле, что и процессор и другие компоненты системы. Кроме того, другие логические блоки, такие как контроллер памяти или графический контроллер, также могут быть размещены в системе на кристалле.

На фиг. 2 показана блок-схема микроархитектуры для процессора 200, которая включает в себя логические схемы для выполнения инструкций в соответствии с одним вариантом осуществления настоящего изобретения. В некоторых вариантах осуществления инструкция, в соответствии с одним вариантом осуществления, может быть воплощена для выполнения операций с элементами данных, имеющими размер байт, слово, двойное слово, учетверенное слово и т.д., а также типы данных, такие как целое число с одиночной и двойной точностью, и типы данных с плавающей точкой. В одном варианте осуществления входной интерфейс 201, работающий по порядку, представляет собой часть процессора 200, который производит выборки инструкций для исполнения и подготавливает их для более позднего использования в конвейере процессора. Входной интерфейс 201 может включать в себя несколько модулей. В одном варианте осуществления модуль 226 предварительного отбора инструкций выбирает инструкции из запоминающего устройства и подает их в декодер 228 инструкции, который по очереди декодирует или интерпретирует их. Например, в одном варианте осуществления, декодер декодирует принятую инструкцию в одну или более операций, называемых “микроинструкциями” или “микрооперациями” (также называются uops), которые может выполнять устройство. В других вариантах осуществления декодер анализирует инструкцию, разбирая ее на коды операций и соответствующие данные, и поля управления, которые используются микроархитектурой для выполнения операций в соответствии с одним вариантом осуществления. В одном варианте осуществления кэш 230 трассы принимает декодированные микрооперации и собирает их в упорядоченную последовательность программ или трассы в очереди 234 микроопераций для выполнения. Когда кэш 230 трассы сталкивается со сложной инструкцией, ROM 232 микрокода предоставляет микрооперации, необходимые для выполнения операции.

Некоторые инструкции преобразуют в одиночные микрооперации, в то время как для других требуется несколько микроопераций для завершения всей операции. В одном варианте осуществления, если более чем четыре микрооперации необходимы для выполнения инструкции, декодер 228 обращается к ROM 232 микрокода для выполнения инструкции. В одном варианте осуществления инструкция может быть декодирована в малое количество микроопераций для обработки в декодере 228 инструкции. В другом варианте осуществления инструкция может быть сохранена в ROM 232 микрокода, в случае, когда множество микроопераций требуется для выполнения операции. Кэш 230 трассы обращается к программируемому логическому массиву (PLA) точки входа для определения правильного указателя на микроинструкции, для считывания последовательности микрокода, для выполнения одной или более инструкций в соответствии с одним вариантом осуществления из ROM 232 микрокода. После окончания ROM 232 микрокода упорядочивания микроопераций для инструкции, внешний интерфейс 201 устройства возобновляет выборку микрооперации из кэш 230 трассы.

Исполнительный механизм 203, работающий не по порядку, используется там, где инструкции подготавливают для выполнения. Исполнительная логическая схема, работающая не по порядку, имеет множество буферов для сглаживания и изменения порядка потока инструкций для оптимизации рабочих характеристик по мере того, как они поступают в конвейер, и планируется их выполнение. Логика распределения выделяет машинные буферы и ресурсы для каждой микрооперации, для которой требуется выполнение. Логика замещения регистра отображает логические регистры на входы в файле регистра. Распределитель также выделяет вход для каждой uop в одной из двух очередей uop, одной или более операций с памятью и одной или более операций, не связанных с памятью, перед планировщиками инструкции: планировщик памяти, быстрый планировщик 202, планировщик 204 медленной/общей обработки с плавающей точкой, и простой планировщик 206 с плавающей точкой. Планировщики 202, 204, 206 uop определяют, когда uop готовы для выполнения, на основе готовности зависящих от них источников операнда входного регистра и доступности ресурсов выполнения, которые требуются для завершения операции uop. Быстрый планировщик 202 в одном варианте осуществления может планировать в каждой половине основного цикла тактовой частоты, в то время как другие планировщики могут планировать один раз за основной цикл тактовой частоты процессора. Планировщики определяют порты отправки для выполнения запланированных uop.

Файлы 208, 210 физического регистра находятся между планировщиками 202, 204, 206 и исполнительными модулями 212, 214, 216, 218, 220, 222, 224 в исполнительном блоке 211. Существует отдельный файл 208, 210 регистра для операций с целыми числами и с плавающей точкой, соответственно. Каждый файл 208, 210 регистра в одном варианте осуществления также включает в себя обходную сеть, которая позволяет обойти или перенаправлять только что законченные результаты, которые еще не были записаны в файл регистра в новые зависимые uop. Файл 208 регистра для целых чисел и файл 210 регистра для чисел с плавающей точкой также выполнены с возможностью передавать данные друг другу. В одном варианте осуществления файл 208 регистра для целых чисел разделен на два отдельных файла регистра, один файл регистра для 32 битов данных младшего порядка и второй файл регистра для 32 битов данных старшего порядка. Файл 210 регистра для чисел с плавающей точкой в одном варианте осуществления имеет входы шириной 128 битов, поскольку инструкции с плавающей точкой обычно имеют операнды шириной от 64 до 128 битов.

Исполнительный блок 211 содержит исполнительные модули 212, 214, 216, 218, 220, 222, 224, где фактически исполняются инструкции. Данный раздел включает в себя файлы 208, 210 регистра, которые содержат значения операнда, представляющие собой данные целых чисел и чисел с плавающей точкой, для исполнения которых требуются микроинструкции. Процессор 200 в одном варианте осуществления состоит из множества исполнительных модулей: модуля 212 генерирования адресов (AGU), AGU 214, быстрого ALU 216, быстрого ALU 218, медленного ALU 220, ALU 222 с плавающей точкой, модуля 224 перемещения с плавающей точкой. В одном варианте осуществления исполнительные блоки 222, 224 с плавающей точкой исполняют операции с плавающей точкой, MMX, SIMD и SSE, или другие операции. ALU 222 с плавающей точкой в одном варианте осуществления включают в себя делитель с плавающей точкой 64 бита на 64 бита для исполнения деления, операции квадратного корня или остальных микроопераций. В вариантах осуществления настоящего изобретения инструкции, в которых используется значение с плавающей точкой, могут обрабатываться с использованием аппаратных средств с плавающей точкой. В одном варианте осуществления операции ALU передают в высокоскоростные исполнительные модули 216, 218 ALU. Быстрые ALU 216, 218, в одном варианте осуществления, позволяют выполнять быстрые операции с эффективной задержкой половина цикла тактовой частоты. В одном варианте осуществления наиболее сложные операции с целым числом передают в медленный ALU 220, поскольку медленный ALU 220 включает в себя исполнительные аппаратные средства для целых чисел, для операций с длинным типом задержки, таких как операции умножения, сдвига, логики флага и ответвления. Операции загрузки/сохранения в запоминающем устройстве выполняются AGU 212, 214. В одном варианте осуществления ALU 216, 218, 220 с целыми числами описаны в контексте выполнения операций с целыми числами для операндов данных размером 64 бита. В альтернативных вариантах осуществления ALU 216, 218, 220 могут быть воплощены для поддержки данных с разных количеством битов, включающих в себя 16, 32, 128, 256 и т.д. Аналогично, модули 222, 224 для работы с плавающей точкой могут быть воплощены для поддержки определенного диапазона операндов, имеющих биты разной ширины. В одном варианте осуществления модули 222, 224 для работы с плавающей точкой могут работать для операндов пакетных данных шириной 128 битов совместно с SIMD и мультимедийными инструкциями.

В одном варианте осуществления планировщики 202, 204, 206 uops отправляют зависимые операции перед окончанием выполнения порождающей нагрузки. Поскольку uop теоретически планируются и исполняются в процессоре 200, процессор 200 также включает в себя логическую схему для обработки потерь в памяти. Если происходят потери загрузки данных в кэш данных, в конвейере в это время должны выполняться зависимые операции, которые оставили в планировщике временно неправильные данные. Механизм повторного воспроизведения отслеживает и повторно исполняет инструкции, которые используют неправильные данные. Зависимые операции должны быть повторно выполнены, и при этом может быть разрешено завершение независимых операций. Планировщики и механизм повторного воспроизведения в одном варианте осуществления процессора также разработаны для захвата последовательности инструкций для операций сравнения текстовой строки.

Термин “регистры” может относиться к местам сохранения в процессоре, которые используются, как часть инструкций, для идентификации операндов. Другими словами, регистры могут представлять собой регистры, которые используются снаружи процессора (с перспективы программиста). Однако регистры в варианте осуществления не должны быть ограничены по значению определенным типом цепи. Вместо этого регистры, в соответствии с вариантом осуществления, могут сохранять и предоставлять данные и выполнять функции, описанные здесь. Регистры, описанные здесь, могут быть воплощены с использованием схемы в процессоре, используя любое количество разных технологий, таких как выделенные физические регистры, динамически выделенные физические регистры, используя замещение регистра, комбинации выделенных и динамически распределенных физических регистров и т.д. В одном варианте осуществления регистры для целых чисел содержат тридцатидвухбитные данные целых чисел. Файл регистра в одном варианте осуществления также содержат восемь мультимедийных регистров SIMD для пакетных данных. Для представленного ниже описания, под регистрами понимают регистры для данных, разработанных для содержания пакетных данных, такие как регистры ММХ шириной 64 бита (также называются регистрами “mm” в некоторых случаях) в микропроцессорах, в которых используются технологии ММХ™ компании Intel Corporation Санта-Клара, Калифорния. Эти регистры ММХ, доступные, как в форме целых чисел, так и числе с плавающей точкой, могут работать с элементами пакетных данных, которые сопровождают инструкции SIMD и SSE. Аналогично, регистры ХММ шириной 128 битов, относящиеся к SSE2, SSE3, SSE4 или к дальнейшей технологии (в общем, называются “SSEx”), также могут использоваться для содержания таких операндов для пакетных данных. В одном варианте осуществления, при сохранении пакетных данных и целых чисел, регистрам не требуется различать между двумя типами данных. В одном варианте осуществления целые числа и числа с плавающей точкой содержатся либо в одном файле регистра или в разных файлах регистра. Кроме того, в одном варианте осуществления, данные с плавающей точкой и целочисленные данные могут быть сохранены в разных регистрах или в одних и тех же регистрах.

На фиг. 3a-3b схематично представлены элементы микроархитектуры процессора, в соответствии с одним или более аспектами настоящего раскрытия. На фиг. 3a, конвейер 400 процессора включает в себя этап 402 выборки, этап 404 декодирования длины, этап 406 декодирования, этап 408 выделения, этап 410 переименования, этап 412 планирования (также известный как этап отправки или выпуска), этап 414 считывания регистра/считывания памяти, исполнительный этап 416, этап 418 обратной записи/записи в память, этап 422 обработки исключения, и этап 424 завершения.

На фиг. 3b стрелками обозначена связь между двумя или более модулями, и направление стрелки обозначает направление потока данных между этими модулями. На фиг. 3b показано ядро 490 процессора, включающее в себя модуль 430 внешнего интерфейса, соединенный с модулем 450 исполнительного механизма, и оба из которых соединены с модулем 470 памяти.

Ядро 490 может представлять собой ядро архитектуры процессора с сокращенным набором команд (RISC), или ядро процессора со сложным набором команд, ядро архитектуры процессора со сложным набором команд (CISC), ядро со словом инструкции очень большой длины (VLIW) или ядро гибридного или альтернативного типа. В качестве еще одного, другого варианта выбора, ядро 490 может представлять собой ядро специального назначения, такое как, например, сетевое ядро или ядро передачи данных, механизм сжатия, графическое ядро и т.п.

Модуль 430 внешнего интерфейса включает в себя модуль 432 прогнозирования ответвления, соединенный с модулем 434 кэш-инструкции, который соединен с буфером 436 хранения трансляции инструкции (TLB), который соединен с модулем 438 выбора инструкции, который соединен с модулем 440 декодирования. Модуль декодирования или декодер может декодировать инструкции, и генерировать, как выход, одну или более микроопераций, точек входа микрокода, микроинструкций, других инструкций или других сигналов управления, которые декодируют, или которые по-другому отражают, или которые выводят из оригинальных инструкций. Декодер может быть воплощен, используя всевозможные механизмы. Примеры соответствующих механизмов включают в себя, но не ограничены этим, справочные таблицы, воплощения аппаратных средств, программируемые логические массивы (PLA), постоянные запоминающие устройства (ROM) для микрокода и т.д. Модуль 434 кэш-инструкции дополнительно соединен с модулем 476 кэш уровня 2 (L2) в модуле 470 памяти. Модуль 440 декодирования соединен с модулем 452 изменения наименования/распределителя в модуле 450 исполнительного механизма.

Модуль 450 исполнительного механизма включает в себя модуль 452 изменения наименования/распределителя, соединенный с модулем 454 окончания инструкции и набором из одного или более модуля (модулей) 456 планировщика. Модуль (модули) 456 планировщика представляет любое количество разных планировщиков, включая в себя станции резервирования, центральное окно инструкции и т.д. Модуль (модули) 456 планировщика соединен с модулем (модулями) 458 файла (файлов) физического регистра.

Каждый из модулей 458 файла (файлов) физического регистра представляет собой один или более файлов физического регистра, разные файлы из которых содержат один или более разных типов данных, таких как скалярное целое число, скалярное число с плавающей точкой, пакетное целое число, пакетное число с плавающей точкой, векторное целое число, векторное число с плавающей точкой и т.д., статус (например, указатель инструкций, который представляет собой адрес следующей инструкции, предназначенный для исполнения), и т.д. Модуль (модули) 458 файла (файлов) физического регистра перекрывается модулем 454 окончания инструкции для иллюстрации различных способов, в которых может быть воплощено замещение регистра и исполнение не по порядку (например, используя буфер (буферы) изменения порядка и файл (файлы) регистров окончания инструкции, используя будущий файл (файлы), буфер (буферы) истории и файл (файлы) регистра окончания инструкции; используя отображения регистров и объединение регистров; и т.д.). Обычно регистры, составляющие архитектуру, видимы снаружи процессора или из перспективы программиста. Регистры не ограничены каким-либо известным конкретным типом цепи. Всевозможные типы регистров пригодны, если только они выполнены с возможностью сохранения и предоставления данных, как описано здесь. Примеры соответствующих регистров включают в себя, но не ограничены этим, специализированные физические регистры, динамически выделенные физические регистры, использующие замещение регистра, комбинации выделенных и динамически размещенных физических регистров и т.д. Модуль 454 окончания инструкции и модуль (модули) 458 файла (файлов) физического регистра соединены с исполнительным кластером (кластерам) 460. Исполнительный кластер (кластеры) 460 включает в себя набор из одного или более исполнительных модулей 162 и набор из одного или более исполнительных модулей 464 доступа к памяти. Исполнительные модули 462 могут выполнять различные операции (например, сдвига, суммирования, вычитания, умножения) и для различных типов данных (например, скалярных с плавающей точкой, пакетных целых чисел, пакетных чисел с плавающей точкой, векторных целых чисел, векторных чисел с плавающей точкой). В то время как некоторые варианты осуществления могут включать в себя множество исполнительных модулей, выделенных для конкретных функций или наборов функций, другие варианты осуществления могут включать в себя один исполнительный модуль или множество исполнительных модулей, все из которых выполняют все функции. Модуль (модули) 456 планировщика, модуль (модули) 458 файла (файлов) физических регистров и исполнительный кластер (кластеры) 460 показаны, как, возможно, присутствующие во множественном числе, поскольку некоторые варианты осуществления формируют отдельные конвейеры для определенных типов данных/операций (например, для скалярного числа с плавающей точкой/пакетного целого числа/пакетного числа с плавающей точкой/векторного целого числа/конвейер для векторного числа с плавающей точкой и/или конвейер для доступа к памяти, каждый из которых имеет свой собственный модуль планировщика, модуль файла (файлов) физического регистра и/или исполнительный кластер (и, в случае отдельного конвейера для доступа к памяти, воплощены некоторые варианты осуществления, в которых исполнительный кластер такого конвейера имеет модуль (модули) 464 доступа к памяти). Следует также понимать, что в случае, когда используются отдельные конвейеры, один или более из этих конвейеров может быть предназначен для выпуска/исполнения не по порядку и другие для работы по порядку.

Набор модулей 464 доступа к памяти соединен с модулем 470 памяти, который включает в себя модуль 472 TLB данных, соединенный с модулем 474 кэш-данных, соединенный с модулем 476 кэш уровня 2 (L2). В одном примерном варианте осуществления модули 464 доступа к памяти могут включать в себя модуль нагрузки, модуль адреса сохранения и модуль данных сохранения, каждый из которых соединен с модулем 472 данных TLB в модуле 470 памяти. Модуль 476 кэш L2 соединен с одним или более другими уровнями кэш и, в конечном итоге, с основным запоминающим устройством.

В качестве примера замещения регистра архитектура ядра выдачи/исполнения не по порядку может воплощать конвейер 400 следующим образом: инструкции выборки 438 выполняют этапы 402 и 404 выборки и декодирования длины; модуль 440 декодирования выполняет этап 406 декодирования; модуль 452 переименования/размещения выполняет этап 408 размещения и этап 410 переименования; модуль (модули) 456 планировщика выполняют этап 412 планирования; модуль (модули) 458 файла (файлов) физического регистра и модуль 470 памяти выполняют этап 414 считывания регистра/считывания памяти; исполнительный кластер 460 выполняет исполнительный этап 416; модуль 470 памяти и модуль (модули) 458 файла (файлов) физического регистра выполняют этап 418 обратной записи/записи в память; различные модули могут быть вовлечены в этап 422 обработки исключений; и модуль 454 окончания инструкции, и модуль (модули) файла (файлов) 458 физического регистра выполняют этап 424 прекращения.

Ядро 490 может поддерживать один или более наборов инструкций (например, набор инструкций x86 (с некоторыми исключениями, которые были добавлены более новыми версиями); набор инструкций MIPS компании MIPS Technologies, Саннивейл, Калифорния; набор инструкций ARM (с дополнительными расширениями, такими как NEON) компании ARM Holdings, Саннивейл, Калифорния).

В некоторых вариантах осуществления ядро может поддерживать многопоточную обработку (исполнение двух или более параллельных наборов операций или потоков) и может выполнять ее различными способами, включая в себя многопоточную обработку во временных интервалах, одновременную многопоточную обработку (где одно физическое ядро предоставляет логическое ядро для каждого из потоков, для которых это физическое ядро одновременно выполняет многопоточную обработку), или их комбинацию (например, выборка во временных интервалах и декодирование, и одновременная многопоточная обработка после этого, такая как в технологии Hyperthreading компании Intel®).

В то время как замещение регистра описано в контексте исполнения не по порядку, следует понимать, что замещение регистра может использоваться в архитектуре с исполнением по порядку. В то время как представленный вариант осуществления процессора также включает в себя отдельную инструкцию и модули 434/474 кэш-данных и модуль 476 совместно используемого кэш L2, альтернативные варианты осуществления могут иметь один внутренний кэш, как для инструкций, так и для данных, такой как, например, внутренний кэш уровня 1 (L1), или множество уровней внутреннего кэш. В некоторых вариантах осуществления система может включать в себя комбинацию внутреннего кэш и внешнего кэш, который является внешним для ядра и/или процессора. В качестве альтернативы, все кэш могут быть внешними для ядра и/или процессора.

На фиг. 4 иллюстрируется блок-схема примерного процессора 102 и других компонентов вычислительной системы 100 в соответствии с одним или более аспектами настоящего раскрытия.

Как представлено на фиг. 4, ядро 490 процессора может включать в себя модуль 202 выборки, предназначенный для выборки инструкций, для исполнения ядром 490. Инструкции могут быть выбраны из одного или более устройств сохранения, таких как память 115. Ядро 490 процессора может дополнительно включать в себя модуль 440 декодирования, предназначенный для декодирования выбранной инструкции в одной или более микрооперациях (uop). Ядро процессора 490 может дополнительно включать в себя модуль 446 планирования для сохранения декодированных инструкций, принятых из модуля 440 декодирования, пока инструкция не будет готова для ее выпуска, например, до тех пор, пока значения операнда для декодированной инструкции не станут доступными. Модуль 446 планирования может планировать и/или выдавать декодированные инструкции в исполнительные модули 450.

Исполнительный модуль 450 включает в себя один или более арифметических и логических модулей (ALU), один или более исполнительных модулей для целого числа, одного или более исполнительных модулей для числа с плавающей точкой и/или других исполнительных модулей. В некоторых вариантах осуществления исполнительный модуль 450 может исполнять инструкции не по порядку (ООО). Ядро 490 процессора может дополнительно включать в себя модуль 454 окончания инструкции для окончания исполняемых инструкций после их завершения.

Ядро 490 процессора может дополнительно включать в себя таблицу 421 замещения регистра (RAT), файл 423 физического регистра (PRF), таблицу 425 устранения перемещения (MIT), модуль 427 слежения за флагом и логику 150 для слежения PRF. Даже при том, что на фиг. 4 логика 150 показана, как находящаяся в ядре 490, логика 150 может быть предусмотрена в другом месте в компьютерной системе 100. Кроме того, логика 150 и/или некоторые из ее компонентов могут совместно использоваться среди множества ядер процессора.

Как отмечено здесь выше, инструкции перемещения могут быть устранены путем копирования указателя регистра источника в указатель регистра назначения в RAT. На фиг. 5 схематично иллюстрируется исполнение инструкции MOV DX, AX при замещении регистра: содержание входа RAT для AX, который представляет собой указатель на вход X в PRF, копируется на вход RAT для DX. Как представлено фиг. 5, в некоторых вариантах осуществления в PRF может быть предусмотрен массив значений физического регистра, и в RAT может быть предусмотрен массив указателей на входы PRF.

Целочисленная инструкция может модифицировать не только значение регистра назначения, но также один или более флагов статуса процессора, включающих в себя, например, флаг (C) переноса, флаг (S) знака, флаг (P) четности, флаг (A) регулирования, флаг (Z) нуля и/или флаг (O) переполнения. Для сохранения значений флага, каждый вход PRF может включать в себя, вместе с полем для значения регистра данных, одно или более полей для значений флага. В некоторых вариантах осуществления флаги статуса процессора могут быть сохранены в двух полях PRF: поле бита C для сохранения значения для флага переноса и 5-битное поле SPAZO для сохранения значений флагов S, P, A, Z и O. Если один или более битов в поле должны быть обновлены новым значением, оставшиеся биты должны быть также обновлены предыдущей версией этих битов. Другими словами, для заданного момента при выполнении программы, один вход PRF содержит обновленные значения этих флагов в поле для этой точки в программе. Для группировок С и SPAZO, один вход PRF или комбинация двух физических регистров требуются для представления правильного состояния флага в заданной точке программы. Таким образом, результат микрооперации с целым числом может включать в себя значение регистра данных назначения и значения флага, которые могут быть записаны в один вход PRF, содержащий три отмеченных выше поля. В других вариантах выполнения все биты флага могут быть сгруппированы в одно поле, требующее только одного входа PRF для представления состояния флага в определенной точке программы; другие варианты осуществления могут администрировать каждым битом флага, как отдельным полем, требующим вплоть до шести входов PRF, для представления состояния флага в точке программы, для процессора с состоянием флага CSPAZO, как описано выше.

RAT может включать в себя один или более указателей, отображающих значения флага на входы PRF. В некоторых вариантах осуществления RAT может включать в себя вход, отображающий значение флага С на вход PRF, и вход, отображающий значения флага SPAZO на вход PRF. Следовательно, флаги статуса процессора могут иметь свои собственные логические входы в RAT (также называются “логическими регистрами флага”), но совместно использовать входы PRF с регистрами данных: как результат операции архитектурного обновления, как данных, так и флагов статуса, некоторые входы RAT могут быть обновлены для отображения на тот же вход PRF.

Вход PRF, на который ссылается множество входов RAT, может стать доступными для использования последующими инструкциями после перезаписи множества указателей RAT, включая в себя указатели на данные и флаг, одной или более инструкциями. Следовательно, механизм отслеживания требуется для отслеживания множества указателей RAT, обращающихся к входу PRF.

В некоторых вариантах осуществления структура данных, к которым обращается модуль отслеживания флага, может использоваться для отслеживания совместного использования входов в PRF логическими регистрами данных и флага. Модуль отслеживания флага может содержать один или более наборов полей, представляющих собой один или более флагов статуса. Как схематично показано на фиг. 6а, в одном примере, в модуле отслеживания флага может быть предусмотрен двумерной массив, имеющий две столбца, представляющие флаги статуса C и SPAZO, соответственно. Бит LDstV может быть установлен для обозначения того, что логический регистр данных, идентифицированный полем LDst, совместно использует вход PRF с соответствующим (например, С или SPAZO) регистром флага. Во время распределения, когда логический регистр был перезаписан, и флаги также были перезаписаны (предполагая отсутствие устранения перемещения), ассоциированный физический регистр может быть восстановлен после перезаписи отмены инструкции. Когда логический регистр, который в настоящее время совместно использует физический регистр с перезаписанными флагами, но в котором все или некоторые из флагов не были перезаписаны, поля LDstV, соответствующие этим полям флага, очищают. Только после перезаписи также этих конкретных групп флагов, физический регистр может быть восстановлен.

В определенных вариантах выполнения структура данных, называемая таблицей множественной инстанциации (MIT), может использоваться для ссыпок отслеживания на входы PRF. В некоторых вариантах осуществления MIT может содержать множество наборов битов, где набор битов может представлять операцию устранения перемещения, и бит в пределах набора может представлять логический регистр данных. MIT может быть воплощена как двумерный массив (например, матрица битов), имеющий множество рядов, представляющих логические регистры, и множество столбцов, представляющих наборы устранения перемещения, в которых установленный бит обозначает, что соответствующий регистр данных участвует в наборе устранения перемещения.

Когда только одно отображение регистра остается в наборе устранения перемещения, таким образом, что на соответствующих входах PRF остается только одна ссылка, набор устранения перемещения, предоставляемый столбцом MIT, может все еще не быть доступен для выделения для другой инструкции перемещения. Такой набор может называться установленным потерянным объектом, поскольку он имеет только одно отображение регистра. Без некоторых действий для очистки установленного потерянного объекта, он может оставаться недоступным до тех пор, пока последний логический регистр не будет перезаписан, уменьшая, таким образом, количество возможных устранений перемещения.

На фиг. 7a-7c схематично иллюстрируются несколько примеров использования таблицы множественной инстанциации (MIT) для отслеживания входа файла физического регистра (PRF), в соответствии с одним или более аспектами настоящего раскрытия. Когда устраняют операцию перемещения, биты, соответствующие логическим регистрам источника и логическим регистрам назначения, могут быть установлены, обозначая, что эти логические регистры составляют часть набора устранения перемещения, как схематично представлено фиг. 7a. Если источник инструкции перемещения представляет собой логический регистр, который уже участвует в наборе устранения перемещения, логический регистр назначения добавляют к набору, как схематично представлено на фиг. 7b. Когда регистр, участвующим в наборе устранения перемещения, перезаписывают другой инструкцией, соответствующий бит MIT (которая была ранее установлена), может быть очищена, что, таким образом, устраняет ассоциацию логического регистра с набором устранения перемещения, как схематично представлено на фиг. 7c. Соответствующий физический регистр, который не является частью какого-либо набора устранения перемещения или представляет собой единственный член в наборе устранения перемещения, может повторно использоваться новой инструкцией, как только все ссылки на физический регистр будут перезаписаны одной или более инструкциями и впоследствии завершены.

Пример, представленный на фиг. 7a-7c, не учитывает возможное совместное использование входов PRF логическими регистрами данных и флага. В некоторых вариантах осуществления модуль отслеживания флага может дополнительно включать в себя бит SharedFlag, который обозначает, используют ли флаги C и SPAZO один и тот вход PRF. В ситуациях, когда один из флагов C или SPAZO перезаписывают инструкцией, другой логический регистр флага может продолжать указывать на тот же вход PRF, до тех пор, пока второй флаг также не будет перезаписан другой инструкцией.

Как схематично показано на фиг. 6b, в одном примере, модуль отслеживания флага может быть расширен так, что он будет включать в себя поля действительного устранение перемещения (МЕВ) и столбец устранения перемещения (MECol). Бит МЕВ может быть установлен так, чтобы он обозначал, что поле MECol содержит действительный идентификатор столбца MIT, представляющий набор устранения перемещения, в котором флаг регистр совместно использует вход PRF с логическими регистрами. В некоторых вариантах осуществления поля LDst и MECol могут быть представлены совместно используемым полем, поскольку только одно из этих двух может быть действительным в любой момент времени.

На фиг. 8a-8c иллюстрируется пример использования модуля отслеживания флага для отслеживания совместного использования входов PRF логическими регистрами данных и флага. На фиг. 8a показано исходное состояние модуля отслеживания флага С: после обновления регистра ЕАХ и флага С исполняемой инструкцией, бит LDstV устанавливают так, чтобы он обозначал, что флаг С совместно использует вход PRF с логическим регистром, идентифицированным полем LDst. На фиг. 8b иллюстрируется результат операции копирования ЕАХ в ЕВХ: указатель ЕАХ в RAT копируют в ЕВХ (не показан); набор устранения перемещения формируют (не показан), так, что он включает в себя ЕАХ, ЕВХ и флаг C, ассоциированный с ним; в модуле отслеживания флага бит LDstV очищают так, чтобы он обозначал, что значение LDst больше не является соответствующим, бит МЕВ установлен, и больше никакой идентификатор набора устранения перемещения количества соответствующих столбцов MIT) на записан в MECol. На фиг. 8c иллюстрируется результат регистра ЕАХ, в который вновь записано новое значение без обновления флага C: Поле LDst обновлено для обозначения, что флаг C совместно использует вход PRF только с одним регистром (ЕВХ), бит LDstV установлен для обозначения того, что флаг С совместно использует вход PRF с логическим регистром, идентифицированным полем LDst (ЕВХ), и бит МЕВ очищен для обозначения того, что MECol не ссылается на действительный набор устранения перемещения.

В некоторых вариантах осуществления MIT может быть расширена так, чтобы она ассоциировала один или более битов, представляющих собой один или более логических регистров флага с каждым набором устранения перемещения. Ассоциация может быть выполнена путем добавления одного или более битов, представляющих один или более регистров логического флага для каждого столбца MIT. Следовательно, столбец MIT может включать в себя набор устранения перемещения (содержащий множество битов, представляющих логические регистры данных) и один или более битов, представляющих один или более логических регистров флага. В некоторых вариантах осуществления один бит может быть представлен двумя или более логическими регистрами флага. В одном примере первый бит, представляющий флаг C, и/или второй бит, представляющий флаги SPAZO, может быть добавлен к каждому столбцу MIT.

Добавление логических регистров флага к столбцам MIT устраняет необходимость установки полей LDst и LDstV в модуль отслеживания флага после того, как набор устранения перемещения становится потерянным объектом (ситуация, представленная примером на фиг. 8c), упрощая, таким образом, конструкцию системы и улучшая эффективность исполнения, как более подробно описано здесь ниже со ссылками на примеры на фиг. 9-10. Назначения установки бита флага в столбце MIT состоит в том, чтобы предотвратить восстановление логикой восстановления потерянного объекта соответствующего набора устранения перемещения, когда только один логический регистр данных остается в наборе.

Для дальнейшего улучшения эффективности исполнения логика 150 может консервативно предполагать, что одна или более операция устранения перемещения может включать в себя логический регистр, который совместно использует вход PRF с флагами статуса C и SPAZO. Следовательно, логика отслеживания может гипотетически устанавливать биты флагов (например, биты флага C и SPAZO) в MIT, в ответ на формирование или добавление регистра к набору устранения перемещения. Когда флаг перезаписывают, соответствующий бит MIT может быть очищен из всех столбцов в MIT для обозначения, что флаг не ассоциирован с наборами устранения перемещения. Как отмечено здесь выше, в некоторых вариантах осуществления, только логические и арифметические операции могут записывать биты флага, следовательно, результат этих операций всегда записывают в новый физический регистр, который может совместно использоваться только после последующей операции перемещения.

Поскольку в некоторых вариантах осуществления биты флага MIT могут быть установлены гипотетически, бит флага MIT не обязательно обозначает, что соответствующий флаг совместно использует вход PRF с другими членами набора устранения перемещения. Для того чтобы способствовать отслеживанию флага, логическая схема 150 может генерировать несколько сигналов, отражающих обновления MIT, включающих в себя сигнал, называемый MITOvrWrCol, обозначающий набор устранения перемещения (например, по числу соответствующих столбцов MIT), из которого логический регистр будет удален, в результате выделенной микрооперации, и сигнал, называемый LDstlsME, обозначающий, используется ли регистр места назначения для микрооперации совместно другим логическим регистром. Когда бит МЕВ для флага установлен (что обозначает, что регистр флага ассоциирован с набором устранения перемещения), сигнал MITOvrWrCol соответствует MECol (обозначающий, что операция выполняется при освобождении логического регистра из набора устранения перемещения, который совместно использует вход PRF, совместно с логическим регистром флага), и сигнал LDstlsME равен false (обозначает, что логический регистр, перезаписанный LDst операции, был последним оставшимся регистром в наборе устранения перемещения), флаг регистра больше не использует совместно вход PRF с регистром данных. Таким образом, бит МЕВ может быть очищен, и следующая операция записи флага может восстановить вход PRF.

Логическая схема отслеживания флага далее описана со ссылками на примеры, схематично представленные на фиг. 9a-9d и 10a-10d. Для ясности описания показаны только один столбец MIT, один флаг статуса и два регистра, но следует понимать, что вариант воплощения может содержать множество столбцов MIT, множество полей флага статуса и множество логических регистров.

В одном примере на фиг. 9a показано исходное состояние столбца 0 MIT и модуля отслеживания флага C: после обновления регистра ЕАХ и флага С выполненного инструкцией, бит LDstV установлен для обозначения того, что флаг С совместно использует вход PRF с логическим регистром, идентифицированным полем LDst. На фиг. 9b иллюстрируется результат операции копирования ЕАХ в ЕВХ: указатель ЕАХ в RAT копируют в ЕВХ (не показан); формируют набор устранения перемещения, включающий в себя ЕАХ, ЕВХ и флаг C; в модуле отслеживания флага бит LDstV очищают для обозначения того, что значение Ldst больше не является соответствующим, бит МЕВ устанавливают, и идентификатор набора устранения перемещения (количество соответствующих столбцов MIT) записывают в MECol. На фиг. 9c иллюстрируется результат перезаписи регистра ЕАХ новым значением: вход MIT отражает удаление ЕАХ из набора устранения перемещения путем сброса бита, представляющего ЕАХ; блок отслеживания флага остается таким же; восстановление потерянного объекта отменяют, поскольку бит флага все еще установлен, что обозначает, что флаги могут совместно использовать вход PRF с ЕВХ. На фиг. 9d иллюстрируется результат регистра ЕВХ, который является самым последним оставшимся регистром данных в наборе устранения перемещения, который перезаписан новым значением, но флаги статуса не были перезаписаны: вход MIT отражает удаление ЕВХ из набора устранения перемещения путем очистки соответствующего бита; в модуле отслеживания флага бит МЕВ очищают, и, следовательно, следующая запись флаг C будет восстанавливать вход PRF. Таким образом столбец 0 MIT является свободным для использования для другого устранения перемещения; флаг C не используется совместно ни с какими другими логическими регистрами, и, таким образом, не требуется отслеживать какое-либо совместное использование ни в одной из структур. Если бы флаг С был обновлен вместе с обновлением ЕВХ, вход PRF мог бы быть отмечен для восстановления в этом цикле.

В другом примере на фиг. 10a показано исходное состояние нескольких структур данных: после обновления регистра ЕАХ и флага C исполняемой инструкцией бит LDstV установлен для обозначения, что флаг С совместно использует вход PRF с логическим регистром, идентифицированным полем LDst. На фиг. 10b иллюстрируется результат операции устранения перемещения MOV ЕВХ, ЕАХ: указатель ЕАХ в RAT копируют в EBX (не показан); формируют набор устранения перемещения, включающий в себя EAX, EBX и флаг C, ассоциированный с ним; в модуле отслеживания флага бит LDstV очищают, бит МЕВ устанавливают, и идентификатор набора устраненного перемещения (число соответствующих столбцов MIT) записывают в MECol. На фиг. 10 с иллюстрируется результат перезаписи как регистра EAX, так и флага C новыми значениями: вход MIT отражает удаление EAX и флага C из набора устранения перемещения путем очистки соответствующих битов; модуль отслеживания флага обновляют для отражения ассоциации флага С и регистра ЕАХ: бит LDstV устанавливают, и бит МЕВ очищают. Следовательно, ЕВХ представляет собой последний регистр, остающийся в наборе устранения перемещения, и в следующем цикле механизм восстановления потерянного объекта восстанавливают в соответствующем столбце устранения перемещения, как схематично представлено на фиг. 10d. Предполагая, что ЕВХ не становится членом нового набора устраненного перемещения, вход PRF, используемый ЕВХ, будет помечен для восстановления в следующий раз, когда он будет перезаписан.

На фиг. 11 представлена блок-схема последовательности операций примера способа для отслеживания флага при операциях устранения перемещения, в соответствии с одним или более аспектами настоящего раскрытия. Способ 800 может выполняться компьютерной системой, которая может содержать аппаратные средства (например, схему, выделенную логическую схему и/или программируемую логическую схему), программное обеспечение (например, инструкции, исполняемые в компьютерной системе, для выполнения имитации аппаратных средств), или их комбинации. Способ 800 и/или каждая из его функций, процедур, подпрограмм или операций может быть выполнен одним или более физическими процессорами или компьютерной системой, исполняющей способ. Две или более функции, процедуры, подпрограммы или операции способа 800 могут быть выполнены параллельно или в порядке, который может отличаться от порядка, описанного выше. В одном примере, как представлено на фиг. 11, способ 800 может быть выполнен компьютерной системой 100 по фиг. 1.

Как показано на фиг. 11, в блоке 810, компьютерная система может сохранять множество значений физического регистра в первой структуре данных, называемой PRF.

В блоке 820, компьютерная система может сохранять во второй структуре данных, называемой RAT, множество элементов, обращающихся к указателям первой структуры данных.

В блоке 830, компьютерная система может сохранять, в третьей структуре данных, которая называется MIT, множество битов, представляющих множество логических регистров.

В блоке 840, компьютерная система может сохранять, в четвертой структуре данных, называемой блоков отслеживания флага, идентификатор регистра данных, совместно использующего элемент первой структуры данных с регистром флага.

В блоке 850, компьютерная система может выполнять операцию устранения перемещения путем обеспечения ссылки элемента второй структуры данных на элемент первой структуры данных.

В блоке 860, компьютерная система может отслеживать, используя, по меньшей мере, одну из третьей структуры данных и четвертой структуры данных, доступность элементов первой структуры данных. После завершения операции, представленной в блоке 850, способ может быть закончен.

На фиг. 12 показана блок-схема примерной компьютерной системы, в соответствии с одним или более аспектами настоящего раскрытия. Как показано на фиг. 12, многопроцессорная система 700 представляет собой систему взаимного соединения из точки в точку и включает в себя первый процессор 770 и второй процессор 780, соединенный со взаимным соединением 750 из точки в точку. Каждый из процессоров 770 и 780 может представлять собой определенную версию процессора 102, выполненную с возможностью выполнения операций транзакций доступа к памяти и/или операций без транзакций доступа к памяти, как описано более подробно здесь выше.

В то время, как показаны только два процессора 770, 780, следует понимать, что объем настоящего изобретения не ограничен этим. В других вариантах осуществления один или более дополнительных процессоров могут присутствовать в данном процессоре.

Процессоры 770 и 780 показаны, как включающие в себя модули 772 и 782 контроллера интегрированной памяти, соответственно. Процессор 770 также включает в себя как часть своих модулей контроллера шины интерфейсы 776 и 778 ʺиз точки в точкуʺ (P-P); аналогично, второй процессор 780 включает в себя интерфейсы 786 и 788 P-P. Процессоры 770, 780 могут выполнять обмен информацией через интерфейс 750 “из точки в точку” (P-P), используя схемы 778, 788 интерфейса P-P. Как показано на фиг. 12, IMC 772 и 782 соединяют процессоры с соответствующим запоминающими устройствами, а именно, с памятью 732 и памятью 734, которые могут представлять собой часть основной памяти, локально соединенной с соответствующими процессорами.

Каждый процессор 770, 780 может выполнять обмен информацией с набором 790 микросхем через индивидуальные интерфейсы 752, 754 P-P, используя схемы 776, 794, 786, 798 интерфейса из точки в точку. Набор 790 микросхем также может выполнять обмен информацией с высокопроизводительной графической схемой 738 через высокопроизводительной графический интерфейс 739.

Совместно используемый кэш (не показан) может быть включен в любой из процессора или за пределами обоих процессоров, все же будучи соединенным с процессорами через взаимное соединение P-P, таким образом, что информация локального кэш любого или обоих процессоров может быть сохранена в совместно используемом кэш, если процессор переведен в режим низкого потребления питания.

Набор 790 микросхем может быть соединен с первой шиной 716 через интерфейс 796. В одном варианте осуществления, первая шина 716 может представлять собой шину межсоединения периферийных компонентов (PCI) или шину, такую как шина PCI Express или другую шину взаимного соединения I/O третьего поколения, хотя объем настоящего изобретения не ограничен этим.

Как показано на фиг. 12, различные устройства 714 I/O могут быть соединены с первой шиной 716 вдоль мостика 718 шины, который соединяет первую шину 716 со второй шиной 720. В одном варианте осуществления вторая шина 720 может представлять собой шину с малым количеством выводов (LPC). Различные устройства могут быть соединены со второй шиной 720, включающие в себя, например, клавиатуру и/или “мышь” 722, устройства 727 передачи данных и модуль 728 сохранения, такой как привод диска или другое устройство большой емкости, которое может включать в себя инструкции/код и данные 730, в одном варианте осуществления. Кроме того, аудио I/O 724 может быть соединен со второй шиной 720. Следует отметить, что также возможны другие архитектуры. Например, вместо архитектуры “из точки в точку” по фиг. 12, система может воплощать многоточечную шину или другую такую архитектуру.

В следующих примерах иллюстрируются различные варианты воплощения в соответствии с одним или более аспектами настоящего раскрытия.

В примере 1 представлена система обработки, содержащая: первую структуру данных, включающую в себя множество значений физического регистра; вторую структуру данных, включающую в себя множество элементов ссылки на указатели первой структуры данных; третью структуру данных, включающую в себя множество наборов устранения перемещения, при этом каждый из наборов устранения перемещения содержит два или более битов, представляющих два или более логических регистра данных, причем третья структура данных дополнительно содержит по меньшей мере один бит, ассоциированный с каждым набором устранения перемещения по меньшей мере один бит, представляющий собой один или более логических регистров флага; четвертую структуру данных, включающую в себя идентификатор регистра данных, совместно использующего элемент первой структуры данных с регистром флага; и логическую схему устранения перемещения, выполненную с возможностью выполнения операции устранения перемещения путем обеспечения обращения элемента второй структуры данных к элементу первой структуры данных, при этом логическая схема устранения перемещения дополнительно выполнена с возможностью отслеживания, используя по меньшей мере одну из третьей структуры данных и четвертой структуры данных, доступность элементов первой структуры данных.

В примере 2 логическая схема устранения перемещения системы обработки по примеру 1 может быть выполнена с возможностью изменением значения бита флага в третьей структуре данных, в ответ по меньшей мере на одно из: формирования нового набора устранения перемещения, суммирования регистра с набором устранения перемещения, или записи новых данных к регистру флага в первой структуре данных.

В примере 3 логическая схема устранения перемещения системы обработки по примеру 1 может быть выполнена с возможностью обнаружения и восстановления набора устранения перемещения, имеющего только один ненулевой бит.

В примере 4 логическая схема устранения перемещения системы обработки по примеру 1 может быть выполнена с возможностью отмены восстановления набора устранения перемещения, имеющего по меньшей мере один ненулевой бит, в ответ на определение, что по меньшей мере один бит, ассоциированный с набором устранения перемещения и представляющий логический регистр флага, имеет ненулевое значение.

В примере 5, четвертая структура данных системы обработки по примеру 1 может содержать: бит, обозначающий действительность набора устранения перемещения, бит, обозначающий, что логический регистр флага совместно использует вход в первую структуру данных с регистром данных, первый идентификатор, обозначающий регистр данных, совместно использующий элемент первой структуры данных с регистром флага, и второй идентификатор, идентифицирующий набор устранения перемещения.

В примере 6, первый идентификатор и второй идентификатор системы обработки по примеру 5 могут быть представлены, как общее поле данных.

В примере 7, логическая схема устранения перемещения системы обработки по примеру 1 может быть дополнительно выполнена с возможностью генерировать первый сигнал, идентифицирующий набор устранения перемещения, в котором один или более логических регистров перезаписаны выделенной микрооперацией, и второй сигнал, обозначающий совместное использование регистра назначения для микрооперации.

В примере 8, логическая схема устранения перемещения системы обработки по примеру 7 может быть дополнительно выполнена с возможностью обновления четвертой структуры данных для обозначения, что регистр флага больше не использует совместно элемент первой структуры данных с регистром данных, в ответ на определение, что логический регистр флага, соответствующий регистру флага, ассоциирован с первым набором устранения перемещения, первый сигнал соответствует идентификатору первого набора устранения перемещения, и второй сигнал имеет значение false.

Пример 9 направлен на способ выполнения операции манипуляции с данными, содержащий этапы, на которых: сохраняют, с помощью компьютерной системы, множество значений физического регистра в первой структуре данных; сохраняют, во второй структуре данных множество элементов, обращающихся к указателям первой структуры данных; сохраняют, в третьей структуре данных множество наборов устранения перемещения и по меньшей мере один бит, ассоциированный с каждым набором устранения перемещения по меньшей мере один бит, представляющий один или более логических регистров флага, каждый набор устранения перемещения, содержащий два или более бита, представляющих два или более логических регистра данных; сохраняют, в четвертой структуре данных, идентификатор регистра данных, совместно использующего элемент первой структуры данных с регистром флага; выполняют операции устранения перемещения путем обеспечения ссылки элемента второй структуры данных на элемент первой структуры данных; и отслеживают используя по меньшей мере, одну из третьей структуры данных и четвертой структуры данных, доступность элементов первой структуры данных.

В примере 10 способ по примеру 9 может дополнительно содержать этап, на котором: изменяют значения бита флага в третьей структуре данных в ответ на по меньшей мере одно из: формирования нового набора устранения перемещения, добавления регистра к набору устранения перемещения или записи новых данных в регистр флага в первой структуре данных.

В примере 11, способ по примеру 9 может дополнительно содержать этап, на котором: обнаруживают и восстанавливают набор устранения перемещения, имеющий только один ненулевой бит.

В примере 12, способ по примеру 11 может дополнительно содержать этап, на котором: отменяют восстановление набора устранения перемещения, имеющего по меньшей мере один ненулевой бит, в ответ на определение, что по меньшей мере один бит, ассоциированный с набором устранения перемещения и представляющий логический регистр флага, имеет ненулевое значение.

В примере 13 четвертая структура данных способа по примеру 9 может содержать: бит, обозначающий действительность набора устранения перемещения, бит, обозначающий, что логический регистр флага совместно использует вход первой структуры данных с регистром данных, первый идентификатор, идентифицирующий регистр данных, совместно использующий элемент первой структуры данных, с регистром флага, и второй идентификатор, идентифицирующий набор устранения перемещения.

В примере 14, первый идентификатор и второй идентификатор способа по примеру 13 могут быть представлены общим полем данных.

В примере 15, способ по примеру 9 может дополнительно содержать этап, на котором: генерируют первый сигнал, идентифицирующий набор устранения перемещения, имеющий один или более логических регистров, перезаписанных выделенной микрооперацией, и второй сигнал, обозначающий совместное использование регистра назначения для микрооперации.

В примере 16, способ по примеру 15 может дополнительно содержать этап, на котором: обновляют четвертую структуру данных для обозначения, что регистр флага больше не использует совместно элемент первой структуры данных с регистром данных, в ответ на определение, что логический регистр флага, соответствующий регистру флага, ассоциирован с первым набором устранения перемещения, первый сигнал соответствует идентификатору первого набора устранения перемещения и второй сигнал равен false.

Пример 17 направлен на устройство, содержащее запоминающее устройство и систему обработки, соединенную с запоминающим устройством, в котором система обработки выполнена с возможностью выполнения способа по любому из примеров 9-16.

Пример 18 направлен на считываемый компьютером энергонезависимый носитель информации, содержащий исполняемые инструкции, которые, при их исполнения компьютерной системой, обеспечивают выполнение компьютерной системой функционирования, содержащего этапы, на которых: сохраняют с помощью компьютерной системы множество значений физического регистра в первой структуре данных; сохраняют во второй структуре данных, множество элементов, обращающихся к указателям первой структуры данных; сохраняют в третьей структуре данных множество наборов устранения перемещения и по меньшей мере одного бита, ассоциированного с каждым набором устранения перемещения по меньшей мере один бит, представляющий один или более логических регистров флага, каждый набор устранения перемещения, содержит два или более битов, представляющих два или более логических регистра данных; сохраняют в четвертой структуре данных, идентификатора регистра данных, совместно использующего элемент первой структуры данных с регистром флага; выполняют операцию устранения перемещения, обеспечивая обращение элемента второй структуры данных к элементу первой структуры данных; и отслеживают, с использованием по меньшей мере одной из третьей структуры данных и четвертой структуры данных, доступность элементов в первой структуре данных.

В примере 19, считываемый компьютером энергонезависимый носитель информации по примеру 18 может дополнительно содержать исполняемые инструкции, обеспечивающие изменение компьютерной системой значения бита флага в третьей структуре данных, в ответ на по меньшей мере одно из: формирования нового набора устранения перемещения, добавления регистра к набору устранения перемещения, или записи новых данных в регистр флага в первой структуре данных.

В примере 20, считываемый компьютером энергонезависимый носитель информации по примеру 18 может дополнительно содержать исполняемые инструкции, обеспечивающие обнаружение компьютерной системой и восстановление набора устранения перемещения, имеющего только один ненулевой бит.

В примере 21, считываемый компьютером энергонезависимый носитель информации по примеру 20 может дополнительно содержать исполняемые инструкции, обеспечивающие отмену компьютерной системой восстановления набора устранения перемещения, имеющего по меньшей мере один ненулевой бит, в ответ на определение, что по меньшей мере один бит, ассоциированный с набором устранения перемещения и представляющий логический регистр флага, имеет ненулевое значение.

В примере 22, четвертая структура данных считываемого компьютером энергонезависимого носителя информации по примеру 18 может содержать: бит, обозначающий действительность набора устранения перемещения, бит, обозначающий, что логический регистр флага совместно использует вход первой структуры данных с регистром данных, первый идентификатор, идентифицирующий регистр данных, совместно использующий элемент первой структуры данных с регистром флага, и второй идентификатор, идентифицирующий набор устранения перемещения.

В примере 23 первый идентификатор и второй идентификатор по примеру 22 могут быть представлены общим полем данных.

В примере 24, считываемый компьютером энергонезависимый носитель информации по примеру 18 может дополнительно содержать исполняемые инструкции, обеспечивающие генерирование компьютерной системой первого сигнала, идентифицирующего набор устранения перемещения, в котором один или более логических регистров перезаписаны выделенной микрооперацией, и второй сигнал, обозначающий совместное использование регистра назначения для микрооперации.

В примере 25 считываемый компьютером энергонезависимый носитель информации по примеру 18 может дополнительно содержать исполняемые инструкции, обеспечивающие обновление компьютерной системой четвертой структуры данных для обозначения, что регистр флага больше не использует совместно используемый элемент первой структуры данных с регистром данных, в ответ на определение, что логический регистр флага, соответствующий регистру флага, ассоциирован с первым набором устранения перемещения, первый сигнал соответствует идентификатору первого набора устранения перемещения, и второй сигнал равен false.