Область техники, к которой относится изобретение

Настоящее изобретение относится в целом к области конвейерных процессоров и, в частности, к способу моделирования поведения предсказания переходов явного вызова подпрограммы или неявного вызова подпрограммы, чтобы уменьшить мощность и повысить коэффициент использования конвейерного процессора.

Уровень техники

Микропроцессоры осуществляют вычислительные задачи в широком множестве приложений. Улучшенная эффективность процессора является почти всегда желательной, чтобы позволить более быструю работу и/или улучшенные функциональные возможности с помощью программных изменений. Во многих осуществленных приложениях, например портативных электронных устройствах, сохранение мощности является также важной целью в проектировании и реализации процессора.

Многие современные процессоры применяют конвейерную архитектуру, где последовательные команды перекрываются в выполнении, чтобы увеличить общую пропускную способность процессора. Поддержание сглаженного выполнения с помощью конвейера является критичным для достижения высокой производительности. Большинство современных процессоров также используют иерархическую память с быстрой внутренней кэш-памятью, сохраняющей локальные копии данных и команд, к которым недавно осуществлялся доступ.

Реальные программы включают в себя непрямые команды перехода, фактическое поведение перехода которых не известно до тех пор, пока команда фактически не оценена глубоко в конвейере выполнения. Большинство современных процессоров используют некоторый вид предсказания перехода, при этом поведение переходов непрямых команд перехода предсказывается заранее в конвейере, например во время этапа извлечения или декодирования конвейера. Используя метод предсказания перехода, процессор спекулятивно (по предположению) извлекает цель непрямой команды перехода и переадресовывает конвейер, чтобы начать обработку извлеченных по предположению команд. Когда фактическая цель перехода определена на последнем этапе конвейера, таком как этап выполнения конвейера, если переход был неверно предсказан, извлеченные по предположению команды должны быть сброшены из конвейера, и новые команды извлечены из правильного адреса цели. Предварительное извлечение команд в ответ на ошибочное предсказание цели перехода отрицательно влияет на эффективность процессора и потребление мощности.

Один пример непрямых команд перехода включает в себя команды перехода, используемые для возвращения из подпрограммы. Например, вызов возврата из подпрограммы может включать в себя команду перехода, адрес возврата которой определяется с помощью содержимого регистра. Адрес возврата определяет следующую команду, подлежащую извлечению после того, как подпрограмма завершится, и является в общем командой после команды перехода, из которой изначально вызывалась подпрограмма. Многие высокоэффективные архитектуры назначают конкретный регистр общего назначения для использования в возвратах подпрограмм, в общем упоминаемый как регистр ссылок.

Для удобства вызов возврата может также упоминаться как команда возврата перехода. Для того чтобы конвейер обработки использовал предсказание переходов для команды возврата перехода, традиционное программное обеспечение включает в себя явный вызов подпрограммы, такой как команда перехода и ссылки для записи адреса возврата в регистр ссылок. Многие высокоэффективные варианты осуществления включают в себя структуру стека ссылок на этапе декодирования обработки команды перехода и ссылки. Значения ссылки возврата помещаются в этот стек для того, чтобы разрешить точное предсказание перехода, когда соответствующие подпрограммы возвращаются. Традиционные структуры стека ссылок содержат список адресов возврата для поддержания многочисленных вызовов подпрограмм, протекающих через конвейер, и поддержания вложенности многочисленных уровней вызовов подпрограмм. Впоследствии, когда команда возврата перехода в подпрограмме декодируется, адрес возврата считывается из структуры стека ссылок, чтобы использоваться в предсказании перехода для предсказания адреса цели, если другое аппаратное оборудование предсказания перехода предписывает, что процессор должен переадресовывать конвейер. Если предсказание указывает переадресовать конвейер, конвейер начинает извлечение команд из адреса возврата, который был считан из стека ссылок.

Однако существует унаследованное программное обеспечение, которое не содержит в себе традиционные команды перехода и ссылки во время вызова подпрограммы и, следовательно, которое не позволяет использовать структуру стека ссылок. В качестве примера сошлемся на следующую таблицу, содержащую сегмент кода, который выполняется на процессоре, совместимом с ARM Ltd.:

Унаследованный сегмент кода

Комбинация команд MOV LR, PC и BR готовит процессор к последующему переходу к подпрограмме. В этом примере фактическая подпрограмма, к которой сделан вызов, начинается с адреса 0x00990000. Команда MOV LR, PC указывает, что содержимое счетчика команд (PC) должно быть скопировано в регистр ссылок (LR). В некоторых архитектурах команд, таких как ARM, счетчик команд фактически определяется как текущий адрес команды плюс 8 байтов. С помощью этого определения перемещение содержимого PC в LR приводит к сохранению адреса возврата, адреса 0x00899908, в регистре ссылок. Адрес возврата извлекается из регистра ссылок в конце подпрограммы. Более конкретно адрес возврата извлекается во время выполнения BX LR, команды возврата перехода.

В современных процессорах, которые включают глубокие конвейеры и используют методы предсказания перехода, предсказание адреса возврата во время декодирования команды возврата перехода без использования стека ссылок является проблематичным из-за различных причин. Одна причина затрагивает соглашение микроархитектуры, которое не позволяет осуществлять доступ к регистру общего назначения, например регистру ссылок, во время этапа декодирования конвейера, таким образом препятствуя предсказанию перехода адреса возврата, используя "текущее" значение регистра ссылок в момент предсказания перехода. Даже если изменение может быть выполнено в этом соглашении микроархитектуры, современные глубокие конвейеры могут привести к ненадежности данных, содержащихся в регистре ссылок, для целей предсказания. Например, в момент времени, когда команда перехода идет от этапа декодирования конвейера, где предсказание выполнено для адреса возврата, в этап выполнения конвейера, где выполнено фактическое разрешение адреса возврата, последующая команда перехода может войти в конвейер и переписать регистр ссылок, вследствие чего фактическое разрешение адреса возврата для первоначальной команды возврата перехода будет отличаться от предсказанного адреса возврата. Это несоответствие между предсказанной величиной и фактическим разрешением упоминается как ошибочное предсказание цели перехода. Ошибочные предсказания перехода приводят к потерянному времени и потерянной мощности, что вместе приводит к спекулятивному выполнению ошибочно предсказанного маршрута.

При заданной распространенности такого унаследованного программного обеспечения и затрат, задействованных в перезаписи унаследованного программного обеспечения, чтобы использовать традиционные команды перехода и ссылки во время вызова подпрограммы, существует необходимость в микропроцессорах, разрабатываемых сегодня для поддержания унаследованного программного обеспечения, и необходимость в использовании этим унаследованным программным обеспечением структуры стека ссылок для того, чтобы эффективно предсказывать адрес возврата, когда команда возврата находится на этапе декодирования конвейера.

Раскрытие изобретения

Настоящее раскрытие распознает шаблон команд, которые определяют неявный вызов подпрограммы для подпрограммы, и использует это распознавание, чтобы разработать способы и устройство для использования ресурсов явного вызова подпрограмм, чтобы разрешить предсказанию перехода предсказывать адрес возврата подпрограммы.

Согласно одному аспекту раскрыт способ моделирования поведения предсказания перехода явной подпрограммы. Способ включает в себя распознавание адреса команды, указывающей неявный вызов подпрограммы в подпрограмме, вычисление адреса возврата из адреса команды и сохранение адреса возврата для ресурса явной подпрограммы.

Другой аспект относится к устройству. Устройство включает в себя первый вход, который конфигурируется для приема адреса команды, и второй вход. Второй вход конфигурируется для приема предварительно декодированной информации, которая описывает адрес команды, как ассоциируемого с неявным вызовом подпрограммы в подпрограмме. В ответ на информацию предварительного декодирования устройство также включает в себя сумматор, сконфигурированный для добавления смещения к адресу команды, определяющего адрес возврата. Сумматор также конфигурируется для хранения адреса возврата к ресурсу явной подпрограммы, облегчая последующее предсказание перехода команды вызова возврата.

Согласно еще одному аспекту раскрыто другое устройство. Устройство содержит первый и второй входы, сконфигурированные для одновременного приема первого и второго адресов команд, и ассоциированную предварительно декодированную информацию. Устройство дополнительно содержит первый набор сумматоров, сконфигурированных для добавления смещения к первым и вторым адресам команд, чтобы определить первый и второй результаты в ответ на предварительно декодированную информацию, указывающую, что первый или второй адрес команд ассоциирован с неявным вызовом подпрограммы для подпрограммы. Устройство дополнительно содержит средство для выбора адреса возврата из первого или второго результата.

Разумеется, что другие варианты осуществления настоящего изобретения легко станут очевидными специалистам в данной области техники из последующего подробного описания, в котором показаны и описаны в качестве иллюстрации различные варианты осуществления изобретения. Как будет представлено, изобретение допускает другие и отличающиеся варианты осуществления, и его различные детали допускают модификацию во многих других отношениях без отклонения от настоящего изобретения. Соответственно, чертежи и подробное описание должны рассматриваться как пояснительные по характеру, а не как ограничивающие.

Краткое описание чертежей

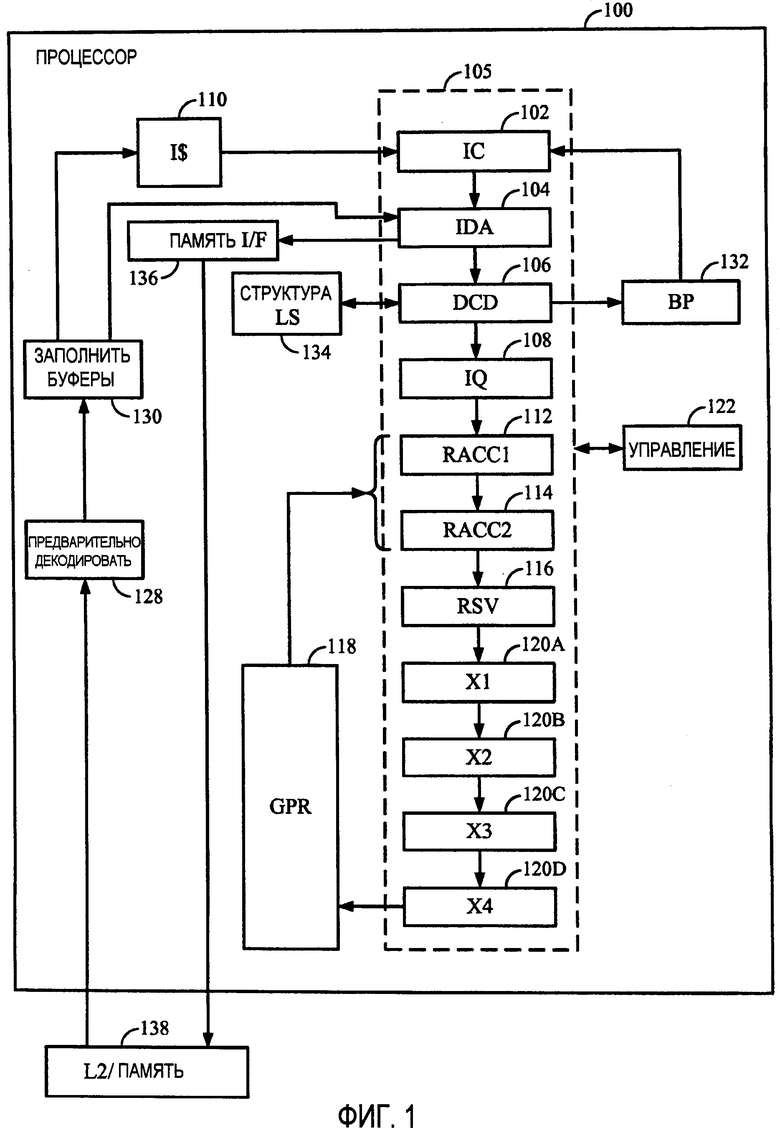

Фиг.1 - функциональная блок-схема процессора.

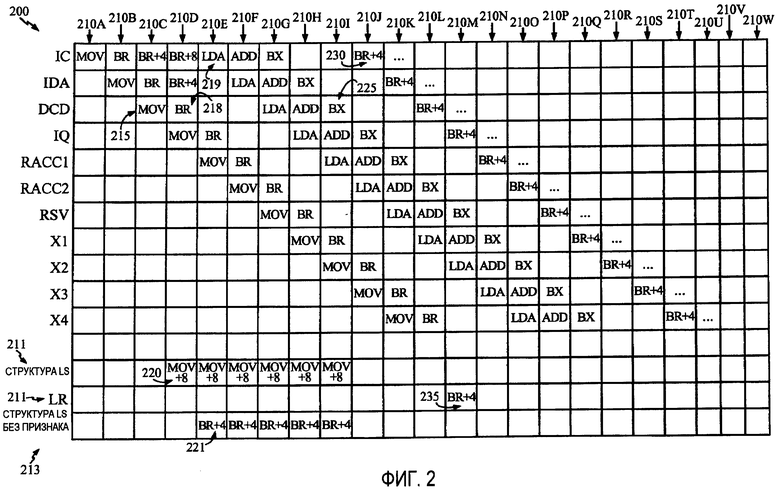

Фиг.2 - временная диаграмма, которой следует протекание команд через конвейер, проиллюстрированный на фиг.1.

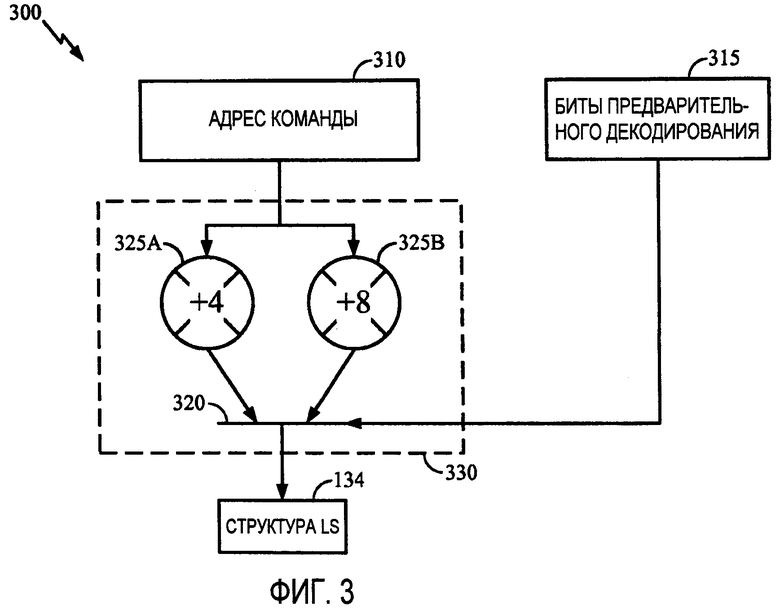

Фиг.3 - примерная часть этапа декодирования конвейером единственной команды.

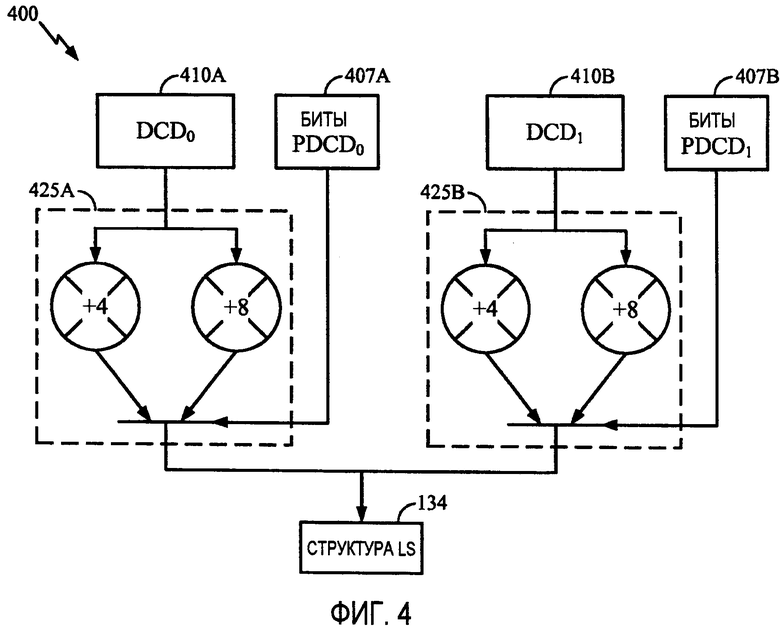

Фиг.4 - примерный первый аспект части этапа декодирования конвейером двойной команды.

Фиг.5 - примерный второй аспект части этапа декодирования конвейером двойной команды на фиг.1.

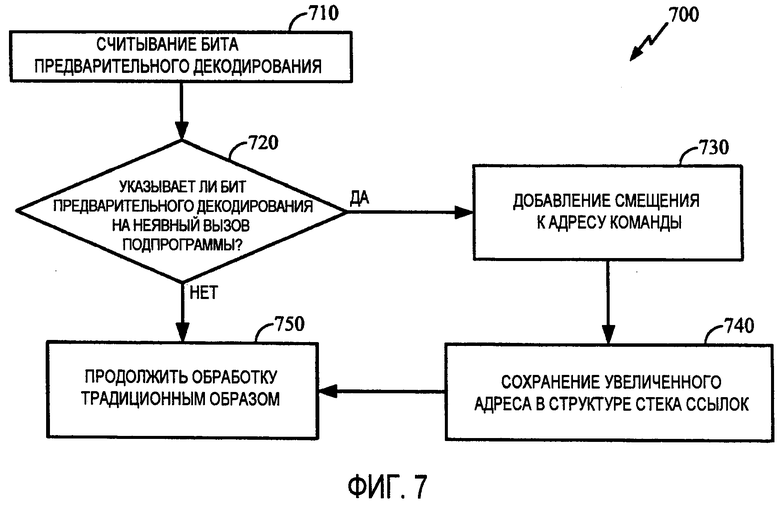

Фиг.6 - блок-схема, иллюстрирующая способ моделирования поведения предсказания переходов явной подпрограммы, когда определяется неявный вызов подпрограммы.

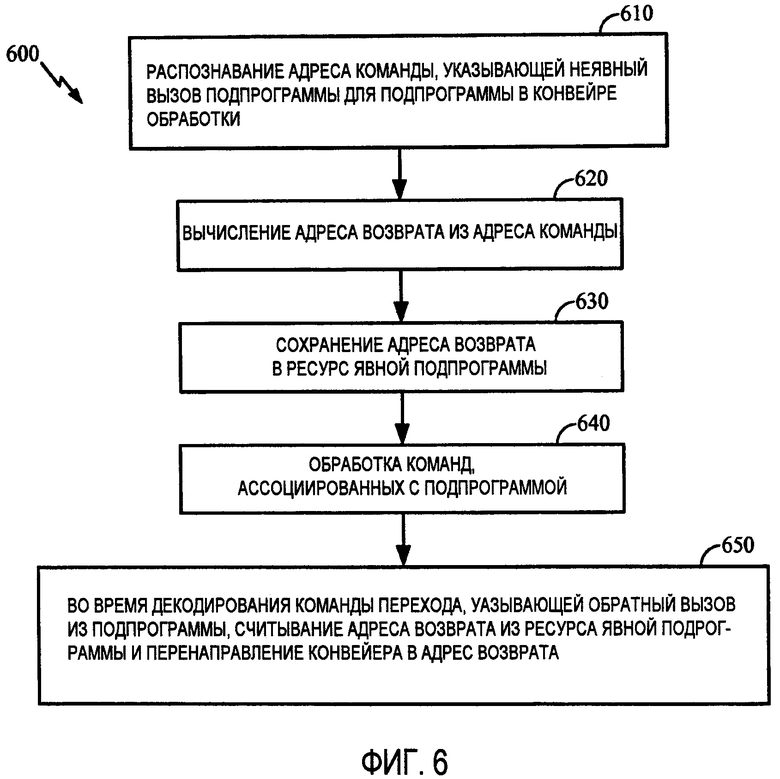

Фиг.7 - блок-схема, которая показывает дополнительные подробности этапов 610, 620 и 630 на фиг.6.

Осуществление изобретения

Фиг.1 показывает функциональную блок-схему процессора 100, в аспектах которого настоящее изобретение может быть применено. Процессор 100 включает в себя кэш 110 команд (I-кэш) для кэширования недавно обработанных команд, интерфейс 136 памяти для осуществления доступа к памяти 138, когда команда не найдена, в I-кэш 110, логическую схему 128 предварительного декодирования для осуществления ограниченного декодирования команды, извлеченной из памяти 138, и логическую схему 130 заполнения буфера для записи данных команд, включающих в себя биты предварительного декодирования, в I-кэш 110 в ответ на отсутствие в I-кэш 110. Биты предварительного декодирования ассоциированы с командой, извлеченной из памяти, и содержат атрибуты, описывающие команду, например указание типа команды. Память 138 может находиться в процессоре 100 или вне его и может содержать компонент памяти уровня 2 (L2).

Процессор 100 также включает в себя конвейер 105 команд для обработки команд и схему 132 предсказания переходов для предсказания адреса цели для команды перехода с косвенной адресацией и предсказание, переадресовывать ли конвейер 105 команд для обработки адреса цели. Если схема 132 предсказания перехода прогнозирует переадресовывать конвейер 105 команд, говорят, что команда перехода с косвенной адресацией должна быть "принята предсказанной". Если команда перехода с косвенной адресацией "принята предсказанной", схема 132 предсказания перехода предсказывает адрес цели команды перехода с косвенной адресацией и переадресовывает конвейер 105 команд к началу извлечения команд, начиная с адреса цели.

Процессор 100 обрабатывает команды в конвейере 105 команд согласно логической схеме 122 управления. В некоторых вариантах осуществления конвейер 105 может быть суперскалярной схемой, которая имеет два или более параллельных конвейера. Конвейер 105 включает в себя различные этапы конвейера: этап 102 поиска кэша команд (IC), этап 104 согласования данных команд (IDA), этап 106 декодирования (DCD), этап 108 очереди команд (IQ), этап 112 доступа к первому регистру (RACC1), этап 114 доступа ко второму регистру (RACC2), этап 116 терминала резервирования (RSV) и четыре этапа 120A-120D выполнения (X1-X4). В некоторых вариантах осуществления этап конвейера может обрабатывать единственную команду в один момент времени. В другом варианте осуществления этап конвейера может одновременно обрабатывать две или более команд. Следует заметить, что этапы конвейера могут быть добавлены или удалены из конвейера 105 без ограничения объема настоящего изобретения. Процессор 100 также включает в себя файл 118 регистра общего назначения (GPR), который включает в себя регистры, которые с помощью соглашения микроархитектуры доступны этапам 112, 114 и 120A-120D конвейера.

Этап 102 поиска кэша команд (IC) пытается извлечь команду из I-кэша 110. Этап 104 согласования данных команд разбивает многочисленные команды и предварительно декодирует информацию, ассоциированную с многочисленными командами. Если адрес команды не найден в I-кэше 110, этап 104 согласования данных команд инициирует запрос для извлечения соответствующей команды из памяти 138. Этап 106 декодирования полностью декодирует команду. Кроме того, в дополнение к традиционным функциям, этап 106 декодирования распознает команды явного вызова подпрограммы и записывает адрес возврата в структуру 134 стека ссылок. Более того, этап 106 декодирования также распознает неявный вызов подпрограммы из унаследованного программного обеспечения и сохраняет адрес возврата в структуру 134 стека ссылок. Структура 134 стека ссылок может быть набором регистров, управляемых как циклический буфер. Адрес возврата является адресом команды, к которой должен переадресовываться конвейер 105 при завершении неявной подпрограммы. Структура и действие соответствующих аспектов этапа 106 декодирования будут описаны более полно в связи с обсуждением фиг.3-5.

Этап 108 очереди команд буферизует одну или более команд, чтобы разрешить спекулятивное извлечение для продолжения во время остановок конвейера выполнения. Эти этапы 112 и 114 доступа к первому и второму регистрам извлекают один или более операндов из регистра 118 общего назначения как может быть необходимо команде. Этап 116 терминала резервирования разрешает команде ожидать устранения отказов прочтения после записи и тому подобного. Этапы выполнения включают в себя известные компоненты, например блоки арифметической логики и тому подобное. Этапы 120A-120D выполнения исполняют команды. Результаты, формируемые из этапов выполнения, записываются в файл 118 GPR. Во время этапов 120A-120D выполнения возникает разрешение фактического перехода для определения, является ли корректным предсказание перехода, сделанное на этапе 106 декодирования. Если разрешение фактического перехода отличается от предсказанного назначения, говорят, что переход предсказан ошибочно.

Специалистам в данной области техники должно быть понятно, что возможны многочисленные варианты процессора 100. Например, процессор 100 может включать в себя кэш второго уровня (L2) для I-кэш 110. Кроме того, один или более функциональных блоков, отображенных в процессоре 100, могут быть опущены в конкретном варианте осуществления. Другие функциональные блоки, которые могут постоянно находиться в процессоре 100, например буфер быстрой переадресации, кэш данных и тому подобное, не являются тесно связанными с описанием настоящего изобретения и опущены для ясности.

Фиг.2 является временной диаграммой 200, отслеживающей поток команд через конвейер 105, проиллюстрированный на фиг.1. В частности, поток команд, отслеживаемый на временной диаграмме 200, является унаследованным кодовым сегментом как проиллюстрировано в таблице 1. Для целей настоящего изобретения термин "неявный вызов процедуры" относится к комбинации из двух или более команд, комбинированной функцией которых является установка регистров, подготавливающихся для вызова подпрограммы, и вызову подпрограммы. Например, ссылаясь на таблицу 1, две команды в комбинации MOV LR, PC/BR определяют неявный вызов подпрограммы. В этом случае команда MOV LR, PC определяет начало неявного вызова подпрограммы, и команда BR определяет окончание неявного вызова подпрограммы.

Первые одиннадцать строк временной диаграммы 200 соответствуют этапам конвейера 105. Столбцы 210A-210W соответствуют последовательным временным циклам. Для целей пояснения каждый этап конвейера обрабатывает одну команду за цикл. Однако специалист в данной области техники может понять, что идеи настоящего изобретения применяются как к многочисленным этапам циклического конвейера, так и к этапам конвейера, которые могут обрабатывать многочисленные команды за цикл.

Строка 211 временной диаграммы 200 соответствует содержимому структуры стека ссылок, например структуре 134 стека ссылок как результату аспектов этапа декодирования конвейера, проиллюстрированного на фиг.3 и 4. Строка 213 временной диаграммы 200 соответствует содержимому структуры стека ссылок как результату аспектов этапа декодирования конвейером, проиллюстрированного на фиг.5. Строка 213 будет рассматриваться в связи с обсуждением фиг.5. Строка 212 временной диаграммы 200 соответствует содержимому регистра ссылок.

В общем, команды входят на этап 102 1С и распространяются до следующего этапа в следующем цикле. На 215 команда MOV LR, PC находится на этапе 106 декодирования. В этот момент времени этап 106 декодирования распознает MOV LR, PC и сохраняет адрес возврата, MOV+8, в структуре стека ссылок. Для целей терминологии MOV+8 относится к добавлению смещения на восемь к адресу команды MOV. Значение восемь включает в себя четыре байта команды MOV и четыре байта последующей команды BR так, чтобы структура стека ссылок содержала адрес последующей команды после команды BR. Как будет рассматриваться дополнительно в связи с рассмотрением фиг.3-4, этап декодирования согласно настоящим идеям раскрытия добавляет смещение из восьми в адрес команды MOV. Как будет рассматриваться дополнительно в связи с рассмотрением фиг.5, этап альтернативного декодирования согласно настоящим идеям раскрытия добавляет смещение из четырех в адрес команды BR. Следует заметить, что обе записи MOV+8 и BR+4 ссылаются на адрес 0x00899908, адрес возврата. В ссылке 220 структура стека ссылок показывает свое содержимое, которое должно быть MOV+8. Когда команда BR обрабатывается с помощью этапа 106 декодирования, цель команды перехода, начало подпрограммы предсказывается и извлекается конвейером в следующем цикле. В ссылке 219 команда LDA, начало подпрограммы, обрабатывается с помощью этапа 102 1С. Так как конвейер 105 перенаправляется для извлечения команды LDA из-за предсказания команды перехода, команды в адресах BR+4 и BR+8 сбрасываются из конвейера. Команды, следующие по порядку за командой LDA, затем извлекаются в конвейере 105.

В ссылке 225 команда возврата перехода BX обрабатывается с помощью этапа 106 декодирования. Этап 106 декодирования активирует схему 132 предсказания перехода с содержимым структуры стека ссылок для предсказания адреса возврата. В другом варианте осуществления схема 132 предсказания перехода считывает структуру стека ссылок. В любом случае схема 132 предсказания перехода использует структуру стека ссылок для предсказания адреса возврата, и в ссылке 230 конвейер перенаправляется для извлечения команды по адресу 0x00899908 возврата. Будучи использованной, запись MOV+8 в строке 211, столбце 210J удаляется из структуры стека ссылок.

В традиционных процессорах, которые не используют стек ссылок для неявных вызовов подпрограмм, значение регистра ссылок (LR) само по себе может не обновляться во времени, чтобы использоваться в цикле 2101, когда команда возврата подпрограммы находится на этапе DCD, и пытается осуществить предсказание. Как показано на схеме, LR не обновляется до тех пор, пока циклу 210М, который находится на четыре цикла позже, не потребуется использовать это значение на этапе DCD. Цикл 210М по ссылке 235 существует после цикла 210I, где выполняется предсказание и извлечения адреса перехода возврата. Таким образом, в традиционных процессорах предсказание перехода по команде возврата перехода, сохраняемой в регистре ссылок, может быть ненадежным.

Фиг.3-5 иллюстрируют альтернативные аспекты изобретения, связанные с этапом декодирования конвейера, например этап 106 декодирования конвейером. Эти альтернативные аспекты обращаются к маршрутам для записи структуры состояния ссылок как для неявного вызова подпрограммы, так и для традиционной команды перехода и ссылки. Следует заметить, что другие маршруты включены в этап декодирования конвейера, например маршруты других команд в наборе команд, но не обладающие этим аспектом настоящего изобретения и таким образом не отображенные в чертежах.

Фиг.3 является примерной частью 300 этапа декодирования конвейером единственной команды. Часть 300 этапа декодирования конвейером единственной команды может быть соответствующим образом размещена на этапе 106 декодирования. Часть 300 этапа декодирования конвейером единственной команды включает в себя адрес 310 команды и биты 315 предварительного декодирования, ассоциированные с адресом 310 команды. Размер адреса 310 команды равен 32 битам, и размер битов 315 предварительного декодирования равен 8 битам. Следует заметить, что аспекты настоящего изобретения предполагают различные размеры адреса команды или битов предварительного декодирования и их соответствующие позиции битов. Адрес 310 команды и биты 315 предварительного декодирования вводятся в часть 300 этапа декодирования конвейером и могут постоянно находиться в тех же самых и различных регистрах данных.

Биты 315 предварительного декодирования включают в себя информацию, относящуюся к команде, соответствующей адресу 310 команды, и определяются логической схемой 128 предварительного декодирования. Биты 315 предварительного декодирования указывают, является ли соответствующая команда началом неявного вызова подпрограммы, например команда MOV LR, PC в комбинации MOV/BR, перечисленной в таблице 1. Биты 315 предварительного декодирования могут быть закодированы различными способами, включая кодирование конкретного бита или комбинации битов 315 предварительного декодирования, чтобы указать, что адрес 310 команды ссылается либо на начало неявного вызова подпрограммы, либо на традиционную команду перехода и ссылки. В другом варианте осуществления код операции (opcode) команды может использоваться для проведения различения неявного вызова подпрограммы и традиционной команды перехода и ссылки от других команд в наборе команд.

Часть 300 этапа декодирования конвейером дополнительно включает в себя комбинацию 330 сумматор/мультиплексор. Комбинация 330 сумматор/мультиплексор включает в себя сумматоры 325A-325B, мультиплексор 320 и структуру 134 стека ссылок. Сумматор 325А добавляет постоянную «четыре» к адресу команды в случае, если адрес 310 команды ссылается на традиционную команду перехода и ссылки. Сумматор 325В добавляет постоянную «восемь» к адресу команды в случае, если адрес 310 команды ссылается на начало неявного вызова подпрограммы. С помощью мультиплексора 320 биты 315 предварительного декодирования выбирают, какой получивший приращение адрес или адрес возврата записывается в труктуру 134 стека ссылок, если есть такие. Ссылаясь на таблицу 1, смещение «восемь» проиллюстрировано, чтобы отразить, что местоположение адреса возврата равно восьми байтам после команды MOV. В традиционной команде перехода и ссылки адрес возврата равен четырем байтам после команды перехода и ссылки. Хотя не показано, другие сумматоры могут быть добавлены или могут заменить проиллюстрированные сумматоры на фиг.3-5 в зависимости от числа команд, составляющих неявный вызов подпрограммы, и размера каждой из команд, составляющих неявный вызов подпрограммы.

Фиг.4 является примерным первым аспектом части 400 этапа декодирования конвейером двух команд. Часть 400 этапа декодирования конвейером двух команд может быть соответствующим образом размещена на этапе 106 декодирования. Часть 400 этапа декодирования конвейером двух команд включает в себя два адреса 410A-410B команды, принимаемые одновременно с их соответствующими битами 407A-B предварительного декодирования и два набора комбинаций 425A-425B сумматор/мультиплексор. Адреса 410A-410B команды и биты 407A-B предварительного декодирования вводятся в часть 400 этапа декодирования конвейером и могут постоянно находиться в тех же самых и различных регистрах данных.

Начало неявного вызова подпрограммы, например адрес для команды MOV LR, PC, может быть найдено в любом адресе 410A или 410B команды. По соглашению адрес 410A команды или DCD0 является первым в порядке программы и адрес команды 410B или DCDj является вторым в порядке программы. Когда адрес для команды, определяющий начало неявного вызова подпрограммы, например адрес для команды MOV LR, PC расположен в адресе 410A команды, вывод сумматор/мультиплексор 425А является достоверным и этот увеличенный адрес записывается в структуру 134 стека ссылок. Если адрес для начала неявной подпрограммы является адресом 410В команды, вывод сумматора/мультиплексора 425B является достоверным, и этот увеличенный адрес или адрес возврата записывается в структуру 134 стека ссылок. Когда распознается неявная подпрограмма, аспекты этапа декодирования конвейером, проиллюстрированные на фиг.3 и 4, записывают в структуру 134 стека ссылок в начале команду, определяющую неявную подпрограмму.

Фиг.5 является примерным вторым аспектом части 500 этапа декодирования конвейером двух команд. Часть 500 этапа декодирования конвейером двух команд может быть соответствующим образом размещена на этапе 106 декодирования. Часть 500 этапа декодирования конвейером двух команд записывает адрес возврата в структуру 134 стека ссылок в ответ на прием адреса последней команды, определяющей неявный вызов подпрограммы. Возвращаясь к фиг.2, для примера, структура 213 состояния ссылок записывается по ссылке 221 с помощью части 500 этапа декодирования конвейером двух команд, в один цикл после декодирования команды перехода комбинации MOV/BR. Следовательно, как проиллюстрировано, значение BR+4 записывается в структуру 213 состояния ссылок по ссылке 221.

Часть 500 этапа декодирования конвейером двух команд включает в себя адреса 510A-510B двух команд, принятых одновременно с их соответствующими битами 507A-B предварительного декодирования. Адреса 510A-510B (DCD0 и DCD1) команд и их соответствующие биты 507A-B (PDCD0 и PDCD1) предварительного декодирования вводятся в части 500 этапа декодирования конвейером и могут постоянно находиться в тех же самых и различных регистрах данных.

Часть 500 этапа декодирования конвейером дополнительно включает в себя логическую схему 510 выбора/разрешения, логическую схему 515 установки флага, сумматоры 525A и 525B и мультиплексор 520. Логическая схема 515 установки флага устанавливает и возвращает в исходное состояние флаг 530. Флаг 530 отслеживает, распознано ли начало неявного вызова подпрограммы либо по адресу 510А, либо по адресу 510В. Флаг 530 не используется, если оба адреса, указывающие начало и окончание неявного вызова подпрограммы, принимаются параллельно. В случае неявного вызова подпрограммы, определяемого комбинацией MOV LR, PC/BR, логическая схема 515 установки флага, использующая биты PDCD0 и PDCD1, устанавливает флаг 530, когда адрес команды MOV LR, PC постоянно находится в области памяти окончательного достоверного декодирования, который может быть либо DCD0 (когда DCD1 недостоверен), либо DCD1.

Логическая схема 510 выбора/разрешения определяет, содержит ли DCD0 или DCD1 адрес окончания неявного вызова подпрограммы. Если окончание неявного вызова подпрограммы находится в DCD0, сумматор 525A добавляет «четыре» к адресу в DCD0, чтобы вычислить адрес возврата для неявного вызова подпрограммы. Если окончание неявного вызова подпрограммы находится в DCD1, сумматор 525В добавляет «четыре» к адресу в DCD1, чтобы вычислить адрес возврата. Логическая схема 510 выбора/разрешения формирует сигнал 540 выбора, если окончание неявного вызова подпрограммы присутствует в DCD0 или DCD1, и, если так, выбирает, какой получивший приращение адрес 535A или 535B команды должен быть записан в структуру 134 стека ссылок.

Для того чтобы гарантировать, что структура 134 стека ссылок не записывается без необходимости, логическая схема 510 выбора/разрешения принимает в качестве ввода принятые предсказанные сигналы 550A и 550B, соответствующие адресам DCD0 и DCD1 команд соответственно от схемы 132 предсказания перехода. Если неявный вызов подпрограммы распознан в регистре 505 данных и неявная подпрограмма принята как предсказанная схемой 132 предсказания перехода, логическая схема 510 выбора/разрешения формирует сигнал 545 разрешения записи в структуру 134 стека ссылок, чтобы разрешить ее запись. Если неявный вызов подпрограммы распознан, но не принят как предсказанный, логическая схема 510 выбора/разрешения не формирует разрешения записи в структуру 134 стека ссылок. Таким образом, неявные вызовы подпрограммы, которые не приняты, как предсказанные, не приводят к записи в структуру 134 стека ссылок. Следует заметить, что хотя настоящее изобретение описывает распознавание неявного вызова подпрограммы и запись в структуру стека ссылок на этапе декодирования конвейера, специалисту в данной области техники должно быть понятно, что эти аспекты изобретения могут быть осуществлены на практике на любом этапе конвейера обработки, где биты предварительного декодирования уже были определены, и предсказание перехода уже было выполнено.

Фиг.6 является блок-схемой, которая иллюстрирует способ 600 моделирования поведения предсказания перехода явной подпрограммы, когда распознается неявный вызов подпрограммы. В блоке 610 адрес команды, указывающей неявный вызов подпрограммы для подпрограммы, определяется в конвейере обработки. В блоке 620 вычисляется адрес возврата из адреса команды. Если неявный вызов подпрограммы содержит две или более команд, величина смещения, добавляемая к адресу команды, зависит от различных факторов, включая в себя то, выполняется ли распознавание в начале или окончании неявного вызова подпрограммы, и размер команд, составляющих неявный вызов подпрограммы. В блоке 630 адрес возврата сохраняется в ресурсе явной подпрограммы, например структуре 134 стека ссылок. Как описано на фиг.3-5, блоки 610, 620 и 630 могут иметь место во время этапа 106 декодирования.

В блоке 640 конвейер обработки обрабатывает команды, ассоциированные с вызываемой подпрограммой. Например, ссылаясь на таблицу 1, в блоке 640 могут обрабатываться адреса 0x00990000-0x00990008 команд. В блоке 650 адрес возврата считывается из ресурса явной подпрограммы в ответ на команду перехода, указывающую вызов возврата из подпрограммы, например, 0x00990008 BX в таблице 1. Дополнительно, в блоке 650 конвейер обработки перенаправляется в адрес возврата, считываемый из ресурса явной подпрограммы. В то время как команда ответного вызова находится на этапе 106 декодирования, адрес возврата извлекается из структуры 134 стека ссылок таким же образом, как когда адрес возврата извлекается в ответ на вызов возврата для подпрограммы, вызываемой традиционной командой перехода и ссылки. Если адрес возврата извлечен и команда вызова возврата принята как предсказанная, адрес возврата извлекается конвейером обработки, преимущественно разрешая более раннее извлечение адреса возврата, как проиллюстрировано на фиг.2.

Фиг.7 является блок-схемой последовательности операций способа, которая показывает дополнительные подробности блоков 610, 620 и 630 на фиг.6. В блоке 710 считывается бит предварительного декодирования, ассоциированный с адресом команды. В блоке 720 блок-схема 700 последовательности операций способа определяет, указывает ли бит предварительного декодирования неявный вызов подпрограммы. Если это так, блок 730 добавляет смещение к адресу команды. В блоке 740 увеличенный адрес сохраняется в структуре стека ссылок. В блоке 750 конвейерная обработка продолжает обработку команд традиционным образом. Если биты предварительного декодирования не указывают неявный вызов подпрограммы, блок 720 переходит к блоку 750, где конвейер обработки продолжает обработку команд традиционным образом.

Различные пояснительные логические блоки, модули, схемы, элементы и/или компоненты, описанные в связи с вариантами осуществления, раскрытыми в материалах настоящей заявки, могут быть реализованы или выполнены с помощью процессора общего назначения, цифрового сигнального процессора (DSP), специализированной интегральной микросхемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического компонента, дискретной вентильной или транзисторной логики, дискретных компонентов аппаратных средств или любого их сочетания, спроектированных для выполнения функций, описанных в материалах настоящей заявки. Процессором общего назначения может быть микропроцессор, но в альтернативном варианте процессором может быть любой типовой процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть также реализован как сочетание вычислительных компонентов, например объединение DSP и микропроцессора, множества микропроцессоров, одного или более микропроцессоров совместно с ядром DSP или любая другая подобная конфигурация.

Способы, описанные применительно к раскрытым в данном документе вариантам осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, исполняемом процессором, или в их сочетании. Программный модуль может постоянно находиться в оперативной памяти, флэш-памяти, ПЗУ, памяти типа EPROM, памяти типа EEPROM, регистрах, на жестком диске, сменном диске, компакт-диске или любой другой форме носителя хранения данных, известной в данной области техники. Носитель хранения данных может быть соединен с процессором, чтобы процессор мог считывать информацию с носителя хранения данных и записывать информацию на него. В альтернативе носитель хранения данных может быть интегрирован в процессор.

Хотя изобретение раскрыто в контексте вариантов осуществления, понятно, что специалистами в данной области техники может применяться широкое разнообразие реализаций, совместимых с вышеизложенным описанием и формулой изобретения, приведенной ниже.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИМИЗИРОВАННАЯ ДЛЯ ПОТОКОВ МНОГОПРОЦЕССОРНАЯ АРХИТЕКТУРА | 2007 |

|

RU2427895C2 |

| ОБРАБОТКА ОШИБОК ПРЕДВАРИТЕЛЬНОГО ДЕКОДИРОВАНИЯ ЧЕРЕЗ КОРРЕКЦИЮ ВЕТВЛЕНИЙ | 2005 |

|

RU2367004C2 |

| МУЛЬТИПРОЦЕССОРНАЯ АРХИТЕКТУРА, ОПТИМИЗИРОВАННАЯ ДЛЯ ПОТОКОВ | 2008 |

|

RU2450339C2 |

| СИСТЕМЫ И СПОСОБЫ ПРОВЕРКИ АДРЕСА ВОЗВРАТА ПРОЦЕДУРЫ | 2014 |

|

RU2628163C2 |

| СХЕМА ОТЛАДКИ, СРАВНИВАЮЩАЯ РЕЖИМ ОБРАБОТКИ НАБОРА КОМАНД ПРОЦЕССОРА | 2007 |

|

RU2429525C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| КОМАНДЫ ЗАГРУЗКИ/ПЕРЕМЕЩЕНИЯ И КОПИРОВАНИЯ ДЛЯ ПРОЦЕССОРА | 2002 |

|

RU2292581C2 |

| АКТИВНЫЙ АППАРАТНЫЙ СТЕК ПРОЦЕССОРА | 2013 |

|

RU2530285C1 |

| ПРЕДСТАВЛЕНИЕ ПЕРЕХОДОВ ЦИКЛА В РЕГИСТРЕ ПРЕДЫСТОРИИ ПЕРЕХОДОВ С ПОМОЩЬЮ МНОЖЕСТВА БИТ | 2007 |

|

RU2447486C2 |

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ВЫПОЛНЕНИЕМ ВНУТРИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2012 |

|

RU2577487C2 |

Изобретение относится к устройствам для моделирования поведения предсказания переходов явного вызова подпрограммы. Технический результат заключается в моделировании предсказания переходов вызова подпрограмм, чтобы уменьшить мощность и повысить коэффициент использования конвейерного процессора. Устройство включает в себя первый вход, который конфигурирован для приема адреса команды, и второй вход, конфигурированный для приема предварительно декодированной информации, которая описывает адрес команды, как связанной с неявным вызовом подпрограммы в подпрограмме. В ответ на предварительно декодированную информацию устройство также включает в себя сумматор, сконфигурированный для добавления константы к адресу команды, определяя адрес возврата, что влечет сохранение адреса возврата в ресурс явной подпрограммы, таким образом облегчая последующее предсказание перехода команды вызова возврата. 2 н. и 11 з.п. ф-лы, 1 табл., 7 ил.

1. Устройство моделирования поведения предсказания переходов явного вызова подпрограммы, которое содержит:

первый и второй входы, сконфигурированные для одновременного приема адресов первой и второй команды и ассоциированной информации предварительного декодирования;

первый набор сумматоров, сконфигурированных для добавления смещения к адресам первой и второй команды, чтобы определить первый и второй результаты в ответ на информацию предварительного декодирования, указывающую, что адрес первой или второй команды ассоциирован с неявным вызовом подпрограммы для подпрограммы;

средство для выбора адреса возврата из одного из первого или второго результатов.

2. Устройство по п.1, дополнительно содержащее средство для записи адреса возврата в ресурс явной подпрограммы.

3. Устройство по п.1, дополнительно содержащее логическую схему установки флага, сконфигурированную для отслеживания, ассоциированы ли адреса, первой или второй команды с неявным вызовом подпрограммы.

4. Устройство по п.1, дополнительно содержащее второй набор сумматоров для добавления второго смещения к адресам первой и второй команд в ответ на информацию предварительного декодирования, указывающую, что адрес первой или второй команды ассоциирован с явным вызовом подпрограммы для подпрограммы.

5. Устройство по п.4, в котором смещение равно восьми и второе смещение равно четырем.

6. Устройство по п.1, в котором информация предварительного декодирования кодируется как комбинация битов для указания того, относится ли адрес первой или второй команды к неявному вызову подпрограммы для подпрограммы.

7. Устройство по п.3, в котором средство для выбора адреса возврата из одного из первого или второго результатов дополнительно содержит логическую схему выбора/разрешения, сконфигурированную для разрешения явного ресурса подпрограммы для записи.

8. Устройство моделирования поведения предсказания переходов явного вызова подпрограммы, которое содержит:

первый вход, сконфигурированный для приема адреса команды;

второй вход, сконфигурированный для приема информации предварительного декодирования, причем информация предварительного декодирования описывает адрес команды как ассоциируемый с неявным вызовом подпрограммы для подпрограммы;

сумматор, сконфигурированный для добавления смещения к адресу команды, определяющего первый адрес возврата в ответ на информацию предварительного декодирования;

третий вход для одновременного приема адреса второй команды с адресом команды;

второй сумматор, сконфигурированный для добавления смещения к адресу второй команды, определяющего второй адрес возврата; и

логику, сконфигурированную для определения, маршрутизировать ли первый адрес возврата или второй адрес возврата к ресурсу явной подпрограммы.

9. Устройство по п.8, в котором второй сумматор дополнительно сконфигурирован для добавления второго постоянного смещения к адресу команды в ответ на явный вызов подпрограммы.

10. Устройство по п.8, в котором ресурс явной подпрограммы считывается в ответ на команду перехода, указывающую вызов возврата из подпрограммы.

11. Устройство по п.8, в котором информация предварительного декодирования дополнительно описывает адрес команды, как начало неявного вызова подпрограммы.

12. Устройство по п.8, в котором информация предварительного декодирования дополнительно описывает адрес команды, как конец неявного вызова подпрограммы.

13. Устройство по п.8, в котором ресурс явной подпрограммы является структурой стека связи.

| US 6889320 B1, 03.05.2005 | |||

| WO 00/04444 A, 27.01.2000 | |||

| US 5964869, 12.10.1999 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| СПОСОБ РАЗРЕШЕНИЯ КОНФЛИКТОВ ПО АДРЕСНОМУ ПРОСТРАНСТВУ МЕЖДУ МОНИТОРОМ ВИРТУАЛЬНЫХ МАШИН И ГОСТЕВОЙ ОПЕРАЦИОННОЙ СИСТЕМОЙ | 2001 |

|

RU2259582C2 |

Авторы

Даты

2011-04-27—Публикация

2007-08-31—Подача