Уровень техники

Настоящее изобретение относится к способу управления компонентом важной для обеспечения безопасности распределенной системы, прежде всего компонентом системы типа "X-by-Wire", используемой в транспортном средстве. При этом управление этим компонентом осуществляется с помощью относящегося к нему первого управляющего модуля по меньшей мере с одной первой микропроцессорной системой. Собственно управление таким компонентом заключается в том, что

а) с помощью первой микропроцессорной системы в зависимости по меньшей мере от одного входного сигнала формируют по меньшей мере один управляющий сигнал для этого компонента,

б) формируют по меньшей мере один логический управляющий сигнал, при этом такой по меньшей мере один логический управляющий сигнал по меньшей мере частично формируется не зависимым от первой микропроцессорной системы контрольным блоком в зависимости от указанного по меньшей мере одного входного сигнала,

в) этот по меньшей мере один управляющий сигнал сравнивают с указанным по меньшей мере одним логическим управляющим сигналом,

г) в зависимости от результата такого сравнения формируют по меньшей мере один разрешающий сигнал и

д) указанный по меньшей мере один управляющий сигнал или по меньшей мере один зависящий от него сигнал в том случае, если по меньшей мере один разрешающий сигнал соответствует заданному значению, передают в компонент.

Настоящее изобретение относится, кроме того, к компьютерной программе, ориентированной на ее выполнение первой микропроцессорной системой управляющего модуля. Такой управляющий модуль предназначен для управления компонентом важной для обеспечения безопасности распределенной системы, прежде всего компонентом системы типа "X-by-Wire", используемой в транспортном средстве.

Способ указанного в начале описания типа известен, например, из заявки DE 19826131 А1. В этой публикации описана важная для обеспечения безопасности распределенная система, которая представляет собой тормозную систему с электроприводом, устанавливаемую на транспортном средстве. При этом компонентами такой системы являются тормозные механизмы транспортного средства или, точнее говоря, исполнительные механизмы, управляющие этими тормозными механизмами. Подобная система является исключительно важной для обеспечения безопасности, поскольку ошибка в управлении ее компонентами, прежде всего ложное или ошибочное срабатывание тормозных механизмов, может привести к непредсказуемым самым тяжелым последствиям. По этой причине возможность ошибок в управлении компонентами этой системы должна быть с высокой степенью надежности исключена.

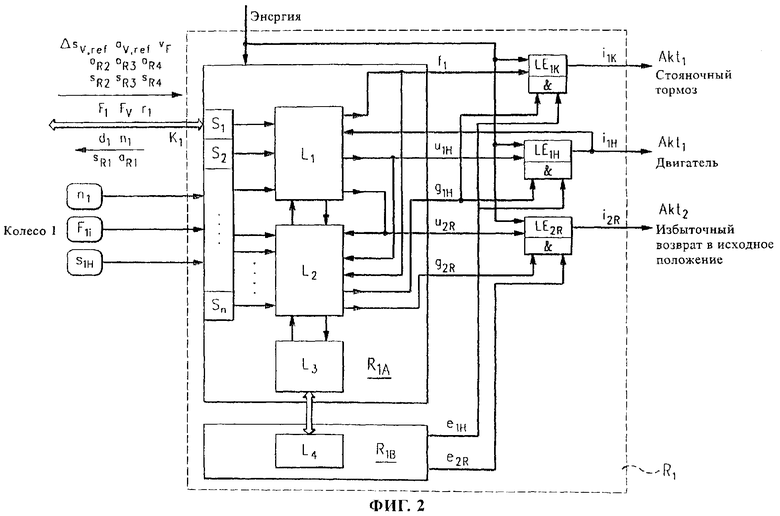

Основной характерной особенностью известной тормозной системы является наличие в ней связанного с педалью тормоза модуля для централизованной регистрации задаваемого водителем воздействия при нажатии на педаль тормоза, четыре управляющих торможением колеса модуля для индивидуального для каждого колеса управления тормозными приводами или исполнительными механизмами тормозных механизмов и модуль обработки для выполнения различных операций по вычислению параметров иных относящихся к тормозной системе функций более высокого уровня. Обмен данными между отдельными такими модулями может осуществляться по одной или нескольким системам связи или передачи данных. На приложенной к настоящему описанию фиг.2 в качестве примера показана внутренняя структура управляющего торможением колеса модуля с различными относящимися к нему логическими уровнями. При этом на логическом уровне L1 выполняются по меньшей мере вычисления параметров управляющих и регулирующих функций, относящихся к колесным тормозным механизмам, тогда как к логическим уровням L2-L4 относятся различные функции, связанные с контролем за функционированием процессора и за работой функций, относящихся к уровню L1.

Процесс управления тормозными механизмами, соответственно электродвигателями, обеспечивающими срабатывание тормозных колодок, состоит для каждого из управляющих торможением колеса модулей в выполнении следующих стадий:

а) формирование первой микропроцессорной системой R1A в зависимости по меньшей мере от одного входного сигнала аR2, аR3, аR4, aV,ref, sR2, sR3, sR4, ΔsV,ref, vF, n1, F1i, s1H по меньшей мере одного управляющего сигнала f1 для тормозного механизма, при этом указанные входные сигналы поступают в микропроцессорную систему R1A по системе связи K1, например по шинной системе,

б) формирование по меньшей мере одного логического управляющего сигнала е1H, при этом такой логический управляющий сигнал е1H по меньшей мере частично формируется не зависимым от первой микропроцессорной системы R1A контрольным блоком R1B в зависимости от указанного по меньшей мере одного входного сигнала,

в) сравнение этого по меньшей мере одного управляющего сигнала f1 по меньшей мере с одним логическим управляющим сигналом е1H в силовом электронном устройстве LE1K,

г) формирование по меньшей мере одного разрешающего сигнала (силовыми электронными устройствами LE) в зависимости от результата, полученного при сравнении управляющего сигнала f1 и логического управляющего сигнала е1H, и

д) подачу этого по меньшей мере одного управляющего сигнала f1 или зависящего от него управляющего сигнала i1K на тормозной механизм, соответственно на исполнительный механизм Akt1, обеспечивающий срабатывание тормозных колодок, при условии, что указанный по меньшей мере один разрешающий сигнал соответствует некоторому заданному значению.

Контрольный блок R1B предназначен прежде всего для обнаружения систематических ошибок (так называемых отказов общего характера). Примером подобного рода ошибок могут служить сбои или перебои в электропитании. В известной тормозной системе контрольный блок R1B выполнен в виде самостоятельной микропроцессорной системы. В другом варианте, однако, этот контрольный блок R1B может быть выполнен в виде аппаратного блока, не имеющего собственного процессора, но способного выполнять конкретные логические функции или, при наличии у него регистра, даже переключательные функции (функции комбинационной логики). В качестве примера подобных аппаратных блоков можно назвать специализированную интегральную схему (СИС), программируемую пользователем вентильную матрицу (ППВМ) или контрольную схему (так называемую "сторожевую" схему).

Недостаток известной из уровня техники системы состоит в том, что логический уровень L4 всегда реализован в виде отдельного блока, и поэтому в важной для обеспечения безопасности распределенной системе, например в управляющих торможением колеса модулях тормозной системы с электроприводом, необходимо помимо всего прочего предусматривать по несколько таких блоков.

В основу настоящего изобретения была положена задача упростить структуру важной для обеспечения безопасности распределенной системы, одновременно повысив или по меньшей мере сохранив обеспечиваемую такой системой степень надежности срабатывания ее компонентов.

В отношении способа указанного в начале описания типа эта задача решается согласно изобретению за счет того, что важная для обеспечения безопасности система помимо первой микропроцессорной системы имеет по меньшей мере еще одну микропроцессорную систему, которая соединена с первой микропроцессорной системой для обмена с ней данными, при этом по меньшей мере одну из вышеуказанных стадий б)-г) осуществляют по меньшей мере в одной из этих дополнительных микропроцессорных систем.

Преимущества изобретения

Согласно изобретению, таким образом, предлагается отказаться от использования отдельного контрольного блока, передав выполнение его функций тем блокам и устройствам важной для обеспечения безопасности распределенной системы, которые в любом случае входят в ее состав. Подобные блоки и устройства должны, чтобы они могли по меньшей мере в ограниченном объеме самостоятельно производить необходимые вычисления, обладать собственной развитой логикой (встроенными вычислительными средствами). Такими блоками или устройствами системы, которые согласно изобретению могут взять на себя выполнение функций контрольного блока, являются прежде всего микропроцессоры одной или нескольких дополнительных микропроцессорных систем.

Микропроцессором первой микропроцессорной системы выполняется некоторый программный код, с помощью которого в зависимости от входных сигналов формируется управляющий сигнал для соответствующего компонента распределенной системы. Такой программный код выполняется, кроме того, по меньшей мере одной из дополнительных микропроцессорных систем с целью формирования логического управляющего сигнала для этого компонента распределенной системы в зависимости от этих же входных сигналов. В этом случае подобный программный код может выполняться в дополнительных микропроцессорных системах, например, их микропроцессорами или другими пригодными для этой цели блоками и устройствами (например, связными контроллерами), обладающими достаточно развитой для выполнения программного кода логикой. Входные сигналы поступают в эти дополнительные микропроцессорные системы, например, по шине данных, которой эти микропроцессорные системы соединены между собой для передачи между ними данных.

Сформированный первой микропроцессорной системой управляющий сигнал с целью проверить, является ли он ложным, соответственно ошибочным или нет, сравнивается с логическими управляющими сигналами. Если формируемые всеми микропроцессорными системами управляющие сигналы, соответственно логические управляющие сигналы соответствуют друг другу, то управляющий сигнал можно расценивать как корректный. Очевидно, что с увеличением количества дополнительных микропроцессорных систем, каждая из которых формирует соответствующие логические управляющие сигналы, надежность контроля за работоспособностью первой микропроцессорной системы повышается. При совместной работе нескольких микропроцессорных систем, взаимно контролирующих работоспособность друг друга, при определенных условиях появляется даже возможность идентифицировать, соответственно локализовать, дефектную микропроцессорную систему.

Согласно одному из предпочтительных вариантов осуществления изобретения важная для обеспечения безопасности система помимо первого управляющего модуля имеет по меньшей мере еще один управляющий модуль, при этом по меньшей мере одна дополнительная микропроцессорная система входит в состав этого по меньшей мере одного дополнительного управляющего модуля. В соответствии с этим вариантом важная для обеспечения безопасности распределенная система имеет, таким образом, несколько однотипных управляющих модулей, в состав которых входят первая микропроцессорная система и дополнительные микропроцессорные системы. Преимущество этого варианта состоит в том, что управляющие модули обычно выполняют идентичные функции (например, приводят в действие или отпускают колесный тормозной механизм в зависимости от определенных входных сигналов), а программные коды, выполняемые их микропроцессорными системами для формирования управляющих сигналов, большей частью совпадают между собой. Иными словами, когда эти дополнительные микропроцессорные системы дополнительных управляющих модулей берут на себя выполнение функций контрольного блока, в них для формирования логических управляющих сигналов не требуется загружать и при необходимости выполнять отдельный программный код. Более того, с этой целью можно использовать в любом случае имеющийся в этих дополнительных микропроцессорных системах программный код, при выполнении которого, однако, обрабатываются входные сигналы, поступающие в первую микропроцессорную систему. Примером распределенной системы, позволяющей реализовать этот вариант осуществления предлагаемого в изобретении способа, служит тормозная система с электроприводом, в которой для всех колес транспортного средства предусмотрены практически идентичные управляющие торможением колеса модули. Таким образом, в этом варианте часто имеющаяся в распределенных системах избыточность позволяет снизить затраты на повышение надежности управления компонентами такой системы.

В соответствии с другим предпочтительным вариантом осуществления изобретения указанные выше стадию б) и стадию в) предлагается осуществлять по меньшей мере в одной из дополнительных микропроцессорных систем. Согласно этому варианту, таким образом, управляющий сигнал сравнивается с логическими управляющими сигналами по меньшей мере в одной из дополнительных микропроцессорных систем. При этом сформированный первой микропроцессорной системой управляющий сигнал необходимо передавать в эту по меньшей мере одну дополнительную микропроцессорную систему, например по шине данных, соединяющей между собой обе эти микропроцессорные системы.

Согласно следующему предпочтительному варианту первая микропроцессорная система через первый связной контроллер подсоединена к физической шинной системе, при этом вышеуказанную стадию б) осуществляют по меньшей мере в одной из дополнительных микропроцессорных систем, а стадию в) осуществляют в этом первом связном контроллере. В соответствии с этим вариантом, таким образом, управляющий сигнал сравнивается с логическими управляющими сигналами в первом связном контроллере, через который первая микропроцессорная система подсоединена к шинной системе. Следует отметить, что связные контроллеры разработанных сравнительно недавно шинных систем, таких, например, как системы TTCAN (Time Triggered Controller Area Network), TTP/C (Time Triggered Protocol Class С согласно SAE) или FlexRay, не просто служат "бездумными" интерфейсами между микропроцессорной системой и шиной данных, а выполняют собственную, иногда достаточно сложную обработку передаваемых данных. С этой цели такие связные контроллеры оснащены собственной развитой логикой, которая позволяет выполнять по меньшей мере простые операции, такие, например, как сравнение, а при определенных условиях - и более сложные вычисления. Для выполнения операции сравнения в первом связном контроллере в него необходимо передавать по меньшей мере один логический управляющий сигнал по меньшей мере от одной дополнительной микропроцессорной системы, например по шине данных, соединяющей их между собой.

В соответствии с другим предпочтительным вариантом осуществления изобретения вышеуказанную стадию г) осуществляют по меньшей мере в одной из дополнительных микропроцессорных систем. Согласно этому варианту, таким образом, по меньшей мере один разрешающий сигнал формируется в дополнительных микропроцессорных системах в зависимости от полученного при сравнении управляющего сигнала с логическим управляющим сигналом результата. При этом сформированный первой микропроцессорной системой управляющий сигнал необходимо передавать в эти дополнительные микропроцессорные системы, например по шине данных. Этот управляющий сигнал сравнивается в таких дополнительных микропроцессорных системах со сформированными каждой из них логическими управляющими сигналами. Разрешающий сигнал в свою очередь передается, например по шине данных, в первую микропроцессорную систему. После этого в случае, если сформированные дополнительными микропроцессорными системами разрешающие сигналы соответствуют некоторым заданным значениям, этот по меньшей мере один управляющий сигнал или по меньшей мере один зависящий от него сигнал выдается на управляемый компонент распределенной системы. При этом разрешающие сигналы можно, например, подвергать простому сравнению или же выбирать соответствующий разрешающий сигнал с использованием процедуры принятия мажоритарного решения.

Согласно другому варианту осуществления изобретения первая микропроцессорная система через первый связной контроллер подсоединена к физической шинной системе, при этом вышеуказанную стадию г) осуществляют в этом первом связном контроллере. Сказанное означает, что сформированные в дополнительных микропроцессорных системах логические управляющие сигналы необходимо передавать, например по шине данных, в первый связной контроллер.

Особое значение имеет реализация предлагаемого в изобретении способа в виде компьютерной программы, ориентированной на ее выполнение микропроцессорной системой управляющего модуля, который предназначен для управления компонентом важной для обеспечения безопасности распределенной системы. При этом такая компьютерная программа ориентирована на ее выполнение микропроцессором этой микропроцессорной системы и пригодна для осуществления предлагаемого в изобретении способа. В этом случае предлагаемое в изобретении решение реализуется, таким образом, посредством компьютерной программы, которая тем самым также является объектом изобретения, как и способ, для осуществления которого она предназначена.

Согласно одному из предпочтительных вариантов осуществления изобретения предлагаемая в нем компьютерная программа хранится в запоминающем элементе, прежде всего во флэш-памяти. Для выполнения такой компьютерной программы, соответственно для осуществления предлагаемого в изобретении способа, эта компьютерная программа покомандно или целиком передается из запоминающего элемента в процессор.

Подобная компьютерная программа служит прежде всего для координации обмена данными между различными блоками и устройствами распределенной системы, обеспечивая таким путем осуществление предлагаемого в изобретении способа. То, какие конкретно данные должны передаваться и в какие именно блоки и устройства, зависит прежде всего от того, какими блоками и устройствами выполняются вышеуказанные стадии б)-д). Вместе с тем компьютерная программа обеспечивает также формирование управляющих сигналов и логических управляющих сигналов в различных блоках и устройствах системы и/или сравнение таких сигналов между собой.

Чертежи

Другие отличительные особенности, возможности применения и преимущества изобретения рассмотрены ниже на примере некоторых вариантов его осуществления со ссылкой на прилагаемые чертежи. При этом все рассмотренные в описании или представленные на чертежах отличительные признаки индивидуально и в любых сочетаниях характеризуют объект изобретения независимо от их компоновки в пунктах формулы изобретения или ссылки на эти пункты, а также независимо от их формулировки, соответственно представления в описании и на чертежах. При этом на прилагаемых к описанию чертежах, в частности, показано:

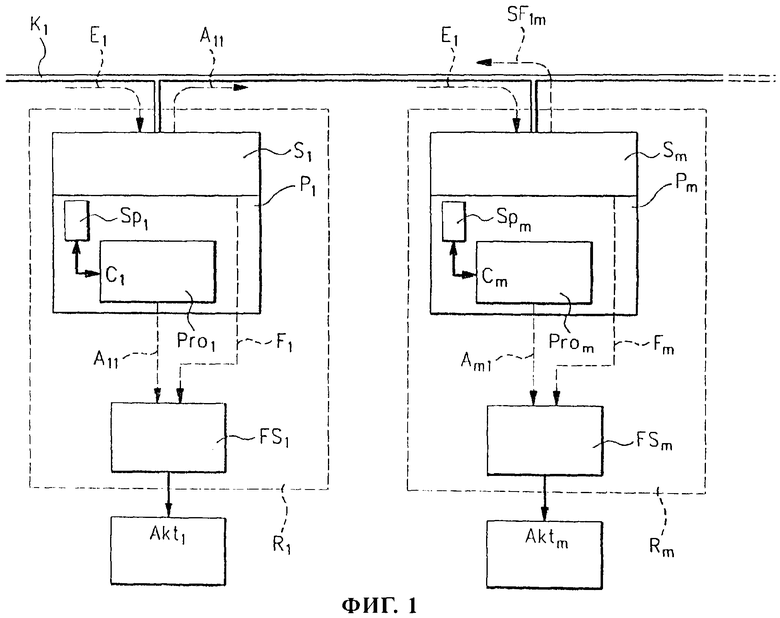

на фиг.1 - фрагмент важной для обеспечения безопасности распределенной системы, предназначенной для осуществления способа в соответствии с первым предпочтительным вариантом,

на фиг.2 - известный из уровня техники управляющий модуль важной для обеспечения безопасности распределенной системы,

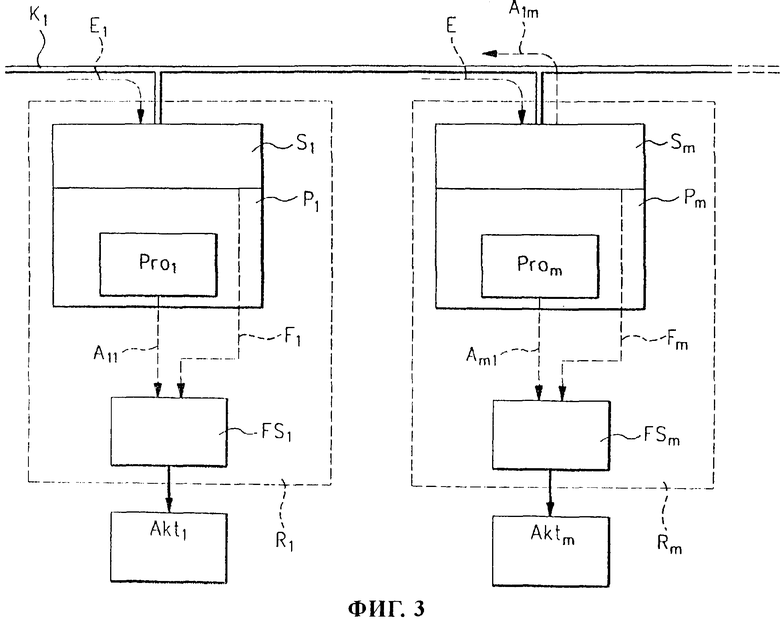

на фиг.3 - фрагмент важной для обеспечения безопасности распределенной системы, предназначенной для осуществления способа в соответствии со вторым предпочтительным вариантом, и

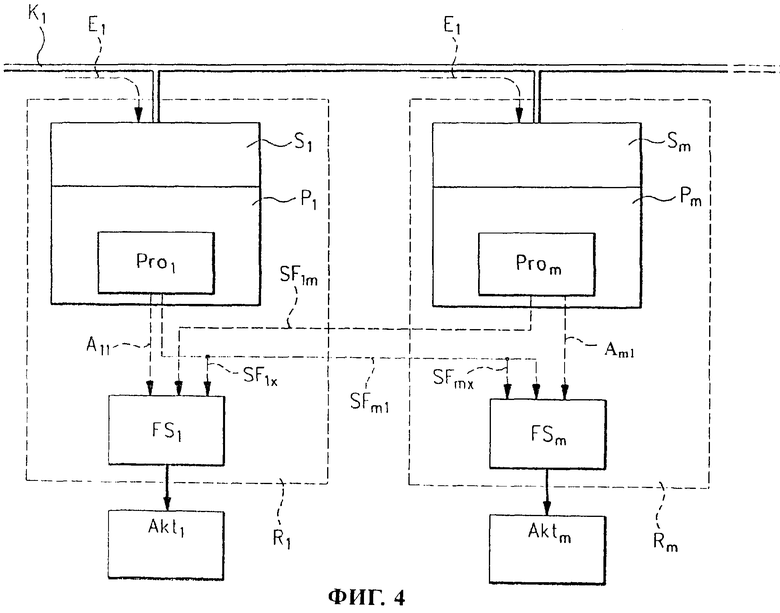

на фиг.4 - фрагмент важной для обеспечения безопасности распределенной системы, предназначенной для осуществления способа в соответствии с третьим предпочтительным вариантом.

Описание вариантов осуществления изобретения

Ниже предлагаемый в изобретении способ более подробно поясняется на примере тормозной системы с электроприводом. Однако предлагаемое в изобретении решение не ограничено его использованием только применительно к тормозным системам с электроприводом и, более того, может найти применение в любых, важных для обеспечения безопасности распределенных системах. Предлагаемое в изобретении решение обеспечивает надежное срабатывание компонентов важных для обеспечения безопасности распределенных систем без применения дополнительных контрольных блоков. Более того, выполнение функций подобных контрольных блоков берут на себя те блоки и устройства важной для обеспечения безопасности распределенной системы, которые в любом случае входят в ее состав.

Рассматриваемая тормозная система имеет по одному для каждого из затормаживаемых колес транспортного средства управляющему торможением колеса модулю R1, Rm. В состав каждого такого управляющего торможением колеса модуля R1, Rm входят микропроцессорная система P1, Рm и деблокирующая схема FS1, FSm (или схема формирования разрешающего сигнала). Каждая из микропроцессорных систем P1, Рm имеет по одному микропроцессору Pro1, Prom и по одному интеллектуальному связному контроллеру S1, Sm. Микропроцессор Pro1, Prom и связной контроллер S1, Sm микропроцессорной системы P1, Рm могут быть выполнены в виде единой полупроводниковой микросхемы (так называемого чипа), однако их, как правило, выполняют в виде отдельных, не зависимых друг от друга блоков или элементов. Каждый управляющий торможением колеса модуль R1, Rm через связной контроллер S1, Sm соединен с физической шиной K1 данных. Передача данных по этой шине данных осуществляется, например, в соответствии с протоколом TTCAN, ТТР/С или FlexRay. Каждый из управляющих торможением колеса модулей R1, Rm управляет работой соответствующего привода или исполнительного механизма Akt1, Aktm, выполненного, например, в виде электродвигателя, управляющего срабатыванием или отпусканием колесных тормозных механизмов.

На фиг.1 показаны внутренняя структура двух управляющих торможением колеса модулей и поток сигналов, которые согласно предлагаемому в изобретении способу поступают в эти модули и выдаются ими, в соответствии с первым предпочтительным вариантом осуществления изобретения. Такой способ предназначен для управления исполнительным механизмом Akt1 тормозной системы с электроприводом с помощью управляющего торможением колеса модуля R1, соответственно с помощью микропроцессорной системы Р1. При управлении исполнительным механизмом Akt1 важно предотвратить возможность срабатывания этого исполнительного механизма Akt1 по ложному или ошибочному управляющему сигналу от микропроцессорной системы P1. Иными словами, управляющий сигнал должен подаваться на исполнительный механизм Akt1 только в том случае, если с достаточно высокой степенью вероятности установлено, что этот сигнал не является ложным или ошибочным. В соответствии с этим процесс управления исполнительным механизмом Akt1 заключается в выполнении следующих основных стадий:

а) Процессор Pro1 микропроцессорной системы P1, выполняя программный код C1, формирует в зависимости по меньшей мере от одного входного сигнала E1 по меньшей мере один управляющий сигнал А11 для исполнительного механизма Akt1. Входные сигналы E1 содержат информацию о фактическом состоянии тормозной системы и всего транспортного средства в целом и поступают в первый управляющий торможением колеса модуль R1 по шине К1 данных.

б) Процессоры Prom (например, m=2...4) остальных микропроцессорных систем Рm, также выполняя программный код C1, формируют в зависимости от входных сигналов E1 соответствующий логический управляющий сигнал A1m. При этом предполагается, что в процессорах Prom помимо программного кода Cm, на основании которого формируются управляющие сигналы Am1 для исполнительных механизмов Aktm, дополнительно должен присутствовать также программный код C1. В рассматриваемом примере, предусматривающем использование нескольких однотипных управляющих торможением колеса модулей R1, Rm, обеспечение их таким программным кодом не связано или связано лишь с минимальными дополнительными затратами, поскольку выполняемые процессорами Pro1, Prom программные коды C1, Cm в основном идентичны. Таким образом, заложенный в любом случае в тот или иной процессор Prom программный код Cm может использоваться при его выполнении для формирования логических управляющих сигналов A1m на основании входных сигналов E1. Подобным же образом можно упростить любую распределенную систему, оснащенную однотипными управляющими модулями. Входные сигналы E1 могут передаваться в микропроцессорные системы Рm по шине K1 данных. При корректном функционировании микропроцессоров Pro1, Prom управляющие сигналы А11 и логические управляющие сигналы A1m должны быть идентичны между собой.

в) Управляющий сигнал А11 сравнивается в микропроцессорах Prom с ранее сформированными ими логическими управляющими сигналами A1m. С этой целью управляющий сигнал А11 необходимо передавать по шине K1 данных в микропроцессорные системы Рm. Микропроцессоры Prom формируют информацию SF1m о состоянии, которая в свою очередь также по шине K1 данных передается в первую микропроцессорную систему P1. Подобная информация о состоянии состоит, например, из одного или нескольких бит. Такую информацию SF1m, предназначенную для передачи в первую микропроцессорную систему P1, можно также включить в протокол передачи данных по шине данных.

г) Связной контроллер S1 первой микропроцессорной системы P1 анализирует или обрабатывает полученную информацию SF1m о состоянии и при наличии соответствующего состояния (т.е. при получении сигнала о корректном функционировании микропроцессора Pro1) формирует разрешающий сигнал F1. Указанную обработку информации SF1m о состоянии можно осуществлять различными путями. Так, например, подобная обработка может заключаться в выполнении над этой информацией SF1m о состоянии операции сравнения, логической операции (предпочтительно логической операции И) или в принятии мажоритарного решения (решения методом голосования).

д) В завершение указанный по меньшей мере один управляющий сигнал А11 или по меньшей мере один зависящий от него сигнал, если по меньшей мере один разрешающий сигнал F1 соответствует заданному значению, подается на исполнительный механизм Akt1. Для проверки этого условия над управляющим сигналом А11 в деблокирующей схеме FS1 выполняется логическая операция И. Если значение разрешающего сигнала F1 соответствует логической "1", то управляющий сигнал А11 выдается на исполнительный механизм Akt1. Если же значение разрешающего сигнала F1 соответствует логическому "0", то управляющий сигнал А11 не выдается на исполнительный механизм Akt1.

Предлагаемый в изобретении способ, который рассмотрен выше, позволяет контролировать работоспособность процессора Pro1 микропроцессорной системы P1 и обеспечить надежное срабатывание исполнительного механизма Akt1 только при наличии достоверного разрешающего сигнала. Для контроля работоспособности процессора Pro1 преимущественно используются процессоры Prom остальных микропроцессорных систем Рm. Однако предлагаемый в изобретении способ равным образом может использоваться для контроля работоспособности процессоров Prom других микропроцессорных систем P1 и обеспечения надежного срабатывания остальных исполнительных механизмов Aktm. В этом случае для подобного контроля задействуются остальные процессоры Prom (за исключением самого контролируемого процессора), а также процессор Pro1 первой микропроцессорной системы P1. Таким образом, каждая отдельная микропроцессорная система важной для обеспечения безопасности распределенной тормозной системы выполняет двойную функцию - основную, состоящую в формировании управляющих сигналов А11, Am1 для связанного с конкретной микропроцессорной системой исполнительного механизма Akt1, Aktm, и дополнительную, состоящую в контроле за работоспособностью остальных процессоров при выполнении ими их основных функций. Тем самым предлагаемое в изобретении решение позволяет без использования дополнительных контрольных блоков обеспечить надежное и даже обладающее некоторой избыточностью управление срабатыванием исполнительных механизмов Akt1, Aktm.

На фиг.3 показаны внутренняя структура двух управляющих торможением колеса модулей и поток сигналов, которые согласно предлагаемому в изобретении способу поступают в эти модули и выдаются ими, в соответствии со вторым предпочтительным вариантом осуществления изобретения. Отличие этого варианта от варианта, показанного на фиг.1, состоит прежде всего в том, что стадия в) выполняется в связном контроллере S1 первой микропроцессорной системы P1.

Логические управляющие сигналы A1m, сформированные на стадии б) процессорами Prom других микропроцессорных систем Рm, передаются по шине K1 данных в первую микропроцессорную систему P1. Затем в этой микропроцессорной системе P1 указанные логические управляющие сигналы A1m сравниваются в ее связном контроллере S1 по меньшей мере с одним управляющим сигналом А11 (стадия в)). В зависимости от полученного при таком сравнении результата в связном контроллере S1 формируется информация SI1m о состоянии, на основании которой затем формируется разрешающий сигнал F1, или же этот разрешающий сигнал F1 формируется сразу же без формирования информации о состоянии (стадия г)).

На фиг.4 показаны внутренняя структура двух управляющих торможением колеса модулей и поток сигналов, которые согласно предлагаемому в изобретении способу поступают в эти модули и выдаются ими, в соответствии с третьим предпочтительным вариантом осуществления изобретения. Отличие этого варианта от вариантов, показанных на фиг.1 и 3, состоит прежде всего в том, что стадия г) выполняется в деблокирующей схеме FS1 первого управляющего торможением колеса модуля R1.

На стадии в) управляющий сигнал А11 сравнивается в микропроцессорах Prom других микропроцессорных систем Rm с ранее сформированными этими микропроцессорными системами логическими управляющими сигналами A1m. Микропроцессоры Prom формируют информацию SF1m о состоянии, которая по шине K1 данных передается в первую микропроцессорную систему P1, а из нее в деблокирующую схему FS1. В этой схеме обрабатывается поступающая в нее от всех остальных микропроцессорных систем Рm информация о состоянии SF1m, SF1x и в том случае, когда такая информация о состоянии SF1m, SF1x указывает на наличие соответствующего состояния, указанной схемой на исполнительный механизм Akt1 выдается по меньшей мере один управляющий сигнал А11 или по меньшей мере один зависящий от него сигнал. В другом варианте в зависимости от полученного в деблокирующей схеме FS1 результата сравнения сначала формируется информация SI1m о состоянии, на основании которой затем формируется разрешающий сигнал F1. Для обработки информации о состоянии SF1m, SF1x в деблокирующей схеме FS1 используется так называемый механизм голосования. При наличии только двух управляющих сигналов А11, A12 этот механизм голосования сводится к выполнению над обоими этими управляющими сигналами А11 и SF1m логической операции И. При наличии же нескольких управляющих сигналов А11, A1m этот механизм голосования может заключаться в принятии мажоритарного решения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль центрального процессора промышленного контроллера | 2019 |

|

RU2703681C1 |

| Система управления грузопассажирским лифтом | 2022 |

|

RU2791781C1 |

| Способ предотвращения аварийных действий при оперативном управлении технологическим объектом | 2020 |

|

RU2758449C1 |

| ЭЛЕКТРОМЕХАНИЧЕСКАЯ ТРАНСМИССИЯ МАШИНЫ С ДВИГАТЕЛЕМ ВНУТРЕННЕГО СГОРАНИЯ | 2017 |

|

RU2648652C1 |

| ЭЛЕКТРОМЕХАНИЧЕСКАЯ ТРАНСМИССИЯ САМОХОДНОЙ МАШИНЫ | 2014 |

|

RU2550408C1 |

| ХВОСТОВОЕ УСТРОЙСТВО КОНТРОЛЯ ЦЕЛОСТНОСТИ ПОЕЗДА | 2021 |

|

RU2764478C1 |

| Система кодово-локационного позиционирования подвижного состава на разветвленных и неразветвленных рельсовых цепях | 2021 |

|

RU2801753C2 |

| СПОСОБ, СИСТЕМА И ЭЛЕКТРОННЫЙ БЛОК УПРАВЛЕНИЯ ДЛЯ ПРЕДОТВРАЩЕНИЯ СПУФИНГА В АВТОМОБИЛЬНОЙ СЕТИ | 2016 |

|

RU2712138C2 |

| СИСТЕМА ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ ТРАНСПОРТНОГО СРЕДСТВА | 2002 |

|

RU2209146C1 |

| СИСТЕМА УПРАВЛЕНИЯ ГРУЗОПОДЪЕМНЫМ КРАНОМ | 2000 |

|

RU2173665C1 |

Изобретение относится к технике обеспечения безопасности распределенной системы, прежде всего компонентом (Akt1) системы типа "X-by-Wire", используемой в транспортном средстве. Управление компонентом (Akt1) осуществляют с помощью относящегося к нему первого управляющего модуля (R1) по меньшей мере с одной первой микропроцессорной системой (P1). Для контроля за работоспособностью микропроцессорной системы (P1) предусмотрен не зависимый от этой первой микропроцессорной системы (P1) контрольный блок. В соответствии с изобретением важная для обеспечения безопасности система помимо первой микропроцессорной системы (P1) имеет по меньшей мере еще одну микропроцессорную систему (Рm), которая, например физической шиной (K1) данных, соединена с первой микропроцессорной системой (P1) для обмена с ней данными. Такие дополнительные микропроцессорные системы (Рm) берут на себя выполнение функций контрольного блока. Тем самым отпадает необходимость предусматривать отдельный контрольный блок. Это позволяет упростить структуру распределенной системы с сохранением надежного срабатывания ее компонентов. 5 з.п. ф-лы, 4 ил.

а) с помощью первой микропроцессорной системы (P1) в зависимости по меньшей мере от одного входного сигнала (E1) формируют по меньшей мере один управляющий сигнал (A11) для этого компонента (Akt1),

б) формируют по меньшей мере один логический управляющий сигнал (A1m), который по меньшей мере частично формируется независимым от первой микропроцессорной системы (P1) контрольным блоком в зависимости от указанного по меньшей мере одного входного сигнала (E1),

в) этот по меньшей мере один управляющий сигнал (А11) сравнивают с указанным по меньшей мере одним логическим управляющим сигналом (A12),

г) в зависимости от результата такого сравнения формируют по меньшей мере один разрешающий сигнал (F1) и

д) указанный по меньшей мере один управляющий сигнал (А11) или по меньшей мере один зависящий от него сигнал в том случае, если по меньшей мере один разрешающий сигнал (F1) соответствует заданному значению, передают в компонент (Akt1),

отличающийся тем, что важная для обеспечения безопасности система помимо первой микропроцессорной системы (P1) имеет по меньшей мере еще одну микропроцессорную систему (Рm), которая соединена с первой микропроцессорной системой (P1) для обмена с ней данными, при этом по меньшей мере одну из стадий б)-г) осуществляют по меньшей мере в одной из этих дополнительных микропроцессорных систем (Рm).

| DE 19717686, 29.10.1998 | |||

| DE 19716197 A1, 22.10.1998 | |||

| DE 19829126 A1, 29.10.1998 | |||

| ТОРМОЗНАЯ СИСТЕМА С АНТИБЛОКИРОВОЧНЫМ УПРАВЛЕНИЕМ И/ИЛИ УПРАВЛЕНИЕМ ПРОСКАЛЬЗЫВАНИЕМ ПРИ ТЯГОВОМ УСИЛИИ | 1994 |

|

RU2110423C1 |

Авторы

Даты

2006-10-10—Публикация

2002-03-14—Подача