Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь кода (см. А.С. СССР №1332536 от 07.03.86, МКИ: Н 03 М 5/12, “Преобразователь кода”, И.В.Келтуяла, опубл. 23.08.87, Бюл. №31), содержащий генератор импульсов, прямой выход которого соединен с вторыми входами первого и второго элементов И, элемент НЕ, выход которого подключен к первому входу второго элемента И, триггер, выход которого является выходом преобразователя. Первый вход первого элемента И объединен с входом элемента НЕ и является входом преобразователя. D-вход триггера подключен к выходу элемента НЕ. Выходы первого и второго элементов И и инверсный выход генератора импульсов соединены, соответственно, с S-, R- и С-входами триггера.

Недостатком известного преобразователя кода является низкое быстродействие из-за низкой скорости преобразования.

Наиболее близким по совокупности существенных признаков к заявляемому изобретению является преобразователь кода (см. патент США № 4100541, “Быстродействующее кодирующее устройство”, МКИ: Н 03 К 13/24, дата публикации: 11 июля 1978 г.), содержащий входную схему для приема последовательной информации, соединенную с синхронизирующим устройством, с помощью которого вырабатывается первая текущая информация и вторая задержанная инверсная текущая информация. С синхронизирующим устройством соединен умножитель (мультиплексор), с помощью которого обеспечивается селекция текущей информации и вырабатывается выходная текущая информация в фазоманипулированном коде (коде Манчестера). Вход входной схемы является входной информационной шиной. Шина тактовых импульсов соединена с синхронизирующим устройством и умножителем. Выход мультиплексора является выходной информационной шиной.

Недостатками известного преобразователя кода являются:

- сложность выделения момента начала поступления полезной информации ввиду постоянного формирования последовательности импульсов на выходе преобразователя в режиме ожидания;

- необходимость формирования признака начала информационной посылки, обеспечивающего взаимную синхронизацию приемника и передатчика и достоверную передачу сообщений вследствие использования фазоманипулированного кода в качестве выходного кода преобразователя;

- отсутствие возможности формирования на выходе преобразователя кода информационных посылок определенной длины вследствие отсутствия в схеме преобразователя устройства, задающего количество битов в выходной информационной посылке.

Задачей, на решение которой направлено заявляемое изобретение, является создание преобразователя кода, обладающего расширенными функциональными возможностями, а именно: формирование на выходе преобразователя сигнала логического "0" в режиме ожидания, формирование на выходе самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, формирование на выходе преобразователя информационных посылок определенной длины.

Технический результат, заключающийся в расширении функциональных возможностей, достигается тем, что в преобразователь кода, содержащий входную информационную шину, шину тактовых импульсов и мультиплексор, выход которого соединен с выходной информационной шиной, введены шина пуска, RS-триггер и блок управления, тактовый вход которого соединен с шиной тактовых импульсов, первый выход - с первым входом мультиплексора, второй вход которого соединен с входной информационной шиной, а вход селекции - со вторым выходом блока управления, третий выход которого соединен с S-входом RS-триггера, выход которого соединен с входом сброса блока управления, а R-вход - с шиной пуска преобразователя.

Указанная совокупность признаков позволяет расширить функциональные возможности преобразователя кода, а именно:

- обеспечить формирование на выходе преобразователя сигнала логического "0" в режиме ожидания, обеспечить формирование на выходе преобразователя информационных посылок определенной длины за счет блокирования работы преобразователя в режиме ожидания и задания количества битов в выходной информационной посылке;

- обеспечить формирование на выходе самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки за счет использования широтно-манипулированного кода, формируемого путем манипуляции шириной импульсов внутри постоянных битовых интервалов, в качестве выходного кода преобразователя.

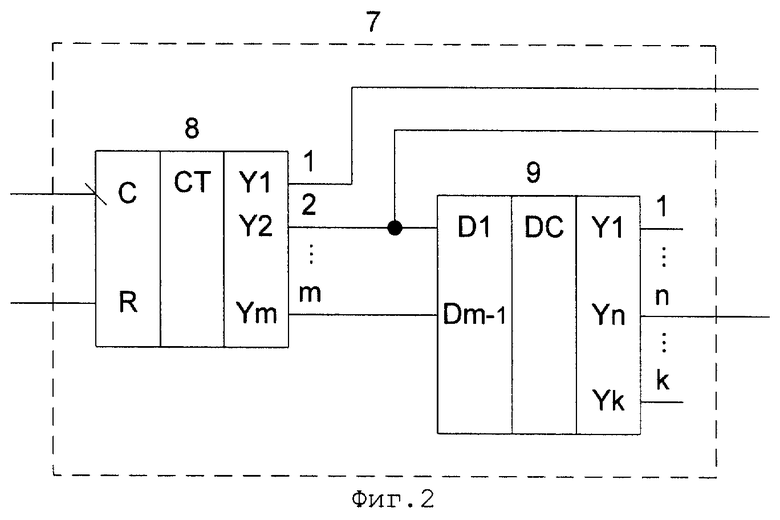

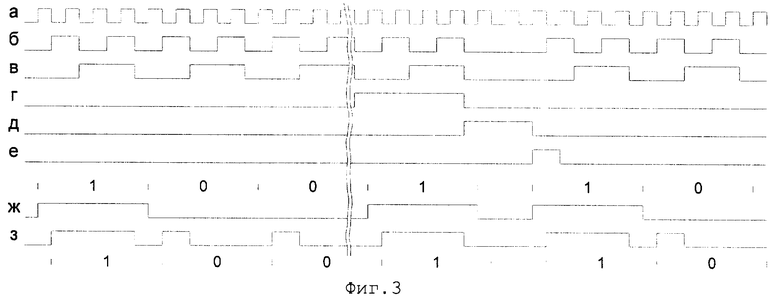

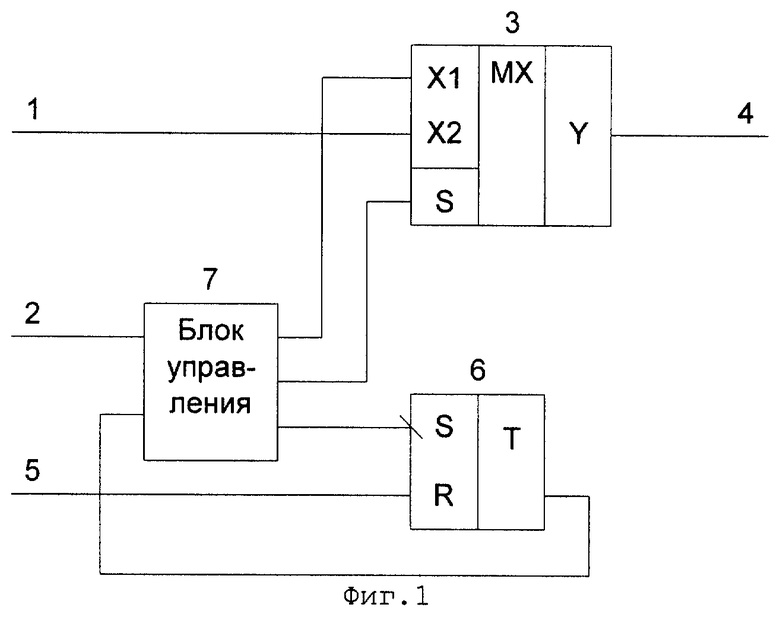

На фиг.1 приведена принципиальная электрическая схема преобразователя кода; на фиг.2 - принципиальная электрическая схема блока управления; на фиг.3 - временные диаграммы работы преобразователя кода.

Преобразователь кода содержит (см.фиг.1) входную информационную шину 1, шину 2 тактовых импульсов, мультиплексор 3, выходную информационную шину 4, шину 5 пуска, переключающийся в единичное состояние по срезу RS-триггер 6 и блок 7 управления. Выход мультиплексора 3 соединен с выходной информационной шиной 4. Тактовый вход блока 7 управления соединен с шиной 2 тактовых импульсов, а его первый выход - с первым входом мультиплексора 3, второй вход которого соединен с входной информационной шиной 1, а вход селекции - со вторым выходом блока 7 управления. Третий выход блока 7 управления соединен с S-входом RS-триггера 6, выход которого соединен с входом сброса блока 7 управления, а R-вход - с шиной 5 пуска преобразователя.

Блок 7 управления (см.фиг.2) выполнен на тактируемом срезом m-разрядном счетчике 8 и дешифраторе 9, имеющем k выходов (k=2m-1). Первым и вторым выходами блока 7 управления являются, соответственно, выходы первого и второго разрядов счетчика 8, третьим выходом - n-й выход дешифратора 9, где n определяет длину передаваемой информационной посылки (n≤k). Тактовым входом и входом сброса блока 7 управления являются соответственно тактовый вход и R-вход счетчика 8. Выходы со второго по m-й разряд счетчика 8 соединены соответственно с адресными входами D1...Dm-1 дешифратора 9.

Преобразователь кода работает следующим образом.

В исходном состоянии на информационной шине 1, шине 2 тактовых импульсов, информационной шине 4 и шине 5 пуска - уровень логического "0". Мультиплексор 3, RS-триггер 6 и блок 7 управления находятся в состоянии логического "0".

Преобразователь готов к преобразованию бинарного кода в широтно-манипулированный код. На шину 2 (см.фиг.3, а) поступают тактовые импульсы. На информационную шину 1 (см.фиг.3, ж) поступает информация в бинарном коде, причем на один бит информации (битовый интервал) приходится четыре импульса на шине 2 тактовых импульсов.

По срезу импульса, поступающего на шину 2 тактовых импульсов (см.фиг.3, а), на первом выходе блока 7 управления (см.фиг.3, б) устанавливается уровень логической "1", который через мультиплексор 3 поступает на информационную шину 4 (см.фиг.3,з). По срезу следующего импульса, поступающего на шину 2 тактовых импульсов, на втором выходе блока 7 управления (см.фиг.3, в) устанавливается уровень логической "1", который поступает на вход селекции мультиплексора 3 и переводит его в режим передачи на свой выход информации со своего второго входа. Таким образом, на информационной шине 4 (см.фиг.3, з) установится логический уровень информационной шины 1 (см.фиг.3, ж). По срезу следующего импульса, поступающего на шину 2 тактовых импульсов, изменения логического уровня на втором выходе блока 7 управления не происходит, поэтому на информационной шине 4 по-прежнему присутствует логический уровень информационной шины 1. По срезу следующего импульса, поступающего на шину 2 тактовых импульсов, на втором выходе блока 7 управления устанавливается уровень логического "0", который поступает на вход селекции мультиплексора 3 и переводит его в режим передачи на свой выход информации со своего первого входа. Уровень логического "0" с первого выхода блока 7 управления через мультиплексор 3 поступает на выходную информационную шину 4. По срезу следующего импульса, поступающего на шину 2 тактовых импульсов, начинается преобразование следующего бита информационной посылки. Преобразование последующих битов информационной посылки осуществляется аналогично. Таким образом, на информационной шине 4 формируется широтно-манипулированный код.

В момент окончания преобразования предпоследнего бита информационной посылки по срезу импульса, поступающего на шину 2 тактовых импульсов, на третьем выходе блока 7 управления (см.фиг.3, г) устанавливается уровень логической "1". В момент окончания преобразования последнего бита информационной посылки по срезу импульса, поступающего на шину 2 тактовых импульсов, на третьем выходе блока 7 управления формируется отрицательный перепад, который переключает в единичное состояние RS-триггер 6 (см.фиг.3, д), уровень логической "1" с выхода которого поступает на вход сброса блока 7 управления, устанавливая последний в нулевое состояние.

Для преобразования следующей информационной посылки необходимо подать информацию в бинарном коде на входную информационную шину 1, а на входе 5 пуска преобразователя (см.фиг.3, е) установить уровень логической "1". При этом RS-триггер 6 устанавливается в нулевое состояние, а удерживающий потенциал с входа сброса блока 7 управления снимается, разрешая тем самым изменение состояния блока 7 управления. Для обеспечения нормального функционирования преобразователя кода необходимо установить уровень логического "0" на входе 5 пуска преобразователя и, соответственно, снять удерживающий потенциал с R-входа RS-триггера 6 до момента окончания преобразования информационной посылки.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2258304C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259009C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259010C1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Программируемое устройство для вычисления логических функций | 1987 |

|

SU1444744A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| Делитель частоты следования импульсов с регулируемым коэффициентом деления | 1987 |

|

SU1517130A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090839C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Техническим результатом является расширение функциональных возможностей. Устройство содержит мультиплексор, RS-триггер, блок управления, выполненный на тактируемом срезом m-разрядном счетчике и дешифраторе. 1 з.п. ф-лы, 3 ил.

| US 4100541 А, 11.07.1978 | |||

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| Преобразователь кода | 1986 |

|

SU1332536A1 |

| Преобразователь кода | 1986 |

|

SU1372624A1 |

| US 4884074 А, 01.09.1998 | |||

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

2005-06-10—Публикация

2002-08-23—Подача