ОБЛАСТЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

Настоящее изобретение относится к детектированию импульсов во входном сигнале, содержащем импульсы различной модуляции и длительности, и, в частности, к детектированию и определению характеристик импульсов на основе оптической аналоговой и цифровой обработки.

ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

Импульсный детектор принимает входной сигнал, содержащий импульсы, характеризующиеся длительностью от нескольких наносекунд или менее до нескольких миллисекунд или более и модуляцией, такой как внутриимпульсная линейная частотная модуляция, фазовая манипуляция, частотная манипуляция и аддитивный Гауссов шум. Выходной сигнал импульсного детектора представляет собой сигнал, идентифицирующий время появления и длительность, т.е. временной интервал, ширину полосы частот и центральную частоту, т.е. частотный интервал каждого импульса во входном сигнале.

В известных системах для детектирования импульсов во входном сигнале использовалась цифровая технология. В известных цифровых системах реализовывался хорошо известный алгоритм «согласованной матрицы детектирования» (СМД) ("matched detection matrix" (MDM) или вариации этого алгоритма для детектирования импульсов в электронном входном сигнале. С помощью алгоритма СМД осуществляется эффективный поиск концентраций энергии во временной области и в частотной области. Часть временной записи, в которой обнаружена энергия, указывает на временной интервал, в котором может существовать импульс. Местоположение энергии в частотной области представляет собой частотный интервал, в котором существует импульс.

С целью точного обнаружения временного интервала и частотного интервала необходимо провести поиск многочисленных временных и частотных интервалов для обнаружения и определения местоположения энергии сигнала. Вычислительная нагрузка, требуемая для проведения поиска этих временных и частотных интервалов, может значительно превышать нагрузку, которую может обеспечить стандартная цифровая вычислительная машина. Таким образом, существует необходимость в системе детектирования импульсов с целью эффективного выполнения алгоритма СМД путем поиска многочисленных временных и частотных интервалов, обладающей большим быстродействием, меньшим весом, меньшими габаритами, более низким энергопотреблением и стоимостью по сравнению с предыдущими цифровыми процессорами.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩЕСТВА ИЗОБРЕТЕНИЯ

В соответствии с настоящим изобретением предлагается способ и устройство для реализации алгоритма СМД с использованием гибридного оптического, электрического аналогового и цифрового процессора.

В соответствии с настоящим изобретением в импульсном детекторе с согласованной матрицей детектирования (СМД) используется коллимированный и когерентный световой пучок для освещения ячейки Брегга, возбуждаемой с помощью входного сигнала, содержащего импульсы различной модуляции и длительности. В ответ на входной сигнал ячейка Брегга модулирует коллимированный световой пучок. Непрозрачная пластина, содержащая множество щелей имеющих заданную длину, установлена в определенном положении для приема модулированного светового пучка после его прохождения через систему оптических линз. Система оптических линз расположена на пути пространственно-модулированного коллимированного светового пучка с целью формирования изображения пучка, выходящего из ячейки Брегга, на плоскости непрозрачной пластины. Голографический элемент расположен на пути образующего изображение пучка и рядом с оптической линзой с целью многократного мультиплицирования изображения апертуры ячейки Брегга в плоскости непрозрачной пластины.

Дополнительным усовершенствованием является то, что длина щели непрозрачной пластины зависит от количества чувствительных элементов детектора/процессора фокальной плоскости в ширине полосы частот импульсов входного сигнала.

При этом непрозрачная пластина импульсного детектора дополнительно содержит призму для каждой щели для того, чтобы направлять пространственно-модулированный коллимированный пучок из каждой щели в выбранный участок фокальной плоскости оптической системы линз.

В еще одном усовершенствовании импульсный детектор дополнительно содержит призму для каждой из щелей для направления пространственно-модулированного коллимированного светового пучка в выбранный участок фокальной плоскости оптической системы линз.

Вторая оптическая система линз на пути пространственно-модулированного светового пучка расположена позади непразрачной пластины. Вторая оптическая система линз формирует пространственное преобразование Фурье распределения света, в результате чего интенсивность света в фокальной плоскости второй оптической системы линз становится пропорциональной энергетической спектральной плотности сигнала, модулирующего ячейку Брегга, непосредственно после модификации оптической пластиной. Детекторная матрица в фокальной плоскости второй оптической системы линз реагирует на интенсивность света для идентификации импульсов во входном сигнале, включая местоположение временных и частотных интервалов в каждом импульсе.

При этом каждая из щелей непрозрачной оптической пластины имеет длину, обусловленную длительностью импульсов входного сигнала.

Предпочтительно импульсный детектор дополнительно содержит призму для каждой из щелей непрозрачной пластины, при этом каждая призма направляет пространственно-модулированный коллимированный световой пучок из каждой щели на выбранный участок фокальной плоскости второй оптической системы линз.

Далее, в соответствии с настоящим изобретением предлагается процессор фокальной плоскости, расположенный после каждого детектора, с целью осуществления импульсного детектора на согласованной матрице детектирования, включающего частотный интегратор для выбранных изображений из множества изображений на оптической пластине. Детектор и процессор фокальной плоскости далее включают интегратор времени для выбранных изображений из множества изображений на оптической плоскости. Кроме того, имеется селектор команд настройки для выбранных изображений из множества изображений.

Интегратор времени процессора фокальной плоскости включает регулятор усиления, реагирующий на выходные сигналы каждого детектора в матрице на фокальной плоскости. Предварительный усилитель реагирует на регулятор усиления, благодаря чему производится регулировка усиления предварительного усилителя. С помощью регулятора усиления производится корректировка колебаний усиления от одного детектора к другому, обусловленных несовместимостью компонентов при изготовлении и шумовыми спектральными изменениями.

Выходной сигнал каждого детектора дискретизируется с минимально допустимой частотой дискретизации (частота Найквиста) или более высокой, усиливается, сохраняется и в последующем считывается в элемент ЗУ мультиплексора. Хранимые выборки в мультиплексоре считываются из памяти, и первая храникмая выборка переводится в последующий элемент ЗУ, и следующая выборка хранится на месте первой. Следующая хранимая выборка далее считывается в мультиплексор, производится вычисление суммы выборок и их считывание из мультиплексора. Этот процесс повторяется, и при каждом повторении значения будут считываться из мультиплексора.

В соответствии с настоящим изобретением частотный интегратор включает пороговый детектор, принимающий выходные сигналы из мультиплексора или интегратора времени, для сравнения с пороговой величиной с целью определения полосы частот, соответствующей конкретному интегратору времени. Время, полоса частот и величина, полученная в результате сравнения с пороговой величиной, передаются в селектор команд настройки. Селектор команд настройки производит обработку выходных сигналов из частотного интегратора, начиная с сигнала максимального уровня и заканчивая минимальным сигналом. Сигнал максимального уровня, вероятней всего, будет соответствовать действующему импульсу. В результате этого обеспечивается оценка полосы пропускания (частотный интервал) импульса и оценка длительности и время появления импульса (временной интервал).

Технической особенностью настоящего изобретения является оптический, электрический, аналоговый и цифровой процессор для детектирования импульсов, реализующий алгоритм СМД. Осуществление в соответствии с настоящим изобретением позволяет производить обработку данных значительно быстрее из расчета времени в относительных единицах по сравнению с ранее реализованными цифровыми методами.

Обеспечивается поиск значительно большего количества временных и частотных интервалов с целью обнаружения импульса, в результате чего достигается более высокая точность определения расположения времени и частоты. Кроме того, большее количество временных и частотных интервалов обеспечивает осуществление более чувствительного детектора импульсов. Другое преимущество настоящего изобретения заключается в способе оптической, электрической, аналоговой и цифровой обработки для детектирования импульсов во входном сигнале, в результате чего обеспечиваются оптимальные вес, габариты, энергоэкономичность и стоимость по сравнению с известными цифровыми детекторами импульсов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Более полное понимание импульсного детектора в соответствии с настоящим изобретением может быть достигнуто из следующего ниже подробного описания, ведущегося со ссылками на прилагаемые чертежи, на которых:

Фиг.1 - упрощенная блок-схема импульсного детектора, принимающего входной сигнал в качестве сенсора и генерирующего выходной сигнал, характеризующий или идентифицирующий импульсы, содержащиеся во входных сигналах;

Фиг.2 - блок-схема способа и устройства для импульсного детектирования, включающие как оптическую, электрическую, аналоговую, так и цифровую обработку в соответствии с настоящим изобретением;

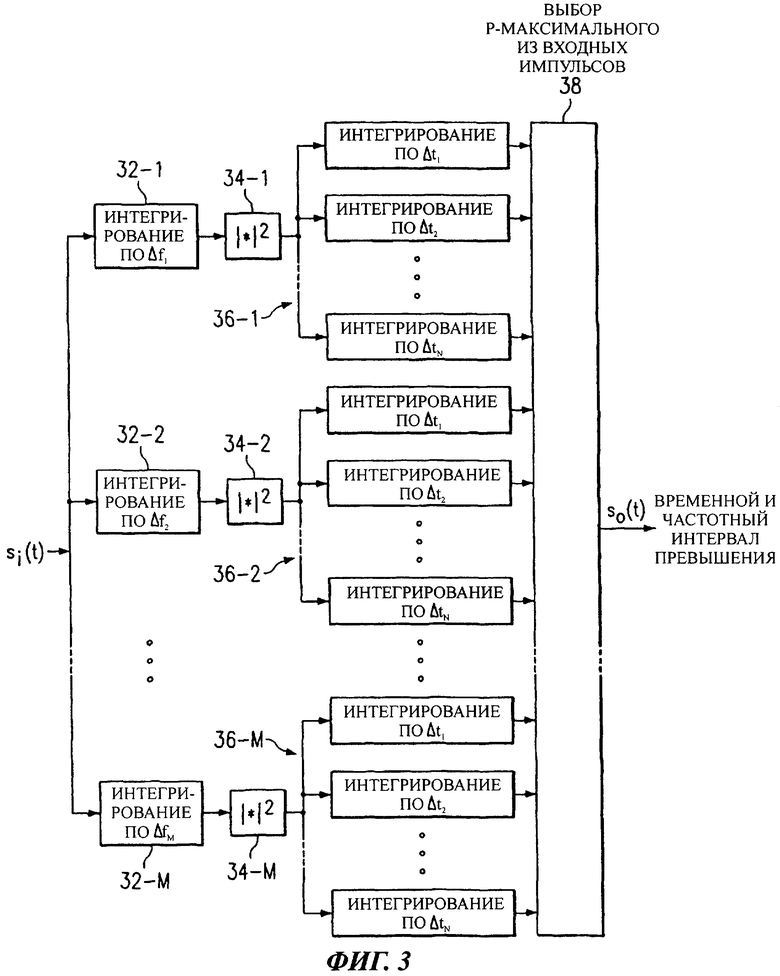

Фиг.3 - схема алгоритма согласованной матрицы детектирования (СМД) для детектирования импульсов;

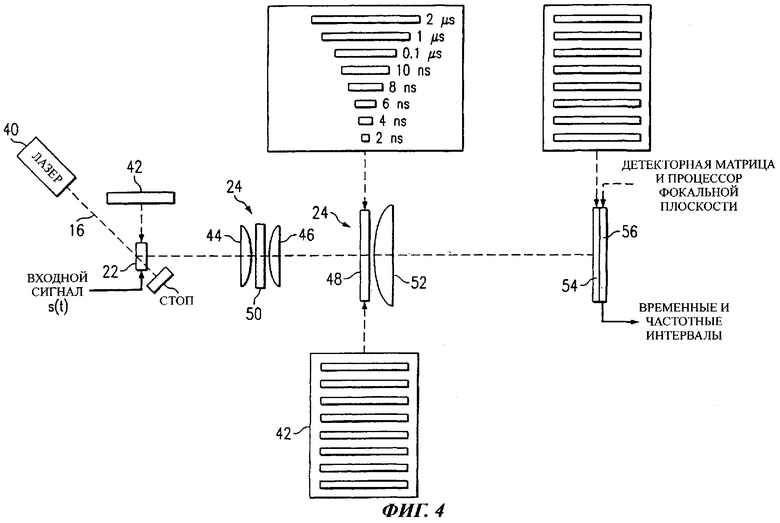

Фиг.4 - схема оптического, электрического, аналогового и цифрового процессора в соответствии с настоящим изобретением для осуществления импульсного детектирования с помощью алгоритма СМД;

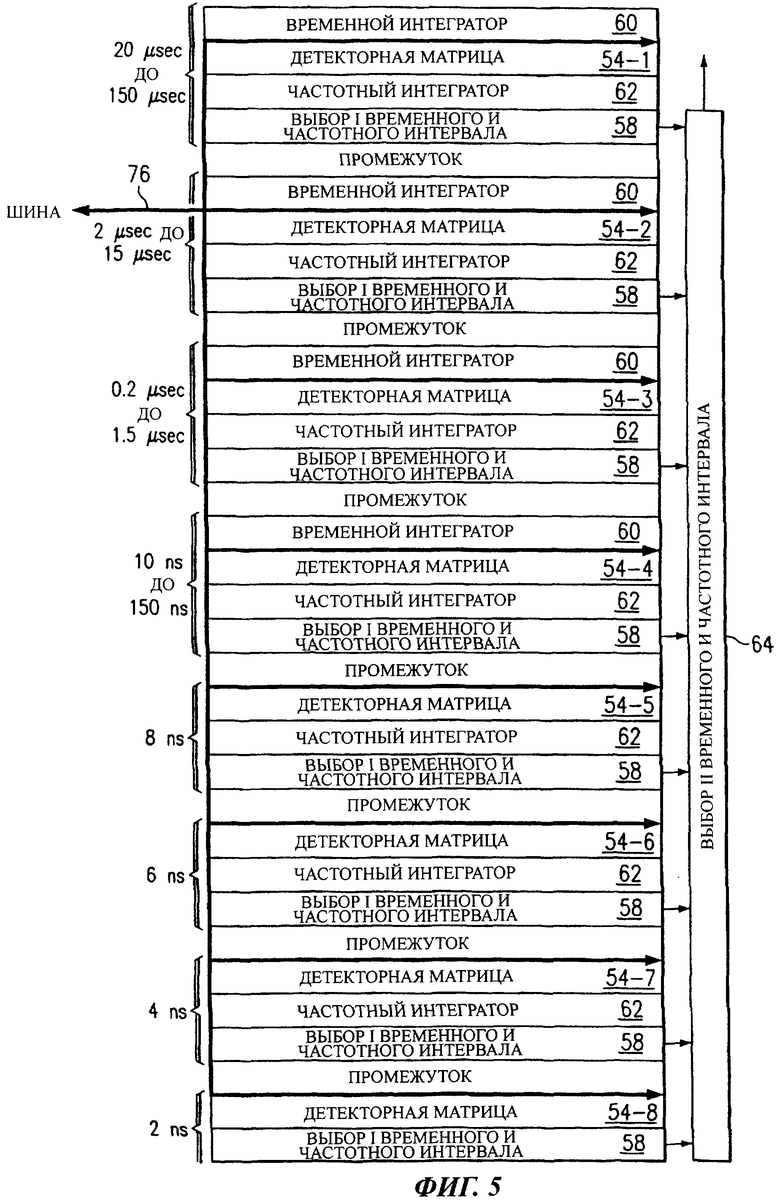

Фиг.5 - архитектура детекторной матрицы и процессор фокальной плоскости, показанные на Фиг 4;

Фиг.6 - схематическое изображение одной из детекторных матриц в архитектуре, схематически показанной на Фиг 5;

Фиг 7 и 8 - схемы альтернативных примеров осуществления интегратора времени в соответствии с настоящим изобретением для детектора и процессора фокальной плоскости импульсного детектора на согласованной матрице детектирования;

Фиг 9 - схема частотного интегратора для детектора и процессора фокальной плоскости импульсного детектора на алгоритме СМД; и

Фиг 10 - блок-схема буфера и многозвенной логической схемы сравнения для выбора I временного и частотного интервала, за которым следует выбор II временного и частотного интервала.

ПОДРОБНОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На Фиг.1 показана схема импульсного детектора и характеризатора импульсов, использующих оптическую/электрическую и аналоговой/цифровую обработки для детектирования импульсов во входном сигнале и затем для определения характеристик детектированных импульсов. Преобразователь частоты 10 понижает частоты сигнала на fo для того, чтобы центральная частота сигнала соответствовала центральной частоте ячейки Брегга. Результирующий сигнал подается в аналого-цифровой преобразователь (АЦП) и в буфер 12, преобразующий сигнал в цифровую форму. Затем оцифрованный сигнал временно сохраняется в буфере. Сигнал также подается в импульсный детектор 14.

Как будет описано ниже, импульсный детектор 14 содержит оптические элементы (не показаны) и реагирует на коллимированный пучок света 16, подаваемый на вход импульсного детектора. Импульсный детектор обнаруживает наличие импульсов и направляет их в виде выходного сигнала, а именно временных и частотных интервалов, которые могут содержать импульсы, в процессор 18 команд начальной настройки. Процессор 18 команд начальной настройки передает временные интервалы, по всей вероятности, содержащие импульс, в буфер 12. Далее оцифрованные записи этих временных интервалов из буфера 12 направляются в поддиапазонный тюнер и в оператор 20 характеризации импульсов. Части сигнала, хранящиеся в буфере 12, которые не рассматриваются импульсным детектором в качестве импульсов, сбрасываются. Процессор 18 команд начальной настройки также определяет, является ли отобранный импульс двойным импульсом, в котором импульсы перекрывают друг друга как по времени, так и по частоте, а не единичным импульсом. Процессор 18 также определяет, могут ли импульсы рассматриваться как последовательность импульсов, а не как единичный импульс. Эта информация вместе с временными и частотными интервалами включает команды начальной настройки. Команды начальной настройки направляются в поддиапазонный тюнер и оператор 20 харакетризации импульсов. Параметры поддиапазонного тюнера устанавливаются командами начальной настройки. Поддиапазонный тюнер фильтрует соответствующую временную запись из буфера 12 с целью снижения шума, связанного с импульсом. Оператор 20 характеризации импульсов определяет длительность импульса, время появления, амплитуду и тип модуляции.

Как показано на Фиг. 2, входной сигнал, содержащий импульсы различной модуляции, такие как внутриимпульсная линейная частотная модуляция, фазовая манипуляция, частотная манипуляция с произвольной длительностью и аддитивный Гауссов шум, подается на ячейку Брегга 22. Ячейка Брегга 22 принимает коллимированный световой пучок 16 для пространственной модуляции светового пучка в соответствии со входным сигналом. При выходе из ячейки Брегга 22 пространственно-модулированный световой пучок направляется на оптическую систему 24, образующую спектры 26 сигнала на детекторной матрице 28. Детекторная матрица 28 реагирует на спектры 26 сигнала в форме аналогового сигнала, подаваемого на процессор 30 фокальной плоскости. Процессор 30 фокальной плоскости реализует алгоритм согласованной матрицы детектирования СМД и подает на выход временные и частотные интервалы, которые, скорее всего, содержат импульс.

На Фиг.3 показан алгоритм согласованной матрицы детектирования (СМД). Входной сигнал Si (t), содержащий импульсы для детектирования, а также шум подается на блок полосовых фильтров 32-1, 32-2...32-М через полосы пропускания Δf1, Δf2,...Δfm, соответственно. Каждая полоса пропускания представляет интервал в частоте. Полосовые фильтры эффективно интегрируют энергию во входной сигнал по этой полосе пропускания. Полосы пропускания выбраны таким образом, чтобы охватить все полосы пропускания, которые могут быть заняты входящим сигналом. Очевидно, что количество полос пропускания может быть исключительно большим. Задача при реализации алгоритма заключается в интегрировании по как можно большему количеству полос пропускания. Выходные сигналы полосовых фильтров 32-1, 32-2...32-М преобразуются в прямоугольную форму в сетях 34-1, 34-2...34-М формирования прямоугольных импульсов и подаются на другой комплект блоков фильтров 36-1, 36-2...36-М. Эти блоки фильтров выполняют временную интеграцию длительности Δtl, где I имеет диапазон от 1 до N, на подаваемом входном сигнале, как показано на Фиг.3. Величины Δtl имеют диапазон в пределах возможной длительности входящего импульса.

Другая цель реализации алгоритма заключается в интегрировании по как можно большему количеству временных интервалов. Максимальный выход из фильтров временного интегрирования 36-1, 36-2...36-М представляет собой выход сигнала из соответствующего полосового фильтра 32-1, 32-2...32-М, в наибольшей степени совпадающий с входящим импульсом в полосе пропускания или временном интервале, и из фильтров временного интегрирования, имеющих время интегрирования, в наибольшей степени совпадающее с длительностью импульса. Время, в течение которого максимальная величина появляется на выходе фильтров интегрирования времени, представляет собой время появления импульсов во входном сигнале Si (t). Выходные сигналы блоков фильтров 36-1, 36-2...36-М подаются на частотно-избирательную схему 38, которая выбирает Р-максимальное входных импульсов, обнаруженных во входном сигнале Si (t), где Р обычно выбирается как число импульсов на единицу времени, которое блок поддиапазонной настройки и характеризации в состоянии обработать. Выходной сигнал частотно-избирательной схемы 38 представляет собой входной сигнал So (t), идентифицирующий время появления и длительность (временной интервал) и полосу пропускания (частотный интервал) импульсов в первоначальной волновой форме.

В соответствии с настоящим изобретением алгоритм согласованной матрицы детектирования (СМД) реализуется гибридным оптическим, электрическим, аналоговым и цифровым процессором, как показано на Фиг.4.

На Фиг.4 показана схема оптического/электрического и аналогового/цифрового импульсного детектора в соответствии с настоящим изобретением. Входной сигнал возбуждает ячейку Брегга, освещаемую коллимированным световым пучком 16 из лазера 40. Ячейка Брегга 22 имеет апертуру ячейки, обозначенную позицией 42, освещаемую коллимированным световым пучком 16. Ячейка Брегга пространственно модулирует коллимированный световой пучок 16, проходящий через апертуру, и при выходе из ячейки Брегга с помощью линз 44 и 46 оптической системы 24 формируется его изображение на плоскости непрозрачной пластины 48, также находящейся внутри оптической системы 24. Бинарная оптическая пластина (или голограмма) 50, расположенная между линзами 44 и 46, мультиплицирует изображение апертуры 42 ячейки Брегга восемь раз, как показано отображением плоскости изображения непрозрачной пластины 48. Специалистам в данной области должно быть очевидно, что бинарная оптическая пластина 50 может быть конфигурирована таким образом, чтобы мультиплицировать изображение апертуры 42 ячейки Брегга более восьми раз. В показанном примере осуществления в соответствии с настоящим изобретением бинарная оптическая пластина 50 была подобрана для мультиплицирования изображения апертуры 42 ячейки Брегга восемь раз.

Как показано на Фиг.4, непрозрачная пластина 48 имеет щели различной длины, расположенные в тех местах, где производится мультиплицирование изображений апертуры 42 ячейки Брегга. С помощью щелей непрозрачной пластины 48 устанавливается эффективная длина апертуры ячейки Брегга для каждого мультиплицирования. Количество изображений и длина щелей в непрозрачной пластине 48 даны в качестве примера, а не в качестве ограничения. Длина щелей, как показано на Фиг.4, обусловлена временем, за которое волна в ячейке Брегга 22 проходит длину щели. Например, длина щелей (не показано) изменяется от 2 наносекунд, 4 наносекунд, 6 наносекунд, 8 наносекунд, 10 наносекунд, 0,1 микросекунды, 1 микросекунды и 2 микросекунд. С целью получения энергетического спектра каждого из изображений щелей в непрозрачной пластине 48 анаморфотная линза 52 расположена на пути света, проходящего через непрозрачную пластину. Анаморфотная линза 52 формирует пространственное преобразование Фурье распределения света в щелях на пластине 48, в результате чего интенсивность света в фокальной плоскости анаморфотной линзы 52 становится пропорциональной энергетической спектральной плотности входного сигнала Si (t). Анаморфотная линза 52 создает изображение каждой из щелей непрозрачной пластины 48 в вертикальном направлении и преобразует изображение в горизонтальном направлении. Свет из анаморфотной линзы 52 воспринимается детекторной матрицей 54, имеющей восемь линий детекторов, соответствующих восьми прорезям в непрозрачной пластине 48. Линии детекторов принимают и детектируют свет из соответствующих прорезей в пластине 48.

Благодаря анаморфотной линзе 52, изображение прорезей на детекторе 54 является неперекрывающимся в вертикальном направлении, и обеспечивается совмещение преобразования Фурье с осью частоты в горизонтальном направлении. Таким образом, анаморфотная линза 52 формирует изображение в вертикальном направлении и преобразует его в вертикальном направлении. Благодаря этому образуются восемь независимых изображений, представляющих спектры, падающие на детекторы 54. Отображаемый спектр ориентирован во времени как в непрозрачной пластине 48, то есть, верхний спектр в изображении предназначен для 2-микросекундного временного интервала, в то время как спектр для нижнего изображения - для 2-наносекундного временного интервала.

К детекторной матрице 54 подсоединен процессор 56 фокальной плоскости для преобразования аналоговых выходных сигналов из детектора 54 во временные и частотные интервалы для обнаружения и определения характеристик импульсов во входном сигнале. В качестве процессора фокальной плоскости обычно используется электрический аналоговый процессор, на который поступает аналоговый ток из детектора и который выполняет математические операции или алгоритмы по этому току.

Процессор 56 фокальной плоскости обрабатывает информацию из детекторной матрицы 54 для выполнения математической операции, приводящей к обнаружению импульсов во входном сигнале, поступающем на ячейку Брегга 22. Математические операции выполняются как во времени, так и по частоте с целью получения временного интервала и частотного интервала импульсов, содержащихся во входном сигнале. На Фиг.5 показаны детектор 54 и процессор 56 фокальной плоскости, содержащие восемь детекторных матриц 54-1...54-8 для каждого из восьми изображений, сформированных анаморфотной линзой 52 на детекторной матрице 54. С каждой из детекторных матриц 54-1...54-8 связан процессор 58 выбора I временного и частотного интервала, интегратор времени 60 и частотный интегратор 62. Для исключения из процессора фокальной плоскости быстродействующих схем в матрице и процессоре фокальной плоскости используется совершенно иной подход в отношении импульсов, имеющих длительность менее 10-наносекунд (нс). Ячейка Брегга, используемая в этом расчете, имеет ширину полосы частот 500 МГц. Минимальная ширина полосы частот 2-наносекундного импульса также составляет около 500 МГц.

Следовательно, имеется допущение, что частотный интервал 2-наносекундного импульса составляет 500 МГц или более ввиду ограничений ячейки Брегга. Не предпринимаются попытки для определения ширины полосы частот 2-наносекундного импульса и, следовательно, не предусматривается интегратор частот. Временной интервал импульсов короче 10 наносекунд определяется с помощью фильтра и пороговой величины после детектора, как показано на Фиг. 8, и об этом речь пойдет ниже.

Импульсная обработка 4-наносекундного импульса отличается от импульсной обработки 2-наносекундного импульса тем, что ширина пропускания частот 4 нс импульса может находиться в пределах от 250 МГц до 500 МГц диапазона системы. Следовательно, частотный интегратор необходим для оценки частотного интервала.

6- нс и 8- нс процессоры фокальной плоскости являются процессорами той же самой модификации, как и 4- нс процессор фокальной плоскости. Для остальных изображений временного интервала, показанных на непрозрачной пластине 48, используется процессор 58 выбора I временного и частотного интервала, интегратор времени 60 и частотный интегратор 62 для обработки импульсных сигналов в различных временных интервалах. Как показано на Фиг.5, каждый из процессоров 58 выбора I временного и частотного интервала формирует выходной сигнал, подаваемый на процессор 64 выбора II временного и частотного интервала.

Для четырех наиболее длительных импульсных интервалов, а именно: 10 нс-150 нс, 0,2 микросекунд-1,5 микросекунд, 2 микросекунды-15 микросекунд и 20 микросекунд-150 микросекунд требуется как временное интегрирование, так и частотное интегрирование с помощью процессора 58 выбора I временного и частотного интервала. В таких случаях необходим процессор 60 фокальной плоскости для временного интегрирования, так как временные интервалы, которые необходимо обнаружить, являются более длительными, чем прорези в изображении интервалов ячейки Брегга.

Выходные сигналы одного ряда или более детекторных матриц дополнительно к обработке с помощью процессора 56 фокальной плоскости снимаются на шину 76 детекторной матрицы в виде оценки фонового шума на различных точках спектра. Уровни фонового шума преобразуются в регулировки усиления в процессоре 56 фокальной плоскости.

На Фиг.6 показана схема одной из детектирующих матриц 54-1...54-8. Размеры, приведенные на Фиг.6, являются типовыми, и в каждой матрице может содержаться 1000 или более детекторов. Количество детекторов Nd устанавливается разрешением по частоте и шириной полосы частот (BW) процессора 56 фокальной плоскости в соответствии с ниже приведенным выражением:

В этом примере ширина полосы частот в 512 МГц используется вместо ширины полосы частот 500 МГц, как установлено в соответствии с ограничениями ячейки Брегга. Использование этой полосы частот позволяет упростить процессор фокальной плоскости, так как ограничение ячейки Брегга уровнем 500 МГц является номинальным ограничением и может быть в целом несколько шире, чем 500 МГц. Допуская ширину полосы частот в 512 МГц и разрешение по частоте в 0,5 МГц, получаем:

На Фиг.7 показана схема части интегратора 60 времени процессора фокальной плоскости для детекторных матриц 54-1...54-4. Выходной сигнал детекторной матрицы 54, подаваемый на электрическую шину 76, используется для определения регулировок усиления интегратора 60 времени. Существует несколько методик, которые могут использоваться для регулировки усиления усилителя 78. Одна из таких методик заключается в следующем. Усиление должно быть установлено с целью снижения сигналов ложной тревоги, вызванных шумом, присутствующим в импульсах. Пороги, служащие для снижения сигналов ложной тревоги и используемые в сочетании с регулировками усиления, находятся позади (см. Фиг.9) части процессора фокальной плоскости, показанного на Фиг.7. В спектр импульса включен спектр шума, связанный с импульсом. Может быть допущено, что шум является статистически-стационарным в интервалах, сравниваемых по длительности с длительностью импульса. Энергетическая спектральная плотность шума оценивается в частях записи, не содержащей импульса.

Микропроцессор, принимающий выходной сигнал детектора с шины 76, показанной на Фиг 7, рассчитывает энергетическую спектральную плотность шума. Среднее значение шумового спектра может быть удалено путем высокочастотной фильтрации выходного сигнала детектора (не показано) с помощью частоты включения, выбранной для пропускания импульса при одновременном устранении среднего значения спектра шума.

В альтернативном случае среднее значение спектра шума могло бы быть рассчитано и извлечено из входного сигнала детектора непосредственно после детектора (также не показано).

Итоговый результат заключается в устранении среднего значения спектра шума, при этом в расчете спектра шума остается только ошибка. С целью сохранения фиксированных пороговых величин на Фиг.9 усиление каждого детектора устанавливается таким образом, чтобы среднеквадратическая ошибка в спектре шума являлась аналогичной для всех выходных сигналов детектора. При рассмотрении Фиг.9 видно, что этот метод позволит поддерживать фиксированные пороговые величины, упрощая таким образом конструкцию процессора фокальной плоскости.

Сигнал регулировки усиления подается на вход предварительного усилителя 78 для регулировки его усиления с целью обработки выходного сигнала детекторной матрицы. Выходной сигнал конкретного детекторного элемента в детекторной матрице 54 дискретизируется с помощью дискретизатора 80 с частотой Найквиста или более высокой частотой и подается на вход предварительного усилителя.

Усиленные выходные сигналы выборок из предварительного усилителя 78 накапливаются на конденсаторе 82-1 и считываются в элемент ЗУ SV1 мультиплексора 84 через усилитель 86-1. Заряды, хранимые в мультиплексоре 84, считываются по линии 88 как входной сигнал в частотный интегратор 62. Следующая выборка из детектора 54 накапливается в конденсаторе 82-1, а предварительно накопленная выборка передается в конденсатор 82-2. Выборка, накопленная в конденсаторе 82-2, подается на вход суммирующего соединения 92-1, которое также принимает новую накопленную выборку из конденсатора 82-1. Самая последняя выборка, накопленная в конденсаторе 82-1, считывается в элемент ЗУ SV1, и сумма выборок, считанных в конденсаторы 82-1 и 82-2, подается с выхода суммирующего соединения 92-1 через усилитель 86-2 и считывается в элемент ЗУ SV2. Кроме того, все накопленные заряды в мультилексоре 84 выводятся на линию 88, ведущую к частотному интегратору 62. Этот процесс повторяется с выборочными выходными сигналами детектора, последовательно передаваемыми через конденсаторы 82-1, 82-2, 82-3...82-14 и накапливаемые в них. Эти выборки суммируются в суммирующих устройствах 92-1...92-13, как показано на Фиг.7. Сумма выходных сигналов выборки из каждого из суммирующих соединений 92 подается через усилитель 86 в элемент ЗУ в мультплексоре 84.

Процесс выборки детектора в детекторной матрице 54 и последовательной передачи выборки через конденсаторы 82-1...82-14 повторяется, и при приеме мультиплексором 84 выборки в каждом из элементов ЗУ будет получено в целом 14 величин, которые будут считываться каждый раз при считывании и подаче выборки на частотный интегратор 62.

Схемы, расположенные позади детекторов в матрицах 54-5, 54-6, 54-7 и 54-8, отличаются от схем на Фиг.7 и показаны на Фиг.8. Разница заключается в сложности создания высокоскоростных процессоров фокальной плоскости. По мере развития уровня технологии высокоскоростных устройств, схемы, расположенные после детекторов, могут быть такими же, как и в детекторных матрицах 54-1, 54-2, 54-3 и 54-4. Как показано на Фиг.8, дискретизатор отсутствует, тем не менее, методика регулировки усиления такая же как и в других детекторных матрицах. Усилитель 78 направляет поступающий сигнал в пороговый детектор 66. Порог устанавливается с целью достижения заданной вероятности детектирования для данной скорости сигнала ложной тревоги. Если порог не превышен, сигнал сбрасывается. Если порог превышен, таймер 70 останавливается, и показание, представляющее поступление импульса, направляется в процессор 58 отбора I временного и частотного интервала вместе с временной записью сигнала, превышающего порог. Таймер 70 устанавливается в исходное состояние и запускается после приема импульса или после заданного времени, если ни один из импульсов не был принят. Сигнал запуска таймера может быть послан по той же шине, по которой проходит сигнал регулировки усиления.

На Фиг.9 показана компоновка каждого из частотных интеграторов 62, показанных на Фиг.5. На Фиг.9 показана конфигурация детекторной матрицы, содержащей 1024 детекторов, показанных на Фиг.6. Следует отметить, что количество детекторов в каждой детекторной матрице 54 изменяется в зависимости от количества разрешаемых элементов в ширине полосы частот процессора фокальной плоскости. Для ширины полосы частот в 500 мегагерц детекторная матрица 54-8 включает только один разрешаемый элемент и, следовательно, только один детектор в детекторной матрице 54-8. Для детекторной матрицы 54-7 при щели 4 нс, как показано на Фиг.4, и при аналогичной рабочей полосе ширины частот в 500 мегагерц детекторная матрица 54-7 включает два разрешаемых элемента, то есть два детектора.

Таким образом, число разрешаемых элементов, то есть число детекторов в каждой из детекторных матриц 54, определяется в соответствии с приведенным выше уравнением. Наиболее значимым примером в плане количества разрешаемых элементов является детекторная матрица из 1024 разрешаемых элементов (1024 детекторов). На Фиг.9 показан пример, в котором количество детекторных элементов составляет 1024. Для детекторной матрицы 54-8, как было изложено выше, выходной сигнал детекторной матрицы подается непосредственно на процессор 58 отбора I временного и частотного интервала. Для детекторной матрицы 54-7 схема частотного интегратора включает каналы S1 и S2, то есть один канал для каждого детектора в детекторной матрице 54-7.

При работе частотного интегратора выходной сигнал частотного интегратора 62 для одного детекторного элемента детекторной матрицы 54 по линии 88 из мультиплексора 84 сравнивается с пороговой величиной в пороговом детекторе 94-1. При превышении этой пороговой величины в полосе частот может находиться импульс, соответствующий выходному сигналу интегратора времени 60. При присутствии импульса в полосе частот, время, полоса частот и значение, представляющие величину сигнала, который превысил пороговое значение, выводятся из порогового детектора 94-1 и подаются на процессор 58 выбора I временного и частотного интервала. Для канала S1 выходной сигнал интегратора времени 60 подается на суммирующее соединение 96-1. Кроме этого, для канала S2 выходной сигнал интегратора времени 60 подается на вход суммирующего соединения 96-1. Выходной сигнал интегратора времени на канале S2 подается в пороговый детектор 94-3, и при превышении порога время, полоса частот и значение, на которое превышена пороговая величина, выводятся из порогового детектора 94-3 и подаются на процессор 58 выбора I временного и частотного интервала.

Суммирование выходных сигналов интегратора времени на каналах S1 и S2 в суммирующем соединении 96-1 сравнивается с пороговой величиной в пороговом детекторе 94-2. При этом, если порог, установленный в пороговом детекторе 94-2, превышен, время, полосы частот каналов S1 и S2 и значение, на которое превышена пороговая величина, передаются в процессор 58 выбора I временного и частотного интервала. Фактически каждый отдельный канал проверяется по отношению к пороговой величине, и результаты направляются в процессор 58 выбора I временного и частотного интервала. Затем каналы суммируются в смежных парах - в данном случае только 512 каналов, - и снова осуществляется их проверка по отношению к пороговой величине, и затем результаты направляются в следующий процессор. Этот процесс продолжается до тех пор, пока не остается только одна пара, а именно суммирующее соединение 96-3. Можно легко продемонстрировать, что имеется десять уровней суммирования и что количество No выходных сигналов, суммированных на уровне k, составляет:

No=2k

Следовательно, для матрицы с 1024 детекторами количество выборок, суммированных на каждом суммирующем соединении, на 10 рассматриваемых в данном случае уровнях, составляет соответственно 1024, 512, 256, 128, 64, 32,16,8,4,2.

Следует отметить, что на Фиг.9 многие из каналов между S2 и S511 не показаны во избежание усложнения рисунка. Аналогичная ситуация наблюдается на Фиг.9 между каналами S514 and S1023, на которой значительное количество интеграторов времени не показано вместе с сопутствующими пороговыми детекторами и суммирующим соединением с целью избежания чрезмерного усложнения рисунка.

По существу, частотный интегратор просматривает каждый детекторный элемент в поисках сигнала путем сравнения выходного сигнала мультиплексора 84 с пороговой величиной. В полосе частот может содержаться сигнал, соответствующий выходному сигналу интегратора времени, когда порог, соединенный с интегратором, превышен. Тем не менее, со ссылкой на каналы S1 и S2 (в качестве примера) порог пороговых детекторов 94-1 и 94-3 может быть не превышен, но сумма сигналов для каналов S1 и S2, при их объединении в суммирующем соединении 96-1, может превышать порог порогового детектора 94-2, тем самым указывая на то, что в соответствующих временных интервалах и частотных интервалах может содержаться сигнал.

На Фиг.10 показана блок-схема процессора 58 выбора I частотного и временного интервала для каждой детекторной матрицы 54-1...54-8. Процессор 58 выбора I частотного и временного интервала выбирает и располагает по порядку, начиная с максимальной разности до минимальной между выходом интегратора времени 60 и пороговой величиной, установленной в пороговом детекторе 94. Кроме того, селектор команд начальной настройки, показанный на Фиг.10, является обобщенным представлением о том, что количество входных сигналов в селекторе 58 команд начальной настройки изменяется в зависимости от числа детекторов в соответствующей детекторной матрице. Например, для детекторной матрицы 54-8, имеющей один элемент разрешения (один детектор), селектор команд начальной настройки на Фиг.10 включает только один вход в буфер и схему сравнения 98. Для детекторной матрицы 54-7 имеется только два элемента разрешения в ширине полосы частот и, следовательно, три выхода из интегратора времени, соединенного с процессором 58 выбора I временного и частотного интервала.

У детекторной матрицы 54-7 только три входа подсоединены к буферу и схеме сравнения 98. Таким образом, сложность процессора 58 выбора I временного и частотного интервала у конкретной детекторной матрицы изменяется аналогичным образом, как и у частотного интегратора, показанного на Фиг.9. Следовательно, детекторная матрица 54-1, содержащая наибольшее количество разрешаемых элементов и наибольшее количество детекторов, будет иметь максимальное количество входов в селектор 58 команд начальной настройки, связанный с такой детекторной матрицей.

Как указывалось выше, в процессе выбора временного и частотного интервала происходит упорядочивание выходных сигналов пороговых детекторов (Фиг.9) от максимальной до минимальной пороговой разности. На практике оператор характеризации импульсов и поддиапазонный тюнер будут ограничены количеством импульсов, которые могут быть обработаны за данный интервал времени. Результат будет заключаться в том, что максимальное количество превышений Р на единицу времени будет направлено в оператор характеризации импульсов, где Р - максимальное количество, которое оператор характеризации импульсов способен обработать за единицу времени. Максимальная пороговая разность, вероятней всего, будет соответствовать импульсу достоверности.

При работе процессора 58 выбора 1 временного и частотного интервала выходные сигналы из связанного интегратора частот 62 хранятся в буфере и схеме сравнений 98. Без сомнения, при отсутствии пороговой разности вход сигнала в буфер и схему сравнения составляет нуль, указывая тем самым на отсутствие сигнала в полосе частот, соответствующей выходу интегратора времени 60.

Выходные сигналы из интегратора частот 62 на детекторные матрицы 54-1...54-7 буферизуются в буфере и схемах сравнения для каждого детекторного элемента, и все буферизованные величины подвергаются сравнению для выбора максимальной пороговой разности. Как показано на Фиг.10, сигналы из 32 детекторных элементов буферизуются. Максимальная пороговая разность для каждого из детекторных элементов перемещается в связанный буфер и схему сравнения 100. Кроме того, пороговые разности, принятые в буфере и схемах сравнения 100 из связанного буфера и сетей сравнения 98, сравниваются, и максимальная пороговая разность передается в буфер и схему сравнения 102. Буфер и схема сравнения 102 принимают выбранные пороговые разности из буфера и схем сравнения 100, и процесс сравнения и оценки максимальных пороговых разностей проходит в буфере и схеме сравнения 102.

При работе процессор 58 выбора I временного и частотного интервала сначала сортирует выходные сигналы детекторных элементов в небольшие группы и выбирает максимальные пороговые разности для второй сортировки. Кроме того, максимальные пороговые разности сортируются в буфере и схеме сравнения 102. На выходе процессора 58 выбора I временного и частотного интервала содержится N-максимальные пороговые разности, где N - выбор, произведенный при инициализации системы. Эти М-максимальные пороговые разности подаются на вход оператора характеризации 64 выбора II временного и частотного интервала.

Как видно на примере на Фиг.9, восьми каналам S-1...S-8, изображенным на этой Фиг., будет соответствовать восемь процессоров 58 выбора I временного и частотного интервала, при этом каждый из них имеет N-максимальных пороговых разностных выходных сигналов, подаваемых на оператор характеризации 64 выбора II временного и частотного интервала. Таким образом, оператор характеризации 64 выбора II временного и частотного интервала принимает N-входных сигналов от каждого из восьми отдельных процессоров 58 выбора I временного и частотного интервала. При N равном 10, оператор характеризации 64 выбора II временного и частотного интервала принимает 80 входных сигналов.

Оператор 64 характеризации выбора II временного и частотного интервала аналогичен по своей конструкции процессору 58 выбора I временного и частотного интервала, т.е. N раз 8 входных сигналов в оператор характеризации 64 выбора II буферизуются и сравниваются поочередно аналогично процессу выбора для процессора 58 выбора I временного и частотного интервала. Р-максимальные пороговые разности, подаваемые на вход оператора характеризации 64 выбора II временного и частотного интервала, выводятся как сигнал So (t) для поддиапазонной настройки и характеризации импульсов в сети 20.

Несмотря на то, что в патенте приведено детальное описание изобретения и его преимуществ, специалистам в данной области техники должно быть очевидно, что могут быть предложены различные изменения, замены и модификации, не выходящие за пределы существа и объема изобретения, определенного прилагаемой формулой изобретения и ее эквивалентом.

Импульсный детектор с согласованной матрицей детектирования содержит коллимированный световой пучок, освещающий ячейку Брегга, возбуждаемую входным сигналом, содержащим импульсы различной модуляции, и пространственно-модулирующую коллимированный световой пучок. Бинарная оптическая пластина мультиплицирует изображение ячейки Брегга на непрозрачной пластине, содержащей множество щелей, каждая из которых имеет заданную длину. Оптическая система линз формирует пространственное преобразование Фурье распределения света, в результате чего интенсивность света в фокальной плоскости оптической системы линз пропорциональна энергетической спектральной плотности распределения света в щелях непрозрачной пластины. Детектор/процессор фокальной плоскости, содержащий детекторную матрицу, реагирует на интенсивность воспринимаемого детекторной матрицей света, обрабатывает аналоговые выходные сигналы и преобразует их в команды начальной настройки для детектирования и определения характеристик импульсов во входном сигнале и генерирует выходные сигналы. Обеспечивается реализация алгоритма согласованной матрицы детектирования с использованием гибридного оптического, электрического аналогового и цифрового процессора. 5 н. и 17 з.п. ф-лы, 10 ил.

коллимированный световой пучок;

ячейку Брегга, содержащую апертуру, освещаемую коллимированным световым пучком, возбуждаемую входным сигналом, содержащим импульсы различной модуляции, и пространственно модулирующую коллимированный световой пучок;

непрозрачную пластину, содержащую множество щелей, каждая из которых имеет заданную длину;

бинарную оптическую пластину или голограмму, расположенную в модулированном коллимированном световом пучке для мультиплицирования изображения апертуры ячейки Брегга в плоскости непрозрачной пластины;

оптическую систему линз на пути пространственно модулированного светового пучка, исходящего из непрозрачной пластины, при этом оптическая система линз формирует пространственное преобразование Фурье распределения света, в результате чего интенсивность света в фокальной плоскости оптической системы линз пропорциональна энергетической спектральной плотности распределения света в щелях непрозрачной пластины; и

детектор/процессор фокальной плоскости оптической системы линз, реагирующий на интенсивность света, воспринимаемого детектором/процессором фокальной плоскости, и генерирующий выходные сигналы.

коллимированный световой пучок;

ячейку Брегга, содержащую апертуру, освещаемую коллимированным световым пучком, возбуждаемую входным сигналом, содержащим импульсы различной модуляции, и пространственно модулирующую коллимированный световой пучок;

непрозрачную пластину, содержащую множество щелей, каждая из которых имеет заданную длину;

бинарную оптическую пластину, расположенную в модулированном коллимированном световом пучке для мультиплицирования изображения апертуры ячейки Брегга в плоскости непрозрачной пластины;

оптическую систему линз на пути пространственно модулированного светового пучка, исходящего из непрозрачной пластины, при этом оптическая система линз формирует пространственное преобразование Фурье распределения света, в результате чего интенсивность света в фокальной плоскости оптической системы линз становится пропорциональной энергетической спектральной плотности распределения света в щелях непрозрачной пластины;

детекторную матрицу в фокальной плоскости оптической системы линз, реагирующую на интенсивность света, воспринимаемую детекторной матрицей, и генерирующую выходные сигналы; и

процессор фокальной плоскости, воспринимающий выходные сигналы детекторной матрицы для генерирования выбранных импульсов входного сигнала, время появления, частотный интервал и длительность выбранных импульсов.

интегратор времени для импульсов входного сигнала для дискретизации выбранных импульсов выходных сигналов детектора при выбранной скорости и для генерирования интегрированного по времени выходного сигнала для выбранных выходных импульсов;

частотный интегратор, принимающий выходной сигнал интегратора времени и генерирующий выходной сигнал для входных импульсов, превышающих пороговую величину;

и

селектор команд настройки для выбранных импульсов из множества импульсов входного сигнала для расположения по порядку выходных импульсов интегратора времени с целью идентификации входных импульсов, которые превышают пороговые величины, и расположенные по порядку от максимального до минимального превышения.

коллимированный световой пучок;

ячейку Брегга, освещаемую коллимированным световым пучком и возбуждаемую входным сигналом, содержащим импульсы различной модуляции, и пространственно модулирующую коллимированный световой пучок в ответ на входной сигнал;

непрозрачную пластину, содержащую множество щелей, каждая из которых имеет заданную длину;

первую оптическую систему линз, расположенную на пути пространственно модулированного коллимированного светового пучка для создания изображения светового пучка на плоскости непрозрачной пластины;

бинарную оптическую пластину, расположенную в модулированном коллимированном световом пучке для мультиплицирования изображения ячейки Брегга в плоскости непрозрачной пластины;

вторую оптическую систему линз на пути пространственно модулированного светового пучка, исходящего из непрозрачной пластины, при этом вторая оптическая система линз формирует пространственное преобразование Фурье распределения света, в результате чего интенсивность света в фокальной плоскости второй оптической системы линз становится пропорциональной энергетической спектральной плотности распределения света в щелях непрозрачной пластины; и

детектор/процессор фокальной плоскости второй оптической системы линз, реагирующий на интенсивность света, воспринимаемого детектором/процессором фокальной плоскости, и генерирующий выходной сигнал, идентифицирующий импульсы входного сигнала.

интегратор времени для выбранных импульсов входного сигнала, генерирующий сигнал временного интервала для выбранных импульсов;

частотный интегратор, реагирующий на сигналы временного интервала из интегратора времени, для сравнения с пороговой величиной с целью идентификации входного импульса в полосе частот, соответствующего импульсам, обработанным интегратором времени; и

селектор команд настройки, реагирующий на выходной сигнал интегратора частоты для расположения по порядку импульсов, превышающих пороговые величины, начиная с максимальных величин превышения порога и кончая минимальными.

детекторную матрицу, реагирующую на оптическое изображение импульсов входного сигнала в данной ширине полосы частот;

интегратор времени, соединенный с детекторной матрицей и реагирующий на поступающие от нее сигналы, при этом интегратор времени дискретизирует выходной сигнал детектора с выбранной скоростью и генерирует выходной сигнал, представляющий выборки интегратора времени;

частотный интегратор, соединенный с выходом интегратора времени для сравнения с пороговой величиной с целью идентификации импульсов входного сигнала в полосе частот, соответствующих интегратору времени и генерирующих выходной сигнал, изменяющийся по времени, полосе частот и величине, превышающей пороговую величину; и

селектор команд настройки, соединенный с частотным интегратором и реагирующий на получаемые от него выходные сигналы для расположения идентифицированных импульсов входного сигнала по порядку величин, превышающих пороговые величины, начиная с максимальных величин и кончая минимальными.

дискретизатор для дискретизации выходного сигнала детекторной матрицы с частотой Найквиста или более высокой частотой;

усилитель, соединенный с дискретизатором для усиления дискретизированного выходного сигнала детекторной матрицы;

множество элементов ЗУ, последовательно соединенных вместе с выходом усилителя, множество суммирующих соединений, количество которых меньше на одно соединение, чем множество элементов ЗУ, и соединенных последовательно, в которых первое суммирующее соединение соединено с первым и вторым элементами ЗУ, а каждое последующее суммирующее соединение в последовательности соединено с предшествующим суммирующим соединением и элементом ЗУ; и

мультиплексор, соединенный с первым элементом ЗУ последовательности и с каждым из суммирующих соединений, для мультиплексирования выборок детекторных матриц и подачи с выхода мультиплексированных выборок на частотный интегратор.

детектор, включающий матричную структуру параллельно расположенных детекторных матриц, при этом каждая из детекторных матриц реагирует на импульсы входного сигнала в выбранной ширине полосы частот;

множество интеграторов времени, по отдельности соединенных с одной из детекторных матриц, для дискретизирования сигналов, полученных от нее, с целью идентификации времени появления импульсов во входном сигнале;

множество частотных интеграторов, по отдельности соединенных с одним из интеграторов времени и реагирующих на выходной сигнал, поступающий от него, с целью идентификации импульсов во входном сигнале в диапазоне выбранной полосы частот; и

селектор команд настройки, соединенный с множеством интеграторов времени для размещения по порядку импульсов во входном сигнале от всех детекторных матриц детектора.

| US 5717401 А, 10.02.1998 | |||

| US 5267188 А, 30.11.1993 | |||

| US 6137612 A, 24.10.2000 | |||

| АКУСТООПТИЧЕСКИЙ ПРИЕМНИК | 1998 |

|

RU2134490C1 |

Авторы

Даты

2006-11-27—Публикация

2002-08-22—Подача