Предлагаемое изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен двухступенчатый MS-триггер [авт. свид. СССР №892663, опубл. 23.12.1981], содержащий два основных триггера и один вспомогательный триггер. Однако быстродействие MS-триггера связано с временем срабатывания вспомогательного триггера и коммутирующего ключевого элемента.

Из числа аналогов наиболее близким по технической сущности является двухступенчатый триггер [Edge Trigger Type Flip-Flop, JP 7095013, опубл. 07.04.1995], который и выбран в качестве прототипа. Этот двухступенчатый триггер является более быстродействующим триггером, так как у него отсутствует вспомогательный триггер второй ступени, а два основных триггера поочередно участвуют в приеме и передаче информации.

В состав прототипа входят два D-триггера, двухвходовой мультиплексор, вход синхронизации, информационный вход и информационный выход, являющийся выходом мультиплексора, первый и второй информационные входы которого соединены с прямыми выходами соответствующих триггеров, а адресный вход мультиплексора объединен с прямым входом синхронизации первого триггера и инверсным входом синхронизации второго триггера и является входом синхронизации устройства, причем информационный D-вход устройства соединен с информационными входами D-триггеров.

Работа прототипа определяется функцией переходов D-триггера.

Недостатком прототипа является функциональная ограниченность, связанная с простым поочередным использованием двух триггеров D-типа, участвующих в приеме и передаче информации.

Задачей, на решение которой направлено заявляемое изобретение, является расширение функциональных возможностей за счет параллельной обработки входной и выходной информации при поочередном совмещении процессов обработки и считывания информации.

Техническим результатом являются расширенные функциональные возможности устройства при сохранении двух основных триггеров, обеспечивающих высокое быстродействие работы.

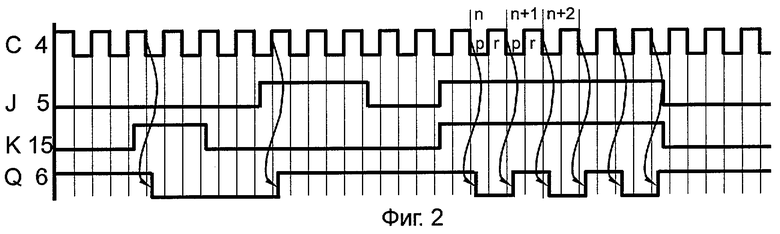

Поставленная задача решается тем, что в двухступенчатый триггер, содержащий первый и второй D-триггеры, двухвходовой мультиплексор, вход синхронизации, информационный вход и информационный выход, являющийся выходом мультиплексора, первый и второй информационные входы которого соединены с прямыми выходами соответствующих D-триггеров, а адресный вход мультиплексора объединен с прямым входом синхронизации первого D-триггера и инверсным входом синхронизации второго D-триггера и является входом синхронизации устройства, введены инвертор, первый, второй, третий, четвертый и пятый двухвходовые элементы И, двухвходовой элемент ИЛИ, трехвходовой элемент ИЛИ и второй информационный вход К, подключенный ко входу инвертора, а первый информационный вход является J-входом устройства и подключен к первым входам второго и пятого элементов И, а также ко второму входу третьего элемента И, при этом вторые входы первого и четвертого элементов И соединены соответственно с прямыми выходами второго и первого D-триггеров, кроме того, второй вход четвертого элемента И объединен со вторым входом пятого элемента И, а первые входы первого, третьего и четвертого элементов И подключены к выходу инвертора, причем выходы первого и второго элементов И соединены соответственно с первым и вторым входами двухвходового элемента ИЛИ, выход которого подключен к информационному входу первого D-триггера, а выходы третьего, четвертого и пятого элементов И соединены соответственно с первым, вторым и третьим входами трехвходового элемента ИЛИ, выход которого подключен к информационному входу второго D-триггера, а инверсный выход этого D-триггера соединен со вторым входом второго элемента И.

Сущность предлагаемого изобретения состоит в создании двухступенчатого JK-триггера с поочередным перекрестным использованием двух основных триггеров с логическими блоками и реализацией параллельного преобразования за счет совмещения во времени (в каждые полтакта) процессов логической обработки входной и выходной информации на одном триггере и считывания выходной информации с другого триггера.

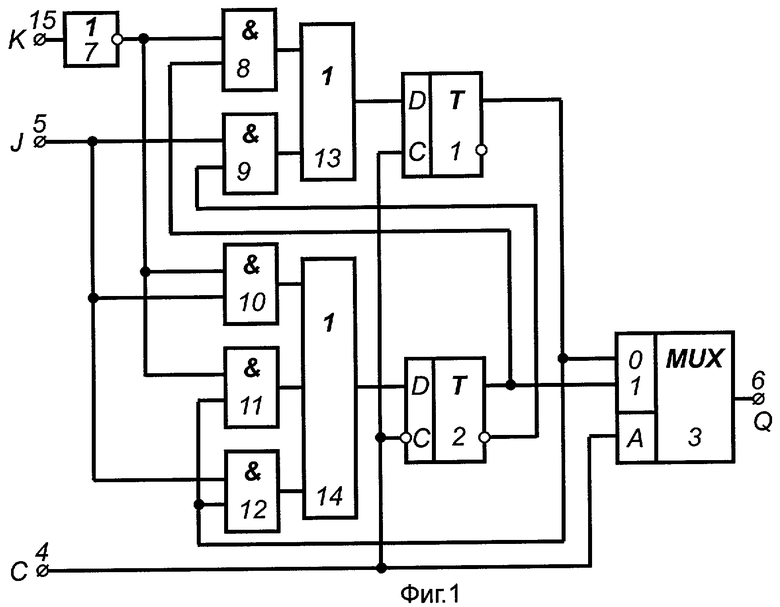

Сущность предлагаемого изобретения поясняется чертежами, где на фиг.1 изображена функциональная схема предлагаемого двухступенчатого JK-триггера, на фиг.2 - временные диаграммы процессов, протекающих в устройстве.

Двухступенчатый триггер (фиг.1) содержит первый 1 и второй 2 D-триггеры, двухвходовой мультиплексор 3, вход синхронизации 4, информационный вход 5 и информационный выход 6, являющийся выходом мультиплексора 3, первый и второй информационные входы которого соединены с прямыми выходами соответствующих D-триггеров 1 и 2, а адресный вход мультиплексора 3 объединен с прямым входом синхронизации первого D-триггера 1, с инверсным входом синхронизации второго D-триггера 2 и является входом синхронизации 4 устройства. Кроме того, устройство содержит инвертор 7, первый 8, второй 9, третий 10, четвертый 11 и пятый 12 двухвходовые элементы И, двухвходовой элемент ИЛИ 13, трехвходовой элемент ИЛИ 14 и второй информационный вход К 15, подключенный ко входу инвертора 7, а первый информационный вход 5 является J-входом устройства и подключен к первым входам второго 9 и пятого 12 элементов И, а также ко второму входу третьего элемента И 10, при этом вторые входы первого 8 и четвертого 11 элементов И соединены соответственно с прямыми выходами второго 2 и первого 1 D-триггеров, кроме того, второй вход четвертого элемента И 11 объединен со вторым входом пятого элемента И 12, а первые входы первого 8, третьего 10 и четвертого 11 элементов И подключены к выходу инвертора 7, причем выходы первого 8 и второго 9 элементов И соединены соответственно с первым и вторым входами двухвходового элемента ИЛИ 13, выход которого подключен к информационному входу первого D-триггера 1, а выходы третьего 10, четвертого 11 и пятого 12 элементов И соединены соответственно с первым, вторым и третьим входами трехвходового элемента ИЛИ 14, выход которого подключен к информационному входу второго D-триггера 2, а инверсный выход этого D-триггера соединен со вторым входом второго элемента И 9.

Устройство работает следующим образом.

Пусть на вход синхронизации 4 устройства поступает синхросигнал С (фиг.2).

При нулевом уровне этого сигнала первый D-триггер 1 находится в состоянии, определенном ранее сигналом с выхода двухвходового элемента ИЛИ 13, и на выход 6 двухступенчатого триггера передается информация с выхода первого D-триггера 1 через мультиплексор 3. Кроме того, эта информация поступает на вторые входы четвертого 11 и пятого 12 элементов И. Входной сигнал с первого 5 информационного входа J подается на первые входы второго 9 и пятого 12 элементов И, а также на второй вход третьего элемента И 10. Входной сигнал со второго 15 информационного входа К через инвертор 7 подается на первые входы первого 8, третьего 10 и четвертого 11 элементов И. В результате сформированы сигналы на выходах третьего 10, четвертого 11 и пятого 12 элементов И, а значит, и на выходе трехвходового элемента ИЛИ 14, и на информационном входе второго D-триггера 2. Этот D-триггер будет находиться в состоянии, определенном его информационным входом. Информация с прямого выхода второго D-триггера 2 поступает на второй вход первого элемента И 8, а на второй вход второго элемента И 9 поступает информация с инверсного выхода этого триггера. В результате будут сформированы сигналы на выходах первого 8 и второго 9 элементов И, а значит, и на выходе двухвходового элемента ИЛИ 13, и на информационном входе первого D-триггера 1.

При смене синхросигнала на единичный уровень (фиг.2) первый D-триггер 1 перейдет в состояние, определенное к этому времени на его информационном входе, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода второго D-триггера 2 через мультиплексор 3. При этом информация с прямого выхода первого D-триггера 1 поступает на вторые входы четвертого 11 и пятого 12 элементов И. В результате будут сформированы сигналы на выходах третьего 10, четвертого 11 и пятого 12 элементов И, а значит, и на выходе трехвходового элемента ИЛИ 14, и на информационном входе второго D-триггера 2.

При смене синхросигнала на нулевой уровень (фиг.2) второй D-триггер 2 перейдет в состояние, определенное к этому времени на его информационном входе, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода первого D-триггера 1 через мультиплексор 3. При этом информация с прямого выхода второго D-триггера 2 поступает на второй вход первого элемента И 8, а на второй вход второго элемента И 9 поступает информация с инверсного выхода второго D-триггера 2. В результате будут сформированы сигналы на выходах первого 8 и второго 9 элементов И, а значит, и на выходе двухвходового элемента ИЛИ 13, и на информационном входе первого D-триггера 1.

Далее, при смене синхросигнала на единичный уровень, процесс повторяется (фиг.2).

Таким образом, смена состояний второго D-триггера 2 происходит при нулевом уровне синхросигнала, а смена состояний первого D-триггера 1 - при единичном уровне синхросигнала. В целом, для двухступенчатого триггера смена состояний происходит после перепада синхросигнала.

Состояние первого D-триггера 1 определяется в зависимости от входных информационных сигналов J, К и состояния второго D-триггера 2.

Пусть на первый 5 и второй 15 информационные входы J и К поступают входные сигналы 0 и 0 соответственно, то есть J=0, K=0. Наличие нулевого сигнала J на первом входе второго элемента И 9 обеспечит нулевой сигнал на выходе этого элемента и на втором входе двухвходового элемента ИЛИ 13. Нулевой сигнал К на входе первого инвертора 7 преобразуется в единичный сигнал на его выходе и на первом входе первого элемента И 8. В результате значение выходного сигнала первого элемента И 8 будет зависеть только от второго входа этого элемента, то есть от значения сигнала на прямом выходе второго D-триггера 2, и будет передаваться на первый вход двухвходового элемента ИЛИ 13. Таким образом, учитывая, что на втором входе двухвходового элемента ИЛИ 13 присутствует нулевой сигнал, выходной сигнал двухвходового элемента ИЛИ 13, а значит, и входной информационный сигнал первого D-триггера 1 будет повторять выходной сигнал прямого выхода второго D-триггера 2.

Аналогично наличие нулевого сигнала J на втором входе третьего элемента И 10 и на первом входе пятого элемента И 12 обеспечит нулевые сигналы на выходах этих элементов и на первом и третьем входах трехвходового элемента ИЛИ 14. Нулевой сигнал К на входе первого инвертора 7 преобразуется в единичный сигнал на его выходе и на первых входах третьего 10 и четвертого 11 элементов И. В результате значение выходного сигнала четвертого элемента И 11 будет зависеть только от второго входа этого элемента, то есть от значения сигнала на прямом выходе первого D-триггера 1, и будет передаваться на второй вход трехвходового элемента ИЛИ 14. Таким образом, учитывая, что на первом и третьем входах трехвходового элемента ИЛИ 14 присутствует нулевой сигнал, выходной сигнал трехвходового элемента ИЛИ 14, а значит, и входной информационный сигнал второго D-триггера 2 будет повторять выходной сигнал прямого выхода первого D-триггера 1.

Следовательно, при комбинации входных сигналов J=0, K=0 двухступенчатый триггер будет сохранять свое предыдущее состояние при любой смене синхросигнала.

Пусть на первый 5 и второй 15 информационные входы J и К поступают входные сигналы 0 и 1 соответственно, то есть J=0, K=1. Наличие нулевого сигнала J на первом входе второго элемента И 9 обеспечит нулевой сигнал на выходе этого элемента и на втором входе двухвходового элемента ИЛИ 13. Единичный сигнал К на входе первого инвертора 7 преобразуется в нулевой сигнал на его выходе и на первом входе первого элемента И 8. В результате значение выходного сигнала первого элемента И 8 будет нулевым и будет передаваться на первый вход двухвходового элемента ИЛИ 13. Таким образом, учитывая, что на первом и втором входах двухвходового элемента ИЛИ 13 присутствуют нулевые сигналы, выходной сигнал двухвходового элемента ИЛИ 13, а значит, и входной информационный сигнал первого D-триггера 1 будет нулевым.

Наличие нулевого сигнала J на втором входе третьего элемента И 10 и на первом входе пятого элемента И 12 обеспечит нулевые сигналы на выходах этих элементов и на первом и третьем входах трехвходового элемента ИЛИ 14. Единичный сигнал К на входе первого инвертора 7 преобразуется в нулевой сигнал на его выходе и на первых входах третьего 10 и четвертого 11 элементов И. В результате значение выходных сигналов третьего 10 и четвертого 11 элементов И будет нулевым и будет передаваться на первый и второй входы трехвходового элемента ИЛИ 14. Таким образом, учитывая, что на первом, втором и третьем входах трехвходового элемента ИЛИ 14 присутствуют нулевые сигналы, выходной сигнал трехвходового элемента ИЛИ 14, а значит, и входной информационный сигнал второго D-триггера 2 будет нулевым.

Следовательно, при комбинации входных сигналов J=0, K=1 двухступенчатый триггер будет иметь нулевое состояние при любой смене синхросигнала.

Пусть на первый 5 и второй 15 информационные входы J и К поступают входные сигналы 1 и 0 соответственно, то есть J=1, K=0. На первом входе второго элемента И 9 будет присутствовать единичный сигнал. Нулевой сигнал К на входе инвертора 7 преобразуется в единичный сигнал на его выходе и на первом входе первого элемента И 8. Так как на второй вход первого элемента И 8 поступает информация с прямого выхода второго D-триггера 2, а на второй вход второго элемента И 9 - информация с инверсного выхода этого же D-триггера 2, то на выходе одного из этих элементов И обязательно будет присутствовать единичный сигнал, который будет передаваться на один из входов двухвходового элемента ИЛИ 13. Таким образом, выходной сигнал двухвходового элемента ИЛИ 13, а значит, входной информационный сигнал первого D-триггера 1 будет единичным.

Аналогично на втором входе третьего элемента И 10 будет присутствовать единичный сигнал. Нулевой сигнал К на входе инвертора 7 преобразуется в единичный сигнал на его выходе и на первом входе третьего элемента И 10. В результате на выходе этого элемента И сформируется единичный сигнал, который будет передаваться на первый вход трехвходового элемента ИЛИ 14. Таким образом, выходной сигнал трехвходового элемента ИЛИ 14, а значит, входной информационный сигнал второго D-триггера 2 будет единичным.

Следовательно, при комбинации входных сигналов J=1, К=0 двухступенчатый триггер будет иметь единичное состояние при любой смене синхросигнала.

Пусть на первый 5 и второй 15 информационные входы J и К поступают входные сигналы 1 и 1 соответственно, то есть J=1, К=1. На первом входе второго элемента И 9 будет присутствовать единичный сигнал. Единичный сигнал К на входе первого инвертора 7 преобразуется в нулевой сигнал на его выходе и на первом входе первого элемента И 8. В результате значение выходного сигнала первого элемента И 8 будет нулевым и будет передаваться на первый вход двухвходового элемента ИЛИ 13. Значение выходного сигнала второго элемента И 9 будет зависеть только от второго входа этого элемента, то есть от инверсного выхода второго D-триггера 2, и будет передаваться на второй вход двухвходового элемента ИЛИ 13. Таким образом, учитывая, что на первом входе двухвходового элемента ИЛИ 13 присутствует нулевой сигнал, выходной сигнал двухвходового элемента ИЛИ 13, а значит, и входной информационный сигнал первого D-триггера 1 будет повторять выходной сигнал инверсного выхода второго D-триггера 2.

Аналогично на втором входе третьего элемента И 10 и на первом входе пятого элемента И 12 будет присутствовать единичный сигнал. Единичный сигнал К на входе первого инвертора 7 преобразуется в нулевой сигнал на его выходе и на первых входах третьего 10 и четвертого 11 элементов И. В результате значение выходных сигналов третьего 10 и четвертого 11 элементов И будет нулевым и будет передаваться на первый и второй входы трехвходового элемента ИЛИ 14 соответственно. Значение выходного сигнала пятого элемента И 12 будет зависеть только от второго входа этого элемента, то есть от прямого выхода первого D-триггера 1, и будет передаваться на третий вход трехвходового элемента ИЛИ 14. Таким образом, учитывая, что на первом и втором входах трехвходового элемента ИЛИ 14 присутствуют нулевые сигналы, выходной сигнал трехвходового элемента ИЛИ 14, а значит, и входной информационный сигнал второго D-триггера 2 будет повторять выходной сигнал прямого выхода первого D-триггера 1.

При нулевом уровне синхросигнала первый D-триггер 1 находится в состоянии, определенном ранее сигналом с выхода двухвходового элемента ИЛИ 13, и на выход 6 двухступенчатого триггера передается информация с выхода первого D-триггера 1 через мультиплексор 3.

При смене синхросигнала на единичный уровень первый D-триггер 1 перейдет в противоположное состояние, определенное к этому времени на его информационном входе, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода второго D-триггера 2 через мультиплексор 3, то есть предыдущее состояние.

При смене синхросигнала на нулевой уровень второй D-триггер 2 примет состояние первого D-триггера 1, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода первого D-триггера 1 через мультиплексор 3, то есть новое инверсное состояние.

При смене синхросигнала на единичный уровень первый D-триггер 1 опять перейдет в противоположное состояние, определенное к этому времени на его информационном входе, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода второго D-триггера 2 через мультиплексор 3, то есть предыдущее инверсное состояние.

При смене синхросигнала на нулевой уровень второй D-триггер 2 снова примет состояние первого D-триггера 1, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода первого D-триггера 1 через мультиплексор 3, то есть новое инверсное состояние, которое соответствует исходному состоянию.

При смене синхросигнала на единичный уровень первый D-триггер 1 опять перейдет в противоположное состояние, определенное к этому времени на его информационном входе, а на выход 6 двухступенчатого триггера будет передаваться информация с прямого выхода второго D-триггера 2 через мультиплексор 3, то есть предыдущее состояние, которое соответствует исходному состоянию.

Далее процесс повторяется.

Следовательно, при комбинации входных сигналов J=1, K=1 двухступенчатый триггер будет менять свое состояние на противоположное после двойной смены синхросигнала.

В основу работы двухступенчатого триггера положен принцип поочередной перекрестной логической обработки входной и выходной информации триггеров при приеме и передаче, благодаря чему в каждые полтакта в зависимости от функции логической обработки информации поочередно на одном триггере реализуется функция триггера, а с другого триггера выполняется считывание информации.

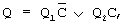

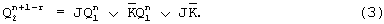

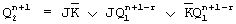

Логическое выражение для информационного выхода 6 двухступенчатого триггера имеет вид:

где Q1 - выходной сигнал первого D-триггера 1,

Q2 - выходной сигнал второго D-триггера 2,

С - синхросигнал.

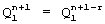

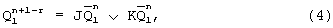

Функциональная характеристика двухступенчатого триггера по выходу 6 определяется выражением:

где  - выходной сигнал первого D-триггера 1 на очередном (n+1)-ом такте синхросигнала в течение действия его нулевого уровня от n+1 до n+1+p;

- выходной сигнал первого D-триггера 1 на очередном (n+1)-ом такте синхросигнала в течение действия его нулевого уровня от n+1 до n+1+p;

- выходной сигнал второго D-триггера 2 на очередном (n+1)-ом такте синхросигнала в течение действия его единичного уровня от n+1+p до n+1+p+r;

- выходной сигнал второго D-триггера 2 на очередном (n+1)-ом такте синхросигнала в течение действия его единичного уровня от n+1+p до n+1+p+r;

р - часть периода синхросигнала, определяемая действием его нулевого уровня;

r - часть периода синхросигнала, определяемая действием его единичного уровня;

p+r=1 - период синхросигнала, определяемый действием его нулевого и единичного уровней (см. фиг.2).

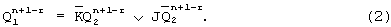

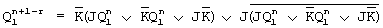

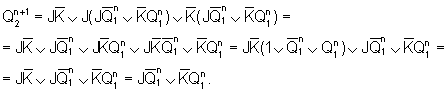

При этом состояние первого D-триггера 1 было сформировано в предыдущем такте синхросигнала в течение действия его единичного уровня от n+р до n+р+r:

Формирование состояния первого D-триггера 1 в предыдущем такте синхросигнала в течение действия его единичного уровня от n+р до n+р+r определялось логической функцией на информационном входе первого D-триггера 1:

При этом состояние второго D-триггера 2 было сформировано в предыдущем такте синхросигнала в течение действия его нулевого уровня от n до n+р:

или

или

Полученное выражение 3 подставляем в выражение 2

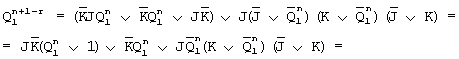

и выполняем логические преобразования для упрощения выражения:

Таким образом,

то есть

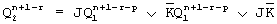

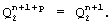

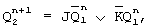

Для функциональной характеристики 1 двухступенчатого триггера по выходу 6 состояние второго D-триггера 2 было сформировано в текущем (n+1)-ом такте синхросигнала в течение действия его нулевого уровня от n+1 до n+1+р:

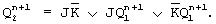

Формирование состояния второго D-триггера 2 в текущем такте синхросигнала в течение действия его нулевого уровня от n+1 до n+1+р определялось логической функцией на информационном входе второго D-триггера 2:

При этом состояние первого D-триггера 1 было сформировано в предыдущем такте синхросигнала в течение действия его единичного уровня от n+р до n+р+r, то есть до n+1:

Следовательно,

Подставляя выражение 4, характеризующее состояние  , можно получить выражение для состояния второго D-триггера 2:

, можно получить выражение для состояния второго D-триггера 2:

Таким образом,

то есть

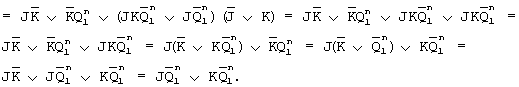

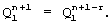

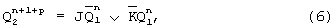

Подставляя выражения 5 и 6 в выражение 1, получаем функциональную характеристику двухступенчатого триггера по выходу 6:

или

или

Как известно, это выражение соответствует характеристическому уравнению двухступенчатого триггера JK-типа [Агаханян, Т.М. Интегральные триггеры устройств автоматики [Текст]: / Т.М.Агаханян, С.П.Плеханов; - М.: Машиностроение, 1978, - 368 с.: ил. - Библиогр.: с.22].

Таким образом, предложенный двухступенчатый ММ-триггер обладает расширенными функциональными возможностями при сохранении двух основных триггеров, обеспечивающих высокое быстродействие работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХСТУПЕНЧАТЫЙ ТРИГГЕР | 2014 |

|

RU2542575C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Делитель частоты с переменным коэффициентом деления | 2020 |

|

RU2752485C1 |

| НЕЛИНЕЙНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 2000 |

|

RU2185022C1 |

| ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 2000 |

|

RU2171011C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| Устройство для определения экстремума | 1988 |

|

SU1603341A1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2014736C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Технический результат заключается в расширении функциональных возможностей при сохранении двух основных триггеров, обеспечивающих высокое быстродействие работы. Двухступенчатый триггер (фиг.1) содержит D-триггеры (1, 2), двухвходовой мультиплексор (MX) (3), вход синхронизации (4), информационный вход (5) и информационный выход (6), являющийся выходом MX (3), информационные входы которого соединены с прямыми выходами соответствующих D-триггеров (1 и 2), а адресный вход MX (3) объединен с прямым входом синхронизации D-триггера (1), с инверсным входом синхронизации D-триггера (2) и является входом синхронизации (4) устройства. Кроме того, устройство содержит инвертор (7), двухвходовые элементы И (8, 9, 10, 11, 12), двухвходовой элемент ИЛИ (13), трехвходовой элемент ИЛИ (14) и второй информационный вход К (15), подключенный ко входу инвертора (7). 2 ил.

Двухступенчатый триггер, содержащий первый и второй D-триггеры, двухвходовой мультиплексор, вход синхронизации, информационный вход и информационный выход, являющийся выходом мультиплексора, первый и второй информационные входы которого соединены с прямыми выходами соответствующих D-триггеров, а адресный вход мультиплексора объединен с прямым входом синхронизации первого D-триггера и инверсным входом синхронизации второго D-триггера и является входом синхронизации устройства, отличающийся тем, что в устройство введены инвертор, первый, второй, третий, четвертый и пятый двухвходовые элементы И, двухвходовый элемент ИЛИ, трехвходовый элемент ИЛИ и второй информационный вход К, подключенный ко входу инвертора, а первый информационный вход является J-входом устройства и подключен к первым входам второго и пятого элементов И, а также ко второму входу третьего элемента И, при этом вторые входы первого и четвертого элементов И соединены соответственно с прямыми выходами второго и первого D-триггеров, кроме того, второй вход четвертого элемента И объединен со вторым входом пятого элемента И, а первые входы первого, третьего и четвертого элементов И подключены к выходу инвертора, причем выходы первого и второго элементов И соединены соответственно с первым и вторым входами двухвходового элемента ИЛИ, выход которого подключен к информационному входу первого D-триггера, а выходы третьего, четвертого и пятого элементов И соединены соответственно с первым, вторым и третьим входами трехвходового элемента ИЛИ, выход которого подключен к информационному входу второго D-триггера, а инверсный выход этого D-триггера соединен со вторым входом второго элемента И.

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| MS-триггер | 1979 |

|

SU892663A1 |

| Триггер | 1979 |

|

SU790129A1 |

| US 6300809 В1, 09.10.2001 | |||

| US 5327019 А, 05.07.1994 | |||

| US 5250858 A, 05.10.1993 | |||

| US 4873456, 10.10.1989. | |||

Авторы

Даты

2007-02-27—Публикация

2005-07-28—Подача