1

Изобретение относится к вычислительной технике.

Известен триггер, содержащий два логических элемента И-НЕ и две цепи обратной связи Ij .

Известен также триггер, содержащий два логических элемента, две цепи обратной связи, элемент И-HE.pJ

Недостатком известных устройств являются узкие функционгшьные возможности, они не могут выполнять задачи управления прохождением потоков информации.

Цель изобретения - расширение функциональных возможностей триггера.

Для достижения поставленной цели в триггере, содержащем два логических элемента, две цепи обратной связи, элемент И-НЕ, в качестве логических элементов использованы мультиплексоры, информационные и селекторные входы которых подключены к соответствующим входг1М триггера, прямой выход первого мультиплексора через первую цепь обратной связи соединен со входом разрешение второго мультиплексора, инверсный выход которого через вторую цепь обратной связи .подключен к первому входу элемента И-HE второй вход

которого подключен к входу начальной установки триггера, а выход соединен со входом разрешение первого мультиплексора, причем в качестве.

5 мультиплексоров использованы программиpye в Ie мультиплексоры.

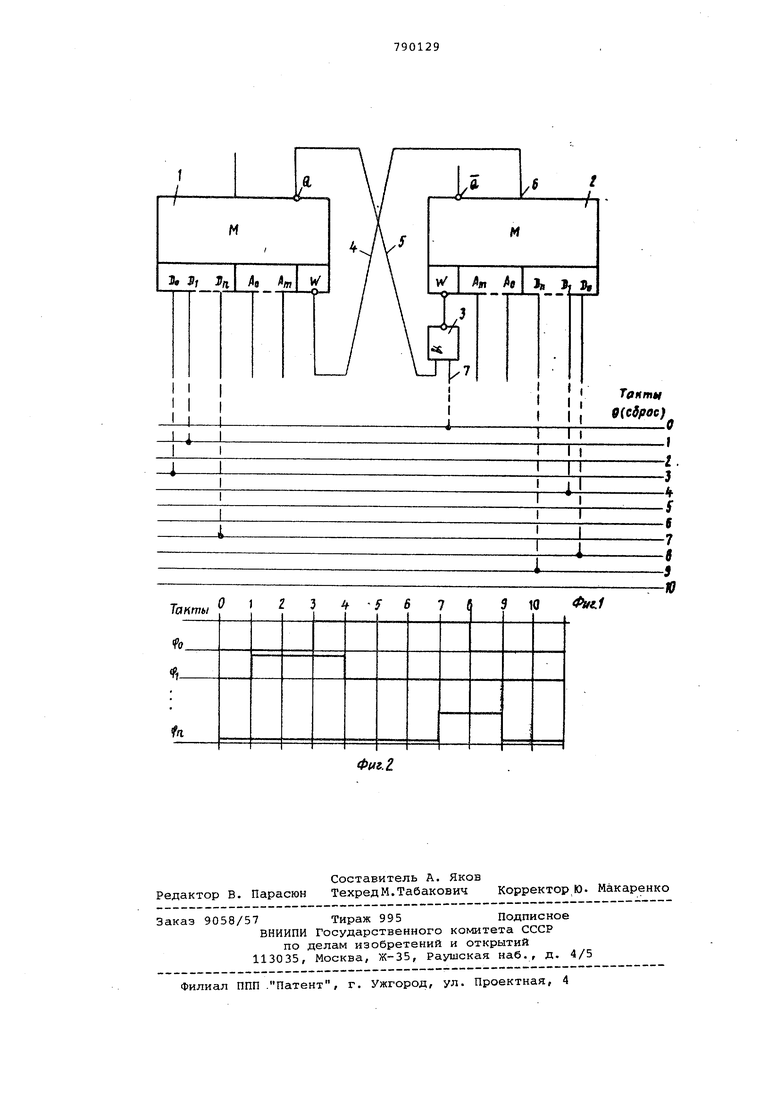

На фиг. 1 приведена принципиальная схема предлагаемого триггера , на фиг. 2 - временные диаграммы раfO боты триггера.

Предлагаемый триггер с прямым выходом Q и инверсным выходом Q содержит два мультиплексора 1 и 2

5 с информационными входг ли D,, селекторными входами Aq- А,, входом разрешение W, элемент И-НЕ 3, цепь 4- и 5 обратной связи,- прямой выход б мультиплексора, вход 7 начальной установки, Показанные на фиг. 2 шины ТАКТ 0: ТАКТ 10, по которым соответственно проходят отрицательные тактовые импульсы O-jlO, в состав триггера не входят,

25 а приведены для описания одной из функциональных возможностей триггера. 0 0 мультиплексора 1 - информационные входы установки триггера, входы Оц-т D мультиплек- .

30 сора 2 - информационные входы сброса триггера. На селекторные входы мультиплексоров 1,2, А„ подается например, код определенной разрядности. Триггер работает следующим образом. В исходном состоянии как на активных выбранных , так и на пассивных (не выбранных) входах мультиплексоров 1,2 - 1. При подаче О на вход 7 триггера на прямом выходе 6 мультиплексора 2 появится О, на выходе триггера Q также установится О. Это состояние принудительной установки - устойчивое, т.к. 1 на входе W мультиплексора 2 сохраняется и при снятии О со входа 7 начальной установки за счет цепи 4 обратной связи. Триггер готов к работе. При подаче О на активный вход мультиплексора 1 на выходе триг Ъера Q устанавливается 1, на входе W мультиплексора 2 - О, на входе Q - О, на прямом выходе 6 мультиплексора 2 - 1. Наступило устойчивое состояние триггера за сче цепи 5 обратной связи и при снятии О с активного входа мультиплексора 1.При последующей подаче О на активный вход мультиплексора 2 на вы ходе Q устанавливается 1, -на выходе 6 - О, на выходе Q снова устанавливается устойчивое состояние О за счет цепи 5 обратной связи и при снятии О с активного входа мультиплексора 2. Меняя активные информационные входы мультиплексоров при помощи селекторных входов Л, можно одновременно управлять прохождением потоков информации, запрог раммировав подключение входов DO , D. -f Dp, триггера к шинам тактовых импульсов, а вход 7 подключив к шине сброса такт О , как показано пунктиром на фиг. 1. Если активными являются входы DO мультиплекторов 1, 2,то после принудительной установки триггера тактом О {Q 0) с приходом такта 3 триггер взводится (Q 1), с приходом такта 8 триггер сбрасывается (Q 0). Таким образом на выходе триггера О формируется фазный сигнал4о . Если активными являются входы D мультиплекторов, то на выходе триггера Q формируется фазный сигнал и т.д. При этом тактовые импульсы Oбecпeчивaют синхронную работу при формировании фазных сигналов .При повышении класса решаемых задач управления прохождением потоков информации целесообразно применять программируемые мультиплексоры. Формула изобретения 1.Триггер, содержащий два логических элемента, две цепи обратной связи и элемент И-НЕ, отличающийся тем, что, с целью расширения функциональных возможностей триггера, в качестве логических элементов использованы мультиплексоры, информационные и селекторные входы которых подключены к соответствующим входам триггера, прямой выход первого мультиплексора через первую цепь обратной связи соединен со входом разрешение второго мультиплексора, инверсный выход которого через вторую цепь обратной связи подключен к первому входу элемента И-НЕ, второй вход которого подключен ко входу начальной установки триггера, а выход соединен со входом разрешение первого мультиплектора. 2.Триггер по п. 1, отличающийся тем, что в качестве мультиплексоров использованы программируемые мультиплекторы. Источники информации, принятые во внимание при экспертизе 1.Алексенко Д.Г. Основы микросхемотехники. М., Советское радио, 1977, с. 106, рис. 4,2,1. 2.Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств, М., Советское радио, 1975, с. 62, рис. 2, 96. Лв т 3 У, ISft 3 I I IТамтц I I д(ебрас) 10

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерное устройство | 1979 |

|

SU841089A1 |

| Распределитель импульсов для управления четырехфазным шаговым двигателем | 1990 |

|

SU1711317A1 |

| Устройство для программного управления шаговым двигателем | 1989 |

|

SU1675850A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Распределитель импульсов для управления шаговым двигателем | 1986 |

|

SU1427545A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU993428A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| Устройство дефектоскопического контроля планарных структур | 1987 |

|

SU1460610A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1997 |

|

RU2125762C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Авторы

Даты

1980-12-23—Публикация

1979-02-23—Подача