Изобретение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах, устройствах обработки аудио и видео сигналов, а также при первичной обработке сигналов фазированных антенных решеток радаров.

Известно устройство [RU Патент №2015539, опубл. 30.06.94] для деления частоты с переменным коэффициентом деления, содержащее n-разрядный двоичный счетчик, входы синхронизации, разрешения счета, установки в начальное состояние и разрешения деления, являющиеся соответствующими входами счетчика, выход переполнения, являющийся соответствующим выходом счетчика, n-разрядная шина управления, информационный выход делителя частоты, n логических элементов с функцией И, первые входы которых соединены соответственно с прямыми разрядными выходами n-разрядного счетчика, а вторые входы этих элементов соединены с n-разрядами шины управления в обратном порядке, причем делитель частоты содержит также двухвходовой элемент И-НЕ, а логические элементы с функцией И по двум входам реализуют еще функцию 2ИЛИ, по выходам - функцию НЕ, составляя таким образом функцию 2ИЛИ-И-НЕ, кроме того, первый вход элемента И-НЕ соединен с выходом первого логического элемента, составляющего функцию 2ИЛИ-И-НЕ, а второй вход - с инверсным выходом синхронизации двоичного счетчика, при этом выход элемента И-НЕ является информационным выходом делителя частоты, выход расширения которого соединен с выходом первого логического элемента 2ИЛИ-И-НЕ, третьи входы всех логических элементов 2ИЛИ-И-НЕ соединены соответственно с инверсными разрядными выходами n-разрядного двоичного счетчика, четвертый вход i-го элемента 2ИЛИ-И-НЕ (i=1, n-1) соединен с выходом (i+1)-го элемента 2ИЛИ-И-НЕ, четвертый вход n-го элемента 2ИЛИ-И-НЕ является входом расширения делителя частоты, причем первые и вторые входы всех логических элементов 2ИЛИ-И-НЕ относятся к первому элементу ИЛИ, а третьи и четвертые входы - ко второму элементу ИЛИ.

Устройство осуществляет деление за счет последовательного преобразования потенциальных (по отношению к сигналу на входе синхронизации) управляющих сигналов с шины управления и от разрядов счетчика на элементах 2ИЛИ-И-НЕ, включенных последовательно, с выделением выходного информационного сигнала из потенциального (по отношению к сигналу на входе синхронизации) сигнала на выходе расширения делителя. Сигнал на выходе расширения получается путем последовательного преобразования с использованием элементов 2ИЛИ-И-НЕ сигналов от прямого и инверсного выходов разряда счетчика, сигнала с шины управления и сигнала с выхода последующего элемента 2ИЛИ-И-НЕ. Элементы 2ИЛИ-И-НЕ образуют итеративную (последовательную) цепочку, в которой на каждом элементе на первой ступени в первой паре сигнал с выхода каждого последующего элемента преобразуется с сигналом с инверсного выхода счетчика, во второй паре сигнал с шины управления преобразуется с сигналом от прямого выхода счетчика, причем на нечетный элемент 2ИЛИ-И-НЕ поступает инверсный управляющий сигнал с шины управления, а на четный - прямой сигнал с шины управления, затем на второй ступени сигналы обеих пар преобразуются в сигнал выхода элемента 2ИЛИ-И-НЕ.

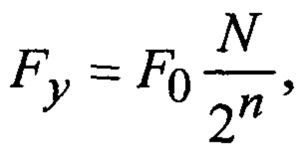

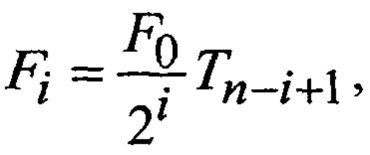

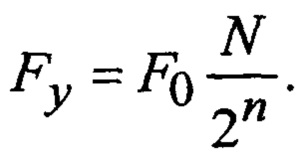

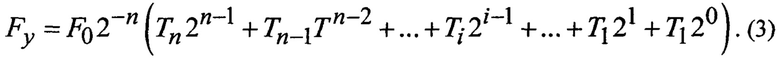

Средняя частота Fy импульсной последовательности на выходе элемента И-НЕ, то есть на выходе устройства, определяется выражением

где N - код, поступающий по n-разрядной шине управления,

F0 - - частота, поступающая на вход синхронизации.

Недостатком этого устройства является большое время преобразования, связанное с последовательной обработкой сигналов.

Из числа аналогов наиболее близким по технической сущности является делитель частоты с переменным коэффициентом деления [RU Патент №2273043, опубл. 27.03.2006], который и выбран в качестве прототипа. В прототипе повышено быстродействие работ устройства при упрощении коммутации формирователя информационного сигнала.

Делитель частоты с переменным коэффициентом деления содержит элемент ИЛИ с n входами, вход синхронизации, n логических элементов L с функцией И, первые входы которых соединены с n-разрядами шины управления в обратном порядке, а выходы элементов L подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты.

Кроме того, устройство содержит два n-разрядных двоичных счетчика, объединенные входы разрешения счета, установки в начальное состояние и разрешения деления, являющиеся соответствующими входами счетчиков, выход переполнения, являющийся соответствующим выходом первого счетчика, при этом вход синхронизации устройства соединен с входом синхронизации первого счетчика, а вход синхронизации второго счетчика соединен с инверсным выходом тактовой частоты первого счетчика.

Прототип работает следующим образом.

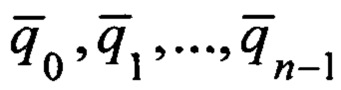

На вход синхронизации счетчика поступает импульсная (тактовая) последовательность с частотой F0. На входы разрешения счета и деления поступают разрешающие сигналы. С помощью сигнала установки в начальное состояние счетчики сбрасываются: выходы Q0, Q1, …, Qn-1 устанавливаются в ноль, а выходы  - в единицу.

- в единицу.

При появлении на входе синхронизации импульсов тактовой частоты F0 начинается одновременная работа счетчиков, причем их состояние отличается на пол такта. За эти пол такта выполняется выделение разряда, в котором происходит изменение состояния из нуля в единицу, и формируется единичный импульс. Этот импульс пропускается на выход сигналом разрешения, который при наличии единицы на соответствующем разряде шины, управляет прохождением импульсов на выход. Управление прохождением импульсов на выход осуществляется сигналами шины управления в обратном порядке.

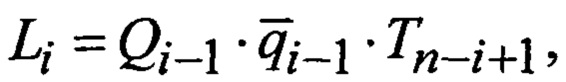

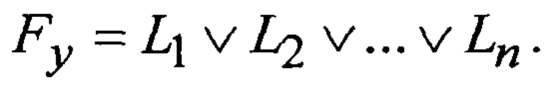

Логическое выражение для выхода Fy имеет вид:

где функция L в общем случае  a i - номер разряда шины управления (от 1 до n).

a i - номер разряда шины управления (от 1 до n).

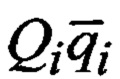

Очевидно, что для любого i равенство единице  достигается при одновременном равенстве единице Qi, и

достигается при одновременном равенстве единице Qi, и  Такая ситуация возникает для каждого единичного состояния Qi в течение времени длительности импульса тактовой частоты τ только при начале этого единичного состояния. Это связано с тем, что переход состояния

Такая ситуация возникает для каждого единичного состояния Qi в течение времени длительности импульса тактовой частоты τ только при начале этого единичного состояния. Это связано с тем, что переход состояния  из единицы в ноль сдвинут на время (относительно перехода Qi из нуля в единицу), и обеспечено тактированием второго счетчика инверсным выходом синхронизации первого счетчика, то есть сигналом

из единицы в ноль сдвинут на время (относительно перехода Qi из нуля в единицу), и обеспечено тактированием второго счетчика инверсным выходом синхронизации первого счетчика, то есть сигналом  На выходе любого логического элемента Li будет формироваться импульсная последовательность с частотой

На выходе любого логического элемента Li будет формироваться импульсная последовательность с частотой

где Ti={0;1} - логическое состояние i-x разрядов кодов управления N.

Импульсы в этих последовательностях разнесены по времени, поэтому на выходе логического элемента ИЛИ, являющегося выходом устройства в целом, происходит формирование суммарной частоты, среднее значение которой, как и у аналога, имеет вид

Недостатком прототипа является сложность, связанная с необходимостью работы двух n-разрядных двоичных счетчиков, управляемых уровнем. Такие счетчики строятся на базе двухступенчатых триггеров, то есть, количество одноступенчатых триггеров, необходимых для реализации n-разрядного счетчика составляет 2n триггеров, а для реализации прототипа с двумя счетчиками потребуется 4n триггеров.

Задачей, на решение которой направлено заявляемое изобретение, является упрощение устройства за счет использования двух n-разрядных линеек одноступенчатых триггеров, то есть используется 2n триггеров, вместо двух n-разрядных двухступенчатых двоичных счетчиков со статическим управлением, для реализации которых необходимо использовать 4n триггеров.

Техническим результатом является сокращение аппаратных затрат при реализации делителя частоты.

Поставленная задача решается тем, что в делитель частоты с переменным коэффициентом деления, содержащий элемент ИЛИ с n входами, вход синхронизации, n логических элементов L с функцией И, первые входы которых соединены с n-разрядами шины управления в обратном порядке, а выходы элементов L подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты, введены первая линейка n одноступенчатых D-триггеров с прямыми динамическими тактовыми входами, вторая линейка n одноступенчатых D-триггеров с инверсными статическими входами установки в «1» и с прямыми динамическими тактовыми входами, которые у этих триггеров объединены и подключены к входу синхронизации, а также к динамическому тактовому входу первого триггера первой линейки, прямой выход которого соединен со вторым входом первого логического элемента L и с D-входом первого триггера второй линейки, а инверсный выход первого триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу второго триггера первой линейки, прямой выход которого соединен со вторым входом второго логического элемента L и D-входом второго триггера второй линейки, а инверсный выход второго триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу третьего триггера первой линейки, прямой выход которого соединен со вторым входом третьего логического элемента L и D-входом третьего триггера второй линейки, а инверсный выход третьего триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу следующего триггера первой линейки, прямой выход которого соединен со вторым входом следующего логического элемента L и D-входом следующего триггера второй линейки, а инверсный выход следующего триггера первой линейки подключен к D-входу этого триггера, при этом связи последующих элементов соответственно повторяются до последних n элементов в каждой линейке, а инверсные выходы D-триггеров второй линейки подключены соответственно к третьим входам логических элементов L.

Сущность предлагаемого изобретения состоит в создании делителя частоты с переменным коэффициентом деления и реализацией выявления импульса на выходе первой линейки триггеров на основании анализа состояния на предыдущем и последующем тактах работы устройства.

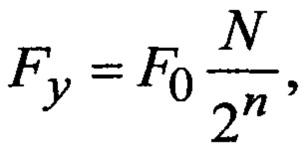

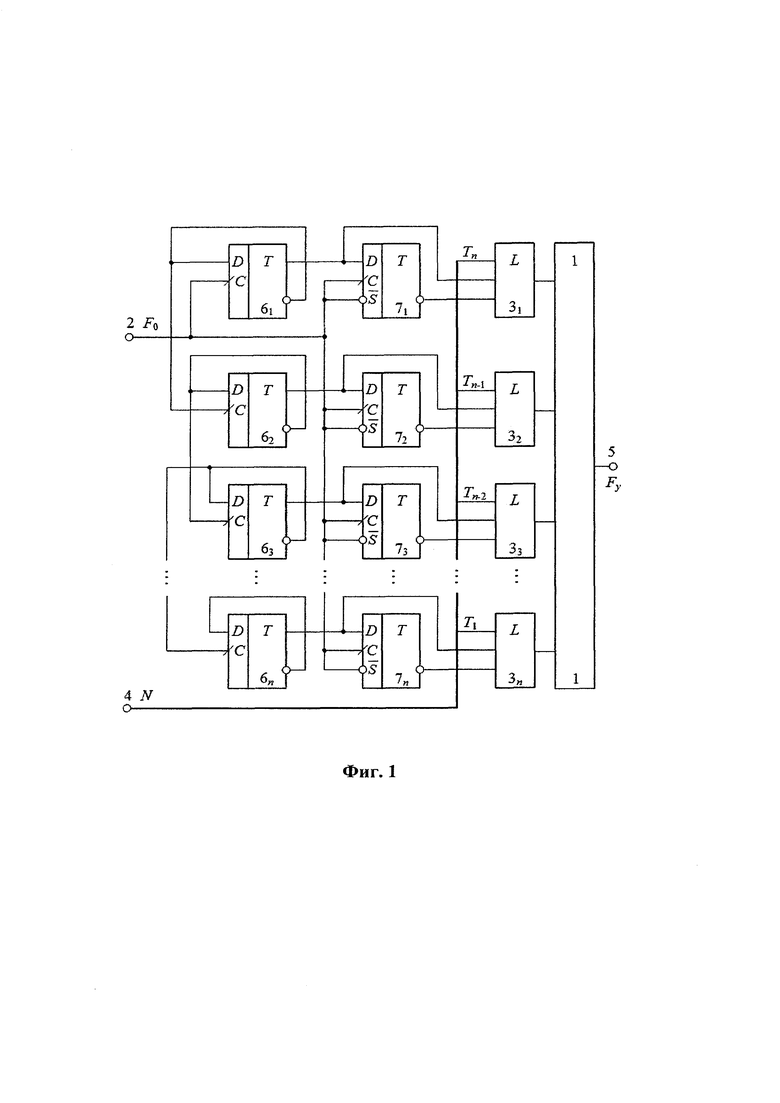

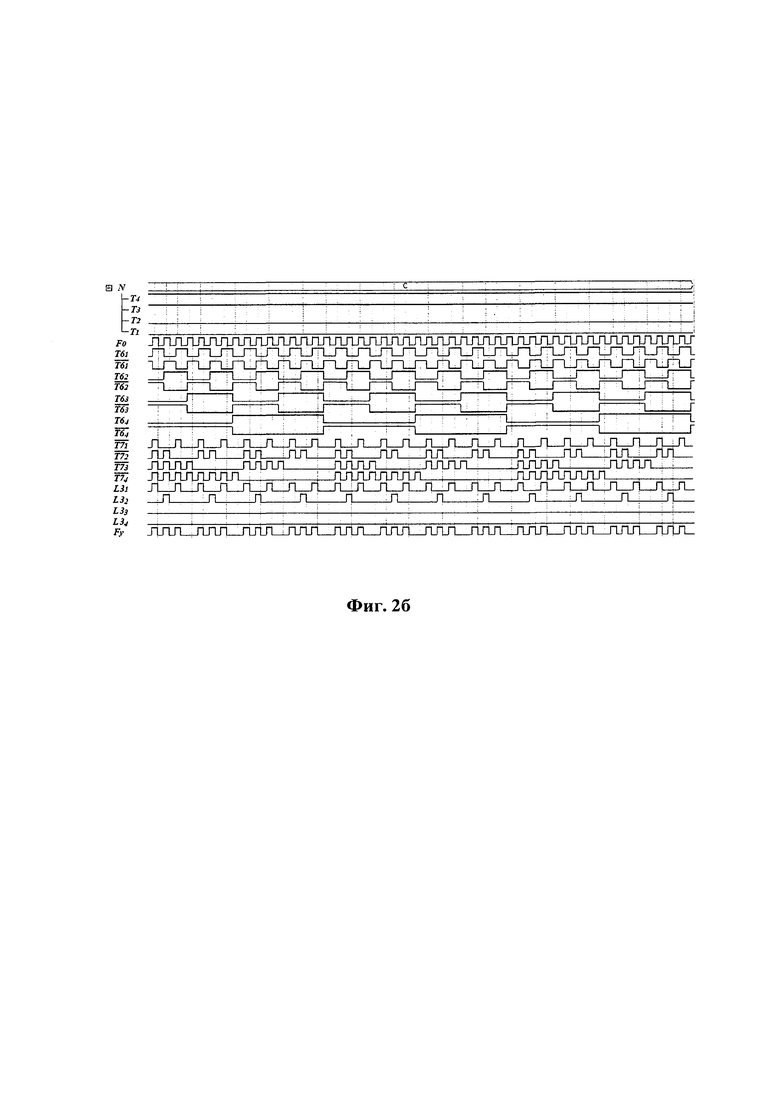

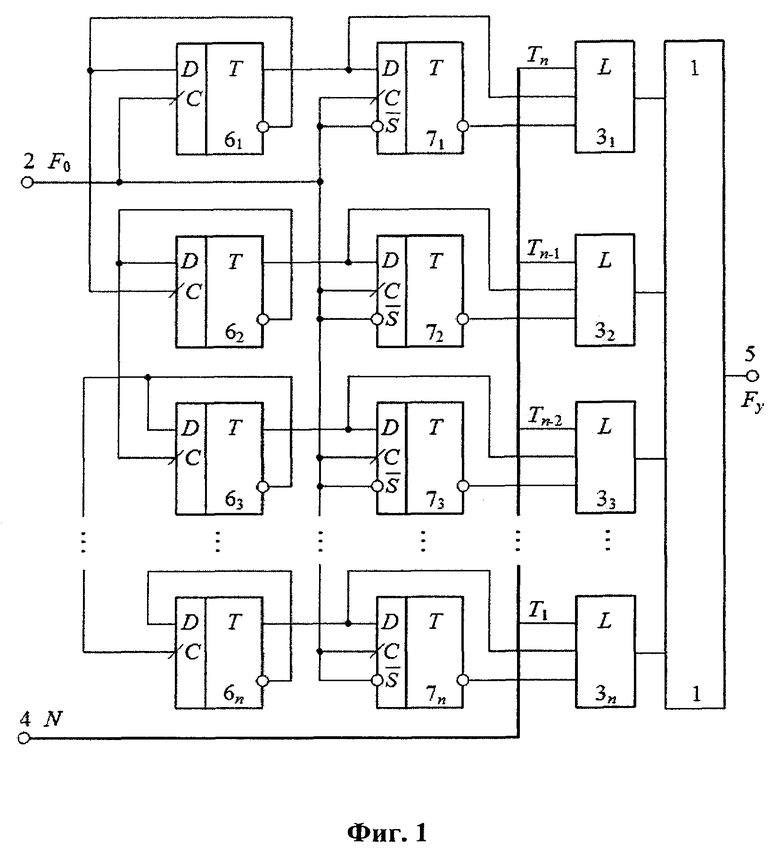

Сущность предлагаемого изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема предлагаемого делителя частоты, на фиг. 2 - временные диаграммы процессов, протекающих в устройстве для N=15 (фиг. 2а), для N=12 (фиг. 2б) и для N=5 (фиг. 2в).

Делитель частоты с переменным коэффициентом деления (фиг. 1) содержит элемент ИЛИ 1 с n входами, вход синхронизации 2, n логических элементов L3 с функцией И, первые входы которых соединены с n-разрядами шины управления 4 в обратном порядке, а выходы элементов L3 подключены к соответствующим входам элемента ИЛИ 1, выход которого является информационным выходом 5 делителя частоты. Кроме того, устройство содержит первую линейку 6n одноступенчатых D-тригтеров с прямыми динамическими тактовыми входами, вторую линейку 7n одноступенчатых D-триггеров с инверсными статическими входами установки в «1» и с прямыми динамическими тактовыми входами, которые у этих триггеров объединены и подключены к входу синхронизации 2, а также к динамическому тактовому входу первого триггера 61 первой линейки 6, прямой выход которого соединен со вторым входом первого логического элемента L31 и с D-входом первого триггера 71 второй линейки 7, а инверсный выход первого триггера 61 первой линейки 6 подключен к D-входу этого триггера 61 и к прямому динамическому тактовому входу второго триггера 62 первой линейки 6, прямой выход которого соединен со вторым входом второго логического элемента L32 и D-входом второго триггера 72 второй линейки 7, а инверсный выход второго триггера 62 первой линейки 6 подключен к D-входу этого триггера 62 и к прямому динамическому тактовому входу третьего триггера 63 первой линейки 6, прямой выход которого соединен со вторым входом третьего логического элемента L33 и D-входом третьего триггера 73 второй линейки 7, а инверсный выход третьего триггера 63 первой линейки 6 подключен к D-входу этого триггера 63 и к прямому динамическому тактовому входу следующего триггера первой линейки 6, прямой выход которого соединен со вторым входом следующего логического элемента L3 и D-входом следующего триггера второй линейки 7, а инверсный выход следующего триггера первой линейки 6 подключен к D-входу этого триггера, при этом связи последующих элементов соответственно повторяются до последних n элементов в каждой линейке, а инверсные выходы D-триггеров второй линейки 7 подключены соответственно к третьим входам логических элементов L3.

Устройство работает следующим образом.

На вход синхронизации 2 устройства поступает импульсная (тактовая) последовательность с частотой F0, на вход 4 шины управления подан код N, а триггеры первой линейки 6 находятся в нулевом состоянии, при этом на их инверсных выходах удерживается значение логической единицы.

Появление на входе 2 первого импульса тактовой частоты F0 обеспечивает появление единицы на прямом выходе первого триггера 61, нулевого значения на инверсном выходе первого триггера 61 первой линейки 6, а также запись нулевых значений с прямых выходов триггеров первой линейки 6 в триггеры второй линейки 7, что обуславливает появление единичных значений на инверсных выходах триггеров второй линейки 7. Появившаяся единица на прямом выходе первого триггера 61, а также единица с инверсного выхода первого триггера 71 второй линейки 7 поступают на второй и третий входы первого логического элемента с функцией И L31. На первый вход первого логического элемента с функцией И подан старший разряд Tn кода N с шины управления. Если этот старший разряд соответствует логической единице, то на выходе элемента И появится единица, которая поступает на выход устройства через элемент ИЛИ. Если же старший разряд Tn соответствует логическому нулю, то на выходе элемента И и на первом входе элемента ИЛИ останется состояние логического нуля. Остальные логические элементы с функцией И L3 блокированы нулевыми значениями, поступающими с выходов триггеров первой линейки 6.

Завершение первого импульса на входе 2 тактовой частоты F0 приводит к появлению нулевого значения на входе асинхронной установки триггеров второй линейки 7, что приводит к их установке в единицу с появлением на их инверсных выходах нулевого значения. Нулевое значение на инверсном выходе триггера 71 приводит к появлению нулевого значения на выходе логического элемента с функцией И L31.

Появление на входе 2 второго импульса тактовой частоты F0 обеспечивает запись нулевого значения в первый триггер 61, что приводит к появлению нуля на прямом выходе первого триггера 61, и единицы на инверсном выходе первого триггера 61 первой линейки 6. Появление единицы на инверсном выходе первого триггера 61 обеспечивает запись единичного значения во второй триггер 62 первой линейки 6. Остальные триггеры первой линейки 6 сохраняют нулевые значения. Кроме того, под воздействием второго импульса тактовой частоты F0 обеспечивается запись содержимого триггеров первой линейки 6 в триггеры второй линейки 7, причем у первого триггера это значение единичное, а у остальных триггеров - нулевое. Это приводит к появлению на инверсном выходе первого триггера 71 второй линейки 7 нулевого значения, а на инверсных выходах остальных триггеров второй линейки 7 - единичного значения. Появившаяся единица на прямом выходе второго триггера 62, а также единица с выхода второго триггера 72 второй линейки поступают на второй и третий входы второго логического элемента с функцией И L32. На первый вход второго логического элемента с функцией И подан предпоследний разряд Tn-1 кода N с шины управления. Если этот разряд соответствует логической единице, то на выходе элемента И появится единица, которая поступает на выход устройства через элемент ИЛИ. Если же предпоследний разряд Tn-1 соответствует логическому нулю, то на выходе элемента И и на втором входе элемента ИЛИ останется состояние логического нуля. В результате ситуация будет соответствовать ранее рассмотренной для нулевого сигнала в старшем разряде шины управления, и на выходе устройства останется состояние логического нуля.

Завершение второго импульса на входе 2 тактовой частоты F0 приводит к появлению нулевого значения на входе асинхронной установки триггеров второй линейки 7, что приводит к их установке в единицу с появлением на инверсных выходах нулевого значения. Нулевое значение на инверсном выходе триггера 72 приводит к появлению нулевого значения на выходе логического элемента с функцией И L32.

Появление на входе 2 третьего импульса тактовой частоты F0 обеспечивает запись единичного значения в первый триггер 61, что приводит к появлению единицы на прямом выходе первого триггера 61, и нуля на инверсном выходе первого триггера 61 первой линейки 6. Остальные триггеры первой линейки 6 сохраняют свои значения. Кроме того, под воздействием третьего импульса тактовой частоты F0 обеспечивается запись содержимого триггеров первой линейки 6 в триггеры второй линейки 7, причем у первого триггера это значение нулевое, у второго - единичное, а у остальных триггеров - нулевые. Это приводит к появлению на инверсном выходе второго триггера 72 второй линейки 7 нулевого значения, а на инверсных выходах остальных триггеров второй линейки 7 - единичных значений. Появившаяся единица на прямом выходе первого триггера 61, а также единица с выхода первого триггера 71 второй линейки поступают на второй и третий входы первого логического элемента с функцией И L31. На первый вход этого логического элемента с функцией И подан последний разряд Tn кода N с шины управления. Работа логического элемента И L31 и, соответственно, состояние на выходе устройства будут соответствовать ранее рассмотренным в зависимости от значения сигнала в старшем разряде шины управления.

Завершение третьего импульса на входе 2 тактовой частоты F0 приводит к появлению нулевого значения на входе асинхронной установки триггеров второй линейки 7, что приводит к их установке в единицы с появлением на инверсных выходах нулевых значений. Нулевое значение на инверсном выходе триггера 71 приводит к появлению нулевого значения на выходе логического элемента с функцией И L31.

Появление на входе 2 четвертого импульса тактовой частоты F0 обеспечивает запись нулевого значения в первый триггер 61, что приводит к появлению нуля на прямом выходе первого триггера 61, и единицы на инверсном выходе первого триггера 61 первой линейки 6.

Появление единицы на инверсном выходе первого триггера 61 обеспечивает запись нулевого значения во второй триггер 62 первой линейки 6, что приводит к появлению единицы на инверсном выходе этого триггера 62, что, в свою очередь, обеспечивает запись единичного значения в третий триггер 63 первой линейки 6. Остальные триггеры первой линейки 6 сохраняют нулевые значения. Кроме того, под воздействием четвертого импульса тактовой частоты F0 обеспечивается запись содержимого триггеров первой линейки 6 в триггеры второй линейки 7, причем у первого и второго триггеров эти значения единичные, а у остальных триггеров - нулевые. Это приводит к появлению на инверсных выходах первого 71 и второго 72 триггеров второй линейки 7 нулевых значений, а на инверсных выходах остальных триггеров второй линейки 7 - единичных значений. Появившаяся единица на прямом выходе третьего триггера 63, а также единица с выхода третьего триггера 73 второй линейки 7 поступают на второй и третий входы третьего логического элемента с функцией И L33. На первый вход этого логического элемента с функцией И подан разряд Tn-2 кода N с шины управления. Работа логического элемента И L33 и, соответственно, состояние на выходе устройства будут соответствовать ранее рассмотренным в зависимости от значения сигнала в старшем разряде шины управления.

Завершение четвертого импульса на входе 2 тактовой частоты F0 приводит к появлению нулевого значения на входе асинхронной установки триггеров второй линейки 7, что приводит к их установке в единицу с появлением на инверсных выходах нулевых значений. Нулевое значение на инверсном выходе триггера 71 приводит к появлению нулевого значения на выходе логического элемента с функцией И L31.

Процессы, связанные с прохождением пятого и всех последующих нечетных импульсов, аналогичны процессам, описанным для первого импульса, а результат соответствует результату, получаемому при поступлении первого импульса.

Процессы, связанные с прохождением шестого, десятого, четырнадцатого (и далее с шагом 4) импульсов, аналогичны процессам, описанным для второго импульса, а результат соответствует результату, получаемому при поступлении второго импульса.

Процессы, связанные с прохождением восьмого, двадцать четвертого (и далее с шагом 16) импульсов, аналогичны процессам, описанным для четных импульсов. При этом формирование сигнала на выходе устройства будет определяться по ранее рассмотренным правилам в зависимости от значения разряда Tn-3 кода N с шины управления.

Процессы, связанные с прохождением двенадцатого, двадцатого (и далее с шагом 8) импульсов, аналогичны процессам, описанным для четвертого импульса, а результат соответствует результату, получаемому при поступлении четвертого импульса.

В основу работы делителя частоты с переменным коэффициентом деления положен принцип последовательного однотактного формирования по прямым динамическим тактовым входам состояний триггеров первой линейки с выделением за полтакта на триггерах второй линейки разряда, в котором происходит изменение состояния из нуля в единицу, и разрешением прохождения полученного сигнала на выход при наличии единицы на соответствующем разряде шины, управляющей в обратном порядке, благодаря чему реализуется простое формирование выходного сигнала.

Логическое выражение для выхода устройства 5, как и у прототипа, имеет следующий вид:

Импульсы в последовательностях L1, L2, …, Ln разнесены по времени, поэтому на выходе логического элемента ИЛИ 1 происходит формирование суммарной частоты.

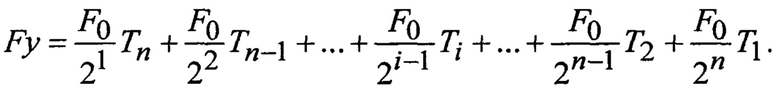

Значения частот на выходах элементов L1, L2, …, Ln описываются выражениями:

где i - номер элемента L;

Tk={0;1} - логическое состояние k-го разряда кода управления;

k=n-i+1.

Таким образом, среднее значение выходной частоты устройства Fy определяется выражением

Подставляя в уравнение (2) выражения (1), имеем:

Вынося за скобки F0 и 2-n, получаем:

В то же время двоичный код N, поступающий по n-разрядной шине управления 4, может быть представлен суммой произведений значения текущего бита кода Ti на вес бита n-разрядной шины управления:

N=Tn2n-1+Tn-12n-2+…+Ti2i-1+…+T221+T220.

С учетом последнего равенства, выражение (3), характеризующее среднюю частоту Fy импульсной последовательности на выходе 5 заявляемого устройства, может быть записано следующим образом:

то есть передаточная функция заявляемого делителя частоты с переменным коэффициентом деления, соответствует передаточной функции прототипа.

При этом, заменив два счетчика, построенные на двухступенчатых триггерах, на две триггерные линейки, характеризующиеся меньшим суммарным количеством триггеров, получили такой же функциональный результат, как и у прототипа.

Кроме того, заявляемое устройство является более компактным, а следовательно, обладает лучшей технологичностью и характеризуется меньшим потреблением мощности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Устройство для приема биимпульсных сигналов | 1990 |

|

SU1741282A2 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Устройство для коррекции погрешности аналого-цифровых преобразователей | 1986 |

|

SU1341717A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в сокращении времени преобразования при обработке сигналов. Делитель частоты с переменным коэффициентом деления содержит элемент ИЛИ с n входами, вход синхронизации, n логических элементов L с функцией И, первые входы которых соединены с n разрядами шины управления в обратном порядке, а выходы элементов L подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты, и в него введены первая линейка n одноступенчатых D-триггеров с прямыми динамическими тактовыми входами, вторая линейка n одноступенчатых D-триггеров с инверсными статическими входами установки в «1» и с прямыми динамическими тактовыми входами, которые у этих триггеров объединены и подключены к входу синхронизации, а также к динамическому тактовому входу первого триггера первой линейки, прямой выход которого соединен со вторым входом первого логического элемента L и с D-входом первого триггера второй линейки. 4 ил.

Делитель частоты с переменным коэффициентом деления, содержащий элемент ИЛИ с n входами, вход синхронизации, n логических элементов L с функцией И, первые входы которых соединены с n разрядами шины управления в обратном порядке, а выходы элементов L подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты, отличающийся тем, что в него введены первая линейка n одноступенчатых D-триггеров с прямыми динамическими тактовыми входами, вторая линейка n одноступенчатых D-триггеров с инверсными статическими входами установки в «1» и с прямыми динамическими тактовыми входами, которые у этих триггеров объединены и подключены к входу синхронизации, а также к динамическому тактовому входу первого триггера первой линейки, прямой выход которого соединен со вторым входом первого логического элемента L и с D-входом первого триггера второй линейки, а инверсный выход первого триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу второго триггера первой линейки, прямой выход которого соединен со вторым входом второго логического элемента L и D-входом второго триггера второй линейки, а инверсный выход второго триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу третьего триггера первой линейки, прямой выход которого соединен со вторым входом третьего логического элемента L и D-входом третьего триггера второй линейки, а инверсный выход третьего триггера первой линейки подключен к D-входу этого триггера и к прямому динамическому тактовому входу следующего триггера первой линейки, прямой выход которого соединен со вторым входом следующего логического элемента L и D-входом следующего триггера второй линейки, а инверсный выход следующего триггера первой линейки подключен к D-входу этого триггера, при этом связи последующих элементов соответственно повторяются до последних n элементов в каждой линейке, а инверсные выходы D-триггеров второй линейки подключены соответственно к третьим входам логических элементов L.

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| КВАДРАТУРНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ДЕЛЕНИЕМ НА ТРИ | 2009 |

|

RU2479121C2 |

| US 8774305 B1, 08.07.2014 | |||

| US 7266579 B2, 04.09.2007. | |||

Авторы

Даты

2021-07-28—Публикация

2020-12-03—Подача