Предлагаемые технические решения объединены единым изобретательским замыслом, относятся к области радиотехники, а именно автоматики, и могут быть использованы в системах и устройствах обработки цифровой информации с резервированием.

Известно устройство дублированной системы с задержкой по а.с. №1660231 СССР, МПК6 Н05К 10/00, от 30.06.91, бюллетень №24. Оно состоит из двух резервных устройств, двух регистров сдвига, сумматора по модулю 2, двух JK-триггеров, трех элементов И, одновибратора, элемента ИЛИ, D-триггера, элемента ИЛИ-НЕ, блока установки, входа дискретных устройств, шины синхронизации, двух выходных шин.

Недостатком данного устройства является низкая вероятность точного принятия решения на подключение резервного устройства. Это объясняется тем, что в этом устройстве могут быть обнаружены только отказы, а сбои в его работе не могут быть выявлены и, следовательно, отсутствует возможность запрета передачи искаженной информационной последовательности импульсов с выхода дублированной системы в канал связи.

Наиболее близким по своей технической сущности к заявленному устройству является устройство, описанное в книге: Чернышев А.А. "Основы конструирования и надежности электронных вычислительных средств." - М.: Радио и связь, 1998. - С.350, состоящее из трех резервных элементов, трех элементов И, одного элемента ИЛИ, к входу которого подключены выходы трех элементов И, входы которых соединены с выходами трех резервных элементов, при этом первый вход первого элемента И подключен к выходу первого резервного элемента и к второму входу третьего элемента И, первый вход которого соединен с выходом третьего резервного элемента и с вторым входом второго элемента И, первый вход которого подключен к выходу второго резервного элемента и к второму входу первого элемента.

Недостатком данного устройства является низкая надежность из-за отсутствия контроля работоспособности резервных элементов, что ведет к нарушению алгоритма маскирования неисправностей при отказе двух и более резервных элементов, и низкая помехоустойчивость вследствие того, что в нем не обеспечивается защита от сбоев резервных элементов.

Техническим результатом является повышение надежности системы резервирования за счет контроля отказов резервных элементов и защиты от сбоев.

Этот результат достигается тем, что в известное трехэлементное мажоритарное устройство резервирования, содержащее три резервных элемента, три элемента И, один элемент ИЛИ, к первому, второму и третьему входам которого подключены соответственно выходы первого, второго и третьего элементов И, причем входы первого, второго и третьего резервных элементов соединены вместе и являются информационным входом устройства, дополнительно введены блок анализа, блок определения параметров, блок памяти, три регистра сдвига, блок определения отказов, блок отображения состояния, три управляемых переключателя, второй элемент ИЛИ, выход которого является информационным выходом устройства, причем его первый вход соединен с выходом первого элемента ИЛИ, а второй, третий, четвертый входы подключены соответственно к вторым выходам первого, второго и третьего управляемых переключателей, причем первый выход первого управляемого переключателя соединен с первым входом первого и вторым входом второго элементов И, первый выход второго управляемого переключателя соединен с первым входом второго и вторым входом третьего элементов И, а первый выход третьего управляемого переключателя соединен с первым входом третьего и вторым входом первого элементов И, вторые входы первого, второго и третьего управляемых переключателей являются управляющими и соединены соответственно с первым, вторым и третьим входом блока отображения состояния и соответственно с первым, вторым и третьим выходами блока определения отказов, четвертый выход которого подключен к третьим входам первого, второго и третьего управляемых переключателей, а его вход является информационной шиной, подключенной к выходу блока памяти, другой выход которого соединен с входом блока определения параметров, первый и второй выходы которого подключены соответственно к второму и третьему входу блока памяти, первый вход которого соединен с выходом блока анализа, первый, второй, третий информационные входы которого подключены соответственно к выходам первого, второго, третьего резервных элементов и, соответственно, к входам первого, второго и третьего регистров сдвига, выход каждого из которых подключен соответственно к первым входам первого, второго и третьего управляемых переключателей.

Благодаря новой совокупности существенных признаков, реализуемых за счет введения блока анализа, блока определения параметров, блока памяти, трех регистров сдвига, блока определения отказов, блока отображения состояния, трех управляемых переключателей, второго элемента ИЛИ и связей между ними, достигается возможность контроля технического состояния резервных элементов и при выходе из строя одного или двух из них выполнять функциональное предназначение, чем обеспечивается более высокая надежность заявляемого устройства по сравнению с известными.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленного трехэлементного мажоритарного устройства резервирования, отсутствуют. Следовательно, заявленное устройство соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

Заявленное устройство поясняется схемами.

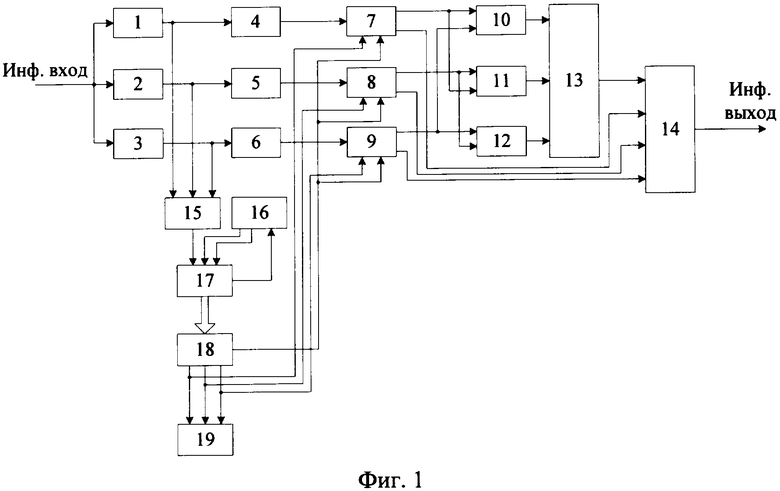

На фиг.1 показана структурная схема трехэлементного мажоритарного устройства резервирования;

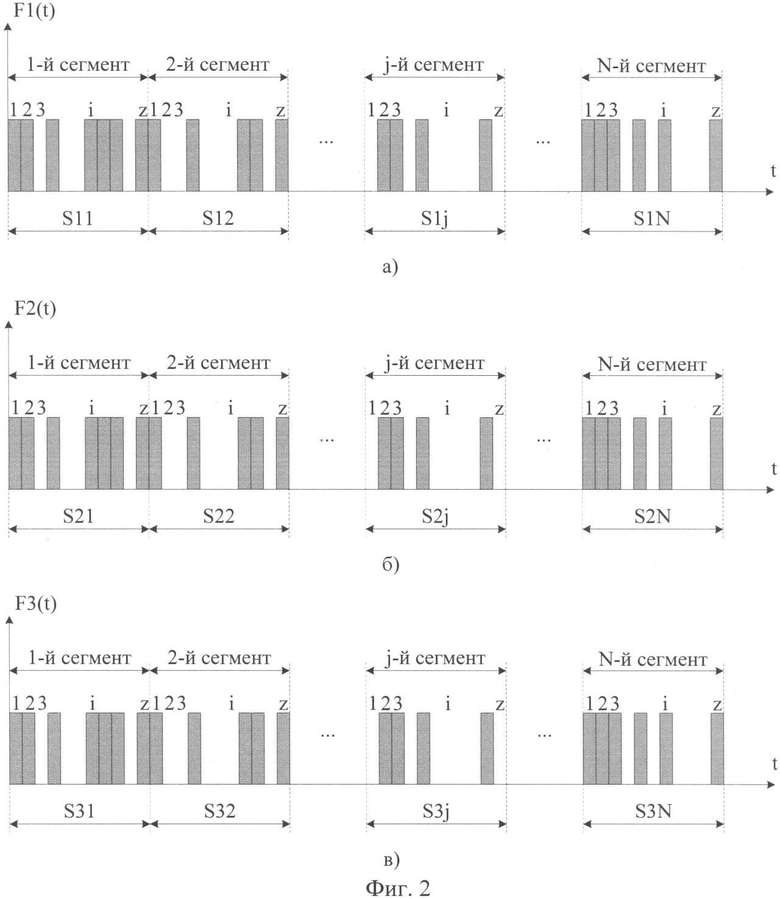

на фиг.2 - структура информационной последовательности импульсов на выходах резервных элементов;

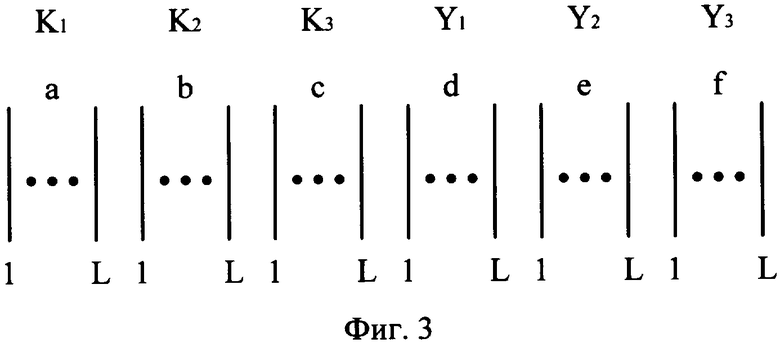

на фиг.3 - структурная схема информационной шины;

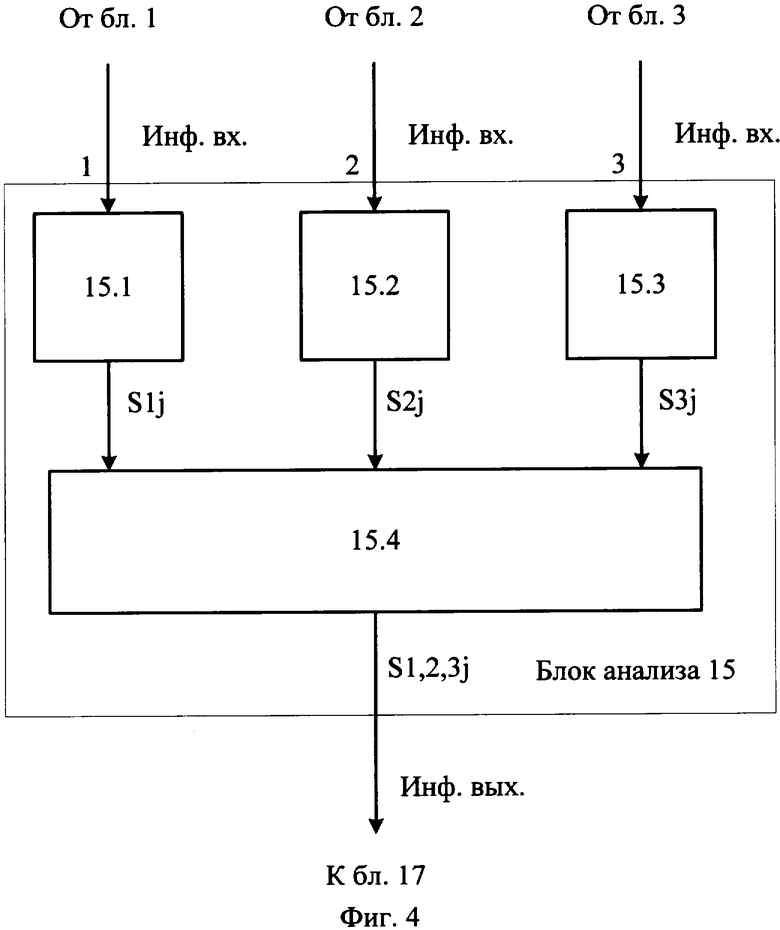

на фиг.4 - структурная схема блока анализа;

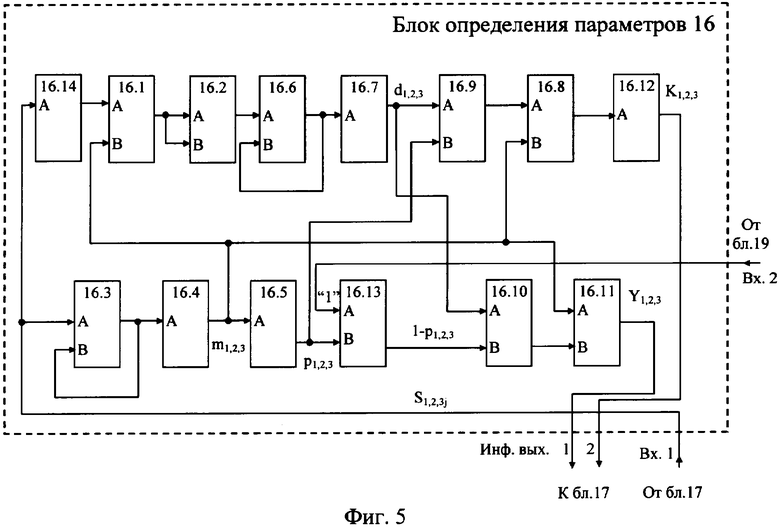

на фиг.5 - структурная схема блока определения параметров;

на фиг.6 - структурная схема блока определения отказов;

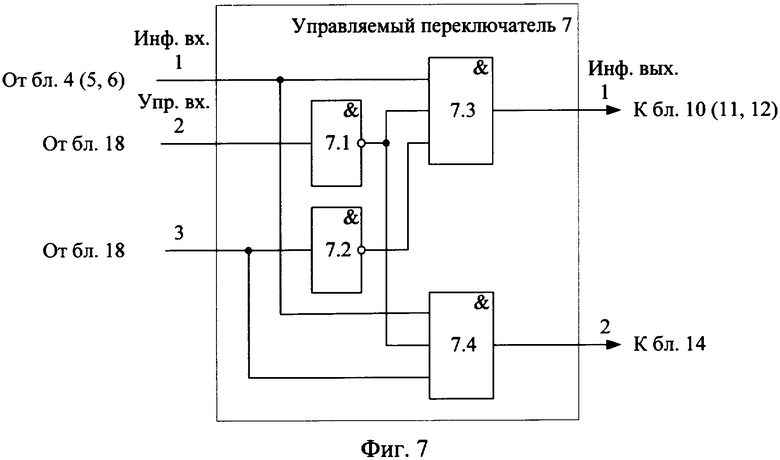

на фиг.7 - структурная схема управляемых переключателей.

Трехэлементное мажоритарное устройство резервирования, показанное на фиг.1, состоит из первого 1, второго 2, третьего 3 резервных элементов, первого 4, второго 5, третьего 6 регистров сдвига, первого 7, второго 8 и третьего 9 управляемых переключателей, первого 10, второго 11, третьего 12 элементов И, первого 13, второго 14 элементов ИЛИ, блока анализа 15, блока определения параметров 16, блока памяти 17, блока определения отказов 18, блока отображения состояния 19.

Информационный вход трехэлементного мажоритарного устройства резервирования подключен к входу каждого из трех резервных элементов 1, 2, 3, выход каждого из которых соединен соответственно с первым, вторым и третьим входом блока анализа 15 и соответственно с входом первого 4, второго 5, третьего 6 регистров сдвига, выход каждого из которых подключен соответственно к информационному входу первого 7, второго 8, третьего 9 управляемых переключателей. Выход блока анализа 15 соединен с первым входом блока памяти 17, а его второй и третий вход соединен соответственно с первым и вторым выходом блока определения параметров 16, вход которого подключен к выходу блока памяти 17, выходная информационная шина которого соединена с входной информационной шиной блока определения отказов 18, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока отображения 19 и соответственно ко вторым входам первого 7, второго 8 и третьего 9 управляемых переключателей, а четвертый выход подключен к третьим входам первого 7, второго 8 и третьего 9 управляемых переключателей. Первый выход первого управляемого переключателя 7 соединен с первым входом первого 10 и вторым входом второго 11 элементов И, первый выход второго управляемого переключателя 8 соединен с первым входом второго 11 и вторым входом третьего 12 элементов И, а первый выход третьего управляемого переключателя 9 соединен с вторым входом первого 10 и с первым входом третьего 12 элементов И. Выходы первого 10, второго 11 и третьего 12 элементов И подключены соответственно к первому, второму и третьему входам первого элемента ИЛИ 13, выход которого соединен с первым входом второго элемента ИЛИ 14, второй, третий и четвертый входы которого подключены соответственно к вторым выходам первого 7, второго 8 и третьего 9 управляемых переключателей, а выход второго элемента ИЛИ 14 является информационным выходом устройства.

На чертеже обозначено:

1, 2, 3 - резервные элементы;

4, 5, 6 - регистры сдвига;

7, 8, 9 - управляемые переключатели;

10, 11, 12 - элементы И;

13, 14 - элементы ИЛИ;

15 - блок анализа;

16 - блок определения параметров;

17 - блок памяти;

18 - блок определения отказов;

19 - блок отображения состояния.

Информационная шина, показанная на фиг.3, содержит шесть групп "а", "b", "с", "d", "е", "f" по L входов в каждой, где L≥2i, i∈1, 2,.... Она состоит из нескольких жгутов, количество которых определяется количеством параметров. Каждый жгут имеет несколько физических проводников, число которых определяется значением L.

Блок анализа 15, показанный на фиг.4, предназначен для выделения информационной последовательности импульсов на выходах резервных элементов и состоит из первого 15.1, второго 15.2 и третьего 15.3 счетчиков единичных импульсов и электронного ключа 15.4. Входы счетчиков единичных импульсов являются соответственно первым, вторым и третьим информационными входами блока анализа. Первый, второй и третий входы электронного ключа 15.4 подключены к выходам соответственно первого 15.1, второго 15.2 и третьего 15.3 счетчиков единичных импульсов. Выход электронного ключа 15.4 является информационным выходом блока анализа 15.

На чертеже обозначено:

15.1, 15.2, 15.3 - счетчики единичных импульсов;

15.4 - электронный ключ.

Блок определения параметров 16, показанный на фиг.5, предназначен для вычисления параметров усечения из обработанных информационных последовательностей импульсов на выходах первого 1, второго 2 и третьего 3 резервных элементов, и состоит из регистра сдвига 16.14, вычитателей 16.1, 16.11, 16.13, сумматоров 16.3, 16.6, 16.8, умножителя 16.2, делителей 16.9, 16.10, делителей с постоянным коэффициентом деления 16.4, 16.5, 16.7, 16.12. Информационный вход является входом блока определения параметров 16 и подключен к первым входам регистра сдвига 16.14 и первого сумматора 16.3. Выход регистра сдвига 16.14 подключен к первому входу первого вычитателя 16.1. Выход первого вычитателя 16.1 подключен к первому и второму входам умножителя 16.2. Выход умножителя 16.2 подключен к первому входу второго сумматора 16.6. Второй вход второго сумматора 16.6 подключен к его выходу и входу третьего делителя с постоянным коэффициентом деления 16.7. Выход третьего делителя с постоянным коэффициентом деления 16.7 подключен к первым входам первого 16.9 и второго 16.10 делителей. Выход первого делителя 16.9 подключен к первому входу третьего сумматора 16.8. Выход третьего сумматора 16.8 подключен к входу четвертого делителя с постоянным коэффициентом деления 16.12. Второй вход первого сумматора 16.3 подключен к его выходу и входу первого делителя с постоянным коэффициентом деления 16.4. Выход первого делителя с постоянным коэффициентом деления 16.4 подключен к входу второго делителя с постоянным коэффициентом деления 16.5, к вторым входам первого вычитателя 16.1, третьего сумматора 16.8 и к первому входу второго вычитателя 16.11. Выход второго делителя с постоянным коэффициентом деления 16.5 подключен к входу третьего вычитателя 16.13 и ко второму входу первого делителя 16.9. Выход третьего вычитателя 16.13 подключен к второму входу второго делителя 16.10. Выход второго делителя 16.10 подключен к второму входу второго вычитателя 16.11. Выходы второго вычитателя 16.11 и четвертого делителя с постоянным коэффициентом деления 16.12 являются соответственно первым и вторым информационными выходами блока определения параметров 16.

На чертеже обозначено:

16.1, 16.11, 16.13 - вычитатели;

16.2 - умножитель;

16.3. 16.6, 16.8 - сумматоры;

16.4. 16.5, 16.7,16.12 - делители с постоянным коэффициентом деления;

16.9, 16.10 - делители;

16.14 - регистр сдвига.

Блок определения отказов 18, показанный на фиг.6, состоит из первого 18.1, второго 18.4, третьего 18.7 L-входовых элементов ИЛИ-НЕ, первого 18.2, второго 18.5, третьего 18.8 L-входовых элементов И, где L≥2i, i∈1, 2,..., трех двухвходовых элементов ИЛИ 18.3, 18.6, 18.9, трех двухвходовых элементов И 18.10, 18.11, 18.12 и одного трехвходового элемента ИЛИ 18.13. Выходы первых элементов ИЛИ-НЕ 18.1 и И 18.2 подключены соответственно к первому и второму входам первого элемента ИЛИ 18.3. Выходы вторых элементов ИЛИ-НЕ 18.4 и И 18.5 подключены соответственно к первому и второму входам второго элемента ИЛИ 18.6. Выходы третьих элементов ИЛИ-НЕ 18.7 и И 18.8 подключены соответственно к первому и второму входам третьего элемента ИЛИ 18.9. Выходы первого 18.3, второго 18.6, третьего 18.9 элементов ИЛИ являются соответственно первым, вторым и третьим управляющими выходами блока. Причем L-входы первых элементов ИЛИ-НЕ 18.1, И 18.2, вторых элементов ИЛИ-НЕ 18.4, И 18.5 и третьих элементов ИЛИ-НЕ 18.7, И 18.8 являются входной информационной шиной блока и соединены с группами соответственно "а", "b", "с", "d", "e", "f". Выходы первого 18.3 и второго 18.6 двухвходовых элементов ИЛИ соединены соответственно с первым и вторым входами первого двухвходового элемента И 18.10, выходы третьего 18.9 и первого 18.3 двухвходовых элементов ИЛИ соединены соответственно с первым и вторым входами второго двухвходового элемента И 18.11, выходы второго 18.6 и третьего 18.9 двухвходовых элементов ИЛИ соединены соответственно с первым и вторым входами третьего двухвходового элемента И 18.12. Выходы первого 18.10, второго 18.11 и третьего 18.12 двухвходовых элементов И соединены соответственно с первым, вторым и третьим входами трехвходового элемента ИЛИ 18.13. Выход трехвходового элемента ИЛИ 18.13 является четвертым управляющим выходом блока определения отказов 18.

На чертеже обозначено:

18.1. 18.4, 18.7 - L-входовые элементы ИЛИ-НЕ;

18.2. 18.5, 18.8 - L-входовые элементы И;

18.3. 18.6, 18.9 - двухвходовые элементы ИЛИ;

18.10, 18.11, 18.12 - двухвходовые элементы И;

18.13 - трехвходовый элемент ИЛИ.

Первый 7, второй 8 и третий 9 управляемые переключатели идентичны и предназначены для коммутации входного информационного сигнала на один из двух выходов.

Управляемый переключатель 7, показанный на фиг.7, состоит из двух элементов И-НЕ 7.1, 7.2 и двух трехвходовых элементов И 7.3, 7.4. Первые входы трехвходовых элементов И 7.3, 7.4 являются информационным входом управляемого переключателя, вход первого элемента И-НЕ 7.1 является вторым входом управляемого переключателя, вход второго элемента И-НЕ 7.2 и третий вход второго трехвходового элемента И 7.4 являются третьим входом управляемого переключателя. Выход первого элемента И-НЕ 7.1 соединен со вторыми входами первого 7.3 и второго 7.4 элементов И, а выход второго элемента И-НЕ 7.2 соединен с третьим входом первого элемента И 7.3. Выходы первого 7.3 и второго 7.4 элементов И являются соответственно первым и вторым выходом управляемого переключателя 7.

На четреже обозначено:

7.1, 7.2 - элементы И-НЕ;

7.3, 7.4 - элементы И.

Блок отображения состояния 19 предназначен для индикации состояния резервных элементов и состоит из трех световых индикаторов. Первый, второй и третий входы блока отображения состояния 19 подключены к первым контактам световых индикаторов, вторые контакты которых подключены на корпусную шину.

Входящие в общую структуру трехэлементного мажоритарного устройства резервирования элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

В качестве блока памяти может быть использовано устройство, схема построения которого известна и приведена, например, в книге: В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение. Справочное пособие" - М.: Радио и связь, 1983, с.175, рис.5.12.

Схемы счетчиков известны и приведены, например, в книге: А.А.Сикарев, О.Н.Лебедев. "Микроэлектронные устройства формирования и обработки сложных сигналов." - М.: Радио и связь, 1983, с.128, рис.518 и могут быть реализованы, например, на микросхеме К176ИЕ2 (см. В.Л.Шило. "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, с.235-236, рис.2.36,а).

Используемые в заявленном устройстве элементы И-НЕ, ИЛИ, ИЛИ-НЕ, регистры сдвига известны и описаны, например, в справочнике В.Л.Шило "Популярные цифровые микросхемы": элементы И-НЕ с.43, рис.1.24, в и могут быть выполнены на микросхемах К155ЛАЗ; элементы ИЛИ - с.48, рис.1.27,з и могут быть выполнены на микросхемах К155ЛЛ1; элемент ИЛИ-НЕ - с.48, рис.1.27,б и может быть выполнен на микросхемах К155ЛЕ1; регистры сдвига - с.106, рис.1.75 и могут быть выполнены на микросхемах К155ИР1. Схемы элементов И известны и описаны, например, в книге "Микросхемы и их применение." / Батушев В.А., В.Н.Вениаминов, Ковалев В.Г. и др. - М.: Энергия, 1978. С.142-147.

Схемы сумматоров, вычитателей описаны, например, в книге: Токхейм Р. "Основы цифровой электроники": Пер. с англ. - М.: Мир, 1988, с.231-232, рис.9.18 и могут быть реализованы, например, на микросхеме К155ИП4 (см. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М.: Радио и связь, 1983, с.129-130).

Схема умножителя известна, приведена, например, в книге: Токхейм Р. "Основы цифровой электроники": Пер. с англ. - М.: Мир, 1988, с.236-240, рис.9.26 и может быть реализована, например, на микросхеме К155ИП4 (см. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М.: Радио и связь, 1983, с.129-130).

Схема делителя, делителя с постоянным коэффициентом деления известна, описана, например, в книге: B.C.Гутников, В.В.Лопатин и др. "Электронные устройства информационно-измерительной техники": Учебное пособие. - Л.: ЛПИ им. Калинина, 1980, с.44-46, 4-50, рис.21,а, 24 и может быть реализована, например, на микросхемах К155ИЕ8, К155ИЕ2 (см. В.Л.Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, с.94-97, рис.1.69).

Заявленное трехэлементное мажоритарное устройство резервирования работает следующим образом.

Информационная последовательность импульсов поступает на входы резервных элементов 1, 2 и 3. Преобразованные в резервных элементах 1, 2, 3 информационные последовательности импульсов

и

и  записываются в регистры сдвига 4, 5 и 6. Одновременно осуществляется оценка состояния резервных элементов 1, 2, 3 и принятие решения на реконфигурацию системы в случае отказа в их работе. Время оценки и принятия решения не превышает время задержки информационной последовательности импульсов в регистрах сдвига 4, 5, 6.

записываются в регистры сдвига 4, 5 и 6. Одновременно осуществляется оценка состояния резервных элементов 1, 2, 3 и принятие решения на реконфигурацию системы в случае отказа в их работе. Время оценки и принятия решения не превышает время задержки информационной последовательности импульсов в регистрах сдвига 4, 5, 6.

Оценка состояния производится следующим образом. Информационные последовательности импульсов

и

и  с выходов резервных элементов 1, 2, 3 подаются на соответствующие входы первого 15.1, второго 15.2 и третьего 15.3 счетчиков единичных символов (счетчиков "1") блока анализа 15, показанного на фиг.4. В счетчиках "1" 15.1, 15.2, 15.3 начинается подсчет числа единичных символов ("1") S1j, S2j, S3j в каждом j-м Z-разрядном сегменте (см. фиг.2), где 1, 2, 3 - первый, второй и третий резервные элементы. После поступления каждого Z-го символа сегмента производится считывание значений счетчиков "1" 15.1, 15.2, 15.3 и их обнуление.

с выходов резервных элементов 1, 2, 3 подаются на соответствующие входы первого 15.1, второго 15.2 и третьего 15.3 счетчиков единичных символов (счетчиков "1") блока анализа 15, показанного на фиг.4. В счетчиках "1" 15.1, 15.2, 15.3 начинается подсчет числа единичных символов ("1") S1j, S2j, S3j в каждом j-м Z-разрядном сегменте (см. фиг.2), где 1, 2, 3 - первый, второй и третий резервные элементы. После поступления каждого Z-го символа сегмента производится считывание значений счетчиков "1" 15.1, 15.2, 15.3 и их обнуление.

Единичные символы S1j, S2j, S3j, представленные в двоичном коде, с выходов счетчиков "1" 15.1, 15.2, 15.3 поступают на первый, второй и третий входы электронного ключа 15.4 и поочередно коммутируются на выход электронного ключа 15.4.

С выхода электронного ключа 15.4 S1j, S2j, S3j поступают на первый информационный вход блока памяти 17, где производится запись их значений в соответствующие ячейки памяти блока памяти 17 в следующей последовательности: S11, S21, S31, S12, S22, S32,..., S1j, S2j, S3j,..., S1N, S2N, S3N.

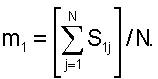

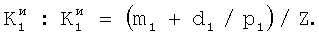

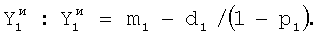

После занесения в блок памяти 17 всех чисел S1j, S2j, S3j выделенных N Z-разрядных сегментов в блоке определения параметров 16 вначале производится вычисление значений математического ожидания m1, дисперсии d1 числа "1" в Z-разрядном сегменте и вероятности появления "1" p1 в каждой позиции Z-разрядных сегментов и по результатам вычислений m1, d1 и p1 определяют значения параметров усечения  и

и  Затем производится вычисление математического ожидания m2, дисперсии d2 числа "1" в Z-разрядном сегменте и вероятности появления "1" p2 в каждой позиции Z-разрядных сегментов и по результатам вычислений m2, d2 и р2 определяют значения параметров усечения

Затем производится вычисление математического ожидания m2, дисперсии d2 числа "1" в Z-разрядном сегменте и вероятности появления "1" p2 в каждой позиции Z-разрядных сегментов и по результатам вычислений m2, d2 и р2 определяют значения параметров усечения  и

и  Затем производится вычисление математического ожидания m3, дисперсии d3 числа "1" в Z-разрядном сегменте и вероятности появления "1" р3 в каждой позиции Z-разрядных сегментов и по результатам вычислений m3, d3 и р3 определяют значения параметров усечения

Затем производится вычисление математического ожидания m3, дисперсии d3 числа "1" в Z-разрядном сегменте и вероятности появления "1" р3 в каждой позиции Z-разрядных сегментов и по результатам вычислений m3, d3 и р3 определяют значения параметров усечения  и

и  Эти вычисления производятся в выделенных N Z-разрядных сегментах информационной последовательности импульсов резервных элементов 1, 2, 3.

Эти вычисления производятся в выделенных N Z-разрядных сегментах информационной последовательности импульсов резервных элементов 1, 2, 3.

С выхода блока памяти 17 производится последовательное считывание значений S1j, S2j, S3j. Эти значения подаются на первый вход первого сумматора 16.3 и вход регистра сдвига 16.14 блока определения параметров 16, показанного на фиг.5. В первом сумматоре 16.3 производится суммирование всех j-х значений S1j выделенных N Z-разрядных сегментов путем сложения каждого j-го значения S1j с суммой предыдущих, поступающих с выхода первого сумматора 16.3 на его второй вход:  . При подаче на первый вход первого сумматора 16.3 последнего значения S1j и получения на его выходе суммарного значения единичных символов S1N в выделенных N Z-разрядных сегментах это значение считывают, а первый сумматор 16.3 обнуляют.

. При подаче на первый вход первого сумматора 16.3 последнего значения S1j и получения на его выходе суммарного значения единичных символов S1N в выделенных N Z-разрядных сегментах это значение считывают, а первый сумматор 16.3 обнуляют.

Сигнал с выхода сумматора 16.3 подается на вход делителя с постоянным коэффициентом деления 16.4. В делителе выполняется операция деления на число N, то есть производится вычисление:

Значение m1 с выхода делителя с постоянным коэффициентом деления 16.4 подается на первый вход делителя с постоянным коэффициентом деления 16.5, второй вход первого вычитателя 16.1, второй вход третьего сумматора 16.8 и первый вход второго вычитателя 16.11. В делителе с постоянным коэффициентом деления 16.5 выполняется операция деления на число Z, то есть производится вычисление вероятности появления "1" p1 в каждой позиции Z-разрядных сегментов:  , после чего производится подача ее на первый вход третьего вычитателя 16.13 и второй вход первого делителя 16.9. В третьем вычитателе 16.13 производится вычисление 1-p1.

, после чего производится подача ее на первый вход третьего вычитателя 16.13 и второй вход первого делителя 16.9. В третьем вычитателе 16.13 производится вычисление 1-p1.

Значение 1-p1 считывается и подается на второй вход второго делителя 16.10.

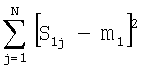

После вычисления значения m1 и подачи его на второй вход первого вычитателя 16.1 производится вычисление значения дисперсии d1. С выхода регистра сдвига 16.14, время задержки которого определяется временем, необходимым для вычисления значения m1 в делителе с постоянным коэффициентом деления 16.4, производится последовательное считывание j-x значений S1j выделенных N Z-разрядных сегментов, и подача этих значений на первый вход первого вычитателя 16.1. В вычитателе 16.1 производится вычисление S1j-m1.

Сигнал с выхода первого вычитателя 16.1 подается на первый и второй входы умножителя 16.2, в которых производится вычисление: [S1j-m1]2, результат которого подается на первый вход второго сумматора 16.6.

После этого производится обнуление первого вычитателя 16.1 и умножителя 16.2.

Во втором сумматоре 16.6 производится сложение [S1j-m1]2 N раз путем добавления каждого значения [S1j-m1]2 к сумме предыдущих, поступающих с выхода второго сумматора 16.6 на его второй вход. При подаче на первый вход второго сумматора 16.6 N-го значения [S1j-m1]2 и вычисления на его выходе суммарного значения  производится считывание этого значения на вход третьего делителя с постоянным коэффициентом деления 16.7 и обнуление второго сумматора 16.6.

производится считывание этого значения на вход третьего делителя с постоянным коэффициентом деления 16.7 и обнуление второго сумматора 16.6.

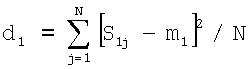

В третьем делителе с постоянным коэффициентом деления 16.7 производится вычисление:  . После вычисления d1 производится считывание значения d1.

. После вычисления d1 производится считывание значения d1.

Значение d1 подается на первые входы первого 16.9 и второго 16.10 делителей. На второй вход делителя 16.9 подано значение p1 с выхода делителя с постоянным коэффициентом деления 16.5. В делителе 16.9 производится вычисление d1/p1, результат которого подается на первый вход третьего сумматора 16.8.

В третьем сумматоре 16.8, на второй вход которого подано значение m1 с выхода делителя с постоянным коэффициентом деления 16.4, производится вычисление: m1+d1/p1.

Результат суммирования подается на вход четвертого делителя с постоянным коэффициентом деления 16.12, в котором производится вычисление и квантование параметра усечения  После вычисления и квантования производится считывание значения

После вычисления и квантования производится считывание значения  и подача этого значения на третий информационный вход блока памяти 17, в котором производится запись значений

и подача этого значения на третий информационный вход блока памяти 17, в котором производится запись значений  в соответствующие ячейки памяти.

в соответствующие ячейки памяти.

Параллельно с вычислением значения  производится вычисление значения

производится вычисление значения  На второй вход делителя 16.10 подается значение 1-p1, а на его первый вход подано значение d1. В делителе 16.10 производится вычисление d1/(1-p1), результат которого подается на второй вход второго вычитателя 16.11. Во втором вычитателе 16.11, на первый вход которого подано значение m1 с выхода делителя с постоянным коэффициентом деления 16.4, производится вычисление и квантование параметра усечения

На второй вход делителя 16.10 подается значение 1-p1, а на его первый вход подано значение d1. В делителе 16.10 производится вычисление d1/(1-p1), результат которого подается на второй вход второго вычитателя 16.11. Во втором вычитателе 16.11, на первый вход которого подано значение m1 с выхода делителя с постоянным коэффициентом деления 16.4, производится вычисление и квантование параметра усечения  После вычисления и квантования производится считывание значения

После вычисления и квантования производится считывание значения  и подача этого значения на второй информационный вход блока памяти 17, в котором производится запись значений

и подача этого значения на второй информационный вход блока памяти 17, в котором производится запись значений  в соответствующие ячейки памяти. После вычисления значений m1, p1 и d1 и параметров усечения

в соответствующие ячейки памяти. После вычисления значений m1, p1 и d1 и параметров усечения  и

и  производится вычисление значений m2, р2 и d2 и параметров усечения

производится вычисление значений m2, р2 и d2 и параметров усечения  и

и  Вычисление значений m2, p2, d2 и параметров усечения

Вычисление значений m2, p2, d2 и параметров усечения  и

и  производится аналогично вычислениям значений m1, p1, d1 и параметров усечения

производится аналогично вычислениям значений m1, p1, d1 и параметров усечения  и

и  После вычисления значений m2, р2 и d2 и параметров усечения

После вычисления значений m2, р2 и d2 и параметров усечения  и

и  производится вычисление значений m3, р3 и d3 и параметров усечения

производится вычисление значений m3, р3 и d3 и параметров усечения  и

и  Вычисление значений m3, р3, d3 и параметров усечения

Вычисление значений m3, р3, d3 и параметров усечения  и

и  производится аналогично вычислениям значений m1, p1, d1 и параметров усечения

производится аналогично вычислениям значений m1, p1, d1 и параметров усечения  и

и

Вычисления в блоке определения параметров 16 производятся непрерывно для каждой N Z-разрядной последовательности сегментов.

На втором этапе по полученным значениям  и

и

и

и

и

и  производится определение состояния резервных элементов 1, 2, 3 и принятие решения на реконфигурацию устройства резервирования.

производится определение состояния резервных элементов 1, 2, 3 и принятие решения на реконфигурацию устройства резервирования.

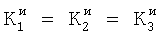

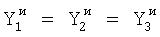

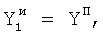

В нормальном режиме работы, когда все три резервных элемента 1, 2, 3 работоспособны ( и

и  ), параметры усечения

), параметры усечения

с блока памяти 17 в параллельном двоичном коде подаются соответственно на первый L-входовый элемент ИЛИ-НЕ 18.1, первый L-входовый элемент И 18.2, второй L-входовый элемент ИЛИ-НЕ 18.4 и второй L-входовый элемент И 18.5, третий L-входовый элемент ИЛИ-НЕ 18.7 и третий L-входовый элемент И 18.8 блока определения отказов 18. На 1, 2 и 3 управляющих выходах блока определения отказов 18 формируются сигналы с уровнем логического "0".

с блока памяти 17 в параллельном двоичном коде подаются соответственно на первый L-входовый элемент ИЛИ-НЕ 18.1, первый L-входовый элемент И 18.2, второй L-входовый элемент ИЛИ-НЕ 18.4 и второй L-входовый элемент И 18.5, третий L-входовый элемент ИЛИ-НЕ 18.7 и третий L-входовый элемент И 18.8 блока определения отказов 18. На 1, 2 и 3 управляющих выходах блока определения отказов 18 формируются сигналы с уровнем логического "0".

Одновременно сигналы с выхода элементов ИЛИ 18.3, 18.6, 18.9 поступают на входы двухвход овых элементов И 18.10, 18.11, 18.12 и затем на вход трехвход ового элемента ИЛИ 18.13 блока определения отказов 18. На 4 управляющем выходе блока определения отказов 18 формируется сигнал с уровнем логического "0".

Сигналы логического "0" с первого, второго и третьего управляющих выходов блока определения отказов 18 поступают на вторые входы соответственно первого 7, второго 8 и третьего 9 управляемых переключателей, а сигнал логического "0" с четвертого выхода блока определения параметров 18 поступает на третьи входы всех трех управляемых переключателей 7, 8 и 9. С выхода первого элемента И-НЕ 7.1 первого управляемого переключателя 7 сигнал логической "1" поступит на вторые входы первого 7.3 и второго 7.4 элементов И, сигнал логической "1" с выхода второго элемента И-НЕ 7.2 поступит на третий вход первого элемента И 7.3. Кроме того, сигнал логического "0" с третьего входа поступит на третий вход второго элемента И 7.4 и, тем самым, заблокирует второй выход управляемого переключателя. Таким образом, информационная последовательность импульсов, поступившая на первый вход, поступит на первый выход управляемого переключателя 7, а затем на первый вход первого 10 и второй вход второго 11 элементов И. Работа элементов второго 8 и третьего 9 управляемых переключателей аналогична рассмотренной выше работе элементов первого управляемого переключателя 7. Информационный сигнал с первого выхода второго управляемого переключателя 8 поступит на первый вход второго 11 и второй вход третьего 12 элементов И, а информационный сигнал с первого выхода третьего управляемого переключателя 9 поступит на первый вход третьего 12 и второй вход первого 10 элементов И. Так как информационные последовательности импульсов с выхода первого 1, второго 2 и третьего 3 резервных элементов одинаковы, то на выходе первого 10, второго 11 и третьего 12 элементов И формируются сигналы исходной информационной последовательности, которые поступают на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

В случае отказа резервного элемента 1 ( и (или)

и (или)

) на первые L-входовые элементы ИЛИ-НЕ 18.1, И 18.2 блока определения отказов 18 подаются логические "0" при

) на первые L-входовые элементы ИЛИ-НЕ 18.1, И 18.2 блока определения отказов 18 подаются логические "0" при  или логические "1" при

или логические "1" при  На выходах ИЛИ-НЕ 18.1 или И 18.2 формируется сигнал логической "1", который через элемент ИЛИ 18.3 подается на вход первого элемента И-НЕ 7.1 первого управляемого переключателя 7, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 7.3, 7.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 7, блокируя сигнал с выхода регистра сдвига 4. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.3 подается на первый вход блока индикации 19, сигнализируя об отказе первого резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.3 подается на входы элементов И 18.10 и 18.11, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся второй 8 и третий 9 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода первого управляемого переключателя 7 блокирует выходы первого 10 и второго 11 элементов И. На выходе третьего элемента И 12 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов второго 8 и третьего 9 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

На выходах ИЛИ-НЕ 18.1 или И 18.2 формируется сигнал логической "1", который через элемент ИЛИ 18.3 подается на вход первого элемента И-НЕ 7.1 первого управляемого переключателя 7, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 7.3, 7.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 7, блокируя сигнал с выхода регистра сдвига 4. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.3 подается на первый вход блока индикации 19, сигнализируя об отказе первого резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.3 подается на входы элементов И 18.10 и 18.11, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся второй 8 и третий 9 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода первого управляемого переключателя 7 блокирует выходы первого 10 и второго 11 элементов И. На выходе третьего элемента И 12 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов второго 8 и третьего 9 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

В случае отказа резервного элемента 2 ( и (или)

и (или)

) на вторые L-входовые элементы ИЛИ-НЕ 18.4, И 18.5 блока определения отказов 18 подаются логические "0" при

) на вторые L-входовые элементы ИЛИ-НЕ 18.4, И 18.5 блока определения отказов 18 подаются логические "0" при  или логические "1" при

или логические "1" при  На выходах ИЛИ-НЕ 18.4 или И 18.5 формируется сигнал логической "1", который через элемент ИЛИ 18.6 подается на вход первого элемента И-НЕ 8.1 второго управляемого переключателя 8, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 8.3, 8.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 8, блокируя сигнал с выхода регистра сдвига 5. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.6 подается на второй вход блока индикации 19, сигнализируя об отказе второго резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.6 подается на входы элементов И 18.10 и 18.12, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся первый 7 и третий 9 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода второго управляемого переключателя 8 блокирует выходы второго 11 и третьего 12 элементов И. На выходе первого элемента И 10 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов первого 7 и третьего 9 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

На выходах ИЛИ-НЕ 18.4 или И 18.5 формируется сигнал логической "1", который через элемент ИЛИ 18.6 подается на вход первого элемента И-НЕ 8.1 второго управляемого переключателя 8, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 8.3, 8.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 8, блокируя сигнал с выхода регистра сдвига 5. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.6 подается на второй вход блока индикации 19, сигнализируя об отказе второго резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.6 подается на входы элементов И 18.10 и 18.12, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся первый 7 и третий 9 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода второго управляемого переключателя 8 блокирует выходы второго 11 и третьего 12 элементов И. На выходе первого элемента И 10 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов первого 7 и третьего 9 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

В случае отказа резервного элемента 3 ( и (или)

и (или)

) на третьи L-входовые элементы ИЛИ-НЕ 18.7, И 18.8 блока определения отказов 18 подаются логические "0" при

) на третьи L-входовые элементы ИЛИ-НЕ 18.7, И 18.8 блока определения отказов 18 подаются логические "0" при  или логические "1" при

или логические "1" при  На выходах ИЛИ-НЕ 18.7 или И 18.8 формируется сигнал логической "1", который через элемент ИЛИ 18.9 подается на вход первого элемента И-НЕ 9.1 третьего управляемого переключателя 9, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 9.3, 9.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 9, блокируя сигнал с выхода регистра сдвига 6. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.9 подается на третий вход блока индикации 19, сигнализируя об отказе третьего резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.9 подается на входы элементов И 18.11 и 18.12, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся первый 7 и второй 8 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода третьего управляемого переключателя 9 блокирует выходы первого 10 и третьего 12 элементов И. На выходе второго элемента И 11 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов первого 7 и второго 8 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

На выходах ИЛИ-НЕ 18.7 или И 18.8 формируется сигнал логической "1", который через элемент ИЛИ 18.9 подается на вход первого элемента И-НЕ 9.1 третьего управляемого переключателя 9, с выхода которого сигнал с уровнем логического "0" поступает на входы двух элементов И 9.3, 9.4, запрещая, тем самым, прохождение сигналов на 1 и 2 информационные выходы управляемого переключателя 9, блокируя сигнал с выхода регистра сдвига 6. Одновременно сигнал логической "1" с выхода элемента ИЛИ 18.9 подается на третий вход блока индикации 19, сигнализируя об отказе третьего резервного элемента. Кроме того, сигнал с выхода элемента ИЛИ 18.9 подается на входы элементов И 18.11 и 18.12, но при этом сигнал на 4 выходе блока определения отказов останется с уровнем логического "0". Оставшиеся первый 7 и второй 8 управляемые переключатели остаются незаблокированными. Сигнал с уровнем логического "0" с первого выхода третьего управляемого переключателя 9 блокирует выходы первого 10 и третьего 12 элементов И. На выходе второго элемента И 11 будет формироваться исходная информационная последовательность за счет сигналов с первых выходов первого 7 и второго 8 управляемых переключателей, которая поступает в качестве выходной информационной последовательности на первый 13, затем на второй 14 элементы ИЛИ, а затем на информационный выход трехэлементного мажоритарного устройства резервирования.

В случае отказа первого и второго резервных элементов 1, 2 и исправной работе третьего резервного элемента 3 ( и (или)

и (или)

и (или)

и (или)

) работа устройства осуществляется по аналогии со случаями, описанными для отказа первого 1 и второго 2 резервных элементов. В результате на первом и втором выходах блока определения отказов 18 формируются сигналы с уровнем логической "1", которые блокируют информационные последовательности с выходов первого 4 и второго 5 регистров сдвига. Одновременно эти сигналы поступят на первый и второй входы блока индикации 19, сигнализируя об отказе первого и второго резервных элементов. Кроме того, сигналы с уровнем логической "1" с выхода элементов ИЛИ 18.3, 18.6 поступят на входы элементов И 18.10, 18.11, 18.12. На выходе первого элемента И 18.10 появится сигнал с уровнем логической "1", который через элемент ИЛИ 18.13 поступит на третьи входы управляемых переключателей 7, 8, 9. Первый 7 и второй 8 управляемые переключатели остаются заблокированными сигналом логической "1" на их вторых входах, а в третьем управляемом переключателе 9 сигнал с уровнем логической "1" с третьего входа поступит на вход второго элемента И 9.2, с выхода которого сигнал с уровнем логического "0" поступит на третий вход элемент И 9.3, заблокировав, тем самым, первый информационный выход третьего управляемого переключателя 9. Одновременно сигнал с уровнем логической "1" с третьего входа поступит на вход второго элемента И 9.4, разрешив, тем самым, прохождение информационной последовательности с первого входа на второй выход третьего управляемого переключателя 9. Со второго выхода управляемого переключателя 9 информационный сигнал поступит на четвертый вход второго элемента ИЛИ 14 и затем на информационный выход трехэлементного мажоритарного устройства резервирования.

) работа устройства осуществляется по аналогии со случаями, описанными для отказа первого 1 и второго 2 резервных элементов. В результате на первом и втором выходах блока определения отказов 18 формируются сигналы с уровнем логической "1", которые блокируют информационные последовательности с выходов первого 4 и второго 5 регистров сдвига. Одновременно эти сигналы поступят на первый и второй входы блока индикации 19, сигнализируя об отказе первого и второго резервных элементов. Кроме того, сигналы с уровнем логической "1" с выхода элементов ИЛИ 18.3, 18.6 поступят на входы элементов И 18.10, 18.11, 18.12. На выходе первого элемента И 18.10 появится сигнал с уровнем логической "1", который через элемент ИЛИ 18.13 поступит на третьи входы управляемых переключателей 7, 8, 9. Первый 7 и второй 8 управляемые переключатели остаются заблокированными сигналом логической "1" на их вторых входах, а в третьем управляемом переключателе 9 сигнал с уровнем логической "1" с третьего входа поступит на вход второго элемента И 9.2, с выхода которого сигнал с уровнем логического "0" поступит на третий вход элемент И 9.3, заблокировав, тем самым, первый информационный выход третьего управляемого переключателя 9. Одновременно сигнал с уровнем логической "1" с третьего входа поступит на вход второго элемента И 9.4, разрешив, тем самым, прохождение информационной последовательности с первого входа на второй выход третьего управляемого переключателя 9. Со второго выхода управляемого переключателя 9 информационный сигнал поступит на четвертый вход второго элемента ИЛИ 14 и затем на информационный выход трехэлементного мажоритарного устройства резервирования.

В случае отказа первого 1 и третьего 3 резервных элементов или второго 2 и третьего 3 резервных элементов работа устройства осуществляется аналогичным образом.

Работа устройства по маскированию сбоев при функционировании одного из резервных элементов описана в книге: Шубинский И.Б. "Активная защита от отказов управляющих модульных вычислительных систем". - СПб., Наука, 1993 -284 с.

Благодаря новой совокупности существенных признаков в заявленном трехэлементном мажоритарном устройстве резервирования достигается возможность контроля технического состояния резервных элементов и при выходе из строя одного или двух из них выполняется функциональное предназначение, чем обеспечивается более высокая надежность заявляемого устройства по сравнению с известными.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ Ethernet | 2014 |

|

RU2546560C1 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ АТМ | 2009 |

|

RU2408985C2 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

Изобретение относится к области радиотехники. Техническим результатом является повышение надежности системы резервирования за счет контроля отказов резервных элементов и защиты от сбоев. Этот результат достигается за счет введения в прототип блока анализа, блока определения параметров, блока памяти, трех регистров сдвига, блока определения отказов, блока отображения состояния, трех управляемых переключателей, второго элемента ИЛИ и связей между ними. Трехэлементное мажоритарное устройство резервирования состоит из первого (1), второго (2), третьего 3 резервных элементов, первого (4), второго (5), третьего (6) регистров сдвига, первого (7), второго (8) и третьего(9) управляемых переключателей, первого (10), второго (11), третьего (12) элементов И, первого (13), второго (14) элементов ИЛИ, блока анализа (15), блока определения параметров (16), блока памяти (17), блока определения отказов (18), блока отображения состояния (19). Благодаря новой совокупности существенных признаков в заявленном трехэлементном мажоритарном устройстве резервирования достигается возможность контроля технического состояния резервных элементов и при выходе из строя одного или двух из них выполняется функциональное предназначение, чем обеспечивается более высокая надежность заявляемого устройства по сравнению с известными. 7 ил.

Трехэлементное мажоритарное устройство резервирования, содержащее три резервных элемента, три элемента И, один элемент ИЛИ, к первому, второму и третьему входам которого подключены соответственно выходы первого, второго и третьего элементов И, входы первого, второго и третьего резервных элементов являются информационным входом устройства, отличающееся тем, что в его состав дополнительно введены блок анализа, блок определения параметров, блок памяти, три регистра сдвига, блок определения отказов, блок отображения состояния, три управляемых переключателя, второй элемент ИЛИ, выход которого является информационным выходом устройства, причем его первый вход соединен с выходом первого элемента ИЛИ, а второй, третий, четвертый входы подключены соответственно к вторым выходам первого, второго и третьего управляемых переключателей, причем первый выход первого управляемого переключателя соединен с первым входом первого и вторым входом второго элементов И, первый выход второго управляемого переключателя соединен с первым входом второго и вторым входом третьего элементов И, а первый выход третьего управляемого переключателя соединен с первым входом третьего и вторым входом первого элементов И, вторые входы первого, второго и третьего управляемых переключателей являются управляющими и соединены соответственно с первым, вторым и третьим входом блока отображения состояния и соответственно с первым, вторым и третьим выходами блока определения отказов, четвертый выход которого подключен к третьим входам первого, второго и третьего управляемых переключателей, а его вход является информационной шиной, подключенной к выходу блока памяти, другой выход которого соединен с входом блока определения параметров, первый и второй выходы которого подключены соответственно к второму и третьему входу блока памяти, первый вход которого соединен с выходом блока анализа, первый, второй, третий информационные входы которого подключены соответственно к выходам первого, второго, третьего резервных элементов и, соответственно, к входам первого, второго и третьего регистров сдвига, выход каждого из которых подключен соответственно к первым входам первого, второго и третьего управляемых переключателей.

| ЧЕРНЫШЕВ А.А | |||

| Основы конструирования и надежности электронных вычислительных средств | |||

| - М.: Радио и связь, 1998, с.350 | |||

| Устройство для мажоритарного резервирования | 1983 |

|

SU1140278A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Трехканальное резервированное устройство | 1976 |

|

SU618875A1 |

| US 6073251, 06.06.2000. | |||

Авторы

Даты

2008-10-20—Публикация

2007-06-09—Подача