Изобретение относится к импульсной технике, а более конкретно к интегральным системам цифровых линий задержки.

Известны линии задержки, включающие ряд ячеек, включенных последовательно и имеющих отдельные выходы к внешней нагрузке [1]. Для получения необходимой величины задержки с помощью таких схем сигнал снимается с соответствующего выхода. При этом величина задержки по каждому выходу относительно входа кратна величине шага и для каждого выхода прямо пропорциональна количеству ячеек до рассматриваемого выхода. Существенным недостатком данного технического решения является большое количество внешних выходов линии задержки, что усложняет реализацию схемы в интегральном исполнении.

Известны также линии задержки, ячейки которых включает инверторы и интегрирующие RC-цепи [2]. Такие линии задержки имеют вход и выход к внешней нагрузке, включают N ячеек (где N>2), включенных последовательно, каждая из которых имеет вход и выход. Данное техническое решение линии задержки является наиболее близким к заявленному по технической сущности и выбирается в качестве прототипа. Линия задержки - прототип - имеет следующие существенные недостатки. Во-первых, ячейки включают аналоговые элементы в виде RC-цепей, которые занимают большую площадь при интегральном выполнении линии задержки. Во-вторых, большое количество выходов к внешней нагрузке существенно усложняет внутрисхемные соединения в интегральной схеме и, следовательно, увеличивает площадь, занимаемую схемой на кристалле. И, в-третьих, в устройстве-прототипе отсутствует возможность программного изменения величины задержки.

Техническим результатом настоящего изобретения является уменьшение площади, занимаемой линией задержки на кристалле интегральной схемы.

Другим техническим результатом является обеспечение программного управления величиной задержки выходного сигнала относительно сигнала на входе линии задержки.

Эти технические эффекты достигнуты в линии задержки, имеющей вход и выход к внешней нагрузке, включающей N ячеек (где N≥2), включенных последовательно, каждая из которых имеет вход и выход

Отличия линии задержки согласно настоящего изобретения заключаются в том, что ячейки выполнены в виде разряда сдвигового регистра, состоящего из триггера типа М, срабатывающего по заднему фронту первого синхронизирующего импульса и имеющего вход и выход, подключенный ко входу триггера типа S, срабатывающего по переднему фронту первого синхронизирующего импульса, при этом входы триггеров М и S типов всех ячеек подключены к первым входам логических схем «И», ко вторым входам которых подключены по одному выходы 2N разрядов реверсивного сдвигового регистра метки, а выходы упомянутых логических схем «И» подключены ко входам 2N-входовой логической схемы «ИЛИ», выход которой подключен к выходу линии задержки. В регистре метки только одна единица, a (2N-1) - нули. Положение единицы определяет величину задержки.

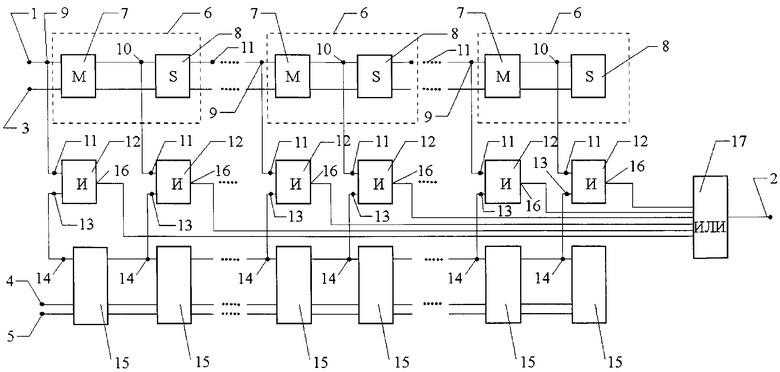

Линия задержки согласно настоящему изобретению поясняется приведенными чертежами.

На чертеже приведена структурная блок-схема линии задержки согласно настоящему изобретению.

Линия задержки согласно настоящему изобретению содержит вход 1 и выход 2 к внешней нагрузке. Вход 3 для подачи первого синхроимпульса. Входы 4 и 5 для подачи второго и третьего синхроимпульсов.

Линия задержки согласно настоящему изобретению содержит N ячеек 6, включенных последовательно (на чертеже N=3). Каждая из ячеек 6 выполнена в виде разряда сдвигового регистра, состоящего из триггера 7 типа М и триггера 8 типа S. Разряды сдвигового регистра 6 имеют входы 9. Выходы 10 триггеров 7 подключены ко входам триггеров 8 S типа. Входы триггеров 7 и 8 всех ячеек 6 подключены к первым входам 11 логических схем «И» 12, ко вторым входам 13 которых подключены по одному входу 14 2N разрядов 15 реверсивного сдвигового регистра метки. Выходы 16 логических схем 12 подключены ко входам 2N-входовой логической схемы «ИЛИ» 17, выход которой подключен к выходу 2 линии задержки согласно настоящему изобретению.

Линия задержки согласно настоящему изобретению работает следующим образом. На вход 1 подается входной сигнал в виде импульсной последовательности. На вход 3 при этом подается первый синхронизирующий импульс. Триггер 7 первого разряда сдвигового регистра перебрасывается в противоположное исходному состояние. При этом на выходе 10 триггера 7 с задержкой по времени формируется выходной сигнал. Величина задержки выходного сигнала относительно входного будет определяться суммой собственной задержки триггера 7 и задержки, определяемой параметрами входной цепи триггера 8 и логической схемы «И-НЕ» 12. Выходной сигнал с выхода триггера 7 поступает на вход триггера 8, срабатывающего по переднему фронту первого синхронизирующего импульса. При этом триггер 8 перебрасывается в состояние, противоположное исходному, и на его выходе 11 появляется выходной сигнал, сдвинутый по времени относительно входного сигнала на время, равное времени задержки. Работа остальных ячеек 7 и 8 сдвигового регистра происходит аналогично описанному выше. Для получения необходимой величины задержки сигнал снимается следующим образом. В один из разрядов 15 2N-разрядный регистр метки записывается «логическая 1», а в остальные (2N-1) разрядов - «логический 0». С помощью второго и третьего синхронизирующих импульсов, которые подаются на входы 4 и 5, записанная «логическая 1» (метка) перемещается из первого разряда 15 реверсивного сдвигового регистра последовательно во второй, третий и N разряды и в обратном порядке.

При этом, когда «метка» находится в каком-либо одном разряде 15, на выходе 14 данного разряда появляется «логическая 1», отпирающая второй вход 13, подключенной логической схемы 12. При наличии на ее первом входе 11 задержанного сигнала, на выходе 16 логической схемы «И» формируется выходной сигнал, который через логическую схему «ИЛИ» 17 поступает на выход 2 линии задержки. Синхросигналы управления на регистр метки могут поступать от схемы фазового детектора, что дает возможность записывать в линию задержки и считывать из нее потоки данных с разными скоростями (частотами синхронизации).

Литература

1. US Patent №4, 330750, 1982.

2. RU Патент №2037953, 19.06.1995, Бюл. №17.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1984 |

|

SU1840489A1 |

| Многопозиционный сенсорный переключатель | 1983 |

|

SU1190516A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU875606A1 |

| Устройство для спектрального анализа сигналов | 1982 |

|

SU1129544A1 |

| Устройство для воспроизведения цифровых сигналов с магнитного носителя | 1990 |

|

SU1737508A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Изобретение относится к импульсной технике. Технический результат заключается в уменьшении площади, занимаемой линией задержки на кристалле интегральной схемы, а также обеспечении программного управления величиной задержки выходного сигнала относительно сигнала на входе линии задержки. Линия задержки содержит сдвиговый регистр, каждя ячейка которого выполнена в виде разряда сдвигового регистра и состоит из триггера типа М, срабатывающего по заднему фронту первого синхронизирующего импульса и имеющего вход и выход, подключенный ко входу триггера типа S, срабатывающего по переднему фронту первого синхронизирующего импульса. При этом входы триггеров М и S типов всех ячеек подключены к первым входам логических схем «И», ко вторым входам которых подключены по одному выходы 2N разрядов реверсивного сдвигового регистра метки, а выходы упомянутых логических схем «И» подключены ко входам 2N-входовой логической схемы «ИЛИ», выход которой подключен к выходу линии задержки. 1 ил.

Линия задержки, имеющая вход и выход к внешней нагрузке, включающая N ячеек (где N≥2), включенных последовательно, каждая из которых имеет вход и выход, отличающаяся тем, что ячейки выполнены в виде разряда сдвигового регистра, состоящего из триггера типа М, срабатывающего по заднему фронту первого синхронизирующего импульса и имеющего вход и выход, подключенный ко входу триггера типа S, срабатывающего по переднему фронту первого синхронизирующего импульса, при этом входы триггеров М и S типов всех ячеек подключены к первым входам логических схем «И», ко вторым входам которых подключены по одному выходы 2N разрядов реверсивного сдвигового регистра метки, а выходы упомянутых логических схем «И» подключены ко входам 2N-входовой логической схемы «ИЛИ», выход которой подключен к выходу линии задержки.

| Устройство задержки | 1975 |

|

SU572909A1 |

| Управляемая линия задержки | 1984 |

|

SU1197068A1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1992 |

|

RU2037953C1 |

| US 4330750, 18.05.1982 | |||

| JP 2001189649 А, 10.07.2001 | |||

| БУКРЕЕВ И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств, Москва, Сов | |||

| радио, 1975, с.85, рис.3.7. | |||

Авторы

Даты

2007-06-27—Публикация

2003-02-18—Подача