Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например, операционных усилителях с токовой обратной связью.

Известны схемы двухтактных выходных каскадов на n-p-n и p-n-p транзисторах [1], которые стали одним из базовых элементов многих аналоговых микросхем, широко используются в структуре различных УНЧ и операционных усилителях как в выходных, так и во входных цепях. Благодаря хорошим статическим и другим характеристикам такие выходные каскады получили специальное название «бриллиантовые» транзисторы. На их совершенствование выдано более 50 патентов в разных странах [1-50].

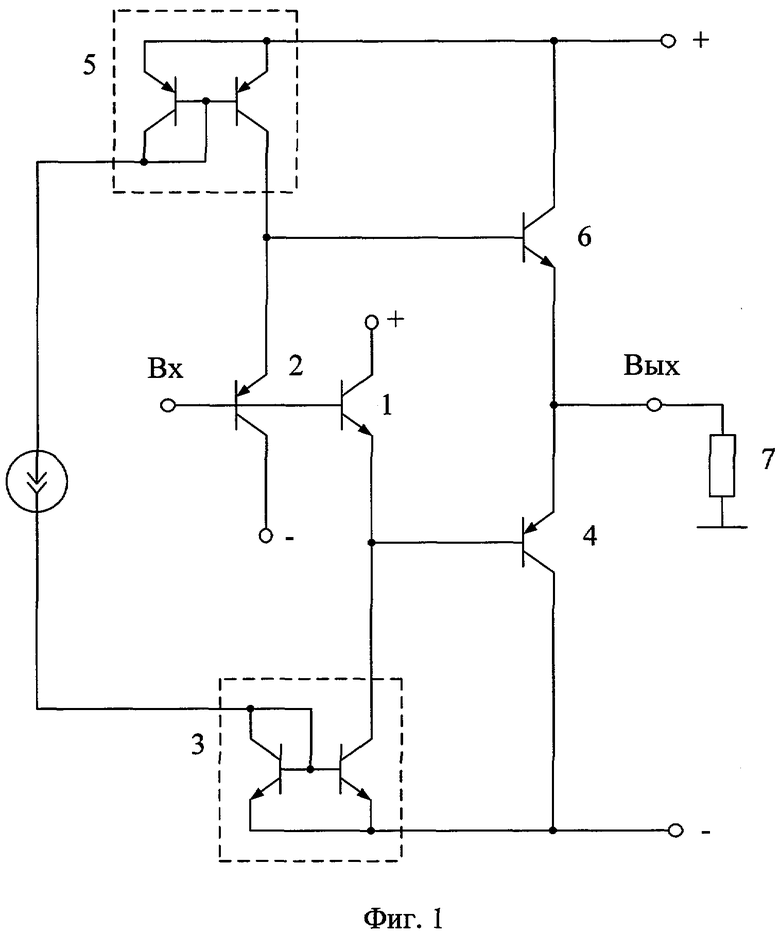

Ближайшим прототипом (фиг.1) заявляемого устройства является выходной каскад, описанный в патентной заявке США US 2005/0127999 A1 (фиг.1) от 16.06.2005, содержащий первый n-p-n 1 и второй p-n-p 2 входные транзисторы с объединенными базами, причем эмиттер первого входного n-p-n 1 транзистора соединен с коллекторным выходом первого токового зеркала 3 и базой первого выходного p-n-p транзистора 4, эмиттер второго входного p-n-p транзистора 2 соединен с коллекторным выходом второго токового зеркала 5 и базой второго выходного n-p-n транзистора 6, а эмиттеры первого 4 и второго 6 выходных транзисторов связаны с нагрузкой 7.

Существенный недостаток известного устройства состоит в том, что оно имеет большое время установления переходного процесса (tфр) при работе с быстроизменяющимися импульсными сигналами большой амплитуды, а также невысокие значения максимальной скорости нарастания выходного напряжения (ϑвых).

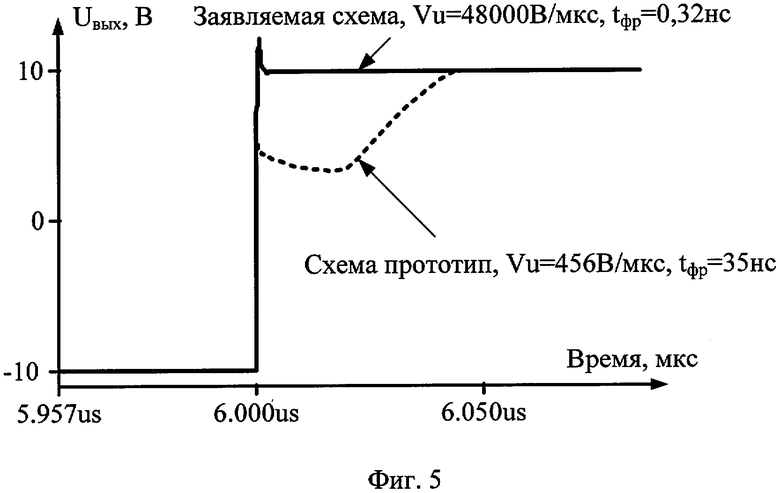

Основная цель предлагаемого изобретения состоит в повышении быстродействия выходного каскада - уменьшении в 20-50 раз времени установления переходного процесса (tфр) для заданной зоны динамической ошибки ε0=10%, и увеличения максимальной скорости нарастания выходного напряжения ϑвых в 20-40 раз.

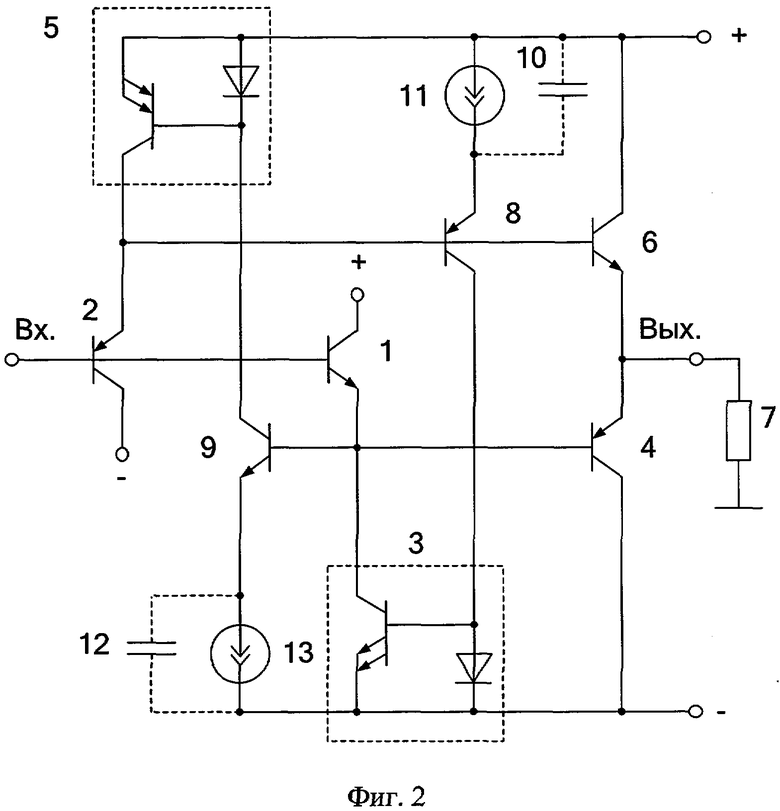

Поставленная цель достигается тем, что в выходной каскад (ВК) фиг.1, содержащий первый n-p-n 1 и второй p-n-p 2 входные транзисторы с объединенными базами, причем эмиттер первого входного n-p-n 1 транзистора соединен с коллекторным выходом первого токового зеркала 3 и базой первого выходного p-n-p транзистора 4, эмиттер второго входного p-n-p транзистора 2 соединен с коллекторным выходом второго токового зеркала 5 и базой второго выходного n-p-n транзистора 6, а эмиттеры первого 4 и второго 6 выходных транзисторов связаны с нагрузкой 7, вводятся новые элементы и связи - первый p-n-p 8 и второй n-p-n 9 вспомогательные транзисторы, причем эмиттер первого вспомогательного p-n-p транзистора 8 соединен с первым корректирующим конденсатором 10 и первым дополнительным источником опорного тока 11, его база подключена к эмиттеру второго 2 входного p-n-p транзистора, а коллектор - ко входу первого токового зеркала 3, эмиттер второго вспомогательного n-p-n транзистора 9 соединен со вторым корректирующим конденсатором 12 и вторым дополнительным источником опорного тока 13, а коллектор подключен ко входу второго токового зеркала 5.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения приведена на чертеже фиг.2.

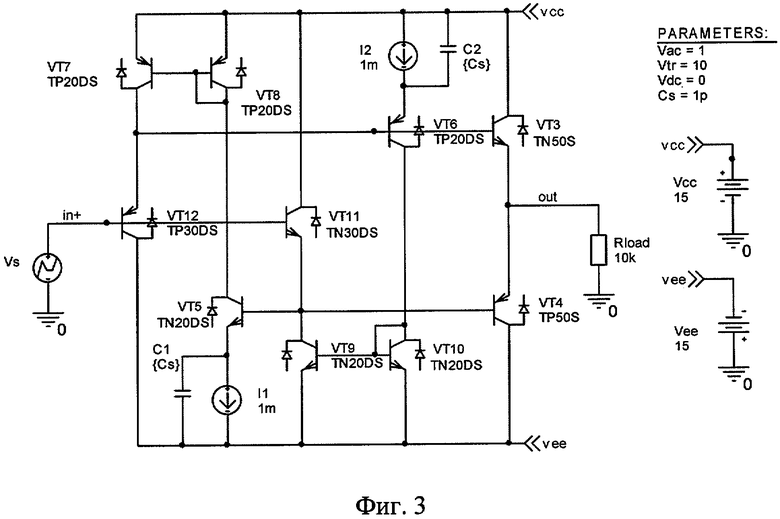

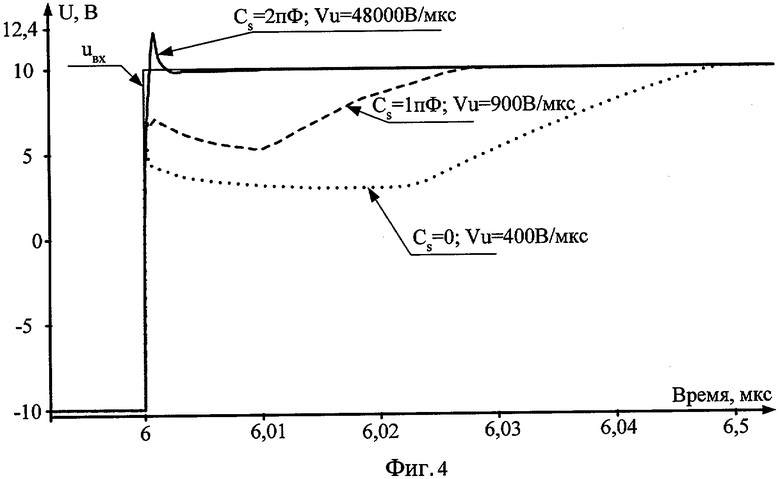

На чертеже фиг.3 показан заявляемый ВК в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар". На чертеже фиг.4, показан переходный процесс на выходе заявляемого устройства при различных значениях емкости корректирующих конденсаторов 10 и 12 (Cs), полученный в результате компьютерного моделирования схемы фиг.3.

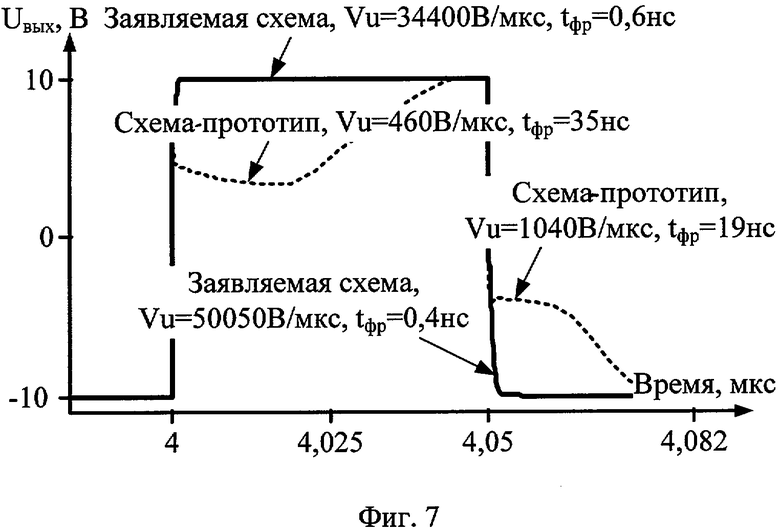

На чертеже фиг.5 показан переходный процесс в заявляемом и известном устройствах, что позволяет сравнить их параметры в одинаковом масштабе и одинаковых режимах измерения.

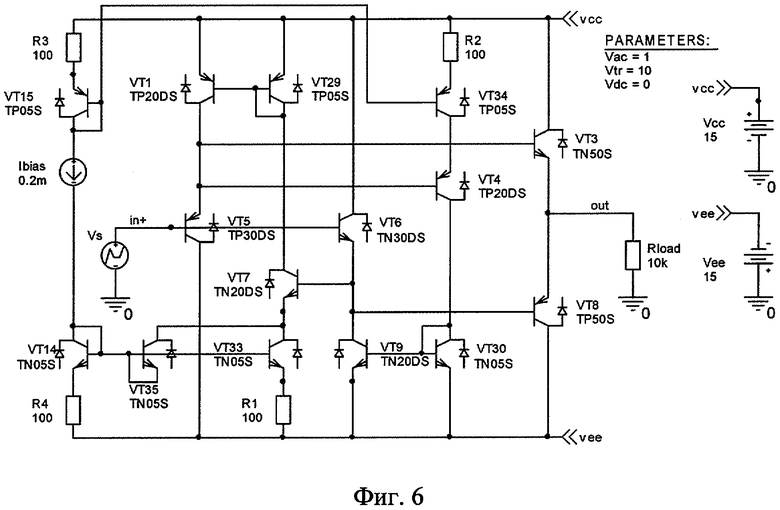

На чертеже фиг.6 показана схема заявляемого ВК по п.2 формулы изобретения в среде PSpice. При этом коэффициент передачи по току первого 3 (VT30, VT9) и второго 5 (VT1, VT29) токовых зеркал выбраны за счет изменения площадей эмиттерных переходов их транзисторов на уровне Ki=4. Это позволило исключить корректирующие конденсаторы 10 и 12 и использовать для повышения быстродействия естественные емкости транзисторов VT33, VT35 и VT34.

На чертеже фиг.7 представлены результаты компьютерного моделирования ВК фиг.6, которые показывают, что заявляемое устройство имеет (в сравнении с прототипом) в 40÷70 раз большую среднюю скорость нарастания выходного напряжения и в 40÷50 раз меньшее время установления переходного процесса.

Выходной каскад фиг.2 содержит первый n-p-n 1 и второй p-n-p 2 входные транзисторы с объединенными базами, причем эмиттер первого входного n-p-n 1 транзистора соединен с коллекторным выходом первого токового зеркала 3 и базой первого выходного p-n-p транзистора 4, эмиттер второго входного p-n-p транзистора 2 соединен с коллекторным выходом второго токового зеркала 5 и базой второго выходного n-p-n транзистора 6, а эмиттеры первого 4 и второго 6 выходных транзисторов связаны с нагрузкой 7. В схему введены первый p-n-p 8 и второй n-p-n 9 вспомогательные транзисторы, причем эмиттер первого вспомогательного p-n-p транзистора 8 соединен с первым корректирующим конденсатором 10 и первым дополнительным источником опорного тока 11, его база подключена к эмиттеру второго 2 входного p-n-p транзистора, а коллектор - ко входу первого токового зеркала 3, эмиттер второго вспомогательного n-p-n транзистора 9 соединен со вторым корректирующим конденсатором 12 и вторым дополнительным источником опорного тока 13, а коллектор подключен ко входу второго токового зеркала 5.

В заявляемом устройстве фиг.2 отношение площадей эмиттерного перехода транзисторов, образующих токовые зеркала 5 и 3 варьируются на уровне 1÷10, что позволяет использовать в качестве корректирующих конденсаторов 10 и 12 емкости на подложку и Скб транзисторов ВК.

Рассмотрим работу заявляемого устройства фиг.2.

В статическом режиме эмиттерные токи транзисторов 1 и 2 равны выходным токам токовых зеркал 3 и 5:

IЭ1=Ki3·I11,

IЭ2=Ki5·I13,

где Кi3, Кi5 - коэффициенты усиления по току токовых зеркал 3 и 5, зависящие от отношения площадей эмиттерных переходов их транзисторов,

I11, I13 - токи источников опорного тока 11 и 13.

В частных случаях коэффициенты Кi3 и Кi5 выбираются в зависимости от численных значений емкостей 10 и 12 и эквивалентных емкостей в эмиттерных цепях транзисторов 1 (С∑1) и 2 (С∑2) в диапазоне 1÷10.

Если на вход ВК подается импульс положительного входного напряжения, близкий к напряжению питания, то это вызывает практически мгновенное запирание транзистора 2. При этом входной импульс передается в эмиттер транзисторов 1, 4, 9, вызывая "скачок" тока коллектора транзистора 9 и, следовательно, выходного тока повторителя 5. Это вызывает быстрый перезаряд суммарной эквивалентной емкости (С∑2) в эмиттерной цепи транзистора 2. Данная емкость складывается из емкостей коллектор-база транзисторов 8 и 6, а также емкости на подложку выходного транзистора токового зеркала 5. Типовые значения С∑2=1÷3 пФ.

Как показывает компьютерное моделирование схем фиг.3, фиг.6 форсирование тока перезаряда паразитной емкости С∑2 повышает быстродействие ВК в 30÷50 раз. При этом данный эффект обеспечивается без увеличения входной емкости ВК и ухудшения стабильности его статического режима.

Источники информации

1. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983.

2. Патент Японии JP 2003258529.

3. Патент Японии JP 2000183666.

4. Патент Японии JP 2000165156.

5. Патент Японии JP 10065457.

6. Патент Японии JP 11167368.

7. Патент Японии JP 10163763.

8. Патент Японии JP 8237044.

9. Патент Японии JP 2004260395.

10. Патент Японии JP 10270954.

11. Патент Японии JP 6204759.

12. Патент Японии JP 11251846.

13. Патент Японии JP 10022747.

14. Патент США №4477780.

15. Патент США №6160451.

16. Патент США №4412184.

17. Патент США №5170134.

18. Патент США №5907262.

19. Патент США №5049653.

20. Патент США №6420933.

21. Патент США №6166603.

22. Патент США №6262633.

23. Патент США №5510754.

24. Патент США №5512859.

25. Патент США №5357211.

26. Патент США №6181204.

27. Патент США №6278356.

28. Патент США №6542032.

29. Патент США №5352969.

30. Патент США №5399991.

31. Патент США №4160216.

32. Патент США №5623230.

33. Патент США №5568090.

34. Патент США №6459338.

35. Патент США №6466062.

36. Патент США №6552612.

37. Патент США №5003269.

38. Патент США №5786731.

39. Патент США №5455533.

40. Патент США №5955908.

41. Патент США №6535063.

42. Патент США №5351012.

43. Патент США №4893091.

44. Патент ЕР 1418668.

45. Патент ЕР 0786858 В1.

46. WO 03/043185 A1.

47. Patent A.P. US 2002/0121934 А1.

48. А. с. СССР 1042156.

49. Патент RU 2168263.

50. А. с. СССР 1506512.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2307455C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2295826C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468500C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421888C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ЦЕПЬЮ КОРРЕКЦИИ КОЭФФИЦИЕНТА УСИЛЕНИЯ | 2011 |

|

RU2459348C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2463703C1 |

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2311729C1 |

Изобретение относится к радиотехнике и связи для использования в качестве выходного устройства для усиления аналоговых сигналов по мощности (буферного усилителя). Технический результат заключается в повышении быстродействия. Выходной каскад (фиг.2) содержит первый n-p-n (1) и второй p-n-p (2) входные транзисторы (Т) с объединенными базами, причем эмиттер первого входного n-p-n (1) Т соединен с коллекторным выходом первого токового зеркала (ТЗ) (3) и базой первого выходного p-n-p Т (4), эмиттер второго входного p-n-p Т (2) соединен с коллекторным выходом второго ТЗ (5) и базой второго выходного n-p-n Т (6), а эмиттеры первого (4) и второго (6) выходных Т связаны с нагрузкой (7). Введены первый p-n-p (8) и второй n-p-n (9) вспомогательные Т, причем эмиттер первого вспомогательного p-n-p Т (8) соединен с первым корректирующим конденсатором (10) и первым дополнительным источником опорного тока (11), его база подключена к эмиттеру второго (2) входного p-n-p Т, а коллектор - ко входу первого ТЗ (3), эмиттер второго вспомогательного n-p-n Т (9) соединен со вторым корректирующим конденсатором (12) и вторым дополнительным источником опорного тока (13), а коллектор подключен ко входу второго ТЗ (5). 1 з.п. ф-лы, 7 ил.

| Двухтактный усилитель мощности | 1982 |

|

SU1113877A1 |

| Выбивная решетка для выбивки отливок | 1981 |

|

SU1042884A1 |

| Повторитель | 1979 |

|

SU785952A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 5049653, 17.09.1991. | |||

Авторы

Даты

2007-09-27—Публикация

2006-03-01—Подача