Изобретение относится к области автоматики и вычислительной техники, и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления.

Известно устройство (пат.2338241 С1 Российская Федерация, МПК G06F 7/523, G06F 7/72 (2006.01). заявл. 22.03.2007; опубл. 10.11.2008.), содержащее генератор гармонического сигнала, управляемые фазовращатели, измеритель фазы гармонического сигнала, группу фазовращателей на фиксированное значение фазы, шифраторы, входы устройства первого операнда, дешифраторы, элементы ИЛИ, блоки умножения на константу по модулю, элементы И, входы устройства разрядов второго операнда, сумматор по модулю два, преобразователь кода числа х в р-х, выход устройства. Недостаток устройства - низкое быстродействие.

Известно также устройство (пат. 2653310 С1 Российская Федерация, МПК G06F 7/72 (2006.01). заявл. 24.05.2017; опубл. 07.05.2018.) содержащее синхронизирующий вход, вход первого сомножителя, входы устройства разрядов второго сомножителя, переключатели, блоки умножения фазы на два в степени, блоки сложения фаз, выход. Недостаток устройства - низкие функциональные возможности.

Наиболее близким к заявляемому является изобретение (пат. 2656992 С1 Российская Федерация, МПК G06F 7/72 (2006.01). заявл. 24.05.2017; опубл. 07.06.2018.), содержащее синхронизирующий вход, входы первого и второго операнда, вход номера операции, мультиплексор, блоки памяти, дешифратор, фазовращатели на фиксированное значение фазы 2π/m, фазированные ключи, управляемые фазовращатели, сумматоры сигналов, результирующий сумматор сигналов, выход.

Недостаток - низкое быстродействие устройства. Это определяется алгоритмом функционирования и структурой составляющих его узлов.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в сокращении времени на выполнение арифметических операций, реализуемых на основе единой конструкции.

Технический результат выражается в повышении быстродействия.

Технический результат достигается тем, что в арифметическое

устройство по модулю m, содержащее синхронизирующий вход устройства, входы устройства первого и второго операнда, вход номера операции устройства, мультиплексор, k блоков памяти (k-количество различных выполняемых устройством операций), дешифратор, m-1 фазовращателей на фиксированное значение фазы 2π/m, первую и вторую группы из m управляемых фазовращателей, первую и вторую группы из m фазированных ключей, первый и второй сумматор сигналов, выход устройства, введены сумматор фаз, первый и второй блоки разности фаз, первый и второй аналоговые мультиплексоры, при этом синхронизирующий вход устройства объединен с третьими входами сумматора фаз и обоих блоков разности фаз, с входом первого фазовращателя на фиксированное значение фазы 2π/m, а также первыми входами всех управляемых фазовращателей и первыми входами первых фазированных ключей обеих групп, вход устройства первого операнда объединен с первым входом сумматора фаз, вторым входом первого аналогового мультиплексора, первым входом первого блока разности фаз, при этом выход сумматора фаз соединен с первым входом первого аналогового мультиплексора, первый выход которого соединен с вторыми входами фазированных ключей первой группы, вход устройства второго операнда объединен с вторым входом сумматора фаз, третьим входом первого аналогового мультиплексора, вторым входом первого блока разности фаз, выход которого соединен с четвертым входом первого аналогового мультиплексора, третий выход которого соединен с вторыми входами фазированных ключей второй группы, при этом второй выход первого аналогового мультиплексора соединен с первым входом второго аналогового мультиплексора, при этом выход s-го фазовращателя на фиксированное значение фазы 2π/m  соединен с первыми входами s+1-ых фазированных ключей обеих групп, выход t-го фазовращателя на фиксированное значение фазы 2π/m

соединен с первыми входами s+1-ых фазированных ключей обеих групп, выход t-го фазовращателя на фиксированное значение фазы 2π/m  также соединен с входом t+1-го фазовращателя на фиксированное значение фазы 2π/m, выходы блоков памяти соединены с соответствующими входами мультиплексора, вход номера операции устройства объединен с k+1-ым входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров, а также с вторыми входами управляемых фазовращателей обеих групп, выходы которых соединены с третьими входами соответствующих фазированных ключей соответствующих групп, выходы которых соединены с соответствующими входами соответствующих группам сумматоров сигналов, выходы которых соединены с соответствующими входами второго блока разности фаз, а также с вторым и четвертым входами второго аналогового мультиплексора соответственно, при этом выход второго блока разности фаз соединен с третьим входом второго аналогового мультиплексора, выход которого объединен с выходом устройства.

также соединен с входом t+1-го фазовращателя на фиксированное значение фазы 2π/m, выходы блоков памяти соединены с соответствующими входами мультиплексора, вход номера операции устройства объединен с k+1-ым входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров, а также с вторыми входами управляемых фазовращателей обеих групп, выходы которых соединены с третьими входами соответствующих фазированных ключей соответствующих групп, выходы которых соединены с соответствующими входами соответствующих группам сумматоров сигналов, выходы которых соединены с соответствующими входами второго блока разности фаз, а также с вторым и четвертым входами второго аналогового мультиплексора соответственно, при этом выход второго блока разности фаз соединен с третьим входом второго аналогового мультиплексора, выход которого объединен с выходом устройства.

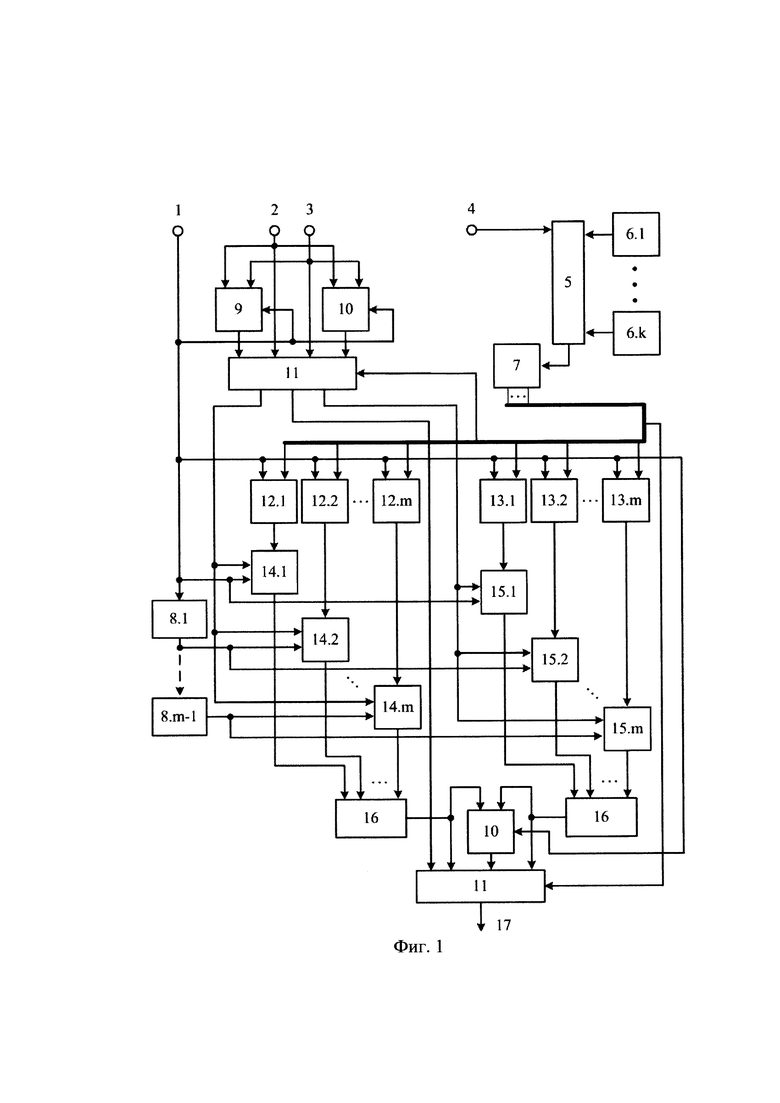

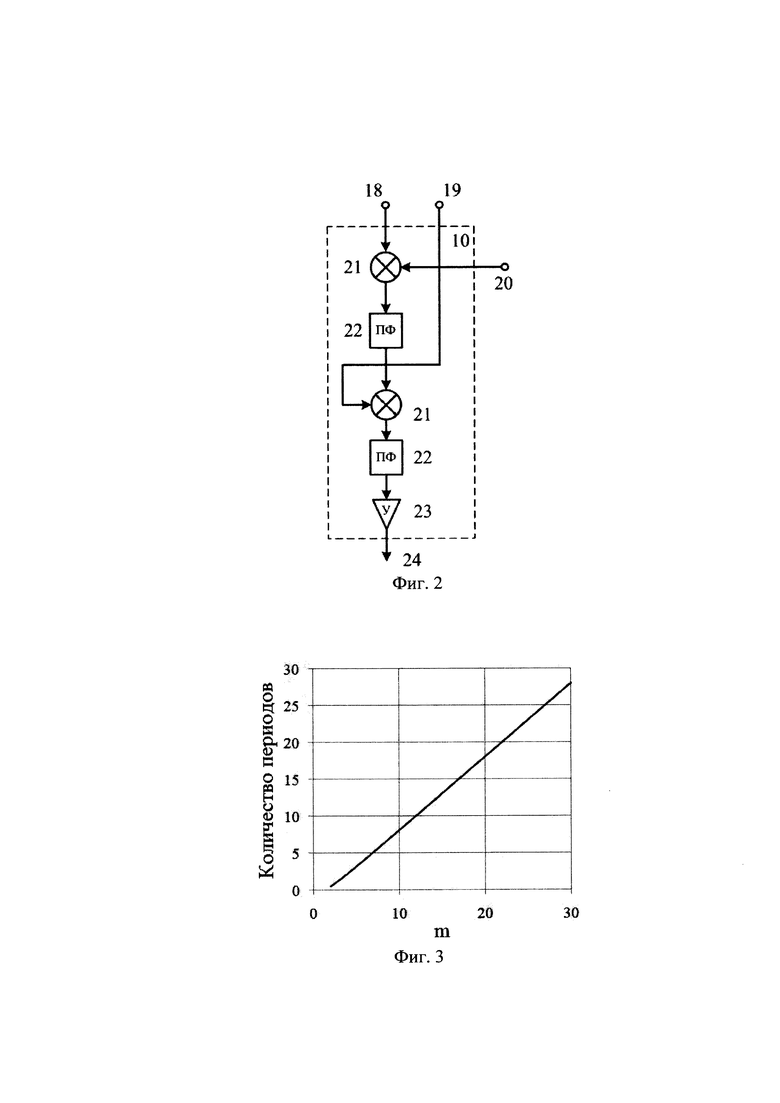

На фиг. 1 представлена структурная схема арифметического устройства по модулю т.

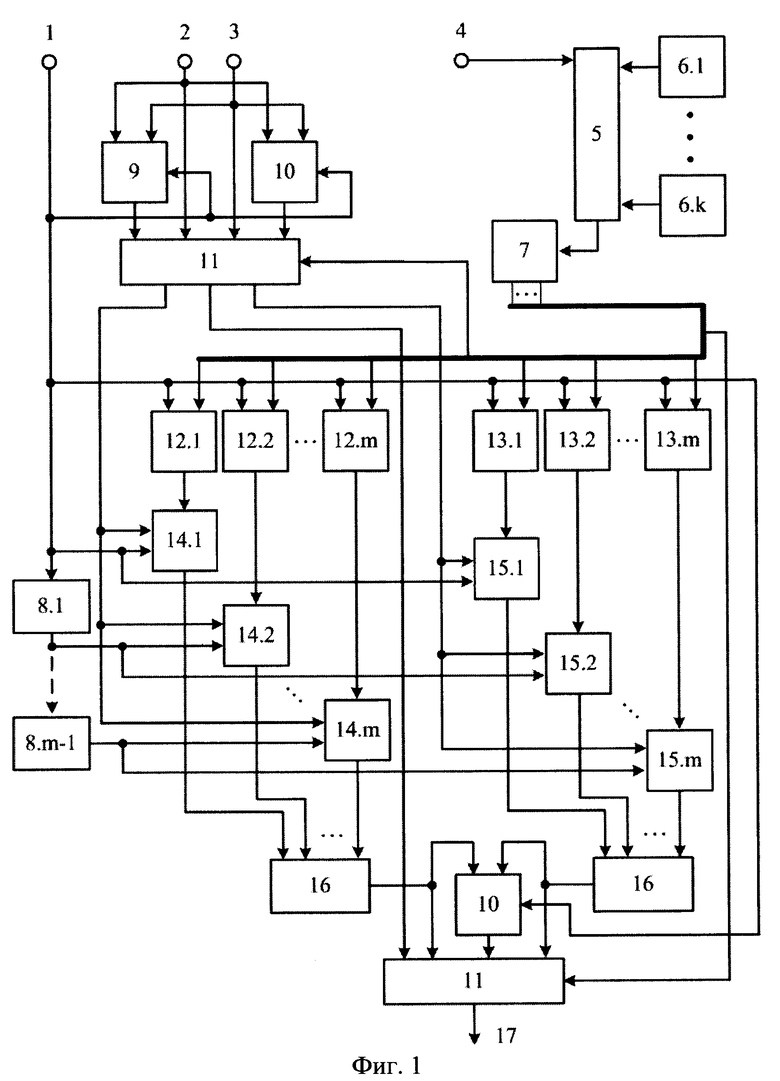

На фиг. 2 приведена схема блока разности фаз.

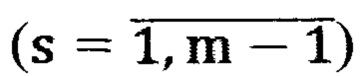

На фиг. 3 приведена зависимость максимальной задержки на линейке фазовращателей прототипа для операции умножения от модуля системы остаточных классов.

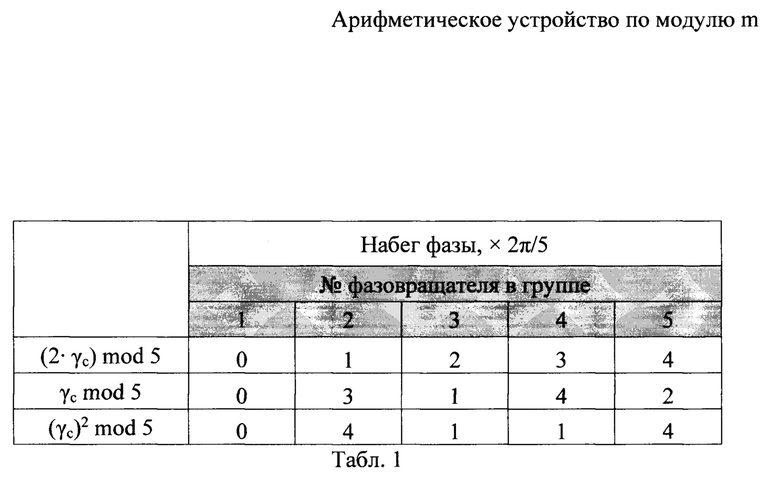

В табл.1 приведены настройки управляемых фазовращателей для операции

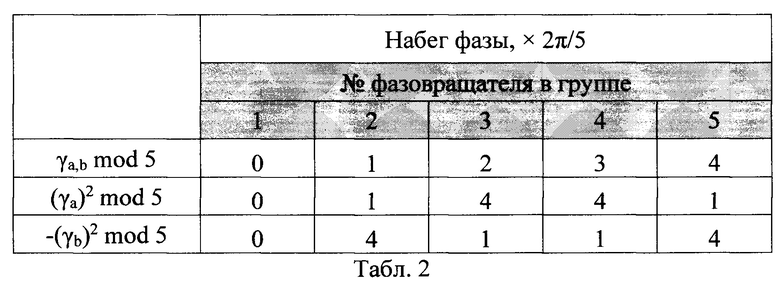

В табл.2 приведены настройки управляемых фазовращателей для операции

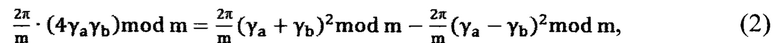

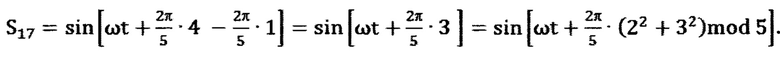

Сущность изобретения заключается в реализации конструкции на основе как алгоритма умножения двух операндов, так и табличного способа вычислений, что определяет не только многофункциональность устройства, но и повышение быстродействия по сравнению с прототипом. Как известно, квадраты суммы и разности, при вычитании второго из первого, позволяют представить умножение двух чисел в виде:

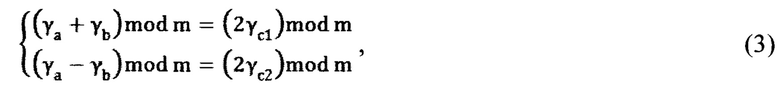

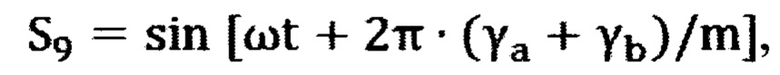

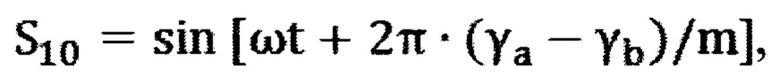

Перепишем выражение с учетом дискретно-фазированного представления по модулю m:

где γа и γb - вычеты чисел а и b по модулю m. В правой части для суммы и разности входных операндов произведем замену так, что:

тогда выражение (2) примет вид:

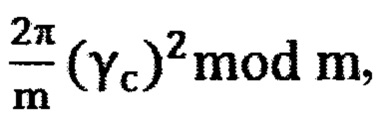

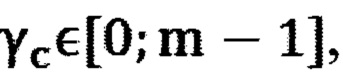

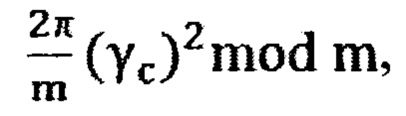

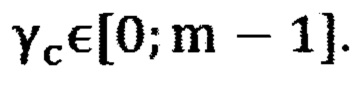

Если использовать результаты сложения и вычитания исходных операндов в качестве адресов для выбора набегов по фазе из заданных для функции умножения и равных  где

где  то останется только последнее вычитание фаз для окончательного выполнения алгоритма.

то останется только последнее вычитание фаз для окончательного выполнения алгоритма.

Для обоснования реализуемого эффекта необходимо оценить время прохождения сигнала через все узлы. В прототипе сигналы операндов последовательно распространяются через два фазированных ключа, линию задержки из ряда управляемых фазовращателей и два сумматора сигналов. В реализуемом устройстве - один фазированный ключ, два блока вычитания (сложения) фаз, один управляемый фазовращатель, один сумматор сигналов и два аналоговых мультиплексора. Удобнее всего воспользоваться величиной задержки, измеренной в количестве периодов. Поскольку структура устройства базируется на основе алгоритма умножения, то в первую очередь рассмотрим решение задачи для данной арифметической операции.

Во-первых, в составе известного по прототипу фазированном ключе (патент РФ №2656992, фиг. 2) содержится полупроводниковый ключ, который, работая с сигналами в СВЧ диапазоне, в лучшем случае осуществляет включение\выключение в течение единиц наносекунд (стр. 12, Щаврук Н.В. Проектирование и изготовление микроэлектромеханических переключателей на подложках GaAs для СВЧ диапазона: дис. … канд. техн. наук: 05.27.01 / Москва. 2015. 130 с.). Поскольку в реализуемом устройстве сигнал проходит лишь через один полупроводниковый ключ, то, при условии работы остальных компонентов на частотах до 100ГГц, должен наблюдаться рост быстродействия практически в два раза.

Во-вторых, если допустить возможность функционирования полупроводникового ключа с приемлемым качеством и достаточным быстродействием (до 100 ГГц) или использования фазированного ключа другой конструкции (патент РФ №2659866), то можно заметить, что без учета управляемых фазовращателей количество узлов, дающих задержку сигнала в прототипе и реализуемом устройстве, примерно одинаково. Как видно из примера операции умножения для прототипа (патент РФ №2656992, фиг. 5), максимальную задержку на линейках фазовращателей можно определить выражением:

что дает практически линейный рост в зависимости от модуля системы остаточных классов (фиг. 3). В реализуемом устройстве задержка на управляемом фазовращателе постоянна и не превышает один период. Таким образом наблюдается эффект повышения быстродействия в реализуемом устройстве с ростом модуля системы остаточных классов.

Для операций сложения и вычитания в реализуемом устройстве возможна коммутация соответствующих блоков 9 и 10 (фиг. 1) через аналоговые мультиплексоры 11 непосредственно к выходу 17, что с учетом примерного равенства по количеству элементов двух блоков сложения (вычитания) одному фазированному ключу, дает кратное увеличение быстродействия по сравнению с прототипом.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1, должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Показанная на фиг. 1 структурная схема арифметического устройства по модулю m содержит синхронизирующий вход устройства 1, входы устройства первого 2 и второго 3 операнда, вход номера операции устройства 4, мультиплексор 5, блоки памяти 6.1-6.k, дешифратор 7, фазовращатели на фиксированное значение фазы 2π/m 8.1-8.(m-1), сумматор фаз 9, первый и второй блоки разности фаз 10, первый и второй аналоговые мультиплексоры 11, первую 12.1-12.m и вторую 13.1-13.m группы управляемых фазовращателей, первую 14.1-14.m и вторую 15.1-15.m группы фазированных ключей, первый и второй сумматор сигналов 16, выход устройства 17.

Синхронизирующий вход устройства 1 объединен с третьими входами сумматора фаз 9 и обоих блоков разности фаз 10, с входом фазовращателя на фиксированное значение фазы 2π/m 8.1, а также первыми входами управляемых фазовращателей 12.1-12.m и 13.1-13.m, и первыми входами фазированных ключей 14.1 и 15.1, вход устройства первого операнда 2 объединен с первым входом сумматора фаз 9, вторым входом первого аналогового мультиплексора 11, первым входом первого блока разности фаз 10, при этом выход сумматора фаз 9 соединен с первым входом первого аналогового мультиплексора 11, первый выход которого соединен с вторыми входами фазированных ключей 14.1-14.m, вход устройства второго операнда 3 объединен с вторым входом сумматора фаз 9, третьим входом первого аналогового мультиплексора 11, вторым входом первого блока разности фаз 10, выход которого соединен с четвертым входом первого аналогового мультиплексора 11, третий выход которого соединен с вторыми входами фазированных ключей 15.1-15.m, при этом второй выход первого аналогового мультиплексора 11 соединен с первым входом второго аналогового мультиплексора 11, при этом выход фазовращателя на фиксированное значение фазы 2π/m 8.s  соединен с первыми входами фазированных ключей 14.s+1 и 15.s+1, выход фазовращателя на фиксированное значение фазы 2π/m 8.t

соединен с первыми входами фазированных ключей 14.s+1 и 15.s+1, выход фазовращателя на фиксированное значение фазы 2π/m 8.t  также соединен с входом фазовращателя на фиксированное значение фазы 2π/m 8.t+1, выходы блоков памяти 6.1-6.k соединены с соответствующими входами мультиплексора 5, вход номера операции устройства 4 объединен с k+1-ым входом мультиплексора 5, выход которого соединен с входом дешифратора 7, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров 11, а также с вторыми входами управляемых фазовращателей 12.1-12.m и 13.1-13.m, выходы которых соединены с третьими входами соответствующих фазированных ключей 14.l-14.m и 15.1-15.m соответственно, выходы которых соединены с соответствующими входами соответствующих группам сумматоров сигналов 16, выходы которых соединены с соответствующими входами второго блока разности фаз 10, а также с вторым и четвертым входами второго аналогового мультиплексора 11 соответственно, при этом выход второго блока разности фаз соединен 10 с третьим входом второго аналогового мультиплексора 11, выход которого объединен с выходом устройства 17.

также соединен с входом фазовращателя на фиксированное значение фазы 2π/m 8.t+1, выходы блоков памяти 6.1-6.k соединены с соответствующими входами мультиплексора 5, вход номера операции устройства 4 объединен с k+1-ым входом мультиплексора 5, выход которого соединен с входом дешифратора 7, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров 11, а также с вторыми входами управляемых фазовращателей 12.1-12.m и 13.1-13.m, выходы которых соединены с третьими входами соответствующих фазированных ключей 14.l-14.m и 15.1-15.m соответственно, выходы которых соединены с соответствующими входами соответствующих группам сумматоров сигналов 16, выходы которых соединены с соответствующими входами второго блока разности фаз 10, а также с вторым и четвертым входами второго аналогового мультиплексора 11 соответственно, при этом выход второго блока разности фаз соединен 10 с третьим входом второго аналогового мультиплексора 11, выход которого объединен с выходом устройства 17.

Показанная на фиг. 2 схема блока разности фаз содержит первый 18, второй 19 и третий 20 входы, первый и второй смеситель 21, первый и второй полосовой фильтр 22, усилитель 23, выход 24.

Второй вход 19 объединен с первым входом второго смесителя 21, первый вход 18 объединен с первым входом первого смесителя 21, третий вход 38 объединен с вторым входом первого смесителя 21, выход которого соединен с входом первого полосового фильтра 22, выход которого соединен с вторым входом второго смесителя 21, выход которого соединен с входом второго полосового фильтра 22, выход которого соединен с входом усилителя 23, выход которого объединен с выходом 24.

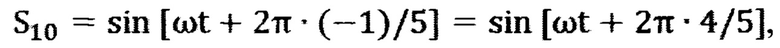

Работа устройства осуществляется следующим образом. Заранее определяется операция, выполняемая на данный момент реализуемым устройством, посредством подключения необходимого блока памяти и настройки аналоговых мультиплексоров и управляемых фазовращателей. На соответствующие входы устройства подаются гармоники одной частоты:

- синхронизирующий S1=sin (ωt),

- первый операнд S2=sin (ωt+2 π ⋅ γa/m),

- второй операнд S3=sin (ωt+2 π ⋅ γb/m),

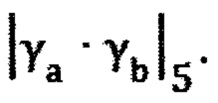

где γa и γb - вычеты по модулю m над которыми осуществляется необходимая операция. В качестве иллюстрации работы устройства рассмотрим три функции: вычитание, умножение и сумму квадратов двух операторов по модулю m.

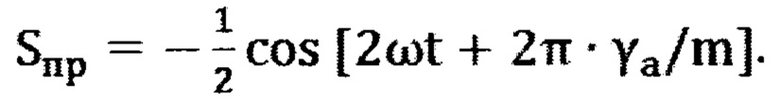

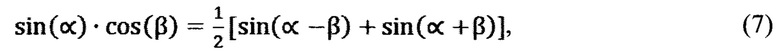

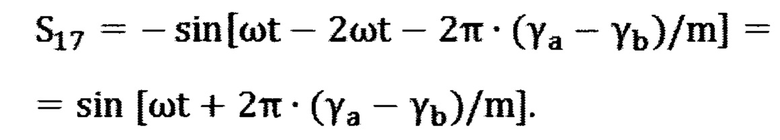

1. Выход первого блока разности фаз 10 через аналоговые мультиплексоры 11 коммутируется непосредственно к выходу 17. Первый S2, второй S3 операнды и синхронизирующий сигнал S1 поступают на входы 18, 19 и 20 первого блока разности фаз 10 соответственно (фиг. 2). На первом смесителе 21 производится перемножение сигналов S2 и S1. Из известного тригонометрического выражения

следует, что после полосовой фильтрации высокочастотной составляющей на первом блоке 22 формируется промежуточный результат:

Гармонический сигнал S3, перемножается вторым смесителем 21 с промежуточной гармоникой. Реализация тригонометрического выражения

после полосовой фильтрации более низкочастотной составляющей на втором блоке 22 и усиления в блоке 23 дает результат в виде гармоники с единичной амплитудой и фазой смещенной относительно синхронизирующего сигнала на 2 π ⋅ (γа - γb)/m:

2. Сумматор фаз 9 и первый блок разности фаз 10 через первый аналоговый мультиплексор 11 коммутируются на входы соответствующих фазированных ключей 14.1-14.m и 15.1-15.m. Управляемые фазовращатели 12.1-12.m и 13.1-13.m настраиваются в соответствии с операцией умножения на набеги фазы  где

где  Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

Блоки 9 и 10 формируют сумму и разности фаз гармоник входных операндов:

которые используются в качестве адреса, позволяющих пропустить сигналы от соответствующих управляемых фазовращателей с фазами кратными 2 π/m. На втором блоке разности фаз 10 происходит окончательная реализация алгоритма, соответствующего выражению (4):

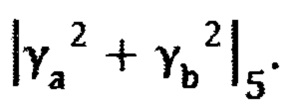

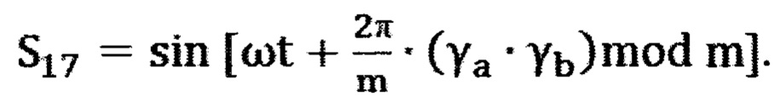

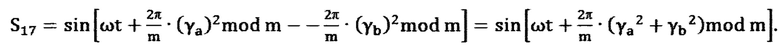

3. Входы операторов 2 и 3 через первый аналоговый мультиплексор 11 коммутируются на соответствующие фазированных ключи 14.1-14.m и 15.1-15.m. Управляемые фазовращатели 12.1-12.m и 13.1-13.m настраиваются в соответствии с функцией на квадрат и минус квадрат операнда по модулю. Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

Сигналы входных операндов используются в качестве адреса и позволяют пропустить гармоники от соответствующих управляемых фазовращателей с фазами кратными 2 π/m. На втором блоке разности фаз 10 происходит вычитание минус квадрата второго операнда из квадрата первого, реализуя конечный результат:

Пример.

На соответствующие входы устройства подаются гармоники одной частоты:

- синхронизирующий S1=sin (ωt),

- первый операнд S2=sin (ωt+2 π ⋅ 2/5),

- второй операнд S3=sin (ωt+2 π ⋅ 3/5),

где γа=2, γb=3 - вычеты по модулю 5 над которыми осуществляется необходимая операция. Рассмотрим три функции: вычитание, умножение и сумму квадратов двух операторов по модулю 5.

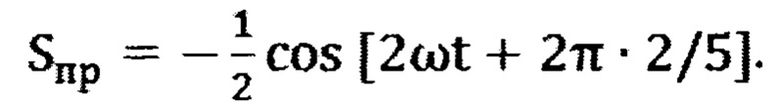

1. Выход первого блока разности фаз 10 через аналоговые мультиплексоры 11 коммутируется непосредственно к выходу 17. Первый S2, второй S3 операнды и синхронизирующий сигнал S1 поступают на входы 18, 19 и 20 первого блока разности фаз 10 соответственно (фиг. 2). На первом смесителе 21 производится перемножение сигналов S2 и S1. Из выражения (6) следует, что после полосовой фильтрации высокочастотной составляющей на первом блоке 22 формируется промежуточный результат:

Гармонический сигнал S3, перемножается вторым смесителем 21 с промежуточной гармоникой. Реализация тригонометрического выражения (7)

после полосовой фильтрации более низкочастотной составляющей на втором блоке 22 и усиления в блоке 23 дает результат в виде гармоники с единичной амплитудой и фазой смещенной относительно синхронизирующего сигнала на 2 π ⋅ (2-3)/5:

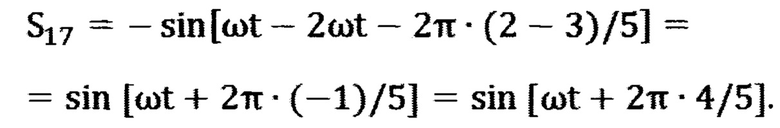

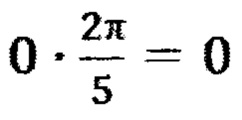

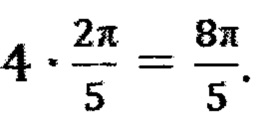

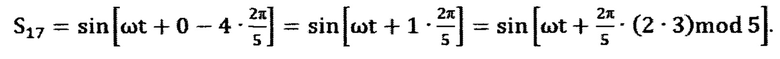

2. Сумматор фаз 9 и первый блок разности фаз 10 через первый аналоговый мультиплексор 11 коммутируются на входы соответствующих фазированных ключей 14.1-14.5 и 15.1-15.5. Управляемые фазовращатели 12.1-12.5 и 13.1-13.5 настраиваются в соответствии с операцией умножения на  (табл. 1). Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

(табл. 1). Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

Блоки 9 и 10 формируют сумму и разности фаз гармоник входных операндов:

которые используются в качестве адреса, позволяющих пропустить сигналы от управляемых фазовращателей 12.1 и 13.5 соответственно с фазами равными  и

и  На втором блоке разности фаз 10 происходит окончательная реализация алгоритма, соответствующего выражению (4):

На втором блоке разности фаз 10 происходит окончательная реализация алгоритма, соответствующего выражению (4):

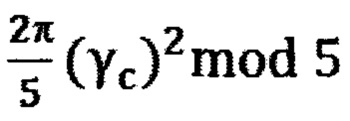

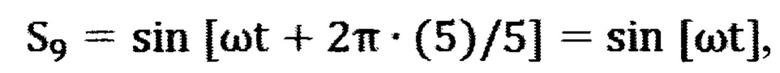

3. Входы операторов 2 и 3 через первый аналоговый мультиплексор 11 коммутируются на соответствующие фазированных ключи 14.1-14.5 и 15.1-15.5. Управляемые фазовращатели 12.1-12.5 и 13.1-13.5 настраиваются в соответствии с функцией на квадрат и минус квадрат операнда по модулю (табл. 2). Второй аналоговый мультиплексор 11 подключает выход 17 к выходу второго блока разности фаз 10.

Сигналы входных операндов используются в качестве адреса и позволяют пропустить гармоники от управляемых фазовращателей 12.3 и 13.4 с фазами 4⋅2 π/5 и 1⋅2 π/5 соответственно. На втором блоке разности фаз 10 происходит вычитание минус квадрата второго операнда из квадрата первого, реализуя конечный результат:

Полученное устройство отражает принципы построения арифметических устройств на основе системы остаточных классов, работающих с дискретно-фазированной формой представления чисел. С точки зрения практического применения устройство реализует возможность построения аналоговых вычислителей СВЧ диапазона, превосходящих по быстродействию современный уровень ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| ФАЗИРОВАННЫЙ КЛЮЧ ПО МОДУЛЮ m | 2017 |

|

RU2659866C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство управления ферритовыми фазовращателями модульной фазированной антенной решетки | 2018 |

|

RU2698957C1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Устройство сложения (вычитания) N чисел с настраиваемым модулем | 2016 |

|

RU2637988C1 |

Изобретение относится к арифметическому устройству по модулю m. Технический результат заключается в повышении быстродействия работы устройства. Устройство содержит синхронизирующий вход устройства, входы устройства первого и второго операнда, вход номера операции устройства, мультиплексор, k блоков памяти (k-количество различных выполняемых устройством операций), дешифратор, m-1 фазовращателей на фиксированное значение фазы 2π/m, первую и вторую группы из m управляемых фазовращателей, первую и вторую группы из m фазированных ключей, первый и второй сумматор сигналов, выход устройства, сумматор фаз, первый и второй блоки разности фаз, первый и второй аналоговые мультиплексоры. 3 ил., 2 табл.

Арифметическое устройство по модулю m, содержащее синхронизирующий вход устройства, входы устройства первого и второго операнда, вход номера операции устройства, мультиплексор, k блоков памяти (k - количество различных выполняемых устройством операций), дешифратор, m-1 фазовращателей на фиксированное значение фазы 2π/m, первую и вторую группы из m управляемых фазовращателей, первую и вторую группы из m фазированных ключей, первый и второй сумматоры сигналов, выход устройства, отличающееся тем, что введены сумматор фаз, первый и второй блоки разности фаз, первый и второй аналоговые мультиплексоры, при этом синхронизирующий вход устройства объединен с третьими входами сумматора фаз и обоих блоков разности фаз, с входом первого фазовращателя на фиксированное значение фазы 2π/m, а также первыми входами всех управляемых фазовращателей и первыми входами первых фазированных ключей обеих групп, вход устройства первого операнда объединен с первым входом сумматора фаз, вторым входом первого аналогового мультиплексора, первым входом первого блока разности фаз, при этом выход сумматора фаз соединен с первым входом первого аналогового мультиплексора, первый выход которого соединен с вторыми входами фазированных ключей первой группы, вход устройства второго операнда объединен с вторым входом сумматора фаз, третьим входом первого аналогового мультиплексора, вторым входом первого блока разности фаз, выход которого соединен с четвертым входом первого аналогового мультиплексора, третий выход которого соединен с вторыми входами фазированных ключей второй группы, при этом второй выход первого аналогового мультиплексора соединен с первым входом второго аналогового мультиплексора, при этом выход s-го фазовращателя на фиксированное значение фазы 2π/m  соединен с первыми входами s+1-х фазированных ключей обеих групп, выход t-го фазовращателя на фиксированное значение фазы 2π/m

соединен с первыми входами s+1-х фазированных ключей обеих групп, выход t-го фазовращателя на фиксированное значение фазы 2π/m  также соединен с входом t+1-го фазовращателя на фиксированное значение фазы 2π/m, выходы блоков памяти соединены с соответствующими входами мультиплексора, вход номера операции устройства объединен с k+1-м входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров, а также с вторыми входами управляемых фазовращателей обеих групп, выходы которых соединены с третьими входами соответствующих фазированных ключей соответствующих групп, выходы которых соединены с соответствующими входами соответствующих групп сумматоров сигналов, выходы которых соединены с соответствующими входами второго блока разности фаз, а также с вторым и четвертым входами второго аналогового мультиплексора соответственно, при этом выход второго блока разности фаз соединен с третьим входом второго аналогового мультиплексора, выход которого объединен с выходом устройства.

также соединен с входом t+1-го фазовращателя на фиксированное значение фазы 2π/m, выходы блоков памяти соединены с соответствующими входами мультиплексора, вход номера операции устройства объединен с k+1-м входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена с пятыми входами обоих аналоговых мультиплексоров, а также с вторыми входами управляемых фазовращателей обеих групп, выходы которых соединены с третьими входами соответствующих фазированных ключей соответствующих групп, выходы которых соединены с соответствующими входами соответствующих групп сумматоров сигналов, выходы которых соединены с соответствующими входами второго блока разности фаз, а также с вторым и четвертым входами второго аналогового мультиплексора соответственно, при этом выход второго блока разности фаз соединен с третьим входом второго аналогового мультиплексора, выход которого объединен с выходом устройства.

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| Устройство сложения (вычитания) N чисел с настраиваемым модулем | 2016 |

|

RU2637988C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ | 1999 |

|

RU2157560C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 5381360 A1, 10.01.1995. | |||

Авторы

Даты

2021-05-31—Публикация

2020-08-05—Подача