Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления.

Известен умножитель по модулю (пат. 2589361 C1, Российская Федерация, МПК G06F 7/523 (2006.01), заявл. 10.03.2015; опубл. 10.07.2016), содержащий входы, двухвходовые сумматоры по модулю два, двухвходовые элементы И, сумматоры по модулю два, выходы. Недостаток - низкое быстродействие.

Известно устройство умножения на константу по модулю (фиг. 2, авт. св. СССР №1617439 А1, МКИ G06F 7/72 (2006.01), заявл. 13.12.1988; опубл. 30.12.1990), содержащее группу элементов ИЛИ, выходы устройства, группу элементов И, прямые и инверсные входы устройства. Недостаток - низкое быстродействие.

Наиболее близким к заявляемому является изобретение (пат. 2338241 C1, Российская Федерация, МПК G06F 7/523, G06F 7/72 (2006.01), заявл. 22.03.2007; опубл. 10.11.2008), содержащее генератор гармонического сигнала, управляемые фазовращатели, измеритель фазы гармонического сигнала, группу фазовращателей на фиксированное значение фазы, шифраторы, входы устройства первого сомножителя, дешифраторы, элементы ИЛИ, блоки умножения на константу по модулю, элементы И, входы устройства разрядов второго сомножителя, сумматор по модулю два, преобразователь кода числа x в p-x, выход устройства.

Недостаток - низкое быстродействие, обусловленное применением цифровых управляемых фазовращателей на основе линий задержки, коммутируемых в электрическую цепь посредством ключей.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в повышении быстродействия.

Технический результат выражается в реализации последовательного умножения дискретных фаз гармоник на два с применением электрических ключей только для формирования константы.

Технический результат достигается тем, что в устройство для умножения числа по модулю на константу, содержащее вход устройства первого сомножителя, k входов устройства разрядов второго сомножителя, выход устройства, введены синхронизирующий вход устройства, k переключателей, k-1 блоков умножения фазы на два в степени, k-1 блоков сложения фаз, при этом синхронизирующий вход устройства объединен с первым входом переключателей, блоков умножения фазы на два в степени и блоков сложения фаз, при этом вход устройства первого сомножителя объединен с вторым входом переключателей, j-й  вход устройства разрядов второго сомножителя объединен с третьим входом соответствующего переключателя, выход первого переключателя соединен с третьим входом первого блока сложения фаз, выход (i+1)-го переключателя

вход устройства разрядов второго сомножителя объединен с третьим входом соответствующего переключателя, выход первого переключателя соединен с третьим входом первого блока сложения фаз, выход (i+1)-го переключателя  соединен с вторым входом i-го блока умножения фазы на два в степени, выход которого соединен с вторым входом соответствующего блока сложения фаз, при этом выход s-го блока сложения фаз

соединен с вторым входом i-го блока умножения фазы на два в степени, выход которого соединен с вторым входом соответствующего блока сложения фаз, при этом выход s-го блока сложения фаз  соединен с третьим входом (s+1)-го блока сложения фаз, выход (k-1)-го блока сложения фаз объединен с выходом устройства.

соединен с третьим входом (s+1)-го блока сложения фаз, выход (k-1)-го блока сложения фаз объединен с выходом устройства.

На фиг. 1 представлена структурная схема устройства для умножения числа по модулю на константу.

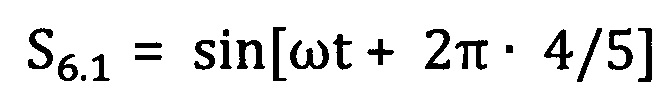

На фиг. 2 приведена схема блока умножения фазы на два в степени.

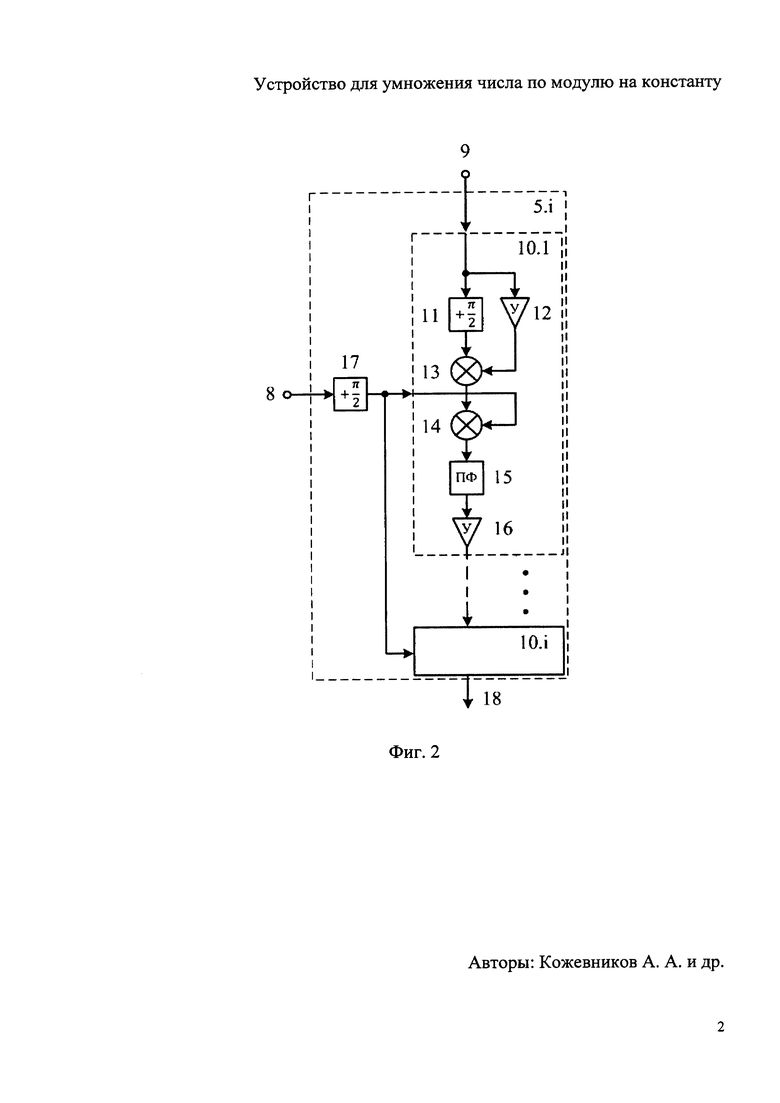

На фиг. 3 приведена схема блока сложения фаз.

Сущность изобретения заключается в осуществлении искомой операции над дискретно-фазированными гармониками СВЧ диапазона в соответствии с известными тригонометрическими выражениями, а не за счет набега фазы сигнала на некоторое дискретное значение, как в прототипе. Рассмотрим операцию умножения двух чисел Г=А×В, где В представлено в виде полинома:  . Здесь k - максимальное количество двоичных разрядов, применяемое для реализации константы В, a

. Здесь k - максимальное количество двоичных разрядов, применяемое для реализации константы В, a  - значения двоичных разрядов,

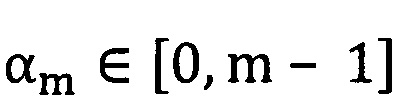

- значения двоичных разрядов,  . Если целый остаток числа А по модулю m есть αm, а результат по модулю m - это γm, то

. Если целый остаток числа А по модулю m есть αm, а результат по модулю m - это γm, то

.

.

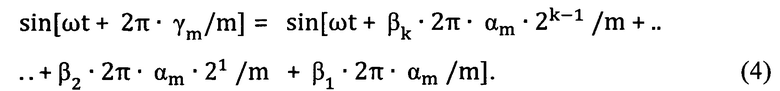

Для реализации алгоритма вычислений на дискретных блоках, полученное выражение примет следующий вид:

Основной причиной, снижающей быстродействие прототипа по сравнению с реализуемым устройством, является переход от вычисления одного произведения к другому, поскольку влечет за собой процесс изменения дискретных величин фазовращения посредством перекоммутации линий задержек. Даже самые быстродействующие полупроводниковые ключи, работающие с сигналами в СВЧ диапазоне, осуществляют данную операцию в течение единиц наносекунд (стр. 12, Щаврук Н.В. Проектирование и изготовление микроэлектромеханических переключателей на подложках GaAs для СВЧ диапазона: дис. … канд. техн. наук: 05.27.01 / Москва. 2015. 130 с.). Таким образом, применение свойств гармонических сигналов с дискретно-фазированным представлением чисел, при условии использования переключателей только для формирования константы, в реализуемом устройстве на рабочей частоте, например, 100 ГГц дает ускорение вычислений на два порядка.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1 и 2 должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Дополнительным эффектом является повышение точности вычислений за счет постоянства импеданса реализуемого устройства, в отличие от прототипа, где при переходе от вычисления одного произведения к другому производится изменение задержек сигнала. Также дополнительным эффектом является расширение функциональных возможностей через выполнение на одном и том же устройстве искомой операции по любому модулю m, в отличие от прототипа, где значения задержек фазы фиксированы. Поскольку константа определяется любым двоичным числом, значение которого может быть много больше основания применяемой СОК, то реализуемое устройство можно использовать для преобразования позиционного цифрового представления в код остатка по модулю в дискретно-фазированной форме, что дает дополнительное расширение функций по сравнению с прототипом.

Показанное на фиг. 1 устройство для умножения числа по модулю на константу содержит синхронизирующий вход устройства 1, вход устройства первого сомножителя 2, входы устройства разрядов второго сомножителя 3.1-3.k, переключатели 4.1-4.k, блоки умножения фазы на два в степени 5.1-5.(k-1), блоки сложения фаз 6.1-6.(k-1), выход устройства 7.

Синхронизирующий вход устройства 1 объединен с первым входом переключателей 4.1-4.k, блоков умножения фазы на два в степени 5.1-5.(k-1) и блоков сложения фаз 6.1-6.(k-1), при этом вход устройства первого сомножителя 2 объединен с вторым входом переключателей 4.1-4.k, при этом вход устройства разрядов второго сомножителя 3.j  объединен с третьим входом переключателя 4.j, при этом выход переключателя 4.1 соединен с третьим входом блока сложения фаз 6.1, при этом выход переключателя 4.(i+1)

объединен с третьим входом переключателя 4.j, при этом выход переключателя 4.1 соединен с третьим входом блока сложения фаз 6.1, при этом выход переключателя 4.(i+1)  соединен с вторым входом блока умножения фазы на два в степени 5.i, выход которого соединен с вторым входом блока сложения фаз 6.i, при этом выход блока сложения фаз 6.s

соединен с вторым входом блока умножения фазы на два в степени 5.i, выход которого соединен с вторым входом блока сложения фаз 6.i, при этом выход блока сложения фаз 6.s  соединен с третьим входом блока сложения фаз 6.(s+1), при этом выход блока сложения фаз 6.(k-1) объединен с выходом устройства 7.

соединен с третьим входом блока сложения фаз 6.(s+1), при этом выход блока сложения фаз 6.(k-1) объединен с выходом устройства 7.

Показанная на фиг. 2 схема блока умножения фазы на два в степени 5.i содержит первый 8 и второй 9 вход, блоки умножения на два 10.1-10.i, фазовращатель на фиксированное значение π/2 17, выход 18.

Первый вход 8 через фазовращатель на фиксированное значение π/2 17 соединен с первым входом блока умножения на два 10.1-10.i, при этом второй вход 9 объединен с вторым входом блока умножения на два 10.1, при этом выход блока умножения на два 10.t  соединен с входом блока умножения на два 10.(t+1), при этом выход блока умножения на два 10.i объединен с выходом 18.

соединен с входом блока умножения на два 10.(t+1), при этом выход блока умножения на два 10.i объединен с выходом 18.

Блоки умножения на два 10.1-10.i содержат фазовращатель на фиксированное значение π/2 11, усилитель 12, смеситель 13, смеситель 14, полосовой фильтр 15, усилитель 16.

Первый вход блока умножения на два объединен с вторым входом смесителя 14, при этом второй вход блока умножения на два объединен с входом фазовращателя на фиксированное значение π/2 11 и усилителя 12, выход которого соединен с вторым входом смесителя 13, при этом выход фазовращателя на фиксированное значение π/2 11 соединен с первым входом смесителя 13, выход которого соединен с первым входом смесителя 14, выход которого соединен с входом полосового фильтра 15, выход которого соединен с входом усилителя 16, выход которого является выходом блока умножения на два.

Показанная на фиг. 3 схема блока сложения фаз содержит первый 19, второй 20 и третий 21 входы, смеситель 22, аттенюатор 23, полосовой фильтр 24, смеситель 25, полосовой фильтр 26, усилитель 27 и выход 28.

Второй вход 20 объединен с первым входом смесителя 22, при этом третий вход 21 объединен с вторым входом смесителя 22, выход которого соединен с входом полосового фильтра 24, выход которого соединен с вторым входом смесителя 25, при этом первый вход 19 объединен с входом аттенюатора 23, выход которого соединен с первым входом смесителя 25, выход которого соединен с входом полосового фильтра 26, выход которого соединен с входом усилителя 27, выход которого объединен с выходом 28.

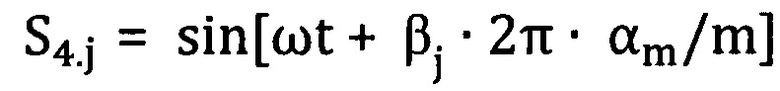

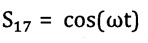

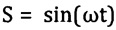

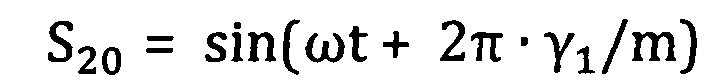

Работа устройства осуществляется следующим образом. На синхронизирующий вход 1 поступает гармонический сигнал  . На информационный вход первого сомножителя 2 поступает дискретно-фазированная гармоника

. На информационный вход первого сомножителя 2 поступает дискретно-фазированная гармоника  , где

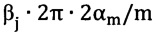

, где  , a m - модуль применяемой системы остаточных классов. На входы 3.1-3.k поступает двоичное слово, устанавливающее переключатели 4.1-4.k в соответствии с значениями разрядов

, a m - модуль применяемой системы остаточных классов. На входы 3.1-3.k поступает двоичное слово, устанавливающее переключатели 4.1-4.k в соответствии с значениями разрядов  ,

,  , k - максимальное количество двоичных разрядов константы. В зависимости от позиции переключателя далее проходит гармоника

, k - максимальное количество двоичных разрядов константы. В зависимости от позиции переключателя далее проходит гармоника

,

,

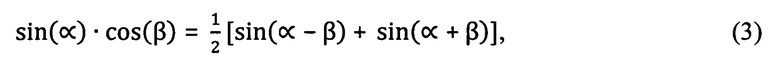

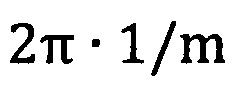

где i - степень двойки, при этом i=j-1 для j>2. На блоках 5.i происходит последовательное умножение фазы на два i раз следующим образом. Попадая в блок умножения на два 10.1 (фиг. 2), фазированная гармоника увеличивает фазу на π/2 в блоке 11, а в параллельной линии - амплитуду в два раза на усилителе 12, после чего оба сигнала поступают на входы смесителя 13, где реализуется известное тригонометрическое выражение:

Полученная промежуточная гармоника удвоенной частоты

перемножается на смесителе 14 с синхронизирующей гармоникой, фаза которой увеличена на π/2 блоком 17 (т.е.  ). При этом согласно тригонометрическому выражению

). При этом согласно тригонометрическому выражению

после полосовой фильтрации более низкочастотной составляющей на блоке 15 и усиления в блоке 16 получается результат в виде гармоники с единичной амплитудой и фазой, смещенной относительно синхронизирующего сигнала на  :

:

.

.

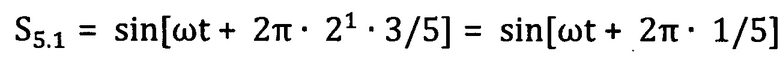

В результате последовательной работы блоков умножения на два 10.1-10.i на выходе блока 5.i (i=j-1 для j>2) формируется сигнал:

.

.

После этого происходит последовательное сложение фаз гармоник всех блоков умножения фазы на два в степени посредством элементов 6.1-6.(k-1) и реализуется выражение (1) в следующем виде:

Процесс сложения фаз осуществляется попарно на соответствующих блоках (фиг. 3). На вход 19 поступает синхронизирующий гармонический сигнал  . На входы 20 и 21 поступают дискретно-фазированные гармоники:

. На входы 20 и 21 поступают дискретно-фазированные гармоники:

и

и

.

.

На смесителе 22 производится перемножение сигналов. Из известного тригонометрического выражения

следует, что после полосовой фильтрации высокочастотной составляющей на блоке 24 формируется промежуточный результат:

.

.

Гармонический сигнал с входа 19, уменьшенный аттенюатором 23 в два раза  , перемножается смесителем 25 с промежуточной гармоникой. Реализация тригонометрического выражения (3) после полосовой фильтрации более низкочастотной составляющей на блоке 26 и усиления в блоке 27 дает результат в виде гармоники с единичной амплитудой и фазой, смещенной относительно синхронизирующего сигнала на

, перемножается смесителем 25 с промежуточной гармоникой. Реализация тригонометрического выражения (3) после полосовой фильтрации более низкочастотной составляющей на блоке 26 и усиления в блоке 27 дает результат в виде гармоники с единичной амплитудой и фазой, смещенной относительно синхронизирующего сигнала на

.

.

Таким образом, на выходе устройства 7 последовательно формируется результат, описанный выражением (4), который можно использовать для дальнейших вычислений в дискретно-фазированной форме.

Реализация дополнительной функции по преобразованию позиционного цифрового представления в код остатка по модулю в дискретно-фазированной форме возможна, если на вход 2 устройства подать гармонику со смещенной на  фазой. Тогда умножение этой фазы на любое число по входам 3.1-3.k после операции деления по модулю, автоматически осуществляемой в силу периодичности гармонического сигнала, даст результат искомой дополнительной функции.

фазой. Тогда умножение этой фазы на любое число по входам 3.1-3.k после операции деления по модулю, автоматически осуществляемой в силу периодичности гармонического сигнала, даст результат искомой дополнительной функции.

Пример

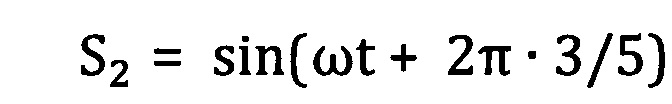

Пусть константа имеет длину в шесть бит (k=6). Тогда реализуемое устройство содержит входы устройства разрядов второго сомножителя 3.1-3.6, переключатели 4.1-4.6, блоки умножения фазы на два в степени 5.1-5.5, блоки сложения фаз 6.1-6.5. Рассмотрим умножения числа по модулю m=5. Пусть А=3, следовательно гармоника на входе 2 имеет значение

.

.

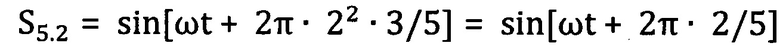

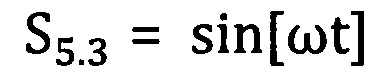

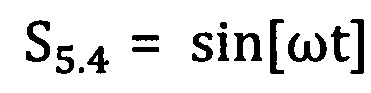

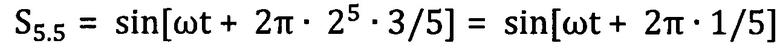

В качестве значения константы, возьмем число 39, тогда полиномиальное ее представление есть B=25+22+21+1, т.е. β1=1, β2=1, β3=1, β4=0, β5==0, β6=1. После перемножения на два в степени на выходах блоков 5.1-5.5 формируются сигналы:

,

,

,

,

,

,

,

,

.

.

Последовательно сложив фазы гармоник с выхода переключателя 4.1 и блоков 5.1-5.5, получим сигналы на выходах 6.1-6.5:

,

,

,

,

,

,

,

,

.

.

Таким образом, результат умножения числа по модулю на константу есть γ5=2. Проверим полученный результат. Г=А×В=3×39=117. Деление по модулю 5 даст целый остаток, равный 2.

Полученное устройство отражает принципы построения арифметических устройств на основе системы остаточных классов, работающих с дискретно-фазированной формой представления чисел. С точки зрения практического применения устройство реализует возможность построения аналоговых вычислителей СВЧ диапазона, превосходящих по быстродействию современный уровень ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗИРОВАННЫЙ КЛЮЧ ПО МОДУЛЮ m | 2017 |

|

RU2659866C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| НЕЛИНЕЙНЫЙ РАДАР ДЛЯ ДИСТАНЦИОННОГО МОНИТОРИНГА ПРОДУКТОПРОВОДОВ | 2007 |

|

RU2343499C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2006 |

|

RU2313124C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| Многоканальное устройство для измерения амплитудно-фазового распределения поля фазированной антенной решетки | 1986 |

|

SU1474563A1 |

Изобретение относится к области автоматики и вычислительной техники. Технический результат заключается в повышении быстродействия устройства. Технический результат достигается за счет устройства для умножения числа по модулю на константу, которое содержит вход устройства первого сомножителя, k входов устройства разрядов второго сомножителя, выход устройства, синхронизирующий вход устройства, k переключателей, k-1 блоков умножения фазы на два в степени, k-1 блоков сложения фаз. 3 ил.

Устройство для умножения числа по модулю на константу, содержащее вход устройства первого сомножителя, k входов устройства разрядов второго сомножителя, выход устройства, отличающееся тем, что введены синхронизирующий вход устройства, k переключателей, k-1 блоков умножения фазы на два в степени, k-1 блоков сложения фаз, при этом синхронизирующий вход устройства объединен с первым входом переключателей, блоков умножения фазы на два в степени и блоков сложения фаз, при этом вход устройства первого сомножителя объединен с вторым входом переключателей, j-й  вход устройства разрядов второго сомножителя объединен с третьим входом соответствующего переключателя, выход первого переключателя соединен с третьим входом первого блока сложения фаз, выход (i+1)-го переключателя

вход устройства разрядов второго сомножителя объединен с третьим входом соответствующего переключателя, выход первого переключателя соединен с третьим входом первого блока сложения фаз, выход (i+1)-го переключателя  соединен с вторым входом i-го блока умножения фазы на два в степени, выход которого соединен с вторым входом соответствующего блока сложения фаз, при этом выход s-го блока сложения фаз

соединен с вторым входом i-го блока умножения фазы на два в степени, выход которого соединен с вторым входом соответствующего блока сложения фаз, при этом выход s-го блока сложения фаз  соединен с третьим входом (s+1)-го блока сложения фаз, выход (k-1)-го блока сложения фаз объединен с выходом устройства.

соединен с третьим входом (s+1)-го блока сложения фаз, выход (k-1)-го блока сложения фаз объединен с выходом устройства.

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ УМНОЖЕНИЯ-СЛОЖЕНИЯ С УПАКОВАННЫМИ ДАННЫМИ | 1996 |

|

RU2139564C1 |

| SU 1485884 A1, 27.02.1996 | |||

| EP 1984810 B1, 22.03.2017. | |||

Авторы

Даты

2018-05-07—Публикация

2017-05-24—Подача