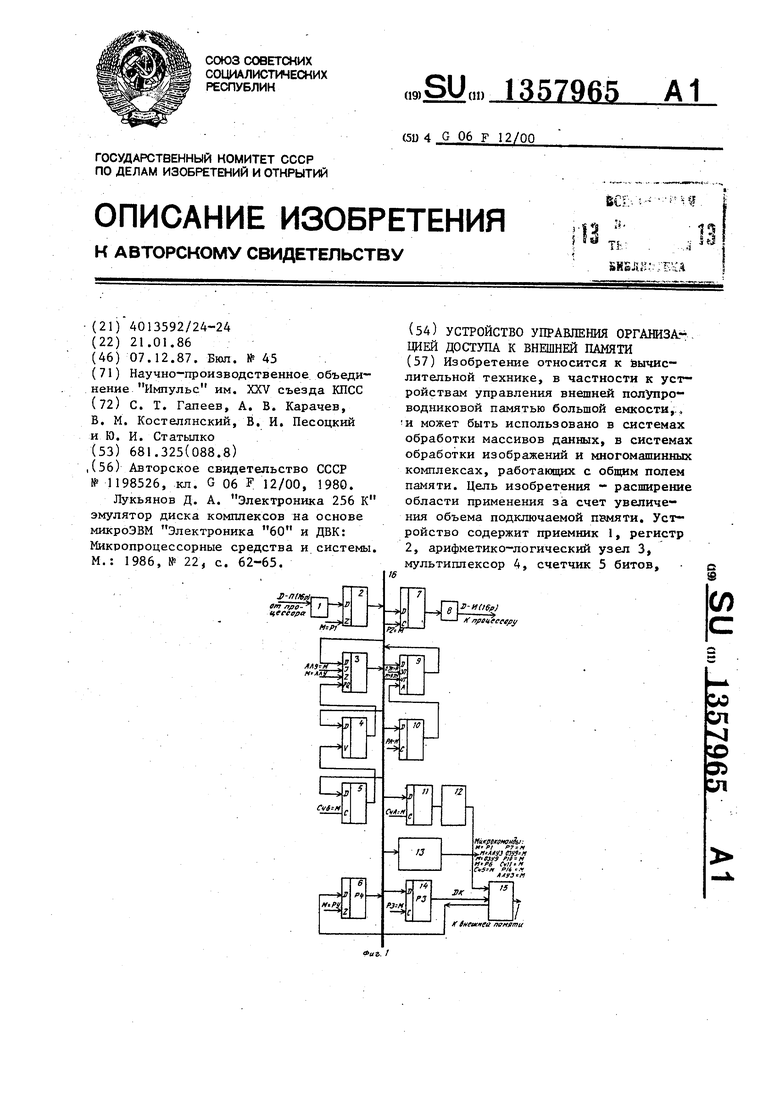

регистр 6, регистр 7, передатчик 8, блок 9 памяти, регистр 10, счетчик 11 адреса, формирователь 12 адреса внешней памяти, блок 13 микропрограммного управления, регистр 14, маги страль 16. Устройство используется для организации доступа к внешней полупроводниковой памяти большой ем

1

Изобретение относится к вычисли-. тельной технике, в частности к устройствам управления внешней полупроводниковой памятью большой емкости, и может быть использовано в системах обработки массивов данных, в системах обработки изображений и многомашинных комплексах, работающих с :обшлм полем памяти.

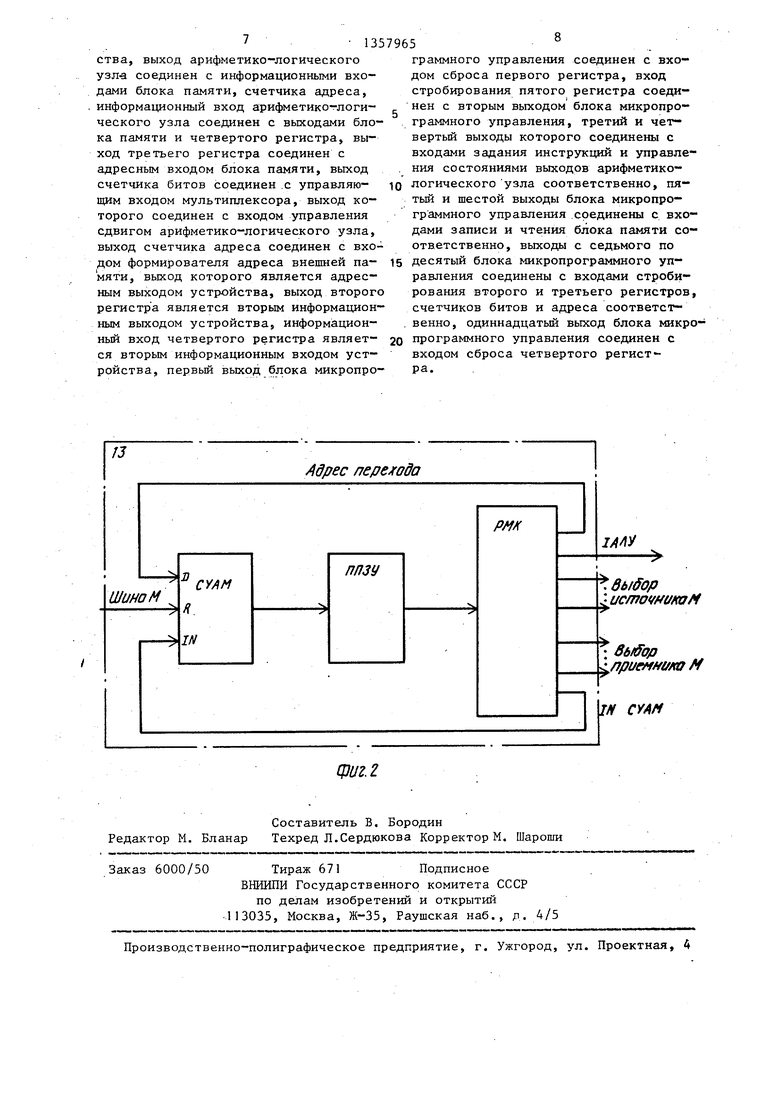

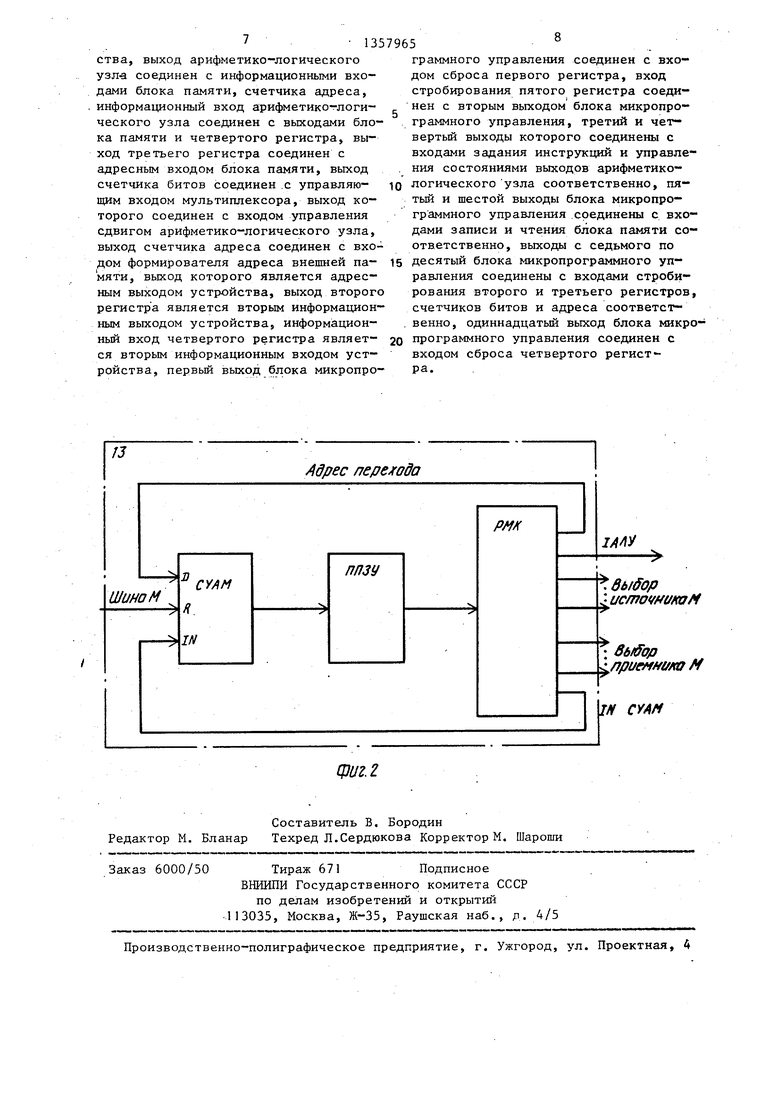

Цель изобретения - расширение области применения за счет увеличения обьема подключаемой памяти. , На фиг. 1 представлена структурная схема устройства; на фиг, 2 - структурная схема блока микропрограммного управления.

Устройство содержит приемник 1, регистр 2, арифметико-логический узел 3, мультиплексор 4, счетчик 5 битов, регистр 6, регистр 7, передатчик 8, блок 9 памяти, регистр 10, счетчик 11 адреса, формирователь 12 адреса внешней памяти, блок 13 микропрограммного управления, регистр 14, блок 15 управления внешней памятью, магистраль 16.

Устройство обеспечивает cлeдylo цIie методы доступа к массивам данных внешней памяти:

квантование данных; при использовании этого метода центральным процессором задаются следующие, парамет А - адрес начальный массива данных, 1 - общая длина массива, А„ - величина пропусков между квантами массива; операции для этого метода доступа выполняются в следующем порядке: начиная с Л, производится чтение или запись части массива величиной Ац, затем адрес увеличивается на величину А и продолжается чтением или записью следующей части массива величиной Apjj вся операция завершакости. Управление устройством осу- ш;ествляется блоком 13 микропрограммного управления в зависимости от кода операции, формируемой процессором. Устройство обеспечивает несколько методов доступа к массивам данных, находящихся во внешней памяти, 2 ил.

ется по исчерпанию общей длины массива;

транспозиция данных; при использовании этого метода центральным процессором задаются следующие параметры: АН, A.fj, Af,. Операции для зтого метода вьшолняются в следуклцем порядке: начиная с А, производится чтение -или запись первого слова (байта),

затем адрес увеличивается на величи- - ну Afi и читается или записывается второе слово (байт), затем адрес вновь увеличивается на величину и читается или записывается третье слово, число таких шагов равно А„; , после исчерпания Ад осуществляется возврат к адресу А +1 и цикл повторяется с возвратом к адресу , операция заканчивается после чтения или

записи массива длиной (А,-А,)+1;

метод доступа с заданной последовательностью адресов; для этого метода необходимо за,цавать Ац и шаблон ад13, шаблон -представляет собой массив 128 слов (2048 бит), который записывается в блок 9 кд кдому адресу (начиная с А), став.ится в соответствие значения соответствующего бита массива шаблона : единичное значение определяет необходимость выполнения операции над ячейкой с , данным адресом, нулевое - переход к следующему адресу без выполнения операции, вся операция завершается

5 по исчерпанию длины шаблона;

метод доступа с заданной последовательностью данных; для этого метода необходимо задавать А и шаблон данных ; шаблон представляет собой

массив 128 слов (2048 бит) и записывается в блок 9 по единичному значению бита шаблона, осуществляется запись в очередную ячейку, по нулево-

bfy - данные игнорируются, текущий адрес формируется прибавлением единицы к предыдущему адресу после очередной записи; вся операция завершается по исчерпанию длины шаблона ;

чтение под маской, предварительно в устройство управления загружается два слова маски (маска нулей и маска единиц) ; на каждое прочитанное слово (байт) накладывается поочередно маска нулей и маска единиц, в разрядах, определенных единицами слов маски, записываются, соответственно.

нули и единицы, остальные разряды не изменяются; этот метод может использоваться совместно с методом квантования данных;

чтение с инверсией; этот метод может использоваться совместно дом квантования данных;

чтение ортогональное; при зтом методе из каждого считанного слова (байта) выделяется один указанньй разряд, из выделенных битов формируется слово (байт) и выдается в центральный процессор; адреса для этого метода формируются прибавлением единицы к текущему адресу или методу квантования данных;

чтение с коньюкцией или дизъюнкцией двух массивов, оба массива находятся в внещней памяти; формирование адреса аналогично предыдущему методу;

поиск по контексту по ключу с битовой или байтовой маской; предварительно в блок 9 необходимо записать |КОнтекст или ключи с масками.

Взаимодействие всех элементов устройства осуществляется посредством магистрали 16. Приемники 1, передат- 1чик 8, регистр 2 и регистр 7 обеспечивают выход на внешний радиальный параллельный (16 разрядов) интерфейс:

регистры которого записываются принимаемые от центрального процессора параметры операции: Ац, А, А,, I, маски, ключи. С помощью счетчика 5 битов обеспечивается выполнение операций ортогональных чтения.

Общее управление элементами схемы осуществляется блоком 13 микропро- 10 граммного управления.

Арифметико-логический узел 3. может быть реализован на микросхеме, содержащей 16 регистров, в которые записываются параметры операций, со- 15 держащиеся в командах процессора. Команда процессора содержит до 15 слов,

Используют следукщие регистры: R1 - адрес текущий первого массива; R2 - длина массива; R3 - величина с мето- 20 приращения адреса первого массива

(АДД); R4 - величина пропуска адресов первого массива (А,,); R5 -маска еди- .ниц; R6 - маска нулей; Н7 - адрес текущий второго массива; R8 - вели- 25 чина приращения адреса второго массива (AJ); R9 - величина пропуска адреса второго массива (А„ ); R10 - Ад, текущее первого массива; R11 А текущее второго массива; R12 - код ко- 30 манды; R13 - константа 2; R14 - рабочий регистр; R15 - длина статистики; R16 - адрес статистики.

Например, чтобы вьшолнить операцию квантования данных, от процессора поступает пятисловная команда, содержащая код операции, .на 1альный адрес массива данных, длину массива А., АП,

В арифметико-логическом узле 3 осуществляется хранение и обработка 40 параметров, заданных в команде процессора.

Например, наращивание текущего адреса (+1, +А или +АП), изменение длины массива и сравнение ее с. за35

данные приемника (В-П), данные источ- 45 данной длиной, осуществляется после

ника (D-И). С помощью счетчика 11 адреса и формирователя 12 адресная последовательность передается в блок 15 управления внешней памятью. Обмен данными с блоком 15 осуществляется с помощью регистров 6 и 14. Блок памяти емкостью 2К байт используется для хранения заданных последовательностей адресов, последовательностей данных, контекстов. Регистр 10 служит для хранения адреса блока 9. Формирование, адресов в соответствии с заданным методом доступа производится с помощью арифметико-логического узла 3, в

каждого обращения к внешней памяти в операциях связанных с записью и чтением данных.

50 Включением общего питания устройства в регистр адреса микрокоманд блока 13 заносится нулевой адрес мик ропрограммы функционирования устройства управления. Первой включается

55 микропрограмма начальной установки и перехода в исходное состояние, В исходном состоянии блок управления находится в режиме ожидания команд про цессора.

35

45 данной длиной, осуществляется после

каждого обращения к внешней памяти в операциях связанных с записью и чтением данных.

50 Включением общего питания устройства в регистр адреса микрокоманд блока 13 заносится нулевой адрес микропрограммы функционирования устройства управления. Первой включается

55 микропрограмма начальной установки и перехода в исходное состояние, В исходном состоянии блок управления находится в режиме ожидания команд процессора.

блок 13 для ана- команде, лриня

операции: лц, ки, шаблоны ном кодом операции. Параметры Л„,

Устройство функционирует следую щим образом.

На вход регистра 2 устройства поступают команды процессора через при емник I , При микрокоманде М Р1 (магистрали и присвоить значение регистра 1), поступающей из блока 13 по радиальным связям, принятая команда процессора устанавливается на магист- раль 16. По микрокоманде АУ-М команда процессора по информационному входу с магистрали 16 заносится в par бочие регистры арифметико-логического узла 3, Одновременно команда по ма- гистрали поступает в лиза кода операции в той от процессора.

Вслед за командой через приемник 1 от процессора поступают параметры AU, AJ,, Ар, I, ключи, мас- в сочетании, определен-

А

А, I, ючи и маски записываются в узел 3 по тому же пути, что и коман- ды. Шаблоны записываются в блок 9 в следующем порядке. Через приемники 1 данные шаблона поступают в регистр 2. Текущий адрес внешней памяти, сформированньш в узел 3 по микро- команде блока 13 М-АЛУЗ магистрали 16 присвоить содержимое узла 3, ус™ танавливается на магистраль 16„ По микрокоманде 10 текущий адрес блока 9 с магистрали 16, заносится в регистр 10.,.Затем до микрокоманде М-Р1 данные шаблона из рег истра 2 устанавливаются на магистраль 16 и.по микрокоманде ОЗУ9-М записываются в блок 9.

Данные в операциях записи во внешг нюю память с входа D-П через приемник 1, входной регистр 2 поступают на вход регистра 14 и по микрокоманде 14-М заносятся в регистр 14.

С выхода регистра 14 данные поступают через блок 15 для записи во внешнюю память. Текущий адрес внешней памяти формируется в узле 3 и поступает на вход счетчика I1 адреса и по микрокоманде Сч11-М заносится в счетчик 11 адреса. С выхода последнего адрес через формирователь 12 поступает в блок 15.

Данные в операциях чтения из внешней памяти через блок 15 поступают в регистр 6 и по микрокоманде М-Рб выдаются на магистраль 16. С последней данные поступают на вход регистра 7,

по микрокоманде Р7-М записываются в него и через передатчики 8 вьщаются в процессор.

Для операций ортогонального чтения считанные внешней памяти данные через регистр 6 поступают на вход мультиплексора 4, в счетчик 5 битов

предварительно записывается номер бита, подлежащего вьщелению, скомму-

тированный бит с выхода мультиплексора 4 поступает на вход сдвиговых регистров арифметико-логического узла 3 и сдвигается.

Операция повторяется до получения 16-разрядного слова, которое с выхода узла 3 ч.ерез регистр 7 и передатчик 8 вьщается в процессор.

Для операций поиска чтения под маской, чтения инверсного, чтения с дизъюнкцией чтения с конъюнкцией все данные из внешней памяти через.регистр 6 поступают в узел 3 по информационному входу. После соответствующих операций в арифметико-логическом узле 3 по микрокоманде АЛУЗ-М данные с выхода узла 3 поступают на магистраль 16 и через регистр 2 и передатчик 8 выдаются в процессор.

Формула изобретения

Устройство управления организацией доступа к внешней памяти, содержащее счетчик адреса, первый регистр, приемник, передатчик, выход приемника соединен с информационным входом первого регистра, выход приемника является первым информационным входом устройства, отличающееся тем, что, с целью расширения области применения за .счет увеличения объема подключаемой памяти, в негр введены четыре регистра, арифметико-логичес- кий узел, блок памяти, мультиплексор, счетчик битов, формирователь ад. реса внешней памяти , блок микропрограммного управления, причем выход первого регистра соединен с информационными входами арифметико-логического узла, второго и третьего регистров, счетчика битов, входом занесения команды блока микропрограммного управления, выход четвертого регистра соединен с информационными входами пятого регистра, мультиплексора, выход пятого регистра соединен с входом передатчика, выход которого является . первым информационным выходом устрой-

ства, выход арифметико-логического узл-а соединен с информационными входами блока памяти, счетчика адреса, информационный вход арифметикотлоги- ческого узла соединен с выходами блока памяти и четвертого регистра, выход третьего регистра соединен с адресным входом блока памяти, выход счетчика битов соединен .с управляющим входом мультиплексора, выход которого соединен с входом управления сдвигом арифметико-логического узла, выход счетчика адреса соединен с входом формирователя адреса внепшей памяти, выход которого является адресным выходом устройства, выход второго регистра является вторым информационным выходом устройства, информацион- ньй вход четвертого регистра является вторым информационным входом устройства, первый выход блока микропрофиг. 2

Составитель В. Бородин Редактор М. Бланар Техред Л.Сердюкова Корректор М. Щароши

6000/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

граммного управления соединен с входом сброса первого регистра, вход стробирования пятого регистра соединен с вторым выходом блока микропрограммного управления, третий и чет- вертьй выходы которого соединены с входами задания инструкций и управле- ния состояниями выходов арифметико-

логического узла соответственно, пятый и шестой выходы блока микропрограммного управления .соединены с входами записи и чтения блока памяти соответственно, вькоды с седьмого по

десятый блока микропрограммного управления соединены с входами строби- ровання второго и третьего регистров, счетчиков битов и адреса соответст- венно, одиннадцатый выход блока микропрограммного управления соединен с входом сброса четвертого регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней полупроводниковой памятью большой емкости,.., тл. может быть использовано в системах обработки массивов данных, в системах обработки изображений и многомашинных комплексах, работающих с общим полем памяти. Цель изобретения - расширение области применения за счет увеличения объема подключаемой памяти. Устройство содержит приемник 1, регистр 2, арифметико-логический узел 3, мультиплексор 4, счетчик 5 битов.

Авторы

Даты

1987-12-07—Публикация

1986-01-21—Подача