Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления дифференциальных сигналов при наличии синфазной составляющей, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных интегральных и решающих усилителях, компараторах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) на основе каскодных токовых зеркал [1-5]. ДУ с такой архитектурой стали основой построения многих современных аналоговых микросхем [1-22], в т.ч. ДУ с опцией rail-to-rail, имеющих максимальную амплитуду выходного напряжения, близкую к напряжениям питания.

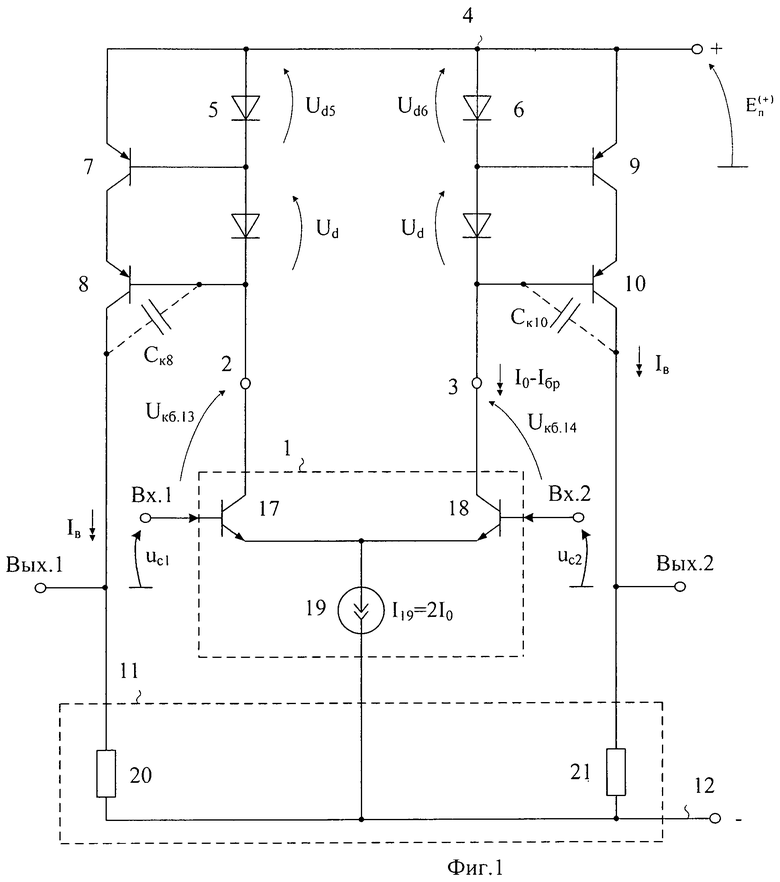

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте US №4241315, fig.4. Его существенная особенность - применение каскодных токовых зеркал, обладающих предельно высоким выходным сопротивлением (влияющим на коэффициент усиления ДУ по напряжению), а также характеризующихся повышенным диапазоном рабочих частот в сравнении с другими вариантами токовых зеркал. Архитектура ДУ-прототипа также используется во многих патентах ведущих микроэлектронных фирм [5-22].

ДУ-прототип фиг.1 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, причем первый 2 токовый выход связан с первой 4 шиной источника питания через первый 5 прямосмещенный p-n переход, а второй 3 токовый выход связан с первой 4 шиной источника питания через второй 6 прямосмещенный p-n переход, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана с первым 5 прямосмещенным p-n переходом, а коллектор соединен с эмиттером второго 8 выходного транзистора, третий 9 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана со вторым 6 прямосмещенным p-n переходом, а коллектор соединен с эмиттером четвертого 10 выходного транзистора, цепь нагрузки 11, согласованную со второй 12 шиной источника питания и связанную с выходами устройства и коллекторами второго 8 и четвертого 10 выходных транзисторов.

Существенный недостаток известного ДУ фиг.1 состоит в том, что при малых напряжениях питания (Еп) он имеет не достаточно широкий относительный (приведенный к Еп) диапазон изменения синфазной составляющей входных напряжений uc≈0,5(uc1+uc2), где uc1, uc2 - напряжения на входах ДУ.

Основная задача предлагаемого изобретения состоит в расширении допустимого диапазона изменения входных синфазных сигналов на 0,7÷0,8 В. При малых напряжениях питания (Еп≤±2 В) - это существенное улучшение одного из важных качественных показателей ДУ.

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, причем первый 2 токовый выход связан с первой 4 шиной источника питания через первый 5 прямосмещенный p-n переход, а второй 3 токовый выход связан с первой 4 шиной источника питания через второй 6 прямосмещенный p-n переход, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана с первым 5 прямосмещенным p-n переходом, а коллектор соединен с эмиттером второго 8 выходного транзистора, третий 9 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана со вторым 6 прямосмещенным p-n переходом, а коллектор соединен с эмиттером четвертого 10 выходного транзистора, цепь нагрузки 11, согласованную со второй 12 шиной источника питания и связанную с выходами устройства и коллекторами второго 8 и четвертого 10 выходных транзисторов, предусмотрены новые элементы и связи - базы второго 8 и четвертого 10 выходных транзисторов соединены с эмиттером дополнительного транзистора 13, эмиттер которого связан с дополнительным источником опорного тока 14, а коллектор подключен к первой 4 шине источника питания, причем в схему введены первый 15 и второй 16 последовательно соединенные дополнительные резисторы, которые включены между базами первого 7 и третьего 9 выходных транзисторов, а общий узел первого 15 и второго 16 дополнительных резисторов связан с базой дополнительного транзистора 13.

Схема дифференциального усилителя-прототипа представлена на фиг.1.

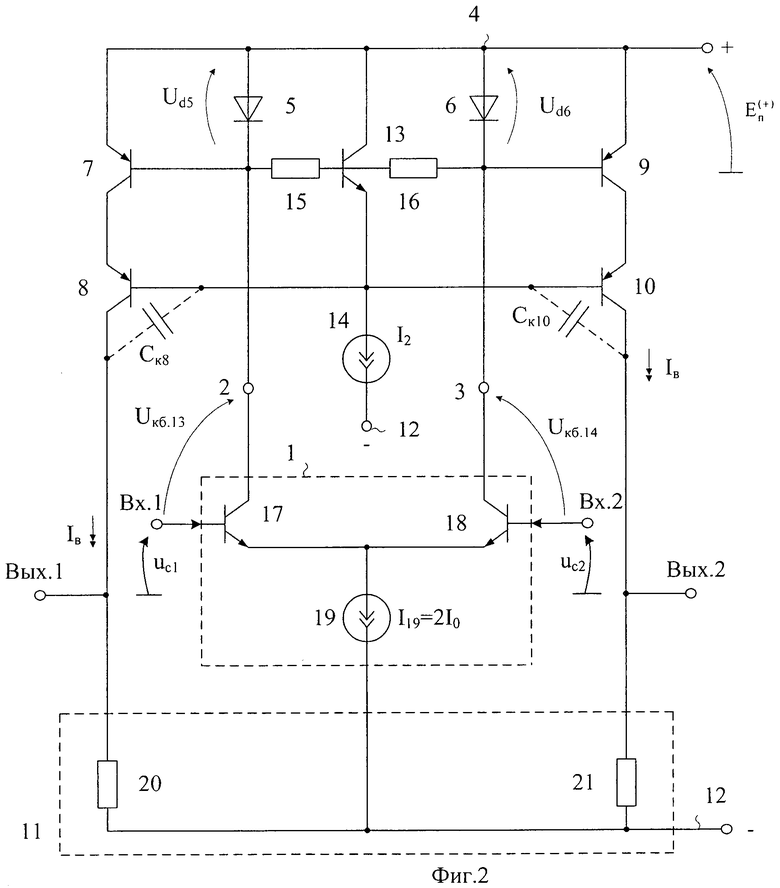

На фиг.2 показана схема заявляемого ДУ в соответствии с формулой изобретения.

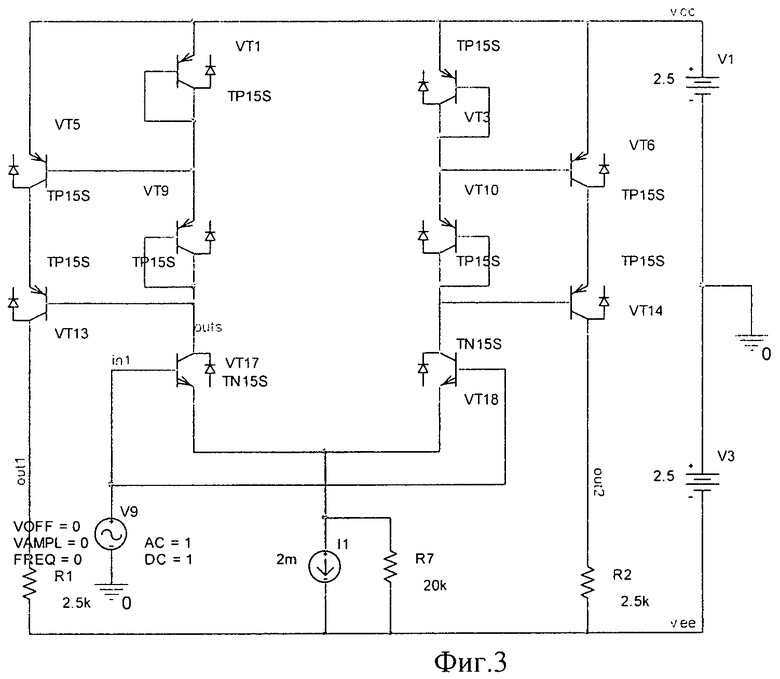

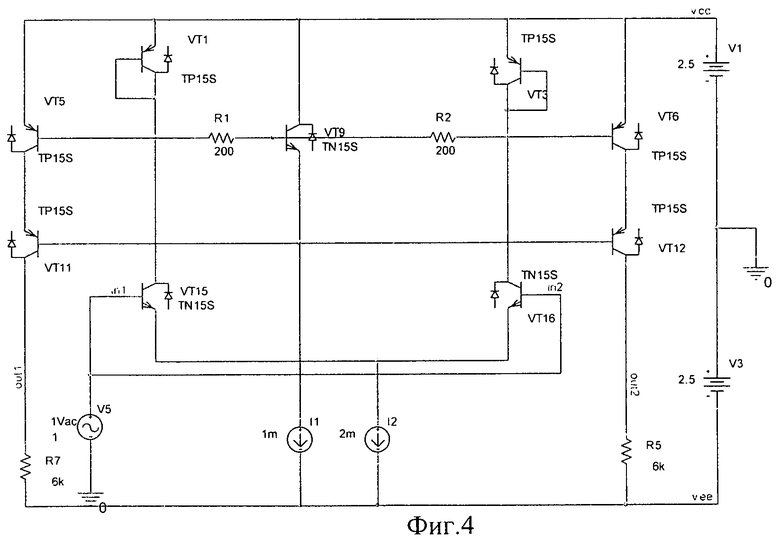

На фиг.3 и фиг.4 показаны схемы усилителя-прототипа (фиг.3) и заявляемого ДУ (фиг.4) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов АВМК_1_3 (НПО «Интеграл», г.Минск).

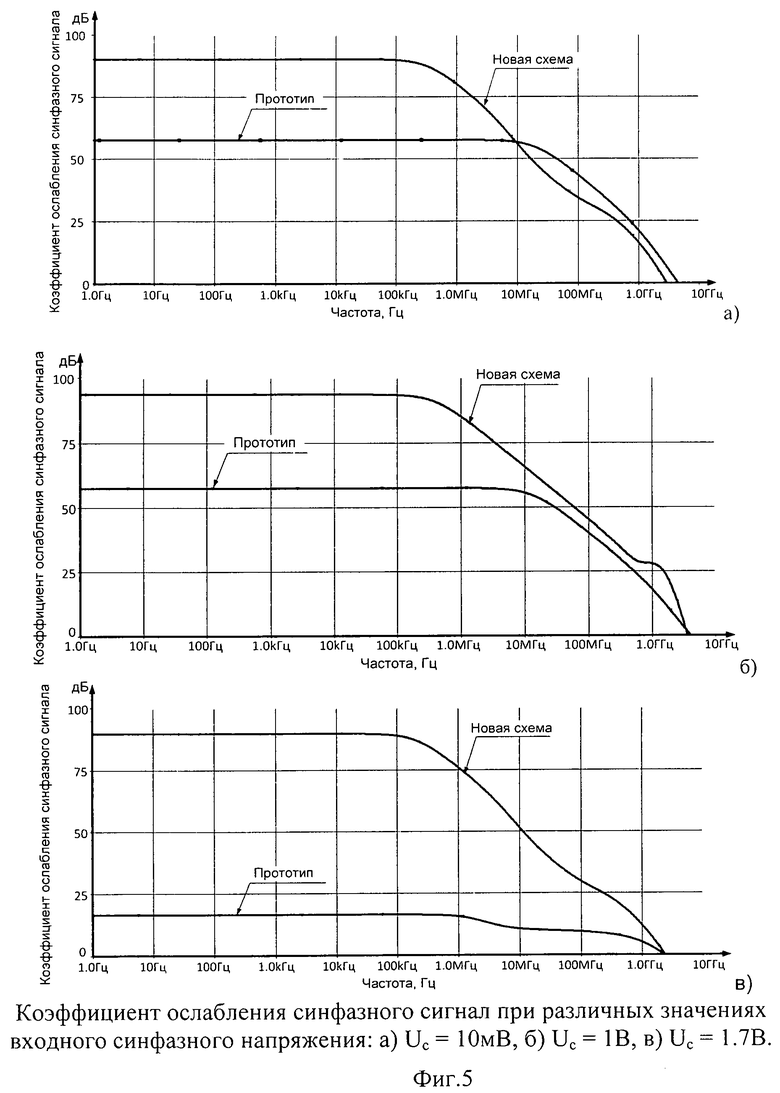

На фиг.5 приведены амплитудно-частотные характеристики коэффициента ослабления входного синфазного сигнала при разных уровнях входного синфазного напряжения: Uc=10 мВ (a), Uc=1 В (б), Uc=1,7 В (в).

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, причем первый 2 токовый выход связан с первой 4 шиной источника питания через первый 5 прямосмещенный p-n переход, а второй 3 токовый выход связан с первой 4 шиной источника питания через второй 6 прямосмещенный p-n переход, первый 7 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана с первым 5 прямосмещенным p-n переходом, а коллектор соединен с эмиттером второго 8 выходного транзистора, третий 9 выходной транзистор, эмиттер которого связан с первой 4 шиной источника питания, база связана со вторым 6 прямосмещенным p-n переходом, а коллектор соединен с эмиттером четвертого 10 выходного транзистора, цепь нагрузки 11, согласованную со второй 12 шиной источника питания и связанную с выходами устройства и коллекторами второго 8 и четвертого 10 выходных транзисторов. Базы второго 8 и четвертого 10 выходных транзисторов соединены с эмиттером дополнительного транзистора 13, эмиттер которого связан с дополнительным источником опорного тока 14, а коллектор подключен к первой 4 шине источника питания, причем в схему введены первый 15 и второй 16 последовательно соединенные дополнительные резисторы, которые включены между базами первого 7 и третьего 9 выходных транзисторов, а общий узел первого 15 и второго 16 дополнительных резисторов связан с базой дополнительного транзистора 13.

В схеме фиг.2 входной каскад 1 реализован на транзисторах 17 и 18 и источнике тока 19, а цепь нагрузки 11 содержит резисторы 20 и 21.

Рассмотрим факторы, определяющие допустимый диапазон Uc.max изменения входных синфазных сигналов ДУ фиг.1 и ДУ фиг.2.

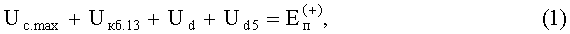

Максимально возможное входное синфазное напряжение ДУ фиг.1 (Uc.max) определяется из уравнения для данной схемы по второму закону Кирхгофа:

где Uc.max=Uc1=Uc2=Uc,

Uкб.13≥0 - напряжение коллектор-база транзистора 13 входного каскада 1, при котором этот транзистор работает в активном режиме;

Ud=Ud5=Ud6≈0,8 В - напряжения на p-n переходах в коллекторной цепи транзисторов 13, 14 входного каскада.

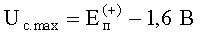

Из уравнения (1) можно найти, что максимально возможное положительное приращение входного синфазного напряжения в ДУ-прототипе Uc.max, при котором не деградирует коэффициент ослабления входных синфазных сигналов (Кос.сф) и другие динамические параметры, не лучше чем

.

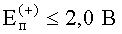

.

При  и SiGe интегральных транзисторах Uc.max≤0,4 В.

и SiGe интегральных транзисторах Uc.max≤0,4 В.

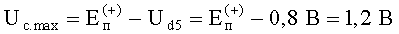

В заявляемой схеме ДУ фиг.2

,

,

т.е. ДУ фиг.2 имеет на 0,8 В более высокое значение Uc.max. При низковольтном питании - это весьма существенное преимущество.

Результаты компьютерного моделирования известной (фиг.3) и предлагаемой (фиг.4) схем ДУ, представленные на чертежах фиг.5, показывают, что схема фиг.4 имеет более высокое значение Uc.max, при превышении которого Кос.сф существенно деградирует.

Кроме этого, заявляемый ДУ характеризуется более широким частотным диапазоном из-за отсутствия эффекта умножения емкостей коллектор-база транзисторов 8 и 10, приведенных к выходам Вых.1, Вых.2.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине Uc.max.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Операционные усилители и компараторы: справочник [Текст]. - М.: Издательский дом «Додэка-XXI», 2001., стр.225.

2. Полонников, Д.Е. Операционные усилители: Принципы построения, теория, схемотехника [Текст] / Д.Е.Полонников. - М., 1983., С.203.

3. Операционные усилители и компараторы. - М.: Издательский дом «Додэка-XXI», 2001., стр.106 (ОУ СА3078).

4. Матавкин, В.В. Быстродействующие операционные усилители [Текст] / В.В.Матавкин. - М.: Радио и связь, 1989. - Рис.2.12.

5. Шкритек, П. Справочное руководство по звуковой схемотехнике [Текст]: Пер. с нем. / П.Шкритек - М.: Мир, 1991. - С.96, рис.8.2.1.

6. Патент США №4783602.

7. Патент США №4176323.

8. Патент США №5371476.

9. Патент США RE 30587.

10. Патент США №4241315.

11. Патент США №4267519.

12. Патент США №4361815.

13. Патент США №3439542.

14. Патент США №5880639.

15. А.св. СССР №361605.

16. Патент ФРГ №2551068.

17. Патент ФРГ №2620999.

18. Патент США №5936568.

19. Патент США №5497124.

20. Патент США №3979689.

21. Патент США №5399991.

22. Патент США №4618832.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2283533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

| ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2309528C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421887C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИНАМИЧЕСКИМ ДИАПАЗОНОМ ДЛЯ ДИФФЕРЕНЦИАЛЬНЫХ И СИНФАЗНЫХ СИГНАЛОВ | 2006 |

|

RU2310976C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292632C1 |

Изобретение относится к области радиотехники и связи. Техническим результатом является расширение допустимого диапазона изменения входных синфазных сигналов на 0,7÷0,8, что является существенным улучшением одного из важных качественных показателей ДУ. Дифференциальный усилитель с расширенным диапазоном изменения входного синфазного сигнала содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первую (4) шину источника питания, первый (5) прямосмещенный p-n переход, второй (6) прямосмещенный p-n переход, первый (7) выходной транзистор, второй (8) выходной транзистор, третий (9) выходной транзистор, четвертый (10) выходной транзистор, цепь нагрузки (11), согласованную со второй (12) шиной источника питания, эмиттер дополнительного транзистора (13), эмиттер которого связан с дополнительным источником опорного тока (14), первый (15) и второй (16) последовательно соединенные дополнительные резисторы. 5 ил.

Дифференциальный усилитель с расширенным диапазоном изменения входного синфазного сигнала, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, причем первый (2) токовый выход связан с первой (4) шиной источника питания через первый (5) прямосмещенный p-n переход, а второй (3) токовый выход связан с первой (4) шиной источника питания через второй (6) прямосмещенный p-n переход, первый (7) выходной транзистор, эмиттер которого связан с первой (4) шиной источника питания, база связана с первым (5) прямосмещенным p-n переходом, а коллектор соединен с эмиттером второго (8) выходного транзистора, третий (9) выходной транзистор, эмиттер которого связан с первой (4) шиной источника питания, база связана со вторым (6) прямосмещенным p-n переходом, а коллектор соединен с эмиттером четвертого (10) выходного транзистора, цепь нагрузки (11), согласованную со второй (12) шиной источника питания и связанную с выходами устройства и коллекторами второго (8) и четвертого (10) выходных транзисторов, отличающийся тем, что базы второго (8) и четвертого (10) выходных транзисторов соединены с эмиттером дополнительного транзистора (13), эмиттер которого связан с дополнительным источником опорного тока (14), а коллектор подключен к первой (4) шине источника питания, причем в схему введены первый (15) и второй (16) последовательно соединенные дополнительные резисторы, которые включены между базами первого (7) и третьего (9) выходных транзисторов, а общий узел первого (15) и второго (16) дополнительных резисторов связан с базой дополнительного транзистора (13).

| US 4241315, 23.12.1980 | |||

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421887C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

Авторы

Даты

2013-02-10—Публикация

2012-01-10—Подача