Изобретение относится к автоматизированным системам регулирования с цифровым управлением и может найти применение в системах регулирования частоты вращения двигателей и положения различных механизмов.

Наиболее близким по технической сущности является цифровой пропорционально-интегрально-дифференциальный регулятор (см. а.с. СССР №1649501, опубл. в БИ №18, 1991 г.), содержащий тактовый генератор, блок управления, четыре регистра и три сумматора.

Недостатком наиболее близкого цифрового пропорционально-интегрально-дифференциального регулятора является то, что при формировании интегральной составляющей закона регулирования в замкнутых системах управления может появиться перерегулирование выходной координаты. Последнее обстоятельство определяется как динамическими настройками системы, так и особенностями цифрового интегрального регулятора, связанными с тем, что направление счета изменяется лишь при смене знака рассогласования. Кроме того, в рассматриваемом цифровом пропорционально-интегрально-дифференциальном регуляторе возможно его опрокидывание (переполнение), т.е. смена знака выходного сигнала при длительном действии однополярного рассогласования.

Сущность изобретения заключается в том, что в цифровой интегральный регулятор, содержащий первый, второй и третий сумматоры, первый, второй и третий регистры, генератор прямоугольных импульсов и блок синхронизации, предназначенный для стробирования регистров, блока логики и сбрасывания выходного сигнала блока логики, причем выход первого сумматора соединен с первым входом первого регистра, выход которого соединен с первым входом второго сумматора, выход генератора прямоугольных импульсов соединен с первым входом блока синхронизации, первый и второй выход которого соединены соответственно с вторым входом первого регистра и первым входом второго регистра, выход второго регистра соединен с вторым входом второго сумматора, выход третьего сумматора соединен с первым входом третьего регистра, причем первый и второй входы первого сумматора являются соответственно входами сигналов задания и обратной связи регулятора, а выход второго регистра - выходом регулятора, дополнительно введены четвертый сумматор, мультиплексор, блок логики, определяющий заданное направление изменения регулируемой координаты и момент времени, когда сигнал войдет в допустимую зону отклонений от конечного значения сигнала задания, блок умножения и блок ограничения, причем выход второго сумматора соединен с первым входом мультиплексора, выход которого соединен с вторым входом второго регистра, выход третьего регистра соединен с первыми входами блока логики и блока умножения, выход которого соединен с первым входом четвертого сумматора, первый вход третьего сумматора соединен с вторым входом четвертого сумматора, выход которого соединен с вторым входом мультиплексора, выход блока логики соединен с вторым входом блока умножения и третьим входом мультиплексора, второй вход первого сумматора соединен с вторым входом третьего сумматора, первый выход блока синхронизации соединен с вторым входом третьего регистра, третий и четвертый выход блока синхронизации соединены соответственно с вторым и третьим входами блока логики, выход второго регистра соединен с первым входом блока ограничения, выход которого соединен с вторым входом блока синхронизации, выход первого регистра соединен с вторым входом блока ограничения, причем первый вход третьего сумматора является входом конечного значения сигнала задания, третий, четвертый и пятый входы блока синхронизации - входами стробирования соответственно сигналов задания, обратной связи и конечного значения сигнала задания, четвертый вход блока логики - входом сигнала допустимой зоны, а третий вход блока умножения - входом параметра настройки.

Существенные отличия находят свое выражение в новой совокупности связей между элементами устройства. Указанная совокупность связей позволяет обеспечить в замкнутых системах регулирования односторонний (без перерегулирования) подход к заданной координате и устойчивую работу регулятора без опрокидывания.

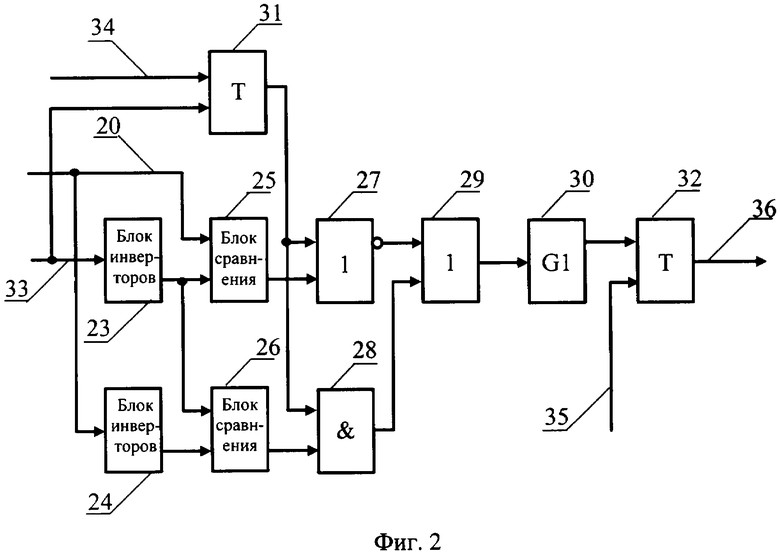

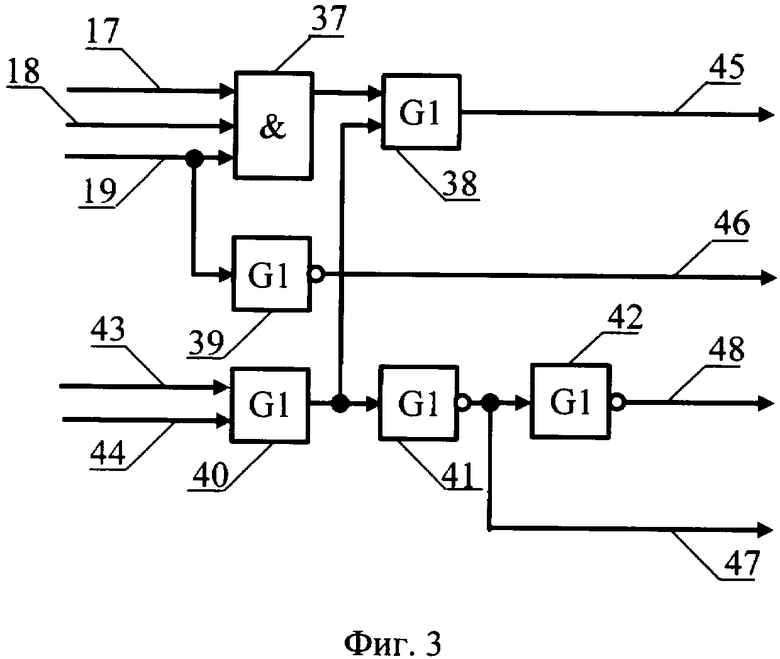

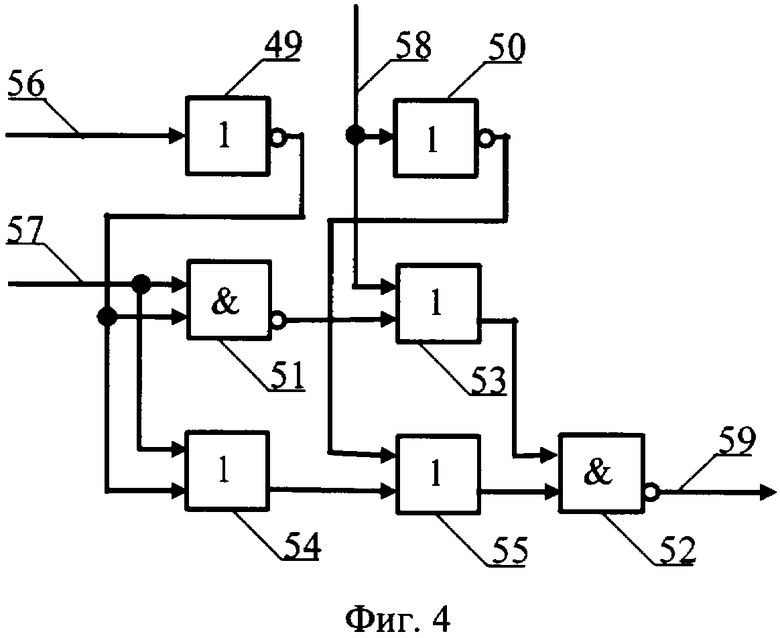

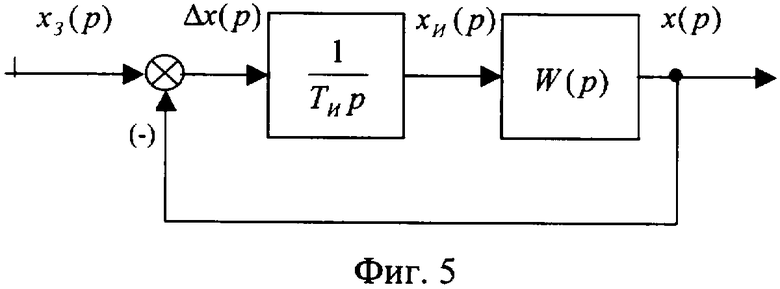

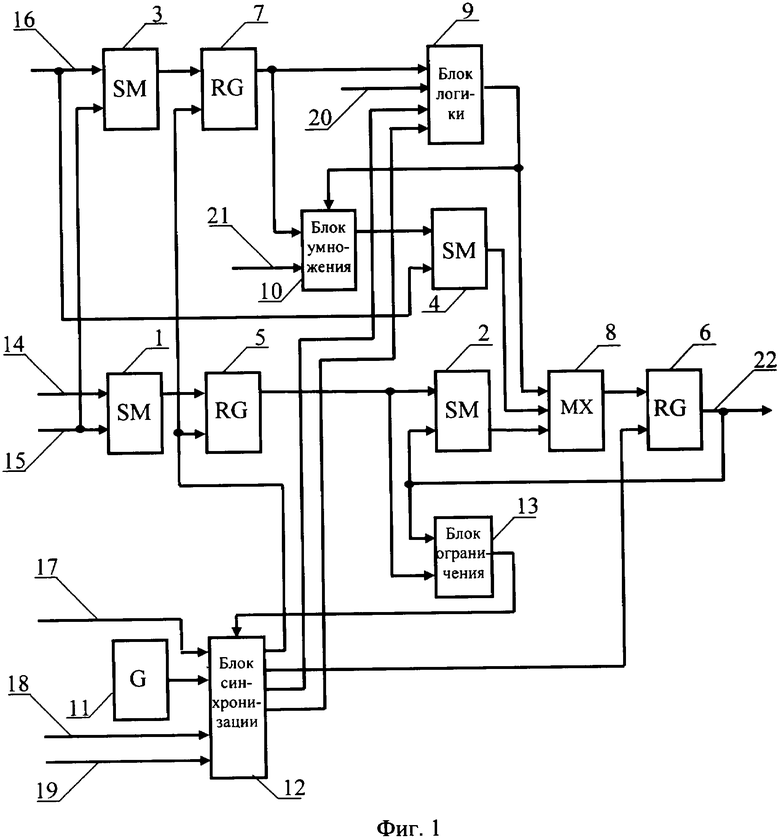

На фиг.1 представлена функциональная схема цифрового интегрального регулятора; на фиг.2 - функциональная схема блока логики, определяющего заданное направление изменения регулируемой координаты и момент времени, когда сигнал войдет в допустимую зону отклонений от конечного значения сигнала задания; на фиг.3 - функциональная схема блока синхронизации, предназначенного для стробирования регистров, блока логики и сбрасывания выходного сигнала блока логики; на фиг.4 - функциональная схема блока ограничения; на фиг.5 - структурная схема возможного включения интегрального регулятора в замкнутой системе автоматического управления.

Цифровой интегральный регулятор (фиг.1) содержит сумматоры 1, 2, 3 и 4, регистры 5, 6 и 7, мультиплексор 8, блок 9 логики, определяющий заданное направление изменения регулируемой координаты и момент времени, когда сигнал войдет в допустимую зону отклонений от конечного значения сигнала задания, блок 10 умножения, генератор 11 прямоугольных импульсов, блок 12 синхронизации, предназначенный для стробирования регистров, блока логики и сбрасывания выходного сигнала блока логики, блок 13 ограничения, вход 14 сигнала задания, вход 15 сигнала обратной связи, вход 16 конечного значения сигнала задания, вход 17 стробирования сигнала задания, вход 18 стробирования сигнала обратной связи, вход 19 стробирования конечного значения сигнала задания, вход 20 сигнала допустимой зоны, вход 21 параметра настройки и выход 22 регулятора. Выход сумматора 1 соединен с первым входом регистра 5, выход которого соединен с первым входом сумматора 2. Выход генератора 11 прямоугольных импульсов соединен с первым входом блока 12 синхронизации, первый и второй выход которого соединены соответственно с вторым входом регистра 5 и первым входом регистра 6. Выход регистра 6 соединен с вторым входом сумматора 2. Выход сумматора 3 соединен с первым входом регистра 7. Первый и второй входы сумматора 1 являются соответственно входами 14 и 15 сигналов задания и обратной связи регулятора, а выход регистра 6 - выходом 22 регулятора. Выход сумматора 2 соединен с первым входом мультиплексора 8, выход которого соединен с вторым входом регистра 6. Выход регистра 7 соединен с первыми входами блока 9 логики и блока 10 умножения, выход которого соединен с первым входом сумматора 4. Первый вход сумматора 3 соединен с вторым входом сумматора 4, выход которого соединен с вторым входом мультиплексора 8. Выход блока 9 логики соединен с вторым входом блока 10 умножения и третьим входом мультиплексора 8. Второй вход сумматора 1 соединен с вторым входом сумматора 3. Первый выход блока 12 синхронизации соединен с вторым входом регистра 7. Третий и четвертый выходы блока 12 синхронизации соединены соответственно с вторым и третьим входами блока 9 логики. Выход регистра 6 соединен с первым входом блока 13 ограничения, выход которого соединен с вторым входом блока 12 синхронизации. Выход регистра 5 соединен с вторым входом блока 13 ограничения. Первый вход сумматора 3 является входом 16 конечного значения сигнала задания, третий, четвертый и пятый входы блока 12 синхронизации - входами 17, 18 и 19 стробирования соответственно сигналов задания, обратной связи и конечного значения сигнала задания, четвертый вход блока 9 логики - входом 20 сигнала допустимой зоны, а третий вход блока 10 умножения - входом 21 параметра настройки.

Основные блоки цифрового регулятора могут быть выполнены, например, на следующих микросхемах: сумматоры 1, 2, 3 и 4 - К555ИМ6; регистры 6, 7, 8, 9 и 10 - К555ТМ8; мультиплексор 8 - К555КП11.

Блок 9 логики (фиг.2), определяющий заданное направление изменения регулируемой координаты и момент времени, когда сигнал войдет в допустимую зону отклонений от конечного значения сигнала задания, например, содержит блоки 23 и 24 инверторов, блоки 25 и 26 сравнения, элемент ИЛИ-НЕ 27, элемент И 28, элемент ИЛИ 29, одновибратор 30, триггеры 31 и 32. Вход блока инверторов 24 и первый вход блока 25 сравнения являются входом 20 сигнала допустимой зоны. Вход 33 блока 23 инверторов является первым входом блока 9 логики. Выход блока 24 инверторов соединен с первым входом блока 26 сравнения, выход которого соединен с первым входом элемента И 28. Выход блока 23 инверторов соединен с вторыми входами блоков 25 и 26 сравнения. Выход блока 25 сравнения соединен с первым входом элемента ИЛИ-НЕ 27. Знаковый разряд входа 33 соединен с первым входом триггера 31, выход которого соединен с вторыми входами элемента ИЛИ-НЕ 27 и элемента И 28. Выход элемента ИЛИ-НЕ 27 соединен с первым входом элемента ИЛИ 29. Выход элемента И 28 соединен с вторым входом элемента ИЛИ 29, выход которого соединен с входом одновибратора 30. Выход одновибратора 30 соединен с первым входом триггера 32, вторые входы триггеров 31 и 32 являются соответственно вторым 34 и третьим 35 входами блока 9 логики. Выход триггера 32 является выходом 36 блока 9 логики.

Блок 10 умножения, например, реализован на микропроцессоре К1801ВМ2, имеющем встроенную функцию умножения.

Генератор 11 прямоугольных импульсов, например, представляет собой автогенератор, выполненный на микросхеме К555ЛА3 с кварцевой стабилизацией, причем выход автогенератора подключен к входу делителя частоты, реализованного на двоичных счетчиках, например К555ИЕ7.

Блок 12 синхронизации (фиг.3), предназначенный для стробирования регистров, блока логики и сбрасывания выходного сигнала блока логики, например, содержит элемент И 37 и одновибраторы 38, 39, 40, 41 и 42. Первый, второй и третий входы элемента И 37 являются входами 17, 18 и 19 стробирования соответственно сигналов задания, обратной связи и конечного значения сигнала задания. Выход элемента И 37 соединен с первым входом одновибратора 38. Третий вход элемента И 37 соединен с входом одновибратрра 39. Первый и второй входы одновибратора 40 являются соответственно первым 43 и вторым 44 входами блока 12 синхронизации. Прямой выход одновибратора 40 соединен с вторым входом одновибратора 38 и входом одновибратора 41, инверсный выход которого соединен с входом одновибратора 42. Прямой выход одновибратора 38 является первым выходом блока 12 синхронизации, а инверсные выходы одновибраторов 39, 41 и 42 - третьим 46, вторым 47 и четвертым 48 выходами блока 12 синхронизации.

Блок 13 ограничения (фиг.4), например, содержит инверторы 49 и 50, элементы И-НЕ 51 и 52, элементы ИЛИ 53, 54 и 55. На вход 56 инвертора 49 подается сигнал со старшего (знакового) разряда выхода регистра 6. Выход инвертора 49 соединен с первыми входами элементов И-НЕ 51 и ИЛИ 54. На вторые входы 57 элементов И-НЕ 51 и ИЛИ 54 подается сигнал с регистра 6 с разряда, определяющего уровень ограничения сигнала на выходе этого регистра. Выход элемента И-НЕ 51 соединен с первым входом элемента ИЛИ 53, выход которого соединен с первым входом элемента И-НЕ 52. На вход 58 инвертора 50 и второй вход элемента ИЛИ 53 подается сигнал со старшего (знакового) разряда выхода регистра 5. Выход элемента ИЛИ 54 соединен с первым входом элемента ИЛИ 55, выход которого соединен с вторым входом элемента И-НЕ 52. Выход инвертора 50 соединен с вторым входом элемента ИЛИ 55. Входы 56 и 57 являются первым входом первого блока 13 ограничения, вход 58 - вторым входом этого блока. Выход 59 элемента И-НЕ 52 является выходом блока 13 ограничения.

Следует также отметить, что основные блоки цифрового интегрального регулятора могут быть также выполнены программно на микропроцессорном контроллере.

Цифровой интегральный регулятор работает следующим образом.

Цифровые коды, соответствующие сигналу задания и обратной связи, подаются соответственно на входы 14 и 15 цифрового интегрального регулятора. Сумматор 1 находит разность сигнала задания и обратной связи. Величина разности записывается в регистр 5 по приходу импульса с первого выхода блока 12 синхронизации и подается на вход сумматора 2. В сумматоре 2 происходит сложение разности сигналов задания и обратной связи с выходным сигналом регистра 6, т.е. с выходным сигналом регулятора. Величина суммы с выхода сумматора 2 через мультиплексор 8 подается на вход регистра 6 и записывается в него по приходу импульса со второго выхода блока 12 синхронизации. Таким образом, с помощью сумматора 2 и регистра 6 происходит интегрирование разности сигналов задания и обратной связи, причем постоянная времени интегрирования определяется величиной тактового интервала генератора 11 прямоугольных импульсов. Нарастание выходного сигнала цифрового интегрального регулятора происходит до тех пор, пока не станет равной нулю величина разности сигналов задания и обратной связи или не сработает блок 13 ограничения, который блокирует подачу импульсов с блока 12 синхронизации на регистр 6. Если сработал блок 13 ограничения, то изменение выходного сигнала регулятора может произойти при смене знака сигнала на выходе регистра 5. Одновременно с работой описанных выше блоков на вход 16 сумматора 3 подается сигнал конечного значения сигнала задания. Сумматор 3 находит разность конечного значения сигнала задания и сигнала обратной связи, которая записывается в регистр 7 по приходу импульса с первого выхода блока 12 синхронизации. Частота импульсов на первом выходе блока 12 синхронизации определяется приходом внешних импульсов на входы 17, 18 и 19 стробирования сигналов задания, обратной связи и конечного значения сигнала задания. Выходной сигнал регистра 7 подается на входы блока 9 логики и блока 10 умножения. Блок 9 логики совместно с сумматором 3 и регистром 7 определяет момент времени, когда сигнал обратной связи войдет в допустимую зону (определяемую величиной сигнала на входе 20) отклонений от конечного значения сигнала задания. Если сигнал вошел в допустимую зону, то на выходе блока 9 логики формируется сигнал, по которому запускается блок 10 умножения и производится переключение мультиплексора 8. Блок 10 умножения вычисляет произведение выходного сигнала регистра 7 и параметра настройки, определяемого сигналом на входе 21. Найденное произведение вычитается в сумматоре 4 из конечного значения сигнала задания. Выходной сигнал сумматора 4 подается через второй вход мультиплексора 8 на вход регистра 6. По приходу очередного импульса со второго выхода блока 12 синхронизации вычисленное сумматором 4 значение записывается в регистр 6, и цифровой интегральный регулятор продолжает работу в обычном режиме, но с откорректированным выходным сигналом. По сигналу с третьего выхода блока 12 синхронизации в блоке логике формируется информация о заданном направлении изменения регулируемой координаты, а сигнал с четвертого выхода блока 12 синхронизации сбрасывает выходной сигнал блока 9 логики. Коррекция выходного сигнала цифрового интегрального регулятора позволяет избежать перерегулирования выходной координаты замкнутой системы, в которой регулятор используется, если правильно выбран параметр настройки. Действительно, в самом общем виде структурную схему замкнутой системы автоматического управления с интегральным регулятором можно представить следующим образом (фиг.5). Здесь  - передаточная функция интегрального регулятора; W(p) - передаточная функция остальной части прямой цепи системы автоматического управления (статическое звено); хЗ(р) - изображение сигнала задания; х(р) - изображение выходной координаты; Δх(р) - изображение сигнала рассогласования (разности); хи(р) - изображение выходного сигнала интегрального регулятора. При подходе к конечному заданному значению выходной координаты при ненулевых начальных условиях изображение (Карсона-Хевисайда) выходного сигнала интегрального регулятора

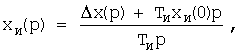

- передаточная функция интегрального регулятора; W(p) - передаточная функция остальной части прямой цепи системы автоматического управления (статическое звено); хЗ(р) - изображение сигнала задания; х(р) - изображение выходной координаты; Δх(р) - изображение сигнала рассогласования (разности); хи(р) - изображение выходного сигнала интегрального регулятора. При подходе к конечному заданному значению выходной координаты при ненулевых начальных условиях изображение (Карсона-Хевисайда) выходного сигнала интегрального регулятора

где хИ (0) - начальное значение выходного сигнала интегрального регулятора.

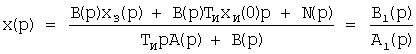

Изображение выходной координаты

где В(р) и А(р) - полиномы числителя и знаменателя передаточной функции W(p). С учетом ненулевых начальных условий выходной координаты замкнутой системы

где N(p) - полином начальных условий.

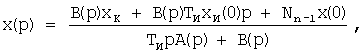

В предположении, что задающий сигнал к моменту коррекции выходного сигнала интегрального регулятора достиг конечного значения хК и производными выходной координаты системы можно пренебречь,

где Nn-1 - коэффициент полинома начальных условий.

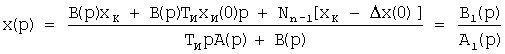

или

Переходя к оригиналу, получим

где pk - корни уравнения А1(p)=0.

Изображение и, следовательно, оригинал являются функциями начальных значений выходного сигнала интегрального регулятора хИ(0), величины рассогласования Δx(0) и динамических свойств системы управления. Присваивая выходному сигналу интегрального регулятора при подходе к заданной координате значение

xИ(0)=xК-Δx(0)kИ,

где kИ - параметр настройки, являющийся функцией динамических свойств замкнутой системы, можно обеспечить односторонний подход к заданной координате.

Таким образом, применение предлагаемого цифрового интегрального регулятора позволяет избежать перерегулирования выходной координаты замкнутой системы, в которой регулятор используется, за счет правильного выбора параметра настройки и коррекции сигнала выходного регистра. Кроме того, в данном цифровом интегральном регуляторе исключается возможность его опрокидывания (переполнения), т.е. смены знака выходного сигнала при длительном действии однополярного рассогласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2000 |

|

RU2181903C2 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2010 |

|

RU2433443C1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2009 |

|

RU2417390C2 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДШИПНИКОМ | 2014 |

|

RU2572386C1 |

| Цифровой интегральный регулятор | 2019 |

|

RU2725410C1 |

| Установка для присоединения проволочных выводов | 1991 |

|

SU1773643A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| Устройство для автоматического управления процессом обессоливания нефти | 1987 |

|

SU1473795A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1553919A1 |

Изобретение относится к автоматизированным системам регулирования с цифровым управлением и может найти применение в системах регулирования частоты вращения двигателей и положения различных механизмов. Технический результат заключается в повышении устойчивости работы регулятора. Он достигается тем, что цифровой интегральный регулятор содержит сумматоры и регистры, мультиплексор, блок логики, блок умножения, генератор прямоугольных импульсов, блок синхронизации, блок ограничения, вход сигнала задания, вход сигнала обратной связи, вход конечного значения сигнала задания, вход стробирования сигнала задания, вход стробирования сигнала обратной связи, вход стробирования конечного значения сигнала задания, вход сигнала допустимой зоны, вход параметра настройки и выход регулятора. 5 ил.

Цифровой интегральный регулятор, содержащий первый, второй и третий сумматоры, первый, второй и третий регистры, генератор прямоугольных импульсов и блок синхронизации, предназначенный для стробирования регистров, блока логики и сбрасывания выходного сигнала блока логики, причем выход первого сумматора соединен с первым входом первого регистра, выход которого соединен с первым входом второго сумматора, выход генератора прямоугольных импульсов соединен с первым входом блока синхронизации, первый и второй выходы которого соединены соответственно с вторым входом первого регистра и первым входом второго регистра, выход второго регистра соединен с вторым входом второго сумматора, выход третьего сумматора соединен с первым входом третьего регистра, причем первый и второй входы первого сумматора являются соответственно входами сигналов задания и обратной связи регулятора, а выход второго регистра - выходом регулятора, отличающийся тем, что в него дополнительно введены четвертый сумматор, мультиплексор, блок логики, определяющий заданное направление изменения регулируемой координаты и момент времени, когда сигнал войдет в допустимую зону отклонений от конечного значения сигнала задания, блок умножения и блок ограничения, причем выход второго сумматора соединен с первым входом мультиплексора, выход которого соединен с вторым входом второго регистра, выход третьего регистра соединен с первыми входами блока логики и блока умножения, выход которого соединен с первым входом четвертого сумматора, первый вход третьего сумматора соединен с вторым входом четвертого сумматора, выход которого соединен с вторым входом мультиплексора, выход блока логики соединен с вторым входом блока умножения и третьим входом мультиплексора, второй вход первого сумматора соединен с вторым входом третьего сумматора, первый выход блока синхронизации соединен с вторым входом третьего регистра, третий и четвертый выходы блока синхронизации соединены соответственно с вторым и третьим входами блока логики, выход второго регистра соединен с первым входом блока ограничения, выход которого соединен с вторым входом блока синхронизации, выход первого регистра соединен с вторым входом блока ограничения, причем первый вход третьего сумматора является входом конечного значения сигнала задания, третий, четвертый и пятый входы блока синхронизации - входами стробирования соответственно сигналов задания, обратной связи и конечного значения сигнала задания, четвертый вход блока логики - входом сигнала допустимой зоны, а третий вход блока умножения - входом параметра настройки.

| RU 2002126986 А, 27.04.2004 | |||

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1988 |

|

SU1649501A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ЦИФРОВОГО ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНОГО РЕГУЛЯТОРА | 1989 |

|

RU2012033C1 |

| US 4679136 A, 07.07.1987 | |||

| Тянущие ролики агрегата непрерывного действия | 1976 |

|

SU606656A1 |

Авторы

Даты

2008-05-27—Публикация

2006-04-17—Подача