Предлагаемое устройство относится к автоматике и может быть использовано для управления объектами с запаздыванием, в частности для регулирования температуры в различных тепловых объектах.

Известно вычислительное устройство цифрового ПИД-регулятора, состоящее из цифрового пропорционального блока, цифрового интегрального блока и блока цифрового дифференцирования (Круг Е. К. , Александри Т. М. , Дилигенский С. Н. Цифровые регуляторы. М. : Энергия, 1966, с. 150, рис. 3-3 а).

Такое вычислительное устройство ПИД-регулятора не устраняет влияние запаздывания объекта управления на устойчивость системы.

Наиболее близким по технической сущности к предлагаемому устройству является вычислительное устройство цифрового ПИД-регулятора (Куо Б. Теория и проектирование цифровых систем управления. М. : Машиностроение, 1986, пер. с анг. , с. 317, рис. 9.48), состоящее из параллельно соединенных цифровых блоков пропорционального преобразования, интегрирования, дифференцирования и цифрового блока суммирования. Входы первых трех параллельно соединенных блоков подключены к аналого-цифровому преобразователю. Выходы этих блоков соединены с входами блока суммирования, выход которого является выходом вычислительного устройства цифрового ПИД-регулятора.

Прототип работает следующим образом. Сигнал ошибки системы X[nT] в цифровой форме поступает в вычислительное устройство, в котором формируется сигнал управления по следующей формуле:

Y[nT] = AoX[nT] - A1X[(n-1)T] + A2X[(n-2)T] + Y[(n-1)T] , (1) где Ао, А1, А2 - параметры настройки ПИД-регулятора;

X[(n-1)T] и X[(n-2)T] - сигналы ошибки системы соответственно в момент времени

t = (n-1)T и t = (n-2)T;

Y[(n-1)T] - сигнал управления в момент времени t = (n-1)T.

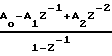

Алгоритм управления (1) получено согласно импульсной передаточной функции

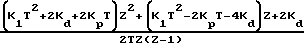

D(Z) =  =

=

=  = (2)

= (2)

=  =

=  .

.

Передаточная функция D(Z) приведена в книге Куо Б. Теория и проектирование цифровых систем управления. М. : Машиностроение, 1986, пер. с англ. , с. 319, формула 9-151.

Данный прототип также не устраняет влияние запаздывания объекта управления на устойчивость системы.

Целью изобретения является расширение области применения за счет устранения влияния запаздывания на устойчивость автоматической системы.

Цель достигается тем, что в вычислительное устройство ПИД-регулятора, содержащее первый цифровой сумматор, к первому, второму и третьему входам которого соответственно через первый блок пропорционального преобразования, блок интегрирования и блок дифференцирования подключен вход вычислительного устройства, введены инвертор, второй цифровой сумматор, четыре блока пропорционального преобразования и элементы задержки, число которых превосходит на два величину отношения времени запаздывания объекта к постоянной времени замкнутой системы, при этом выход первого цифрового сумматора соединен с первым входом второго сумматора непосредственно, а с вторым его входом через последовательно подключенные первый элемент задержки и инвертор, выход первого элемента задержки соединен с третьим входом второго цифрового сумматора через второй блок пропорционального преобразования, с четвертым входом через последовательно подключенные второй элемент задержки и третий блок пропорционального преобразования, выход второго элемента задержки соединен с пятым входом второго цифрового сумматора через последовательно подключенные элементы задержки, начиная с третьего, за исключением последнего, и четвертый блок пропорционального преобразования, выход предпоследнего элемент задержки соединен с шестым входом второго цифрового сумматора через последовательно подключенные последний элемент задержки и пятый блок пропорционального преобразования, выход второго цифрового сумматора является выходом вычислительного устройства цифрового ПИД-регулятора.

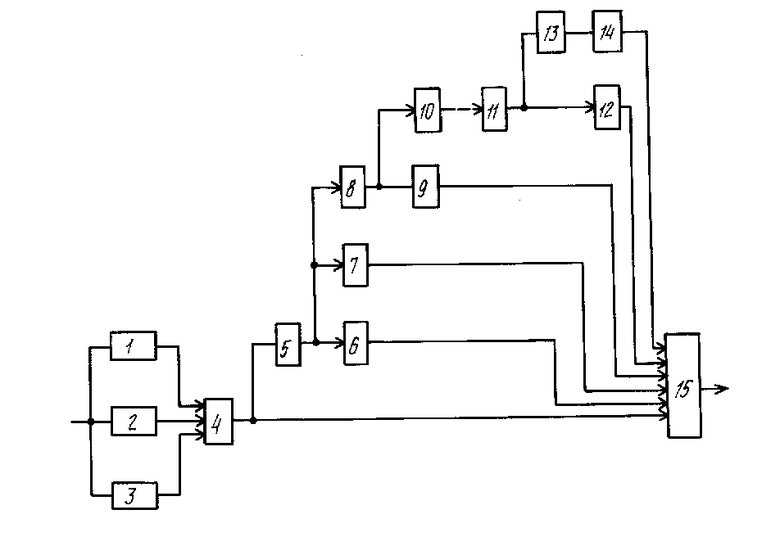

Функциональная схема вычислительного устройства цифрового ПИД-регулятора приведена на чертеже.

Устройство содержит первый цифровой сумматор 4, к первому, второму и третьему входам которого соответственно через первый блок 1 пропорционального преобразования, блок 2 интегрирования и блок 3 дифференцирования подключен вход вычислительного устройств. Выход первого цифрового сумматора 4 соединен с первым входом второго цифрового сумматора 15 непосредственно, а с вторым его входом через последовательно подключенные первый элемент 5 задержки и инвертор 6. Выход первого элемента задержки соединен с третьим входом второго цифрового сумматора 15 через второй блок 7 пропорционального преобразования, с четвертым входом через последовательно подключенные второй элемент 8 задержки и третий блок 9 пропорционального преобразования. Выход второго элемента задержки соединен с пятым входом второго цифрового сумматора через последовательно подключенные элементы 10,11 задержки и четвертый блок 12 пропорционального преобразования. Выход элемента 11 задержки соединен с шестым входом второго цифрового сумматора 15 через элемент 13 задержки и пятый блок 14 пропорционального преобразования. Выход второго цифрового сумматора 15 является выходом вычислительного устройства цифрового ПИД-регулятора.

Входом вычислительного устройства является сигнал ошибки системы, который подается на входы блоков 1,2 и 3. Выход блока 15 является выходом вычислительного устройства, т. е. сигнала управления Y[nT] . Этот сигнал определяется на основе следующего алгоритма:

Y[nT] = AoX[nT] - A1X[(n-1)T] +

+A3X[(n-2)T] + A4Y[(n-1)T] +

+A5Y{ n-(m+1)] T} +

+ A6Y{ [n-(m+ 2)] T} (3)

Сумма коэффициентов при величинах Y равна единице:

А4 + А5 + А6 = 1.

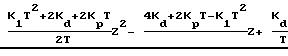

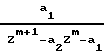

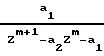

Алгоритм (3) получен из передаточной функции вычислительного устройства цифрового ПИД-регулятора, которая равна

D(Z) =  .

.

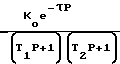

Для обоснования отличительного свойства изобретения берут объект управления второго порядка с запаздыванием, передаточная функция которого равна

Wo(P) =  , где Ко - коэффициент передачи;

, где Ко - коэффициент передачи;

Т1 и Т2 - постоянные времени;

τ - время запаздывания объекта.

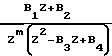

Тогда с учетом экстраполятора нулевого порядка приведенная передаточная функция к непрерывной части системы в форме Z-преобразования имеет вид

Wпр(Z) =  , где В1, В2, В3 и В4 - коэффициенты, значения которых определяются из свойств конкретного объекта управления.

, где В1, В2, В3 и В4 - коэффициенты, значения которых определяются из свойств конкретного объекта управления.

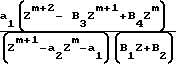

Передаточная функция разомкнутой системы в форме Z-преобразования имеет вид

W(Z) = D(Z)·Wпр(Z) =  .

.

Характеристическое уравнение для замкнутой системы

1 + W (Z) = 0

или 1 +  = 0 и, следовательно Zm+1-a2Zm = 0.

= 0 и, следовательно Zm+1-a2Zm = 0.

Окончательно получают Zm(Z-a2) = 0 или

Из выражения Zm = 0 следует, что запаздывающее звено не влияет на устойчивость системы.

Технико-экономический эффект от предлагаемого устройства заключается в существенном увеличении коэффициента усиления разомкнутой системы, что обеспечивает уменьшение ошибок и высокое быстродействие системы.

Устройство прошло опытно-промышленные испытания. Благодаря высоким статистическим и динамическим свойствам существенно повышаются качественные показатели выпускаемой продукции.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЧЕСКИЙ ЭЛЕКТРИЧЕСКИЙ РЕГУЛЯТОР | 1995 |

|

RU2105339C1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1339494A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА УПРАВЛЕНИЯ | 1992 |

|

RU2068196C1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 2013 |

|

RU2541848C1 |

| ОПТИМАЛЬНЫЙ РЕГУЛЯТОР | 1996 |

|

RU2105341C1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 2007 |

|

RU2368934C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1994 |

|

RU2128358C1 |

| Система регулирования объектов высокого порядка с запаздыванием | 1989 |

|

SU1667002A1 |

| Адаптивная система автоматического управления для нестационарных объектов с запаздыванием | 1986 |

|

SU1451644A1 |

| Способ адаптивного управления плохо формализуемым объектом | 2016 |

|

RU2612084C1 |

Изобретение относится к автоматике и может быть использовано для управления объектами с запаздыванием, в частности для регулирования температуры в различных тепловых объектах. Цель изобретения - расширение области применения за счет устранения влияния запаздывания объекта управления на устойчивость системы. Вычислительное устройство цифрового пропорционально-интегрального регулятора содержит первый блок 1 пропорционального преобразования, блок 2 интегрирования, блок 3 дифференцирования, первый цифровой сумматор 4, первый элемент 5 задержки, инвертор 6, второй блок 7 пропорционального преобразования, второй элемент 8 задержки, третий блок 9 пропорционального преобразования, элемент 10, 11 задержки, четвертый блок 12 пропорционального преобразования, элемент 13 задержки, пятый блок 14 пропорционального преобразования, второй цифровой сумматор 15. Цель изобретения достигается за счет введения элементов 5 - 15. 1 ил.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ЦИФРОВОГО ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНОГО РЕГУЛЯТОРА, содержащее первый цифровой сумматор, к первому, второму, третьему входам которого соответственно через первый блок пропорционального преобразования, блок интегрирования, блок дифференцирования подключен вход вычислительного устройства, отличающееся тем, что, с целью расширения области применения путем обеспечения возможнсти регулирования объектов с запаздыванием, введены инвертор, второй цифровой сумматор, четыре блока пропорционального преобразования и элементы задержки, число которых превосходит на два величину отношения времени запаздывания объекта к постоянной времени замкнутой системы, выход первого цифрового сумматора соединен с первым входом второго цифрового сумматора непосредственно, а с вторым его входом - через последовательно подключенные первые элементы задержки и инвертор, выход первого элемента задержки соединен с третьим входом второго цифрового сумматора через второй блок пропорционального преобразования, с четвертым входом - через последовательно подключенные второй элемент задержки и третий блок пропорционального преобразования, выход второго элемента задержки соединен с пятым входом второго цифрового сумматора через последовательно подключенные элементы задержки, начиная с третьего, за исключением последнего, и четвертый блок пропорционального преобразователя, выход предпоследнего элемента задержки соединен с шестым входом второго цифрового сумматора через последовательно подключенные последний элемент задержки и пятый блок пропорционального преобразования, выход второго цифрового сумматора является выходом вычислительного устройства цифрового пропорционально-интегрально-дифференциального регулятора.

Авторы

Даты

1994-04-30—Публикация

1989-12-14—Подача