Изобретение относится к устройствам для управления сложными объектами, в частности электрофизическими установками, и может быть использовано в системах контроля и управления, в системах синхронизации в качестве формирователя синхронизирующих и управляющих сигналов.

Известен многоканальный программируемый генератор импульсов (а.с. СССР №1348985, МПК4 Н03К 3/64, опубл. 30.10.87. Бюл. №40), содержащий генератор опорной частоты (тактовой частоты), выход которого соединен с тактовым входом формирователя периода, каналы формирования импульса, блок управления, первый и второй счетчики, схему сброса, линию задержки. Причем первая группа выходов блока управления соединена с информационными входами формирователя периода, первый выход которого подключен к счетным входам первого и второго счетчиков, информационные входы которых поразрядно объединены и подключены к второй группе выходов блока управления, третья группа выходов которого подключена соответственно к управляющим входам каналов формирования импульса, первые адресные шины которых поразрядно объединены и соединены с выходами первого счетчика, установочный вход которого подключен к второму выходу формирователя периода и через схему сброса - к установочному входу второго счетчика, выходы которого соединены с разрядными входами схемы сброса и с вторыми поразрядно объединенными адресными шинами каналов формирования импульса, стробирующие входы которых объединены и соединены с выходом линии задержки, вход которой подключен к выходу генератора опорной частоты. Каждый канал формирования импульса содержит первый и второй блоки памяти, первые выходы которых подключены соответственно к первому и второму входам первого коммутатора, выход которого соединен с первым входом триггера, второй вход которого подключен к выходу второго коммутатора, первый и второй входы которого соединены с вторыми выходами соответственно первого и второго блоков памяти, причем объединенные входы управления первого и второго блоков памяти являются управляющим входом канала формирования импульса, адресные входы первого и второго блоков памяти являются соответственно первыми и вторыми адресными шинами канала формирования импульса, объединенные третьи входы первого и второго коммутаторов являются стробирующим входом, а выход триггера - выходом канала формирования импульса.

Такому устройству свойственны следующие недостатки:

- низкий уровень надежности и низкое быстродействие из-за использования преимущественно дискретных электронных компонентов;

- высокое энергопотребление;

- громоздкость;

- низкий уровень помехоустойчивости.

Наиболее близким к предлагаемому генератору является выбранный в качестве прототипа цифровой генератор задержанных импульсов (техническое описание «Model DG535 Digital Delay / Pulse Generator», Stanfbrd Research Systems, Inc, Revision 2.4 (11/97), 1997 г.). Данный генератор задержанных импульсов содержит блок питания, соединенный с блоком управления, включающим панель управления, тактовый генератор, по крайней мере один канал входных импульсов, управляющий микроконтроллер, соединенный двухсторонней связью с панелью управления, многоканальное устройство задержки с заданным количеством каналов выходных импульсов, при этом блок управления соединен с каждой линией задержки по крайней мере одной шиной данных и линиями связи, одни из которых предназначены для передачи сигналов с тактовыми частотами, а другие предназначены для передачи сигналов запуска.

Однако недостаточное количество входных и выходных каналов приводит к увеличению используемой аппаратуры, так как невозможно обеспечить сложный алгоритм работы электрофизической установки. Также при использовании в составе мощных высоковольтных электрофизических установок применение электрических входных и выходных каналов приводит к снижению помехоустойчивости.

Техническая задача: создание генератора задержанных импульсов с высокой степенью надежности, имеющего высокий уровень помехозащищенности при использовании в составе мощных высоковольтных электрофизических установок.

Технический результат: упрощение конструкции, что привело к облегчению сборки и ремонта, упрощение алгоритма работы, повышение помехоустойчивости, в результате обеспечение высокой надежности работы в составе высоковольтных электрофизических установок.

Поставленная задача решается следующим образом. Заявляется генератор задержанных импульсов, содержащий блок питания, соединенный с блоком управления, включающим панель управления, тактовый генератор, по крайней мере один канал входных импульсов, управляющий микроконтроллер, соединенный двухсторонней связью с панелью управления, многоканальное устройство задержки с заданным количеством каналов выходных импульсов. Блок управления соединен с каждой линией задержки по крайней мере одной шиной данных и линиями связи, одни из которых предназначены для передачи сигналов с тактовыми частотами, а другие предназначены для передачи сигналов запуска.

В отличие от прототипа заявляемое устройство выполнено в виде модульной конструкции, включающей модули блока управления, блока питания и модули устройства задержки. Генератор задержанных импульсов содержит несколько каналов входных импульсов. Входные и выходные каналы импульсов выполнены в виде оптических преобразователей сигналов. Блок управления дополнительно содержит программируемую логическую интегральную схему (ПЛИС БУ), предназначенную для буферизации тактового сигнала с начальной тактовой частотой, преобразования тактового сигнала в синхронизирующие импульсы с преобразованной тактовой частотой, мультиплексирования входных сигналов и формирования сигналов запуска на модули устройства задержки, тактовый вход которой соединен с выходом тактового генератора, первая группа выводов ПЛИС БУ соединена с первой группой выводов управляющего микроконтроллера, входные каналы блока управления соединены со второй группой выводов ПЛИС БУ, каждый модуль устройства задержки дополнительно содержит вспомогательный микроконтроллер (МК МЗ), таймер и программируемую логическую интегральную схему модуля задержки (ПЛИС МЗ), предназначенную для формирования заданных интервалов задержки совместно с таймером модуля устройства задержки. Первая группа выводов вспомогательного микроконтроллера каждого модуля задержки соединена посредством первой шины данных со второй группой выводов управляющего микроконтроллера, вторая группа выводов вспомогательного микроконтроллера соединена второй шиной данных с первой группой выводов таймера и первой группой выводов ПЛИС МЗ, вторая группа выводов таймера соединена с четвертой группой выводов ПЛИС МЗ двухсторонней четвертой линией связи, предназначенной для передачи сигналов управления, третья группа выводов ПЛИС БУ соединена первой линией связи, передающей сигналы с начальной тактовой частотой на синхронизирующий вход ПЛИС МЗ каждого модуля задержки, четвертая группа выводов ПЛИС БУ соединена второй линией связи, передающей сигналы с преобразованной тактовой частотой с синхронизирующими входами таймера и вспомогательного микроконтроллера каждого модуля задержки. Пятая группа выводов ПЛИС БУ соединена третьей линией связи, передающей сигналы запуска, со второй группой выводов ПЛИС МЗ каждого модуля задержки. Каждый вывод из третьей группы выводов ПЛИС МЗ через буферный усилитель соединен с соответствующим выходным каналом каждого модуля задержки.

В генераторе задержанных импульсов блок управления может дополнительно содержать интерфейс связи, группа выводов которого с одной стороны соединена с UART-выводами управляющего микроконтроллера, а группа выводов с другой стороны интерфейса выполнена с возможностью соединения с персональным компьютером через СОМ-порт.

Применение современной элементной базы на основе серийных микросхем (СБИС), или иначе ПЛИС (программируемых логических интегральных схем), изготовленных с применением CMOS EEPROM технологии позволяет повысить надежность генератора в составе высоковольтных установок. В результате устройство состоит из относительно малого числа элементов, имеющих высокую надежность. Использование ПЛИС и микроконтроллеров позволяет существенно упростить управление.

Применение оптоволоконного ввода и вывода сигналов позволяет обеспечить помехозащищенность по внешним цепям, защита от помех по цепям питания обеспечивается применением собственного блока питания.

Модульность конструкции позволяет упростить конструкцию, упростить сборку и ремонт генератора.

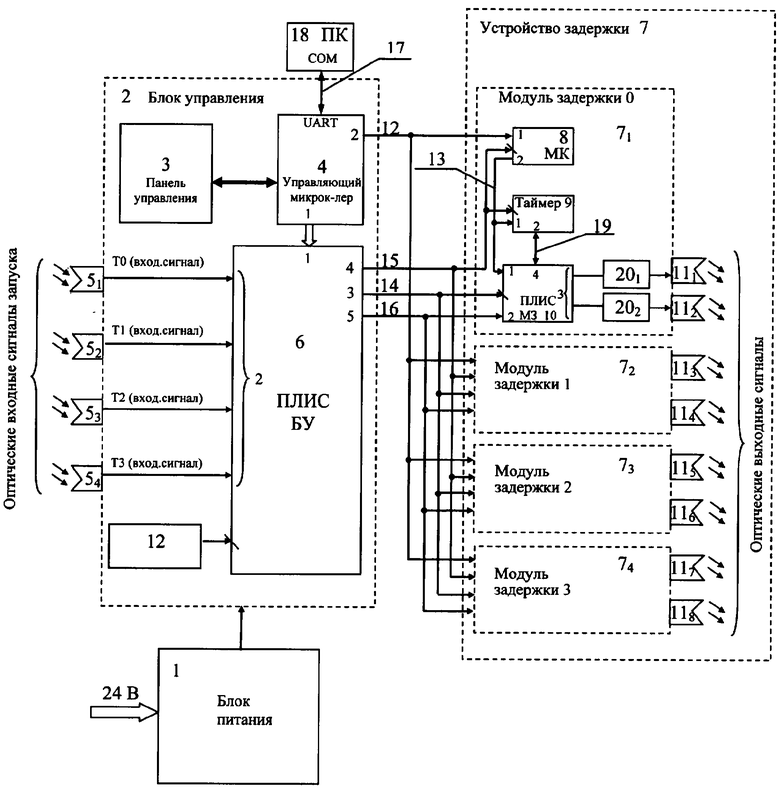

Изобретение поясняется чертежом, на котором представлена блок-схема заявляемого генератора задержанных импульсов.

Генератор задержанных импульсов содержит блок питания 1, соединенный с блоком управления 2, включающим панель управления 3, тактовый генератор 12, каналы входных импульсов 5, управляющий микроконтроллер 4, соединенный двухсторонней связью с панелью управления 3, многоканальное устройство задержки 7 (в данном случае состоящее из четырех модулей-линий задержки) с заданным количеством каналов выходных импульсов 11 (в данном примере восемь каналов).

Блок управления 2 соединен с каждым модулем задержки 7i по крайней мере одной шиной данных 12 и линиями связи, одни из которых предназначены для передачи сигналов с тактовыми частотами 14, 15, а другие - для передачи сигналов запуска 16.

Генератор задержанных импульсов выполнен в виде модульной конструкции: модуля блока управления 2, модулей (линий) задержки 7i, блока питания 1, выполненных на отдельных платах. Модули задержки 7i соединены с блоком управления 2 с помощью разъемных узлов соединения.

Входные 5 и выходные каналы 11 импульсов выполнены в виде оптических преобразователей сигналов (HFBR-2412TC, HFBR-1414TM).

Генератор задержанных импульсов содержит несколько каналов 5 входных импульсов, в данном случае четыре.

Блок управления 2 дополнительно содержит программируемую логическую интегральную схему ПЛИС БУ 6 (ЕРМ 7032AELC44-4), тактовый вход которой соединен с выходом тактового генератора 12 (GTXO-420T/HRN).

Первая группа выводов ПЛИС БУ 6 соединена с первой группой выводов управляющего микроконтроллера 4 (AT90S8535-8PI). Каналы 5 входных импульсов соединены со второй группой выводов ПЛИС БУ 6.

Каждый модуль 7i устройства задержки 7 содержит вспомогательный микроконтроллер МК МЗ 8 (AT90S2313), таймер 9 (D71054C) и программируемую логическую интегральную схему модуля задержки ПЛИС МЗ 10 (ЕРМ 7032AELC44-4).

Первая группа выводов вспомогательного микроконтроллера 8 каждого модуля задержки 7i соединена посредством первой шины данных 12 со второй группой выводов управляющего микроконтроллера 4. Вторая группа выводов вспомогательного микроконтроллера 8 соединена второй шиной данных 13 с первой группой выводов таймера 9 и первой группой выводов ПЛИС МЗ 10. Вторая группа выводов таймера 9 соединена с четвертой группой выводов ПЛИС МЗ 10 двухсторонней четвертой линией 19 связи, предназначенной для передачи сигналов управления. Третья группа выводов ПЛИС БУ 6 соединена первой линией связи 14, передающей сигналы с начальной тактовой частотой, с синхронизирующим входом ПЛИС МЗ 10 каждого модуля задержки 7i. Четвертая группа выводов ПЛИС БУ6 соединена второй линией связи 15, передающей сигналы с преобразованной тактовой частотой, с синхронизирующими входами таймера 9 и вспомогательного микроконтроллера 8 каждого модуля задержки 7i. Пятая группа выводов ПЛИС БУ6 соединена третьей линией связи 16, передающей сигналы запуска, со второй группой выводов ПЛИС МЗ 10 каждого модуля задержки 7i. Каждый вывод из третьей группы выводов ПЛИС МЗ 10 через буферный усилитель 20i соединен с соответствующим выходным каналом 11i каждого модуля задержки 7i.

Блок управления 2 генератора задержанных импульсов может дополнительно содержать интерфейс связи 17, группа выводов которого с одной стороны интерфейса соединена с UART-выводами управляющего микроконтроллера 4, а группа выводов с другой стороны интерфейса выполнена с возможностью соединения с персональным компьютером 18 через СОМ-порт.

Генератор задержанных импульсов работает следующим образом.

При включении напряжения питания происходит инициализация генератора задержанных импульсов.

Входное напряжение 24 В подается на вход блока питания 1. Блок питания 1 формирует два уровня напряжения питания 5 В, 3,3 В. Сформированные напряжения питания поступают на разъем питания (на блок-схеме не показан) блока управления 2 и далее на разъемы питания каждого модуля задержки 7i соответственно.

Синхронизация генератора задержанных импульсов осуществляется с блока управления 2. Тактовый сигнал GCLK (100 МГц) с тактового генератора 12 поступает на тактовый вход ПЛИС БУ 6.

В ПЛИС БУ 6 программно реализованы следующие функции:

- буферизация тактового сигнала GCLK с начальной тактовой частотой 100 МГц, размножение и передача его на модули задержки 7i с третьей группы выводов по первой линии связи 14;

- преобразование тактового сигнала GCLK в синхронизирующие импульсы с частотой 7,142 МГц и передача их на модули задержки 7i с четвертой группы выводов по второй линии связи 15;

- мультиплексирование входных сигналов Т0÷Т3 и передача сигналов запуска на модули задержки 7 с пятой группы выводов по третьей линии связи 16.

Программирование генератора задержанных импульсов (выбор модулей задержки 7i, выбор входного канала, ввод значений временных интервалов) осуществляется по двунаправленной шине с панели управления 3. Введенные значения передаются в управляющий микроконтроллер 4. Значение временного интервала со второй группы выводов управляющего микроконтроллера 4 по первой шине данных 12 согласно протоколу I2С передается на первую группу выводов вспомогательного микроконтроллера 8, который является основным управляющим элементом модуля задержки 7i. Он обеспечивает энергонезависимое хранение введенной задержки; программно преобразует и загружает данные в таймер 9 и в ПЛИС МЗ 10 модуля задержки 7i по второй шине данных 13 в следующем порядке:

- младшие семь разрядов значения задержки передаются в ПЛИС МЗ 10;

- оставшиеся разряды сдвигаются на семь битов вправо и побайтно передаются в таймер 9.

Каждый модуль задержки 7i может запускаться одним из 4 входных сигналов Т0÷Т3, а также программно реализована возможность запуска одновременно нескольких модулей задержки 7i от одного запускающего импульса Ti. Выбор запускающего сигнала и модуля задержки 7i осуществляется ПЛИС БУ 6 в зависимости от запрограммированного введенного значения, которое передается с первой группы выводов управляющего микроконтроллера 4 на первую группу выводов ПЛИС БУ 6.

При инициализации управляющий микроконтроллер 4 последовательно начинает обрабатывать программу, расположенную в его флэш-памяти:

- устанавливаются в начальное состояние все внутренние регистры устройства;

- последнее сохраненное значение задержки из энергонезависимой памяти вспомогательного микроконтроллера 8 загружается в таймер 9 и ПЛИС МЗ 10 каждого модуля задержки 7i по второй шине данных 13;

- программой отслеживаются нажатие кнопки, положение энкодера на панели управления 3 (на чертеже не показаны), состояние генератора задержанных импульсов отображается на жидкокристаллическом индикаторе ЖКИ (на чертеже не показан) на панели управления 3.

После выполнения всех вышеописанных операций генератор задержанных импульсов находится в состоянии ожидания входного импульса.

Входной оптический запускающий сигнал приходит на оптический преобразователь 5i и преобразуется им в электрический сигнал ТТЛ-уровня. Далее входной сигнал Тi поступает на соответствующий вывод второй группы выводов ПЛИС БУ 6, где в зависимости от введенных запрограммированных значений преобразуется (размножается) в запускающие сигналы, которые в свою очередь передаются на соответствующие модули задержки 7i по третьей линии связи 16.

С приходом запускающего импульса по третьей линии связи 16 на ПЛИС МЗ 10 начинают работать внутренние шестиразрядные счетчики, а также согласно внутренней логике ПЛИС МЗ 10 тактовый сигнал GCLK преобразуется в два синхросигнала, которые идут на таймер 9 по двусторонней линии связи 19 и являются тактирующими для внутренних счетчиков таймера 9.

Несмотря на то, что таймер 9 является медленным устройством относительно ПЛИС МЗ 10, проблема скорости обработки задержки решена следующим образом: ПЛИС МЗ 10 отрабатывает задержку ≤ 635 нс (определяется шестиразрядным счетчиком в ПЛИС МЗ, который обрабатывает младшие разряды значения задержки). Регистр констант вмещает максимальное значение, соответствующее 630 нс. Младший бит запоминается во внутренний триггер, который управляет дополнительной задержкой в 5 нс и в зависимости от нулевого или единичного значения бита он либо добавляется к общей задержке, либо нет.

Если запрограммирован временной интервал, превышающий значение 635 нс, то к формированию задержки подключается таймер 9. За один тактовый импульс счетчик таймера вычитает значение, равное 640 нс. Оба эти устройства работают последовательно, т.е. отработанные значения задержки складываются.

Последовательная работа таймера 9 и ПЛИС МЗ 10 организована следующим образом:

- младшие биты значения задержки обрабатывает быстрое устройство ПЛИС МЗ 10 и по завершении счета ждет единичное значение сигнала по четвертой линии связи 19 от таймера 9, отрабатывая в это время пустые циклы;

- первый внутренний счетчик таймера 9 COUNTO по завершении цикла счета выдает «1» на ПЛИС МЗ 10 по четвертой линии связи 19, которая перебрасывает внутренний триггер в ПЛИС МЗ 10 в нулевое состояние; ПЛИС МЗ 10 формирует первый выходной сигнал, который идет на первый буферный усилитель 201 с третьей группы выводов ПЛИС МЗ 10, усиливается до значения 60 мА, необходимого для включения первого оптического H1 излучателя; с первого буферного усилителя сигнал подается на вход первого оптического преобразователя 111;

- второй внутренний счетчик таймера 9 COUNT1, получив информацию от первого внутреннего счетчика COUNTO, что сформирован первый выходной сигнал, запускает на счет значение длительности первого выходного импульса; по завершении цикла счета по четвертой линии связи 19 таймер 9 выдает «1» на внутренний триггер ПЛИС МЗ 10, который перебрасывается в единичное состояние и сформированный выходной импульс прекращается;

- сразу после завершения работы счетчика COUNT0 запускается внутренний счетчик COUNT2 таймера 9, который формирует задержку второго выходного импульса и по завершении счета выдает «1» по четвертой линии связи 19, которая в свою очередь перебрасывает внутренний триггер в ПЛИС МЗ 10 в 0;

- ПЛИС МЗ 10 формирует второй выходной сигнал, который поступает на второй выходной буферный усилитель 202 с третьей группы выводов ПЛИС МЗ 10, усиливается до значения 60 мА, необходимого для включения второго оптического 112 излучателя. Со второго буферного усилителя сигнал подается на вход второго оптического преобразователя 112. Вспомогательный микроконтроллер 8 обрабатывает программное прерывание, формирующее длительность второго выходного импульса.

При использовании генератора задержанных импульсов в составе автоматизированной системы управления программирование установочных значений и осуществление контроля за работой прибора может быть осуществлено с компьютера по интерфейсу 17 (RS232). Введенные установочные значения передаются в управляющий микроконтроллер 4 на UART-выводы по интерфейсу - двунаправленной линии связи 17 через СОМ-порт с персонального компьютера 18. Далее загрузка введенных значений в основные модули генератора осуществляется аналогично, как в случае ручного управления (с панели управления).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ГЕНЕРАТОР ЗАДЕРЖАННЫХ СИГНАЛОВ | 2023 |

|

RU2822509C1 |

| СПОСОБ ПОВЫШЕНИЯ ЭНЕРГЕТИЧЕСКИХ ПОКАЗАТЕЛЕЙ ЭЛЕКТРОВОЗА ПЕРЕМЕННОГО ТОКА И КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ НА ТОКОПРИЕМНИКЕ ПРИ ЕГО РАБОТЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2467892C1 |

| Имитатор пространственного радиолокационного сигнала | 2018 |

|

RU2687071C1 |

| МОДУЛЬ СБОРА ДАННЫХ | 2008 |

|

RU2374683C1 |

| Устройство для исследования оперативной памяти | 1986 |

|

SU1404059A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ УСТАНОВИВШЕГОСЯ ПЕРИОДА ЯДЕРНОГО РЕАКТОРА | 2022 |

|

RU2784409C1 |

| СПОСОБ ГЛУБИННОЙ ГЕОРАДИОЛОКАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2022 |

|

RU2816128C1 |

| ВОЗБУДИТЕЛЬ ДЛЯ РАДИОПЕРЕДАТЧИКОВ | 2016 |

|

RU2625527C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

Использование: в системах контроля и управления в качестве формирователя синхронизирующих и управляющих сигналов. Технический результат заключается в упрощении конструкции и алгоритма работы, повышении помехоустойчивости и надежности работы. Генератор содержит модуль блока питания, модуль блока управления, включающий панель управления, тактовый генератор, управляющий микроконтроллер, модуль многоканального устройства задержки с заданным количеством каналов выходных импульсов. Входные и выходные каналы импульсов выполнены в виде оптических преобразователей сигналов. Блок управления дополнительно содержит программируемую логическую интегральную схему (ПЛИС БУ), каждый модуль устройства задержки дополнительно содержит вспомогательный микроконтроллер (МК МЗ), таймер и программируемую логическую интегральную схему модуля задержки (ПЛИС МЗ). В генераторе задержанных импульсов блок управления может дополнительно содержать интерфейс связи, группа выводов которого с одной стороны соединена с выводами управляющего микроконтроллера, а группа выводов с другой стороны интерфейса выполнена с возможностью соединения с персональным компьютером через СОМ-порт. 1 з.п. ф-лы, 1 ил.

Генератор задержанных импульсов, содержащий блок питания, соединенный с блоком управления, включающим панель управления, тактовый генератор, по крайней мере один канал входных импульсов, управляющий микроконтроллер, соединенный двухсторонней связью с панелью управления, многоканальное устройство задержки с заданным количеством каналов выходных импульсов, при этом блок управления соединен с каждой линией задержки по крайней мере одной шиной данных и линиями связи, одни из которых предназначены для передачи сигналов с тактовыми частотами, а другие предназначены для передачи сигналов запуска, отличающийся тем, что выполнен в виде модульной конструкции, включающей модули блока управления, блока питания и модули устройства задержки; генератор задержанных импульсов содержит несколько каналов входных импульсов, входные и выходные каналы импульсов выполнены в виде оптических преобразователей сигналов; блок управления дополнительно содержит программируемую логическую интегральную схему (ПЛИС БУ), предназначенную для буферизации тактового сигнала с начальной тактовой частотой, преобразования тактового сигнала в синхронизирующие импульсы с преобразованной тактовой частотой, мультиплексирования входных сигналов и формирования сигналов запуска на модули устройства задержки, тактовый вход которой соединен с выходом тактового генератора, первая группа выводов ПЛИС БУ соединена с первой группой выводов управляющего микроконтроллера, входные каналы блока управления соединены со второй группой выводов ПЛИС БУ; каждый модуль устройства задержки дополнительно содержит вспомогательный микроконтроллер (МК МЗ), таймер и программируемую логическую интегральную схему модуля задержки (ПЛИС МЗ), предназначенную для формирования заданных интервалов задержки совместно с таймером модуля устройства задержки, первая группа выводов вспомогательного микроконтроллера каждого модуля задержки соединена посредством первой шины данных со второй группой выводов управляющего микроконтроллера, вторая группа выводов вспомогательного микроконтроллера соединена второй шиной данных с первой группой выводов таймера и первой группой выводов ПЛИС МЗ, вторая группа выводов таймера соединена с четвертой группой выводов ПЛИС МЗ двухсторонней четвертой линией связи, предназначенной для передачи сигналов управления, третья группа выводов ПЛИС БУ соединена первой линией связи, передающей сигналы с начальной тактовой частотой на синхронизирующий вход ПЛИС МЗ каждого модуля задержки, четвертая группа выводов ПЛИС БУ соединена второй линией связи, передающей сигналы с преобразованной тактовой частотой, с синхронизирующими входами таймера и вспомогательного микроконтроллера каждого модуля задержки, пятая группа выводов ПЛИС БУ соединена третьей линией связи, передающей сигналы запуска, со второй группой выводов ПЛИС МЗ каждого модуля задержки, каждый вывод из третьей группы выводов ПЛИС МЗ через буферный усилитель соединен с соответствующим выходным каналом каждого модуля задержки.

| ПРОГРАММИРУЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1992 |

|

RU2019907C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2133076C1 |

| Многоканальный программируемый генератор импульсов | 1985 |

|

SU1348985A1 |

| US 5159205 A, 27.10.1992. | |||

Авторы

Даты

2008-07-10—Публикация

2006-06-13—Подача