1

Изобретение относится к импульсной технике и может быть использовано в контрольно-измерительной аппаратуре и цифровых вычислительных ма- ишнах, в частности в устройствах функционального контроля интегральных схем с повышенным уровнем интеграции, в качестве формирователя синхронизирующих, стробирующих и управляющих сигналов для объектов контроля и амплитудно-временных дискриминаторов.

Цель изобретения - повышение надежности работы и расширение функциональных возможностей устройства.

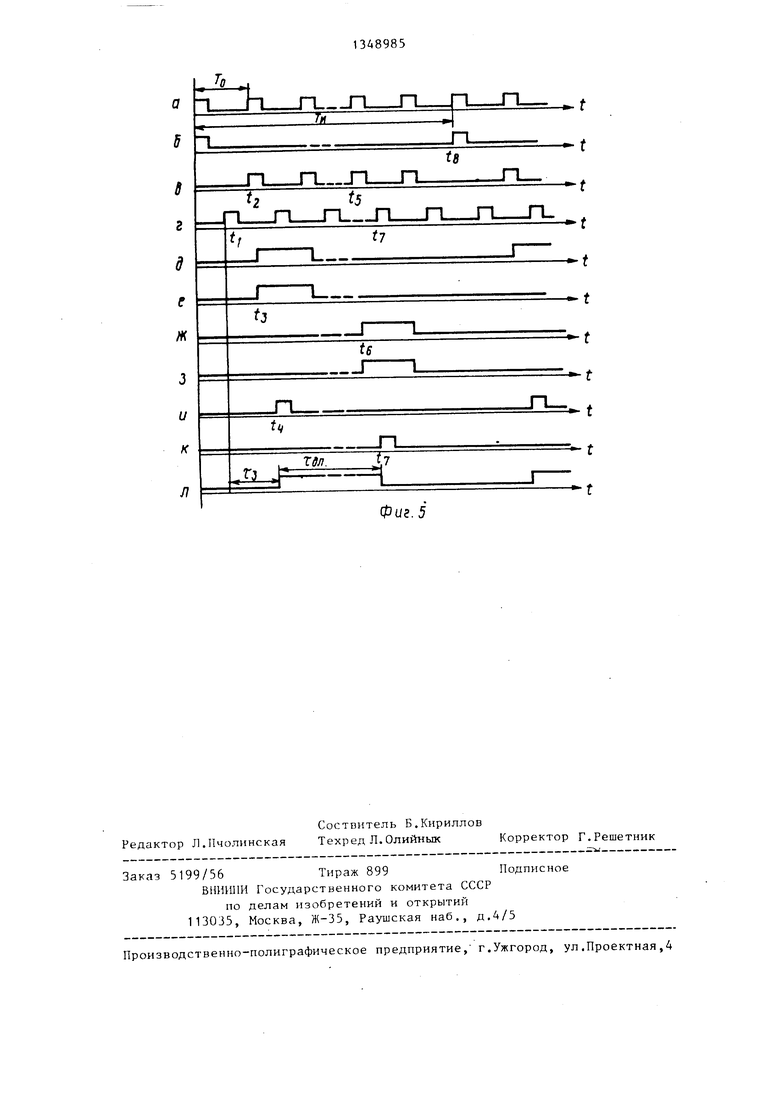

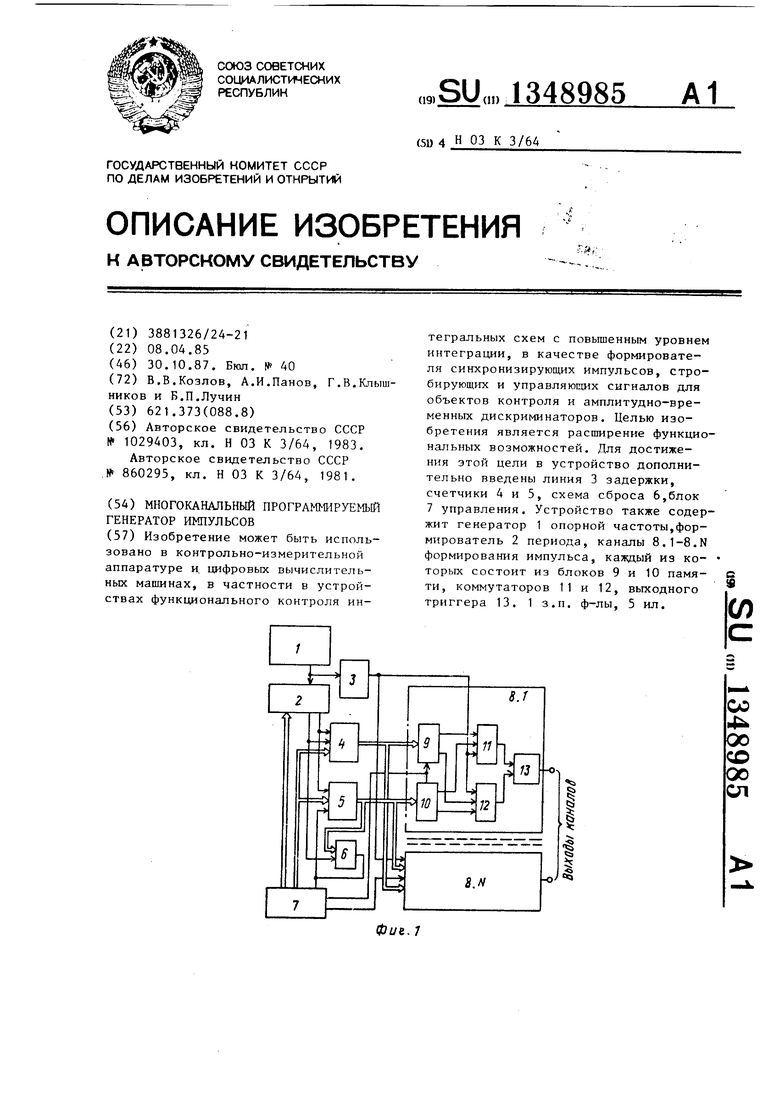

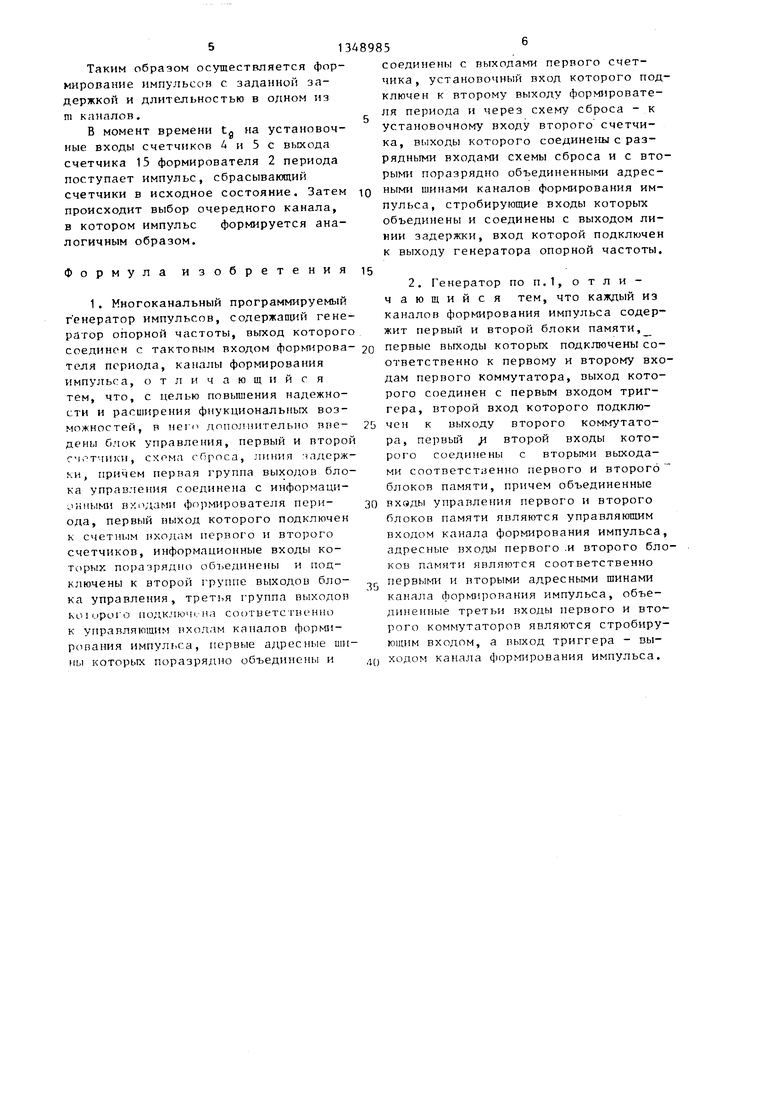

На фиг.1 представлена блок-схема Uюгoкaнaльнoгo программируемого генератора импульсов; на фиг,2-А - схемы формирователя периода, устройства сброса и блока управления; на фиг.5 - временные диаграммы работы устройства.

Устройство содержит генератор 1 опорной частоты, формирователь 2 периода, линию 3 задержки, счетчики 4 и 5,схему 6 сброса,блок 7 управления я каналы 8.1-8.N формирования импульса, каждый из которых состоит из блоков 9 и 10 памяти, коммутаторов 11 и 12 и выходного триггера 13.

Выход генератора 1 опорной частоты соединен с тактовым входом формирователя 2 периода и через линию 3 задержки с первыми входами коммутаторов 11 и 12 каналов 8,1-8.N фор- мире)вания импульса. Г1ери,1й пыход формирователя 2 периода соединен со счетными входами счетчиков 4 и 5, второй выход - с установочн1 1ми входа ми счетчика 4 и схемы 6 сброса, выхо KoTopoii соединен с установочным вхо- сч- тчпка 5. Информационные нходы формирователя 2 периода подключены к первой группе выходов блока 7 управления, вторая группа выходов которого соединена с информационными входами счетчиков 4 и 5. Выходы разрядов счетчика 4 подключены к адресным входам блока 9 памяти каждого из кан;и1ов 8.1-8.N формирования импульса,, выходы рагфядов счетчика 5 - к разрядным входам схемы 6 сбро- са и anpecHiiiM входам блока 10 памяти каждого канала 8.1-8.N. Трет1)Я груп- :т;1 улзгхпдов блока 7 у111:1апления пока- нально соединена с объединенными в каждом канале управляющими входами блоков 9 и 10 памяти. Первые выходы

489852

блоков 9 и 1( памяти соединены соответственно с вторыми и третьими входами коммутатора 11, вторые выходы блоков 9 и 10 памяти - с вторым и третьим входами коммутатора 12, выходы коммутатора 11 и 12 раздельно подключены к входам выходного триггера 13.

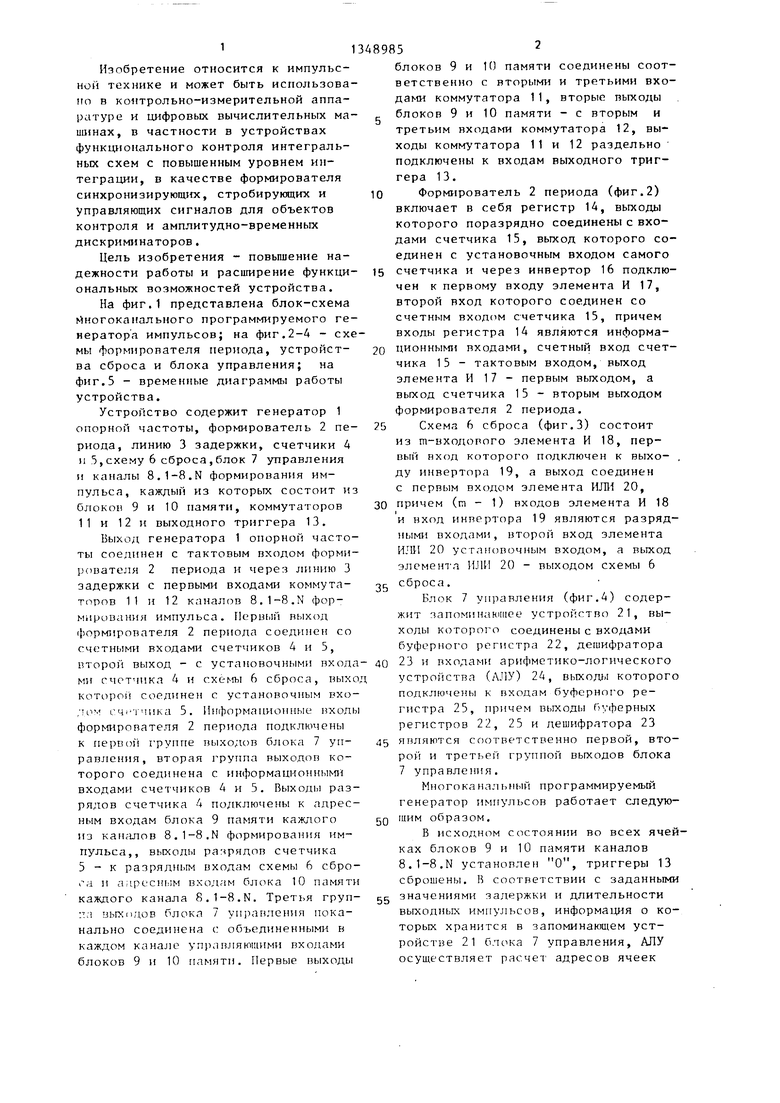

10 Формирователь 2 периода (фиг.2) включает в себя регистр 14, выходы которого поразрядно соединены с входами счетчика 15, выход которого соединен с установочным входом самого

15 счетчика и через инвертор 16 подключен к первому входу элемента И 17, второй вход которого соединен со счетным входом счетчика 15, причем входы регистра 14 являются информа20 ционными входами, счетный вход счетчика 15 - тактовым входом, выход элемента И 17 - первым выходом, а выход счетчика 15 - вторым выходом формирователя 2 периода.

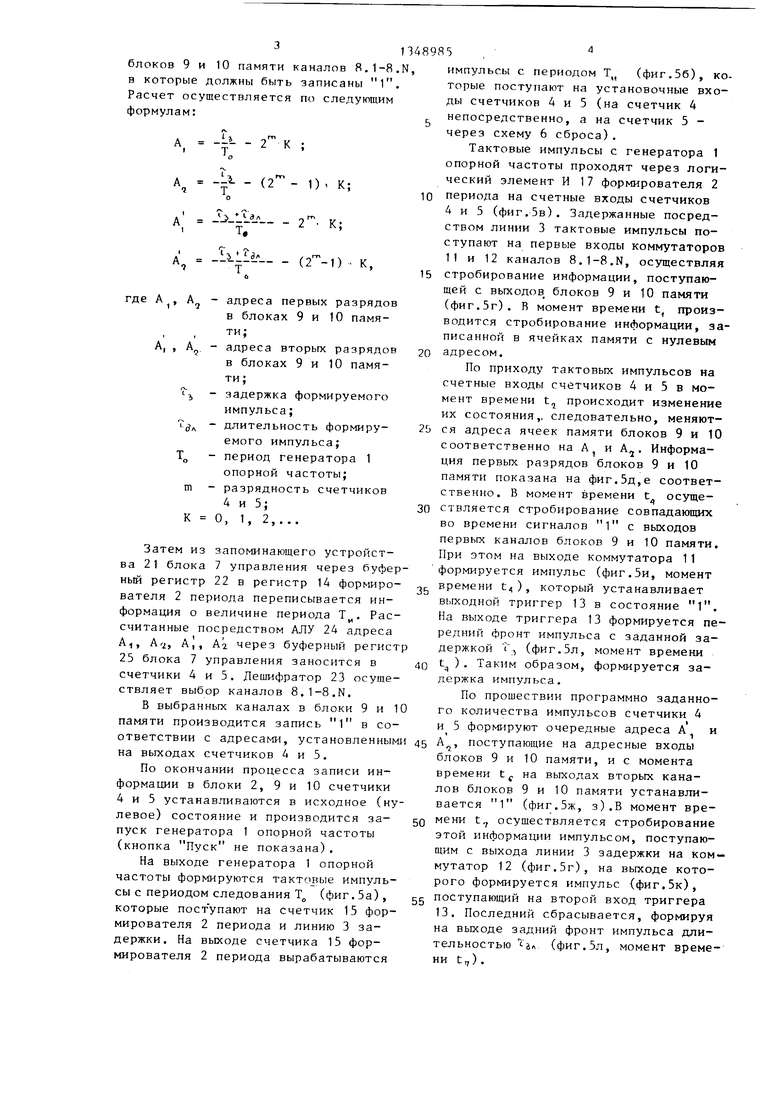

25 Схема 6 сброса (фиг.З) состоит из т-входопого элемента И 18, первый вход которого подключен к выходу инвертора 19, а выход соединен с первым входом элемента ИЛИ 20,

30 причем (т - 1) входов элемента И 18 и вход инвертора 19 являются разрядными входами, второй вход элемента ИЛИ 20 установочным входом, а выход элемента ИЛИ 20 - выходом схемы 6

og сброса.

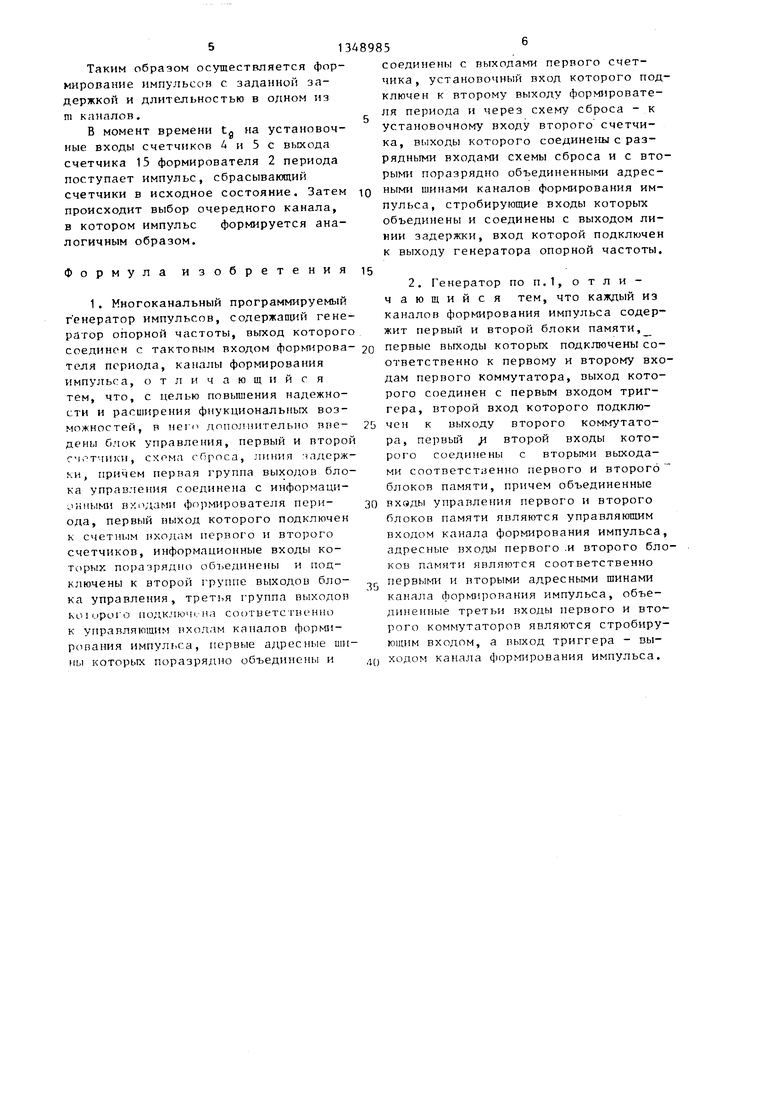

Блок 7 управления (фиг.4) содержит запоминакинее устройство 21, выходы которого соединены с входами буферного регистра 22, дешифратора 40 23 и входами арифметико-логического устройства (ЛЛУ) 24, выход1л которого подключены к входам буферного регистра 25, причем выходы бу(}1ерных регистров 22, 25 и дешифратора 23

45 являются соответственно первой, второй и третьей группой выходов блока 7 управления.

Многоканальный программируемый генератор импульсов работает следую50 шим образом.

В исходном состоянии во всех ячейках блоков 9 и 10 памяти каналов 8.1-8.N установлен О, триггеры 13 сброшены. В соответствии с заданными

gg значениями задержки и длительности выходных импульсов, информация о которых хранится в запоминающем устройстве 21 блока 7 управления, АЛУ осуществляет расчет адресов ячеек

3П489Я5 .

блоков 9 и 10 памяти каналов 8,1-8.N, импульсы с периодом Т

в которые должны быть записаны 1 , Расчет осуществляется по следующим формулам:

торые поступают на уст ды счетчиков 4 и 5 (на непосредственно, а на через схему 6 сброса),

.г Т

- 2 К

А

-Li

- ( 1), К;

ij) ал Т,

- 2

К;

.illli - (2--1)

де А

А„ А, , А, адреса первых разрядов в блоках 9 и 10 памяти;

адреса вторых разрядов в блоках 9 и 10 памяти;

задержка формируемого импульса;

длительность формируемого импульса; период генератора 1 опорной частоты; разрядность счетчиков А и 5; К О, 1, 2,...

m

30 ствляется стробирование совпадающих во времени сигналов 1 с выходов первых каналов блоков 9 и 10 памяти, При этом на выходе коммутатора 11 формируется импульс (фиг.Зи, момент

Затем из запоминающего устройства 21 блока 7 управления через буферный регистр 22 в регистр 14 формиро- .,(- времени t ), который устанавливает вателя 2 периода переписывается ин- выходной триггер 13 в состояние 1.

формация о величине периода Т. Рассчитанные посредством АЛУ 24 адреса А,, А7, А,, Аа через буферный регистр 25 блока 7 управления заносится в счетчики 4 и 5. Дешифратор 23 осуществляет выбор каналов 8.1-8.N.

В выбранных каналах в блоки 9 и 10

блоков 9 и 10 памяти, и с момента времени t,. на выходах вторых кана50

лов блоков 9 и 10 памяти устанавливается 1 (фиг.5ж, з).В момент времени t,

памяти производится запись 1 в со- и 5 формируют очередные адреса А и ответствии с адресами, установленными 45 А, поступающие на адресные входы на выходах счетчиков 4 и 5.

По окончании процесса записи информации в блоки 2, 9 и 10 счетчики 4 и 5 устанавливаются в исходное (нулевое) состояние и производится запуск генератора 1 опорной частоты (кнопка Пуск не показана).

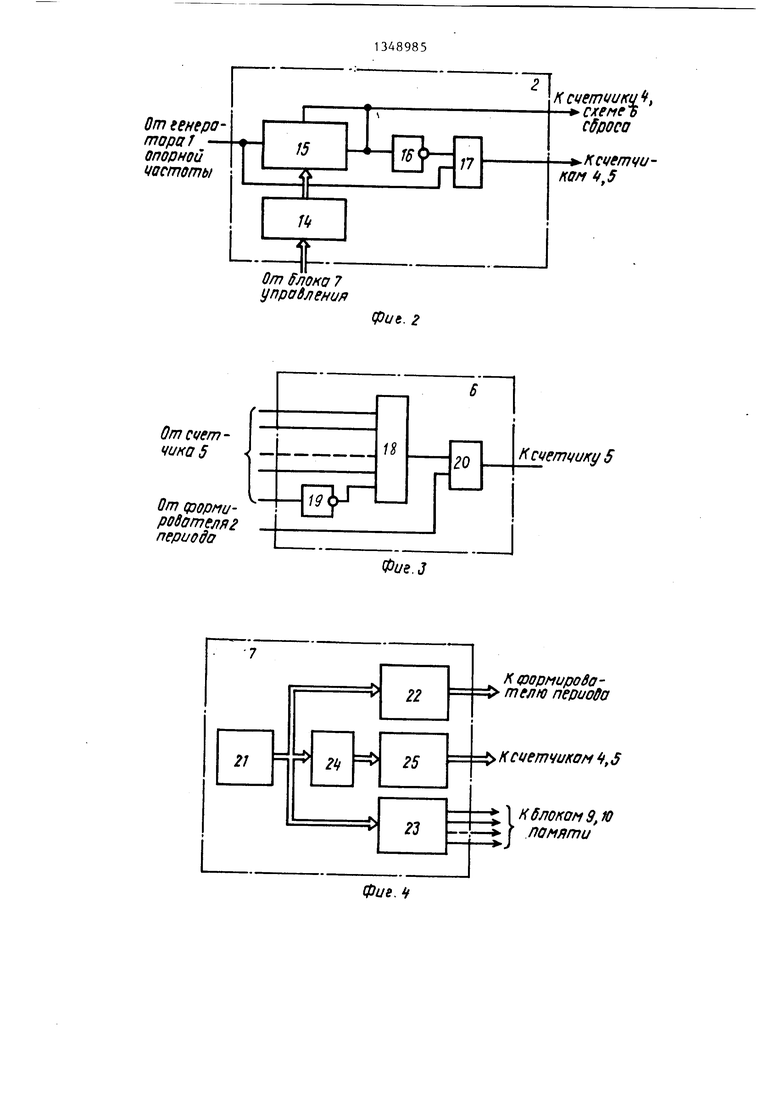

На выходе генератора 1 опорной частоты формируются тактовые импульсы с периодом следования Т (фиг.5а), которые пост упают на счетчик 15 формирователя 2 периода и линию 3 задержки. На выходе счетчика 15 формирователя 2 периода вырабатываются

осуществляется стробирование этой информад11и импульсом, поступающим с выхода линии 3 задержки на коммутатор 12 (фиг.5г), на выходе которого формируется импульс (фиг.Зк), gg поступающий на второй вход триггера 13. Последний сбрасывается, формируя на выходе задний фронт импульса длительностью йл (фиг. 5л, момент времени t).

, импульсы с периодом Т

(фиг.Зб), которые поступают на установочные входы счетчиков 4 и 5 (на счетчик 4 непосредственно, а на счетчик 5 - через схему 6 сброса),

Тактовые импульсы с генератора 1 опорной частоты проходят через логический элемент И 17 формирователя 2

10 периода на счетные входы счетчиков 4 и 5 (фиг.Зв), Задержанные посредством линии 3 тактовые импульсы поступают на первые входы коммутаторов 11 и 12 каналов 8.1-8.N, осуществляя

15 стробирование информации, поступающей с выходов блоков 9 и 10 памяти (фиг.5г). В момент времени t, производится стробирование информации, записанной в ячейках памяти с нулевым

20 адресом.

По приходу тактовых импульсов на счетные входы счетчиков 4 и 5 в момент времени t происходит изменение их состояния,, следовательно, меняют25 ся адреса ячеек памяти блоков 9 и 10 соответственно на А и А. Информация первых разрядов блоков 9 к 10 памяти показана на фиг.5д,е соответственно. В момент времени t осуще-

30 ствляется стробирование совпадающих во времени сигналов 1 с выходов первых каналов блоков 9 и 10 памяти, При этом на выходе коммутатора 11 формируется импульс (фиг.Зи, момент

- .,(- времени t ), который устанавливает выходной триггер 13 в состояние 1.

На выходе триггера 13 формируется передний фронт импульса с заданной задержкой 1, (фиг.5л, момент времени t ) Таким образом, формируется задержка импульса.

По прошествии программно заданного количества импульсов счетчики 4

блоков 9 и 10 памяти, и с момента времени t,. на выходах вторых канаи 5 формируют очередные адреса А А, поступающие на адресные входы

лов блоков 9 и 10 памяти устанавливается 1 (фиг.5ж, з).В момент времени t,

осуществляется стробирование этой информад11и импульсом, поступающим с выхода линии 3 задержки на коммутатор 12 (фиг.5г), на выходе которого формируется импульс (фиг.Зк), поступающий на второй вход триггера 13. Последний сбрасывается, формируя на выходе задний фронт импульса длительностью йл (фиг. 5л, момент времени t).

Таким образом осуществляется формирование импульсов с заданной задержкой и длительностью в одном из m каналов.

В момент времени tg на установочные входы счетчиков Д и 5 с выхода счетчика 15 формирователя 2 периода поступает импульс, сбрасывающий счетчики в исходное состояние. Затем происходит выбор очередного канала,

10

в котором импульс логичным образом.

формируется анаФормула изобретения 15

1. Многоканальный программируемый г енератор импульсов, содержаний генератор опорной частоты, выход которого

соединены с выходами первого счетчика , установочный вход которого подключен к второму выходу формирователя периода и через схему сброса - к установочному входу второго счетчика, выходы которого соедине1ал с разрядными входами схемы сброса и с вторыми поразрядно объединенными адресными шинами каналов формирования импульса, стробирующие входы которых объеди)1ены и соединены с выходом линии задержки, вход которой подключен к выходу генератора опорной частоты.

2. Генератор по п.1, о т л и - чающийся тем, что каждый из каналов формирования импульса содержит первый и второй блоки памяти, соединен с тактовым входом форьшрова- 20 первые выходы которых подключены со- теля периода, каналы формирования импульса, отличающийся тем, что, с целью повьпиения надежности и расширения фнукциональных возможностей, в негп дополнительно вне- 2S дены блок управления, первый и второй гмотчик и, схома сброса, линия яадсрж- ки, причем первая группа выходов блока управления соедине)1а с информаци- cDiiibibOi входами формирователя пери- зо ода, первый выход которого подключен к счетным нходам первого и второго счетчиков, информационные входы которых поразрядно обт.единены и подключены к второй группе выходов бло- ка управления, трет15Я группа выходов Koiuporo подключена соответственно к управляющим входам каналов формирования импул 1са, первые адресные шп- иы которых поразрядно объединены и ,,j()

ответственно к первому и второму входам первого коммутатора, выход которого соединен с первым входом триггера, второй вход которого подключен к выходу второго коммутатора, первый второй входы которого соединены с вторыми выходами соответственно первого и второго блоков памяти, причем объединенные вхэды управления первого и второго блоков памяти являются управляющим входом канала формирования импульса, адресные входы первого .и второго блоков памяти являются соответственно первыми и вторыми адресными щинами канала фор№1рования импульса, объединенные третьи входы первого и рого коммутаторов являются стробиру- Ю1ЦИМ входом, а выход триггера - выходом канала формирования импульса.

2. Генератор по п.1, о т л и - чающийся тем, что каждый из каналов формирования импульса содержит первый и второй блоки памяти, первые выходы которых подключены со-

ответственно к первому и второму входам первого коммутатора, выход которого соединен с первым входом триггера, второй вход которого подключен к выходу второго коммутатора, первый второй входы которого соединены с вторыми выходами соответственно первого и второго блоков памяти, причем объединенные вхэды управления первого и второго блоков памяти являются управляющим входом канала формирования импульса, адресные входы первого .и второго блоков памяти являются соответственно первыми и вторыми адресными щинами канала фор№1рования импульса, объединенные третьи входы первого и рого коммутаторов являются стробиру- Ю1ЦИМ входом, а выход триггера - выходом канала формирования импульса.

21 -

Фик. 2

Фие.З

кформиродо- телн} периода

К счетчиком ,S

К блоком 9,Ю Г памяти

Фие. if

ж

5

I

n

tv

,й

Гдл.

Соствнтель Б.Кириллов

Редактор Л.Пчолинская Техред Л.Олийнык Корректор Г.Решетник

.,.....«...;г...-

Заказ 5199/56Тираж 899Подписное

ВИИИ11И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная ,4

П.

tB

5

t

l7

-t

f

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

Изобретение может быть использовано в контрольно-измерительной аппаратуре и. цифровых вычислительных машинах, в частности в устройствах функционального контроля интегральных схем с повышенным уровнем интеграции, в качестве формирователя синхронизирующих импульсов, стро- бирующих и управляющих сигналов для объектов контроля и амплитудно-временных дискриминаторов. Целью изобретения является расширение функциональных возможностей. Для достижения этой цели в устройство дополнительно введены линия 3 задержки, счетчики 4 и 5, схема сброса 6,блок 7 управления. Устройство также содержит генератор 1 опорной частоты,формирователь 2 периода, каналы 8.1-8.N формирования импульса, каждый из которых состоит из блоков 9 и 10 памяти, коммутаторов 11 и 12, выходного триггера 13. 1 з.п. ф-лы, 5 ил. (Л 00 4 00 со 00 ел Фиъ. 1

| Многоканальный генератор импульсов | 1981 |

|

SU1029403A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный программируемый генератор импульсов | 1979 |

|

SU860295A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-30—Публикация

1985-04-08—Подача