Изобретение относится к электронике, автоматике, измерительной и вычислительной технике и может быть использовано в высокоскоростных аналоговых и цифровых устройствах, в частности в электронных вычислительных машинах (ЭВМ) с элементами искусственного интеллекта.

Известны аналоговые инвертирующие сумматоры, формирующие алгебраическую сумму 2-х и более входных напряжений и меняющие ее знак на обратный, работа которых основана на сложении сигналов с использованием резисторов на инвертирующем входе операционного усилителя и получении на выходе устройства суммированного, с учетом фазы и амплитуды, результирующего сигнала [А.Р.Мамий, В.Б.Тлячев. Операционные усилители. - Майкоп: АГУ, 2005, с.60].

Известны также цифровые сумматоры, работа которых основана на двоичной логике Буля (да, нет), использующей два устойчивых состояния (или уровня сигнала): условный ноль, когда электрического сигнала нет, и условная единица, когда электрический сигнал есть [П.Хоровиц, У.Хилл. Искусство схемотехники. В 3-х томах. Перевод с англ., изд. 4-е, переработанное и дополненное. - М.: Мир, 1993].

Однако сегодня такая техника не отвечает требованиям потребителя и принципиально не пригодна для создания ЭВМ с элементами искусственного интеллекта. Использование в ЭВМ троичной логики Аристотеля (да, не знаю, нет) или пятеричной логики искусственного интеллекта (точно да, около да, не знаю, около нет, точно нет) приостановилось в связи с тем, что нет эффективных полупроводниковых элементов с тремя или пятью устойчивыми состояниями (или уровнями сигнала).

Заявителем в патентной и научно-технической документации не было обнаружено аналогичных универсальных технических устройств.

Задача, решаемая изобретением, - создание универсального (базового) логического элемента для логики, отличающейся от двоичной логики Буля, например, для троичной логики Аристотеля (да, не знаю, нет) или пятеричной логики искусственного интеллекта (точно да, около да, не знаю, около нет, точно нет), применимого как в аналоговой, так и в цифровой электронике, автоматике, измерительной и вычислительной технике и может быть использовано в высокоскоростных аналоговых и цифровых устройствах, в частности, в ЭВМ с элементами искусственного интеллекта.

Поставленная задача решается тем, что универсальный мостовой инвертирующий сумматор (УМИС) содержит подключенные входными электродами к шинам положительного и отрицательного питания УМИС соответственно первое и второе токовые зеркала, причем второе токовое зеркало выполнено комплементарно к первому, и выходные комплементарные транзисторы, которые последовательно включены между шинами положительного и отрицательного питания УМИС, точки соединения выходных комплементарных транзисторов подключены к предварительным выходам УМИС. Между первым и вторым токовыми зеркалами последовательно включены третье и четвертое токовые зеркала, выполненные комплементарно соответственно к первому и второму токовым зеркалам, причем точки соединения соответствующих выходных электродов третьего и четвертого токовых зеркал подключены к соответствующим входам УМИС, а точки соединения соответствующих выходных электродов соответственно первого, третьего и второго, четвертого токовых зеркал подключены соответственно к управляющим электродам выходных комплементарных транзисторов, при этом каждое токовое зеркало содержит одинаковое количество входных и выходных электродов. Между соответствующими входными электродами третьего и четвертого токовых зеркал и предварительными выходами УМИС включены резисторы, а предварительные выходы объединены в общий выход УМИС через резисторы.

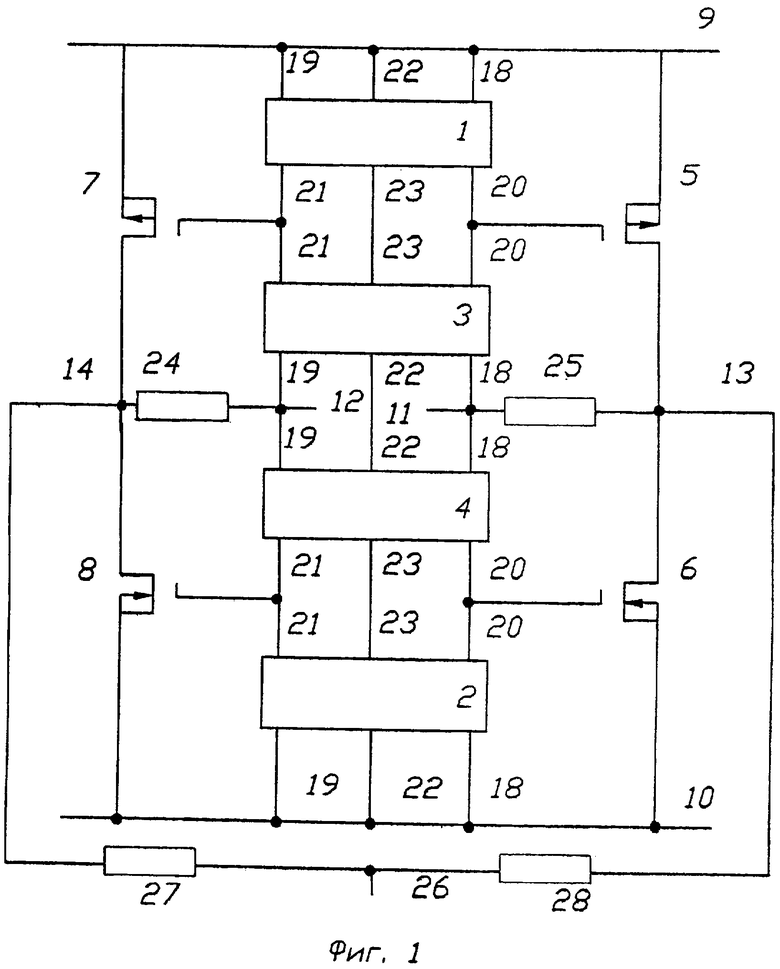

Для решения поставленной задачи также токовое зеркало содержит опорный диод, включенный между опорным входным и опорным выходным электродами токового зеркала, и МОП транзисторы, каждый из которых включен между соответствующими входными и выходными электродами токового зеркала, затворы которых подключены к опорному выходному электроду токового зеркала.

Использование в вычислительных устройствах УМИС, основанных на логике, отличающейся от двоичной логики Буля, позволит:

- обеспечить высокую вирусоустойчивость компьютерных программ, так как в троичной или пятеричной логике компьютеру легче выделить вредоносные программы как инородные и самостоятельно принять решение об их изоляции или уничтожении;

- увеличить скорость работы компьютера, вследствие чего компьютер сможет в несколько раз быстрее производить сложные математические вычисления, в том числе с отрицательными числами (в настоящее время для обозначения знака числа в ЭВМ выделяют дополнительный разряд);

- повысить стабильность работы компьютеров: в случае каких-либо сбоев в отдельных программах они не будут зависать, как это часто происходит в двоичной логике (что вызвано отсутствием состояния «не знаю» и противоречием состояния «да и нет»), и компьютер не нужно будет перезагружать заново, теряя при этом полезную информацию. Новые ЭВМ будут продолжать работать в других блоках программы и ожидать промежуточного решения для подпрограммы, давшей сбой. К тому же троичная или пятеричная логика наиболее удобна для написания программ с использованием русского языка, что создаст гораздо больше возможностей при пользовании такими компьютерами русскоязычным пользователям;

- создавать кибернетические устройства (в том числе и соответствующим программированием) с элементами искусственного интеллекта, что, в свою очередь, существенно упростит пользование таким компьютером, т.е. бытовой компьютер может быть превращен в электронного эксперта;

- создавать новое поколение электронных технических систем различного назначения с элементами искусственного интеллекта, программные продукты, обеспечивающие новые функциональные качества и конкурентоспособность производимой продукции;

- создать свои надежные аналогово-цифровые электронно-вычислительные машины с элементами искусственного интеллекта, работающие в режиме реального времени, например для автопилотов в авиастроении;

- расширить возможности для равноправного международного сотрудничества в сфере высоких технологий.

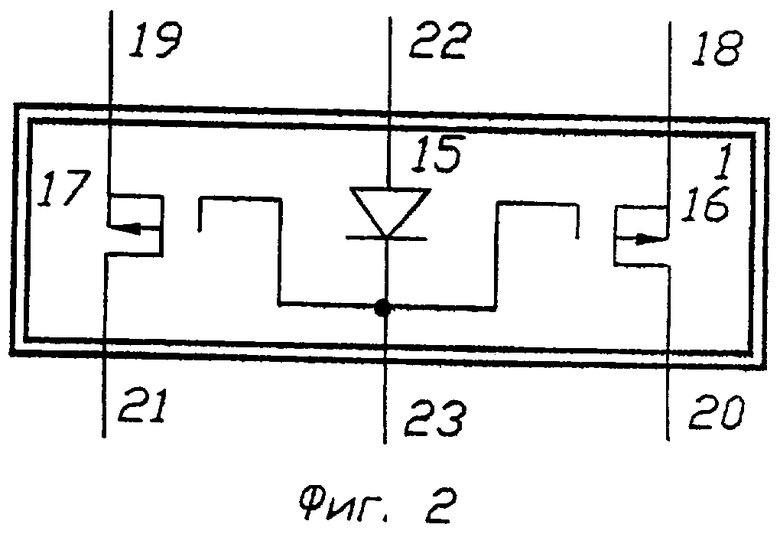

На фиг.1 показана блок-схема универсального мостового инвертирующего сумматора, на фиг.2 показан пример выполнения токового зеркала, а в таблице приведена таблица истинности УМИС.

Универсальный мостовой инвертирующий сумматор (УМИС) содержит токовые зеркала 1-4, выходные транзисторы 5-8, шины положительного 9, отрицательного 10 напряжения питания, входы 11, 12, предварительные выходы 13, 14. Токовое зеркало (фиг.2) содержит, например, опорный диод 15, транзисторы 16, 17, входные электроды 18, 19, выходные электроды 20, 21, опорный входной электрод 22, опорный выходной электрод 23. При этом в качестве диода может быть использован транзистор в диодном включении. Между входными электродами 18, 19 и предварительными выходами 13, 14 установлены резисторы 24, 25, при этом предварительные выходы 13, 14 объединены в общий выход 26 через резисторы 27, 28.

Работает УМИС следующим образом. Уровень сигнала, соответствующий числу Ч1, подают на вход 11 (или 12), а на вход 12 (или 11) подают уровень сигнала, который соответствует числу Ч2. Входные сигналы поступают со входов 11 и 12 (фиг.1) на входы 18 и 19 токовых зеркал 3 и 4, через выходы 20 и 21 которых передаются к управляющим электродам, выходных комплементарных транзисторов 5, 6 и 7, 8. В итоге на нагрузке 27 и 28, которая подключена к предварительным выходам 13 и 14 (между точками соединения выходных транзисторов), образуется суммированный итоговый сигнал (ИС) на выходе 26, который соответствует числу результата с противоположным (инвертированным) знаком. Полная таблица истинности УМИС приведена в таблице.

На пересечении строк (число Ч1 на входе 11) и столбцов (число Ч2 на входе 12) - итоговый сигнал ИС (уровень сигнала) на выходе 26,

где: - 1-й уровень сигнала (+2) - уровень питания +V; (точно да/нет)*

- 2-й уровень сигнала (+1) - уровень питания +V/2; (около да/нет)*

- 3-й уровень сигнала (0) - уровень питания 0; (не знаю)

- 4-й уровень сигнала (-1) - уровень питания -V/2; (около нет/да)*

- 5-й уровень сигнала (-2) - уровень питания -V; (точно нет/да)*

- * обозначает, что уровень ориентировочный (условный) и зависит от технологических особенностей конкретного исполнения УМИС.

В итоге получают 5 (пять) устойчивых условных уровней сигнала (поэтому легко воспроизводимых), которые пригодны для реализации логики, отличающейся от двоичной логики Буля, например, для троичной логики Аристотеля (да, не знаю, нет) или пятеричной логики искусственного интеллекта (точно да, около да, не знаю, около нет, точно нет).

Заявляемое техническое решение соответствует критерию «новизна», так как аналогичных устройств заявителем не обнаружено. Следует отметить, что предлагаемое устройство является универсальным, поскольку в отличие от известных решений оно одновременно работает как аналоговой сумматор и как цифровой сумматор.

В литературе известен «Малошумящий широкополосный усилитель тока Олексенко-Колесникова» [патент РФ №2178235, МПК 7 Н03F 1/26, 3/26, опубликован 10.01.2002], который имеет сходное техническое строение. Он содержит входные электроды, подключенные к шинам положительного и отрицательного питания усилителя, соответственно первое и второе токовые зеркала, причем второе токовое зеркало выполнено комплементарно к первому, и выходные комплементарные транзисторы, которые последовательно включены между шинами положительного и отрицательного питания усилителя, точки соединения выходных комплементарных транзисторов подключены к выходам усилителя, причем между первым и вторым токовыми зеркалами последовательно включены третье и четвертое токовые зеркала, выполненные комплементарно соответственно к первому и второму токовым зеркалам, причем точки соединения соответствующих выходных электродов третьего и четвертого токовых зеркал подключены к соответствующим входам усилителя, а точки соединения соответствующих выходных электродов соответственно первого, третьего и второго, четвертого токовых зеркал подключены соответственно к управляющим электродам выходных комплементарных транзисторов, при этом каждое токовое зеркало содержит одинаковое количество входных и выходных электродов.

Однако указанное решение обладает только тремя устойчивыми состояниями (или уровнями сигнала) на каждом из своих выходов (+V, 0, -V), но не имеет пяти устойчивых состояний (или уровней сигнала). Кроме того, оно выполняет только функцию усилителя и не способно выполнять функцию сумматора. На основании этого заявитель считает, что заявляемое техническое решение соответствует критерию «изобретательский уровень».

Использование принципиально нового универсального мостового инвертирующего сумматора (далее - УМИС) позволит создать в России свои аналогово-цифровые электронно-вычислительные машины с элементами искусственного интеллекта.

(уровень сигнала) на входе 11

Универсальный мостовой инвертирующий сумматор (УМИС) предназначен для использования как в аналоговой, так и в цифровой электронике, вычислительной технике. УМИС содержит подключенные входными электродами к шинам положительного и отрицательного питания УМИС соответственно первое (1) и второе (2) токовые зеркала (ТЗ), причем ТЗ (2) выполнено комплементарно к ТЗ (1), и выходные комплементарные транзисторы (Т) (5-8), которые последовательно включены между шинами положительного и отрицательного питания УМИС. Точки соединения Т (7, 8) и Т (5, 6) подключены к предварительным выходам (14, 13) УМИС. Между ТЗ (1) и ТЗ (2) последовательно включены третье (3) и четвертое (4) ТЗ, выполненные комплементарно соответственно к ТЗ (1) и ТЗ (2). Точки соединения соответствующих входных электродов ТЗ (3) и ТЗ (4) подключены к соответствующим входам УМИС, а точки соединения соответствующих выходных электродов соответственно ТЗ (1, 3) и ТЗ (2, 4) подключены соответственно к управляющим электродам выходных комплементарных Т (5-6). Каждое ТЗ содержит одинаковое количество входных и выходных электродов. Между соответствующими выходными электродами ТЗ и предварительными выходами УМИС включены резисторы (24, 25), а предварительные выходы объединены в общий выход УМИС через резисторы (27, 28). Технический результат заключается в создании аналого-цифровых электронно-вычислительных машин с элементами искусственного интеллекта. 1 з.п. ф-лы, 1 табл., 2 ил.

| JP 1153778 А, 12.07.1986 | |||

| МАЛОШУМЯЩИЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ ТОКА ОЛЕКСЕНКО-КОЛЕСНИКОВА | 2000 |

|

RU2178235C1 |

| Усилитель тока | 1989 |

|

SU1739476A1 |

| JP 61065525 A, 04.04.1986 | |||

| US 4577160, 18.03.1986. | |||

Авторы

Даты

2008-08-10—Публикация

2007-05-10—Подача