Изобретение относится к области радиотехники и может быть использовано в качестве функционального узла аналоговых микросхем (например, дифференциальных (ОУ) и мультидифференциальных операционных усилителях (МОУ), компараторах и т.п.) для задач усиления и фильтрации сигналов, в том числе в диапазоне низких температур.

Основой современных микроэлектронных операционных усилителей, стабилизаторов напряжения, компараторов и т.п. являются так называемые «токовые зеркала», обеспечивающие инверсию по фазе входного токового сигнала в широком диапазоне его изменения [1-21]. Качественные показатели практически всех современных аналоговых микросхем определяются статическими и динамическими параметрами токовых зеркал (ТЗ). Предполагаемое изобретения относится к данному подклассу устройств.

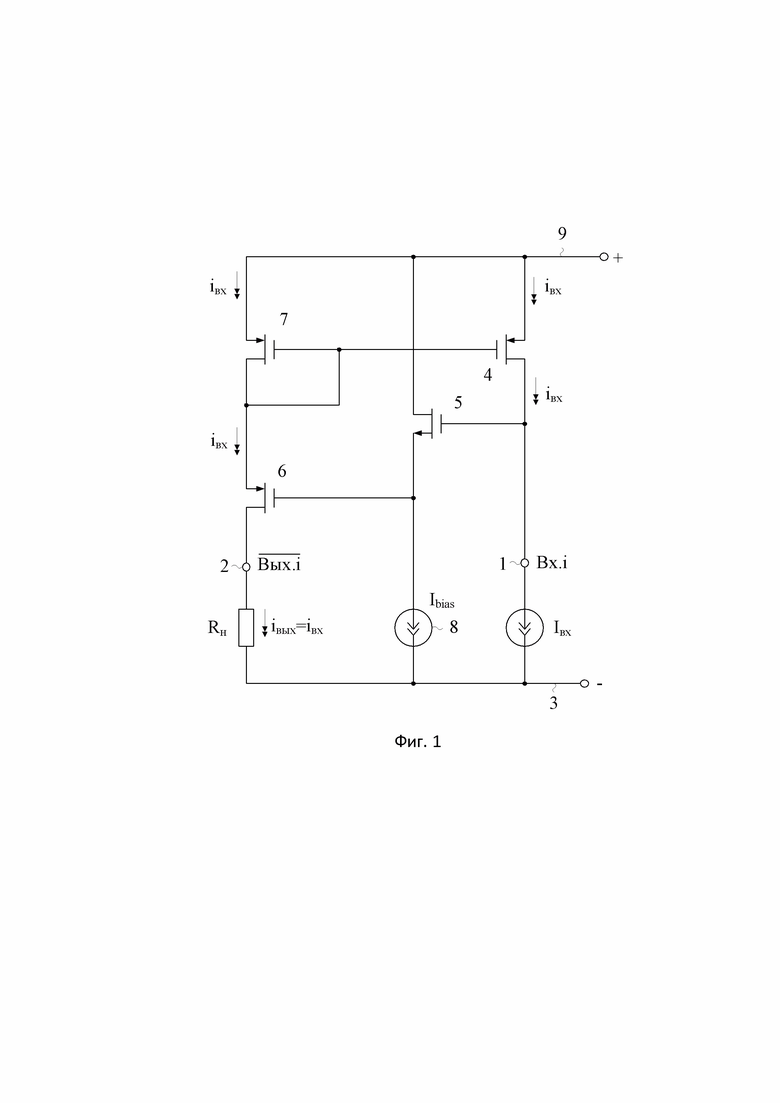

Ближайшим прототипом (фиг. 1) заявляемого устройства является токовое зеркало, описанное в патенте фирмы Intel Corporation US 6.630.818 (fig. 4, 2003 г.), содержащее вход 1 и инвертирующий выход 2 устройства, согласованные с первой 3 шиной источника питания, первый 4 входной полевой транзистор, сток которого связан со входом 1 устройства и соединен с затвором второго 5 входного полевого транзистора, первый 6 выходной полевой транзистор, сток которого подключен к инвертирующему выходу 2 устройства, второй 7 выходной полевой транзистор, источник опорного тока 8, вторую 9 шину источника питания.

Существенный недостаток известного токового зеркала состоит в том, что оно оказывается неработоспособным при реализации на JFet полевых транзисторах, обеспечивающих экстремально малый уровень шумов, высокую радиационную стойкость и стабильную работу аналоговых микросхем в диапазоне криогенных температур. Кроме этого, оно имеет только инвертирующий выход. В тоже время для многих задач аналого-цифрового усиления и фильтрации сигналов крайне необходимы токовые зеркала, содержащие неинвертирующий токовых выход, для которого коэффициент передачи по входному току лежит в диапазоне 1-10 единиц. Такие функциональные узлы позволяют создавать высококачественные активные RC-фильтры, положительная обратная связь в которых замыкается через токовое зеркало.

Основная задача предполагаемого изобретения состоит в создании как инвертирующего, так и неинвертирующего токового зеркала на комплементарных полевых транзисторах с управляющим p-n-переходом для работы при низких температурах, обеспечивающего для разных выходов инвертирующее и неинвертирующее преобразования входного токового сигнала с коэффициентом передачи по току больше единицы.

Поставленная задача решается тем, что в токовом зеркале фиг. 1, содержащем вход 1 и инвертирующий выход 2 устройства, согласованные с первой 3 шиной источника питания, первый 4 входной полевой транзистор, сток которого связан со входом 1 устройства и соединен с затвором второго 5 входного полевого транзистора, первый 6 выходной полевой транзистор, сток которого подключен к инвертирующему выходу 2 устройства, второй 7 выходной полевой транзистор, источник опорного тока 8, вторую 9 шину источника питания, предусмотрены новые элементы и связи - исток второго 5 входного полевого транзистора соединен с первым 10 источником опорного напряжения, его сток соединен с затвором второго 7 выходного полевого транзистора и через источник опорного тока 8 связан со второй 9 шиной источника питания, исток второго 7 выходного полевого транзистора связан с истоком первого 4 входного полевого транзистора и истоком первого 6 выходного полевого транзистора, затвор первого 4 входного полевого транзистора связан с затвором первого 6 выходного полевого транзистора и подключен ко второму 11 источнику опорного напряжения, а сток второго 7 выходного полевого транзистора связан с дополнительным неинвертирующим токовым выходом 12 устройства, причем в качестве всех упомянутых выше полевых транзисторов токового зеркала используются полевые транзисторы с управляющим p-n-переходом JFET.

На фиг. 1 представлена схема токового зеркала-прототипа по патенту 2003 года US 6.630.818 (fig. 4) фирмы Intel Corporation.

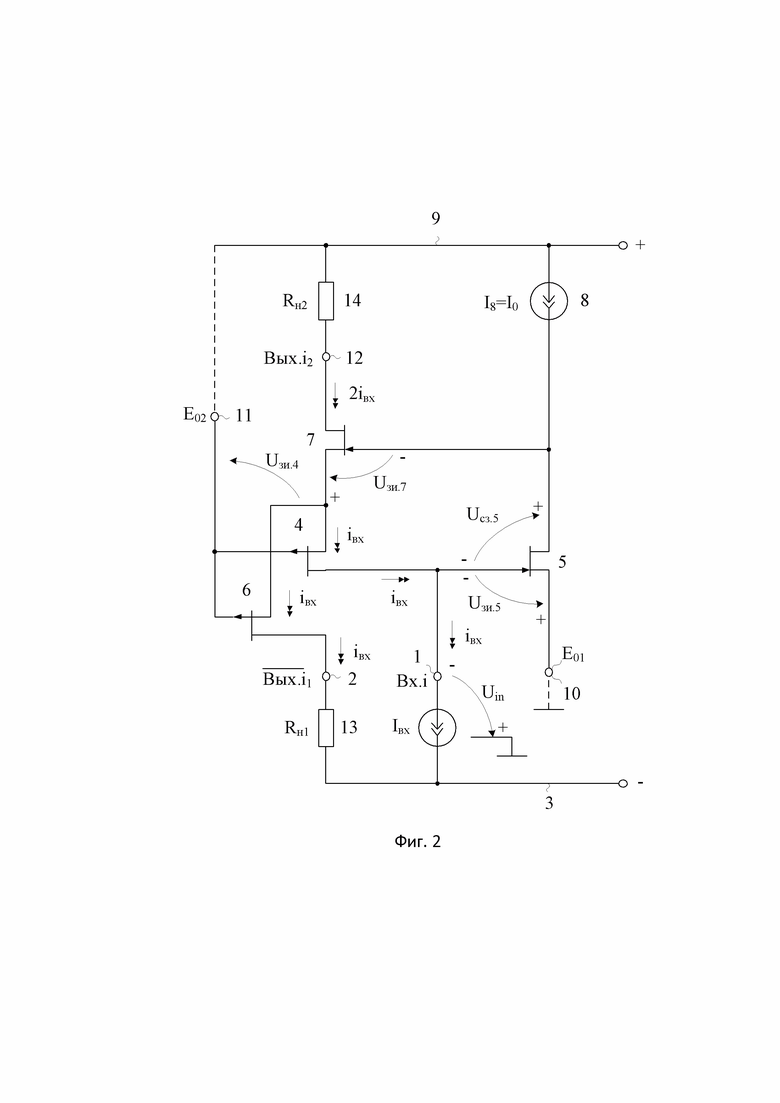

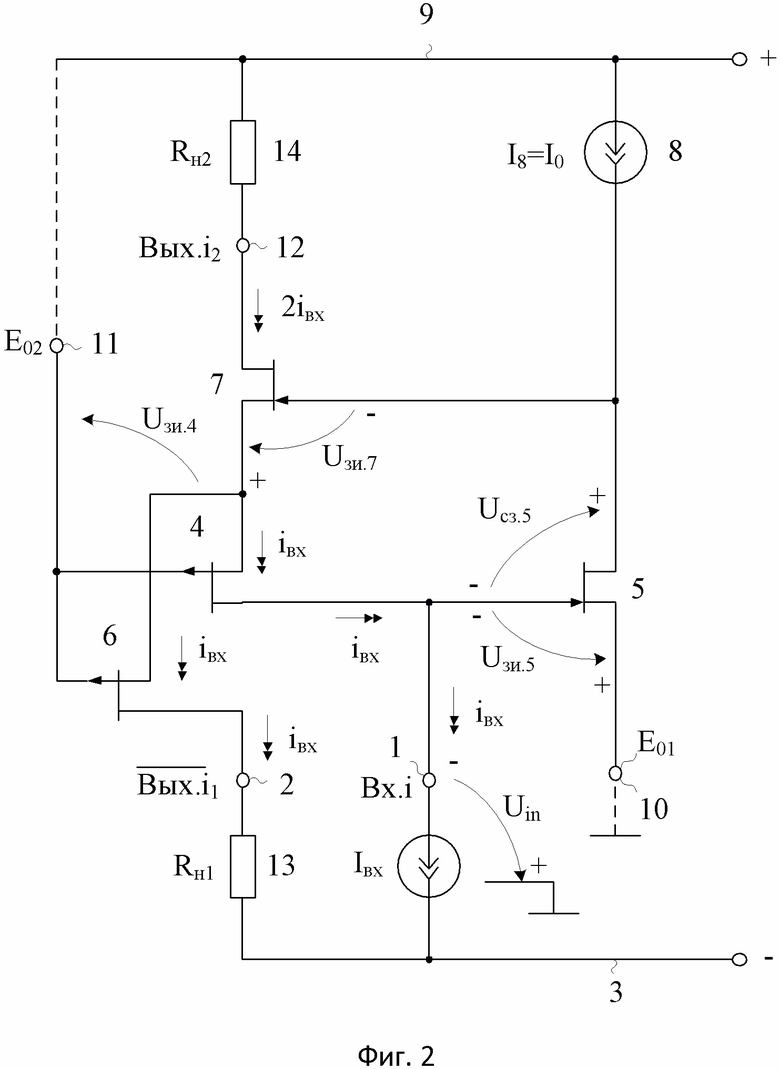

На фиг. 2 показана схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

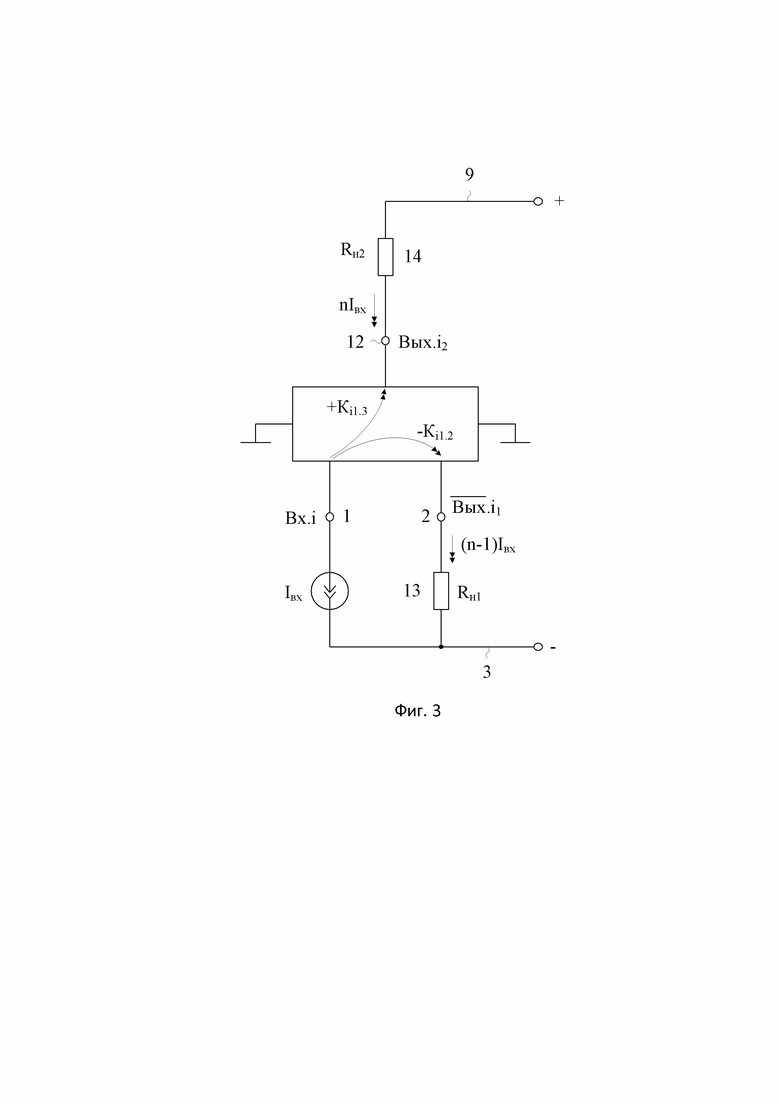

На фиг. 3 приведена функциональная схема заявляемого устройства фиг. 2.

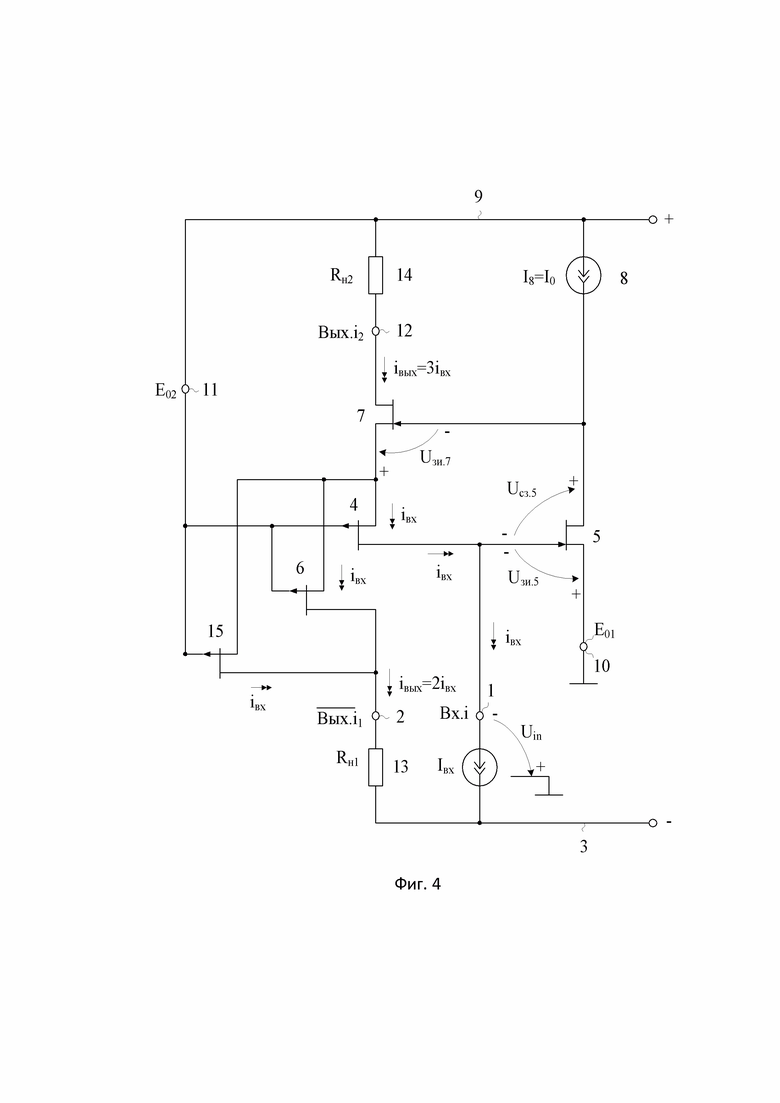

На фиг. 4 представлена схема заявляемого устройства в соответствии с п. 3 формулы изобретения.

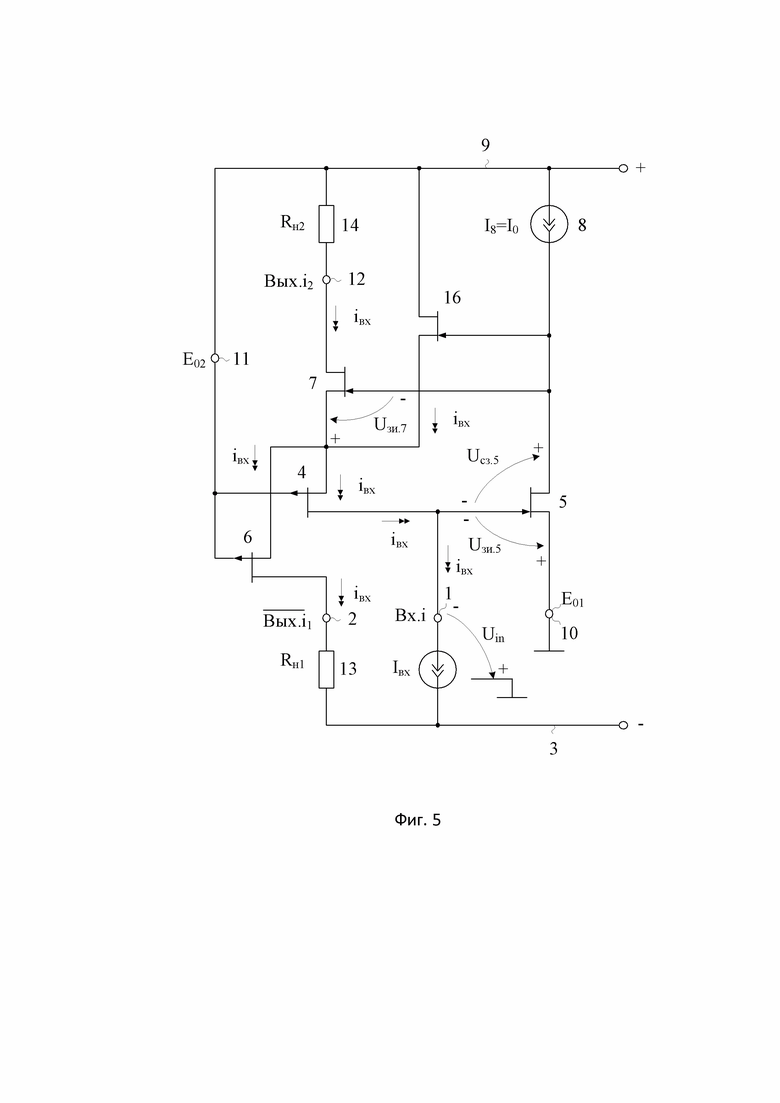

На фиг. 5 показана схема заявляемого устройства в соответствии с п. 4 формулы изобретения.

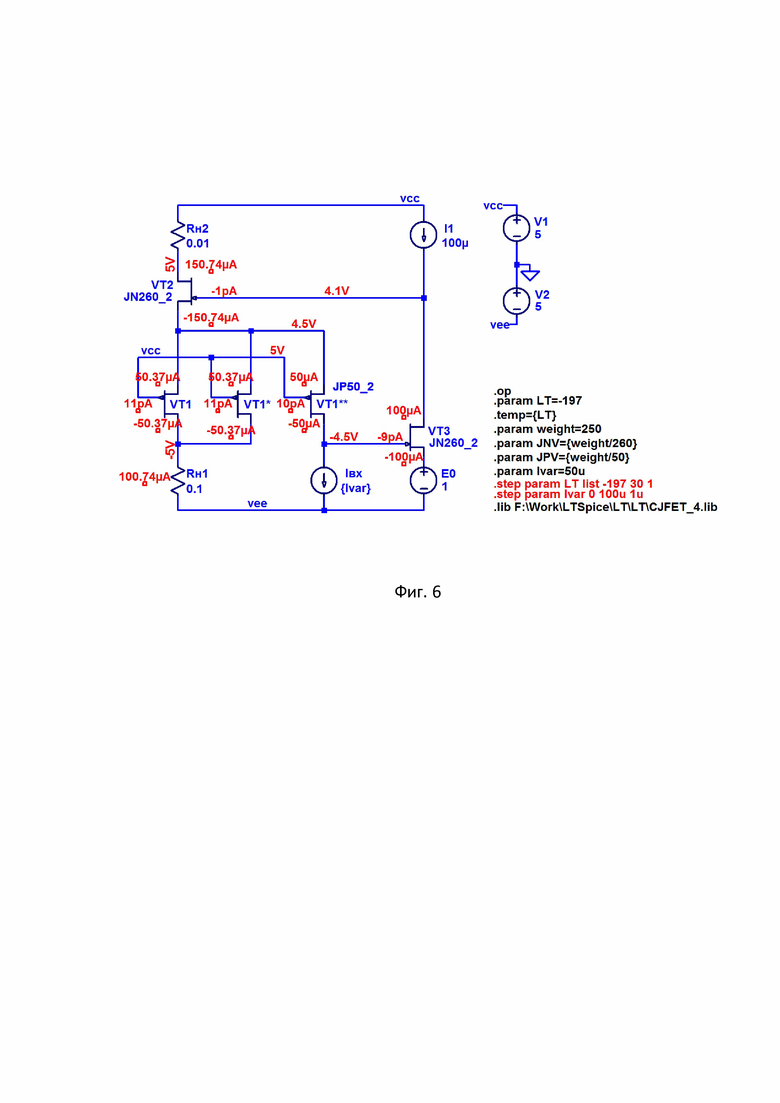

На фиг. 6 приведен статический режим токового зеркала фиг. 4 при температуре -197°С в среде LTSpiceXVII на моделях комплементарных полевых транзисторах ОАО «Интеграл» (г. Минск) при I1=100 мкА, Iвх=I2=50 мкА.

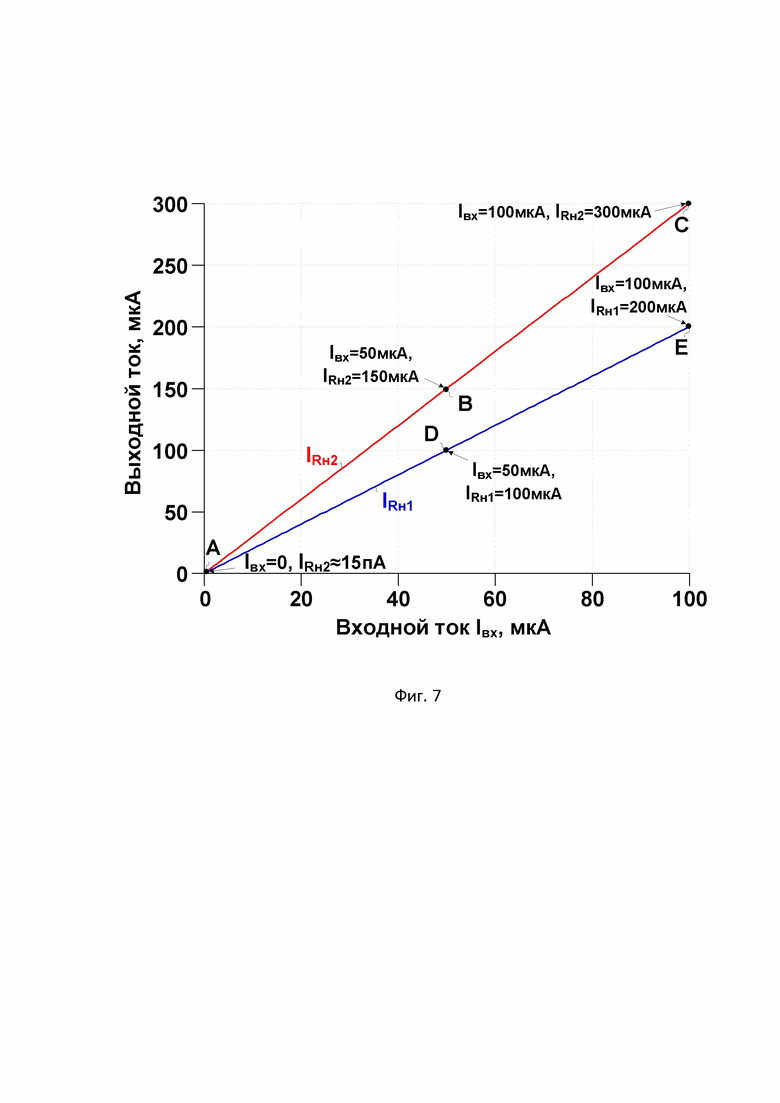

На фиг. 7 показаны зависимости выходных токов токового зеркала фиг. 6 для инвертирующего (2) и неинвертирующего (12) токовых выходов (фиг. 2) при температурах 27°С и -197°С для токов I1=100 мкА, Iвх=I2=0÷100 мкА.

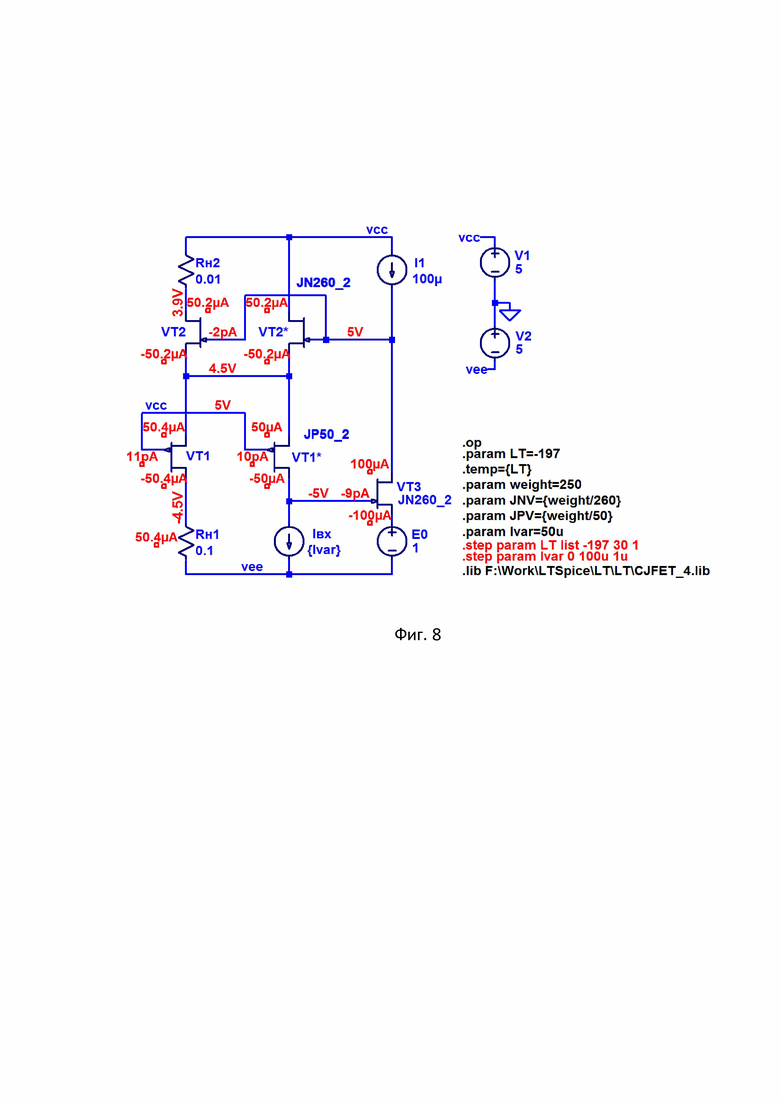

На фиг. 8 представлен статический режим токового зеркала фиг. 5 при температуре -197° на моделях комплементарных полевых транзисторах ОАО «Интеграл» (г. Минск) при I1=100 мкА, Iвх=I2=50 мкА.

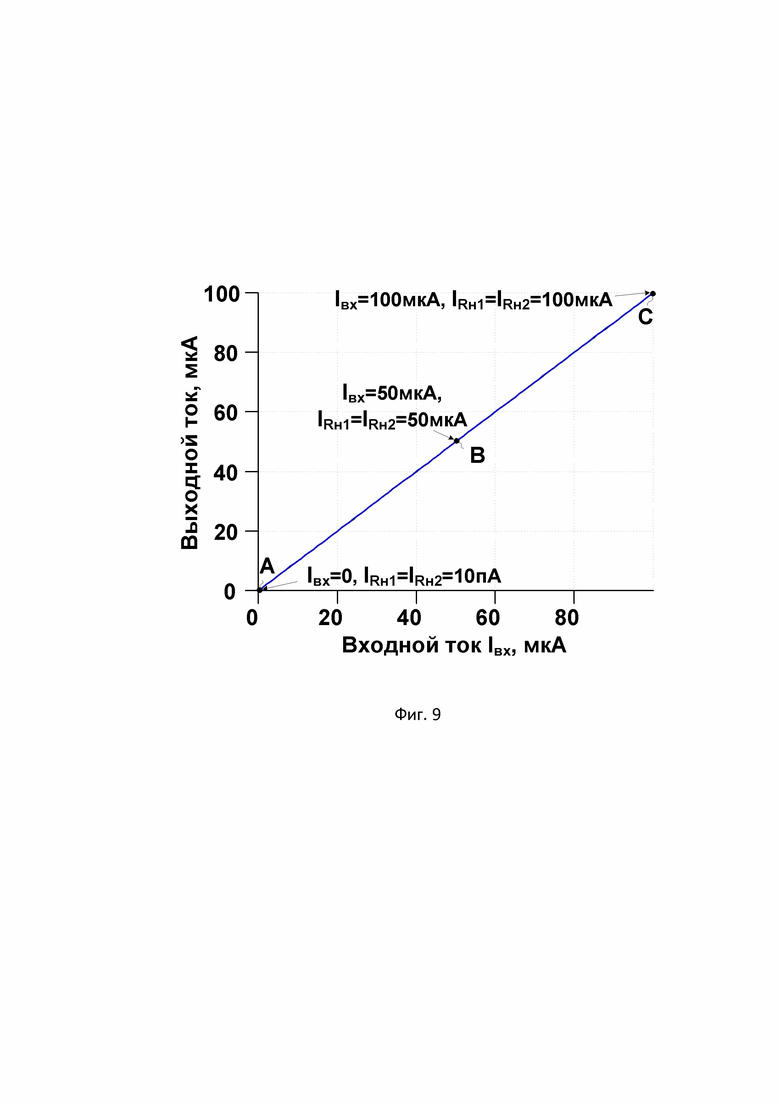

На фиг. 9 показаны зависимости выходных токов токового зеркала фиг. 8 для инвертирующего (2) и неинвертирующего (12) токовых выходов (фиг. 2) при температурах 27°С и -197°С для токов I1=100 мкА, Iвх=I2=0÷100 мкА.

Токовое зеркало фиг. 2 содержит вход 1 и инвертирующий выход 2 устройства, согласованные с первой 3 шиной источника питания, первый 4 входной полевой транзистор, сток которого связан со входом 1 устройства и соединен с затвором второго 5 входного полевого транзистора, первый 6 выходной полевой транзистор, сток которого подключен к инвертирующему выходу 2 устройства, второй 7 выходной полевой транзистор, источник опорного тока 8, вторую 9 шину источника питания. Исток второго 5 входного полевого транзистора соединен с первым 10 источником опорного напряжения, его сток соединен с затвором второго 7 выходного полевого транзистора и через источник опорного тока 8 связан со второй 9 шиной источника питания, исток второго 7 выходного полевого транзистора связан с истоком первого 4 входного полевого транзистора и истоком первого 6 выходного полевого транзистора, затвор первого 4 входного полевого транзистора связан с затвором первого 6 выходного полевого транзистора и подключен ко второму 11 источнику опорного напряжения, а сток второго 7 выходного полевого транзистора связан с дополнительным неинвертирующим токовым выходом 12 устройства, причем в качестве всех упомянутых выше полевых транзисторов токового зеркала используются полевые транзисторы с управляющим p-n-переходом JFET. На фиг. 2 двухполюсники 13 и 14 моделируют свойства нагрузки подключаемой к инвертирующему выходу 2 устройства и дополнительному неинвертирующему токовому выходу 12 устройства, для которого коэффициент передачи по току равен двум единицам.

Функциональная схема фиг. 3 соответствует конкретным схемотехническим решениям ТЗ (фиг. 2, фиг. 4, фиг. 5).

На фиг. 4, в соответствии с п. 3 формулы изобретения, в схему введен третий 15 JFET выходной полевой транзистор, затвор которого соединен с затвором первого 6 JFET выходного полевого транзистора, исток соединен с истоком первого 6 JFET выходного полевого транзистора, а сток соединен с инвертирующим выходом 2 устройства. В таком схемотехническом решении коэффициент передачи по току для дополнительного неинвертирующего токового выхода 12 устройства равен трем единицам, а для инвертирующего выхода 2 устройства - двум единицам. Кроме этого, на фиг. 4, в качестве первого 10 источника опорного напряжения используется напряжение на общей шине источников питания, а в качестве второго 11 источника опорного напряжения используется напряжение на второй 9 шине источника питания.

На фиг. 5, в соответствии с п. 4 формулы изобретения, в схему введен дополнительный 16 JFET полевой транзистор, сток которого связан со второй 9 шиной источника питания, затвор соединен с затвором второго 7 JFET выходного полевого транзистора, а исток подключен к объединенным истокам первого 4 JFET входного и первого 6 JFET выходного полевых транзисторов. Введение здесь дополнительных элементов обеспечивает единичные коэффициенты передачи по току как для дополнительного неинвертирующего токового выхода 12 устройства, так и для инвертирующего выхода 2 устройства - это значительно расширяет функциональные возможности предлагаемого ТЗ и позволяет создавать нетрадиционные аналоговые схемы на его основе. Известные ТЗ данным свойством не обладают.

Рассмотрим работу ТЗ с учетом результатов моделирования, представленных на фиг. 6- 9.

Предлагаемое ТЗ имеет устойчивый статический режим (фиг. 6) при температуре до минус 197°С.

Зависимости выходного тока ТЗ фиг. 6, представленные на фиг. 7 для разных температурных условий (27°С и -197°С) в широком диапазоне изменения входных токов Iвх=I2=0÷100 мкА показывают, что предлагаемое устройство обеспечивает высокую точность передачи тока на неинвертирующий выход (IRн2, коэффициент передачи - 3 единицы) и инвертирующий выход (IRн1, коэффициент передачи - 2 единицы).

Особенность схемы фиг. 8 состоит в том, что здесь коэффициент передачи по току строго равен единице (фиг. 9) как по инвертирующему (IRн1), так и по неинвертирующему (IRн2) токовым выходам, в широком диапазоне температур. Это позволяет создавать нетрадиционные схемотехнические решения на его основе для задач прецизионного усиления и фильтрации сигналов.

Следует также заметить, что по реализуемой точности передачи тока и численных значениях коэффициента усиления, который зависит от числа параллельно включенных элементарных транзисторов в структуре первого 6 и второго 7 составных JFET выходных полевых транзисторов (фиг. 4, фиг. 5), предлагаемые схемы ТЗ не имеют аналогов. Моделирование показывает, что данные качества сохраняются не только в диапазоне криогенных температур, но и при воздействии проникающей радиации.

Представленные на фиг. 9 зависимости выходных токов IRн1 и IRн2 от входного тока Iвх ТЗ фиг. 8 для разных температурных условий (27°С и -197°С), показывают, что заявляемое устройство имеет не только неинвертирующеий токовый выход (IRн2), а может также обеспечить инвертирующее преобразование входных сигналов относительно инвертирующего выхода 2. Это значительно расширяет функциональные возможности предлагаемого схемотехнического решения при его использовании в современной CJFet аналоговой схемотехнике.

Таким образом, заявляемо устройство имеет существенные преимущества в сравнении с аналогами.

Источники информации

1. Патент US №6.630.818, fig. 4, 2003 г.

2. Патент ЕР №2652872, fig. 2, 2015 г.

3. Патент US №7.869.285, fig. 1, 2011 г.

4. Патент US №7.312.651, 2007 г.

5. Патент RU №2544780, fig. 2, 2013 г.

6. Патент US №8.169.263, 2012 г.

7. Патент US №7.915.948, 2011 г.

8. Патент US №6.492.796, fig. 1, fig. 2, fig. 8, 2002 г.

9. Патент US №7.541.871, fig. 1, 2009 г.

10. Патент US №5.801.523, fig. 1, 1998 г.

11. Патент US №6.617.915, 2003 г.

12. Заявка на патент US №2007/0216484, fig. 15, 2007 г.

13. Патент US №6.639.452, fig. 1, 2003 г.

14. Патент US №5.515.010, 1996 г.

15. Заявка на патент US №2006/0232340, 2006 г.

16. Патент ЕР №1313211, fig. 3, 2001 г.

17. Патент US №6.842.050, fig. 3, 2005 г.

18. Патент US №6.980.054, fig. 7, 2005 г.

19. Авт. свид. SU 1529410, 1989 г.

20. Полезная модель 139042, 2014 г.

21. Токовые зеркала для проектирования КМОП аналоговых микросхем: основные модификации (ТЗ №1-№36) / Прокопенко Н.Н., Титов А.Е., Бутырлагин Н.В. // Библиотека схемотехнических решений. ИППМ РАН, 2019, С. 1-29. URL: http://www.ippm.ru/data/eljrnal/paper/J4.pdf (режим доступа свободный).

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕИНВЕРТИРУЮЩЕЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720554C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ УСИЛИТЕЛЬ ТОКА ДЛЯ ЗАДАЧ ПРОЕКТИРОВАНИЯ АКТИВНЫХ RC-ФИЛЬТРОВ | 2020 |

|

RU2727965C1 |

| КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2020 |

|

RU2736548C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ И РАДИАЦИОННО-СТОЙКИЙ КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2732950C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

Изобретение относится к области радиотехники. Технический результат заключается в создании как инвертирующего, так и неинвертирующего токового зеркала на комплементарных полевых транзисторах с управляющим p-n-переходом для работы при низких температурах, обеспечивающего для разных выходов инвертирующее и неинвертирующее преобразования входного токового сигнала с коэффициентом передачи по току больше единицы. Токовое зеркало содержит шину источника питания, полевые транзисторы, источник опорного напряжения, полевые транзисторы с управляющим p-n-переходом (JFET). 3 з.п. ф-лы, 9 ил.

1. Токовое зеркало для работы при низких температурах, содержащее вход (1) и инвертирующий выход (2) устройства, согласованные с первой (3) шиной источника питания, первый (4) входной полевой транзистор, сток которого связан со входом (1) устройства и соединен с затвором второго (5) входного полевого транзистора, первый (6) выходной полевой транзистор, сток которого подключен к инвертирующему выходу (2) устройства, второй (7) выходной полевой транзистор, источник опорного тока (8), вторую (9) шину источника питания, отличающееся тем, что исток второго (5) входного полевого транзистора соединен с первым (10) источником опорного напряжения, его сток соединен с затвором второго (7) выходного полевого транзистора и через источник опорного тока (8) связан со второй (9) шиной источника питания, исток второго (7) выходного полевого транзистора связан с истоком первого (4) входного полевого транзистора и истоком первого (6) выходного полевого транзистора, затвор первого (4) входного полевого транзистора связан с затвором первого (6) выходного полевого транзистора и подключен ко второму (11) источнику опорного напряжения, а сток второго (7) выходного полевого транзистора связан с дополнительным неинвертирующим токовым выходом (12) устройства, причем в качестве всех упомянутых выше полевых транзисторов токового зеркала используются полевые транзисторы с управляющим p-n-переходом (JFET).

2. Токовое зеркало для работы при низких температурах по п. 1, отличающееся тем, что в качестве первого (10) источника опорного напряжения используется напряжение на общей шине источников питания, а в качестве второго (11) источника опорного напряжения используется напряжение на второй (9) шине источника питания.

3. Токовое зеркало для работы при низких температурах по п. 2, отличающееся тем, что в схему введен третий (15) JFET выходной полевой транзистор, затвор которого соединен с затвором первого (6) JFET выходного полевого транзистора, исток соединен с истоком первого (6) JFET выходного полевого транзистора, а сток соединен с инвертирующим выходом (2) устройства.

4. Токовое зеркало для работы при низких температурах по п. 2, отличающееся тем, что в схему введен дополнительный (16) JFET полевой транзистор, сток которого связан со второй (9) шиной источника питания, затвор соединен с затвором второго (7) JFET выходного полевого транзистора, а исток подключен к объединенным истокам первого (4) JFET входного и первого (6) JFET выходного полевых транзисторов.

| US 6630818 B1, 07.10.2003 | |||

| ТОКОВОЕ ЗЕРКАЛО | 2008 |

|

RU2365969C1 |

| Повторитель тока | 1987 |

|

SU1529410A1 |

| US 7463013 B2, 09.12.2008. | |||

Авторы

Даты

2020-04-29—Публикация

2019-11-25—Подача