Изобретение относится к области радиотехники и может быть использовано в качестве функционального узла аналоговых микросхем (например, дифференциальных (ОУ) и мультидифференциальных операционных усилителях (МОУ), компараторах и т.п.) для задач усиления и фильтрации сигналов, в том числе в диапазоне низких температур.

Основой современных микроэлектронных операционных усилителей, стабилизаторов напряжения, компараторов и т.п. являются так называемые «токовые зеркала», обеспечивающие инверсию по фазе входного токового сигнала в широком диапазоне его изменения [1-21]. Качественные показатели практически всех современных аналоговых микросхем определяются статическими и динамическими параметрами токовых зеркал (ТЗ). Анализ существующих вариантов построения ТЗ представлен в [21]. Предполагаемое изобретения относится к данному подклассу устройств.

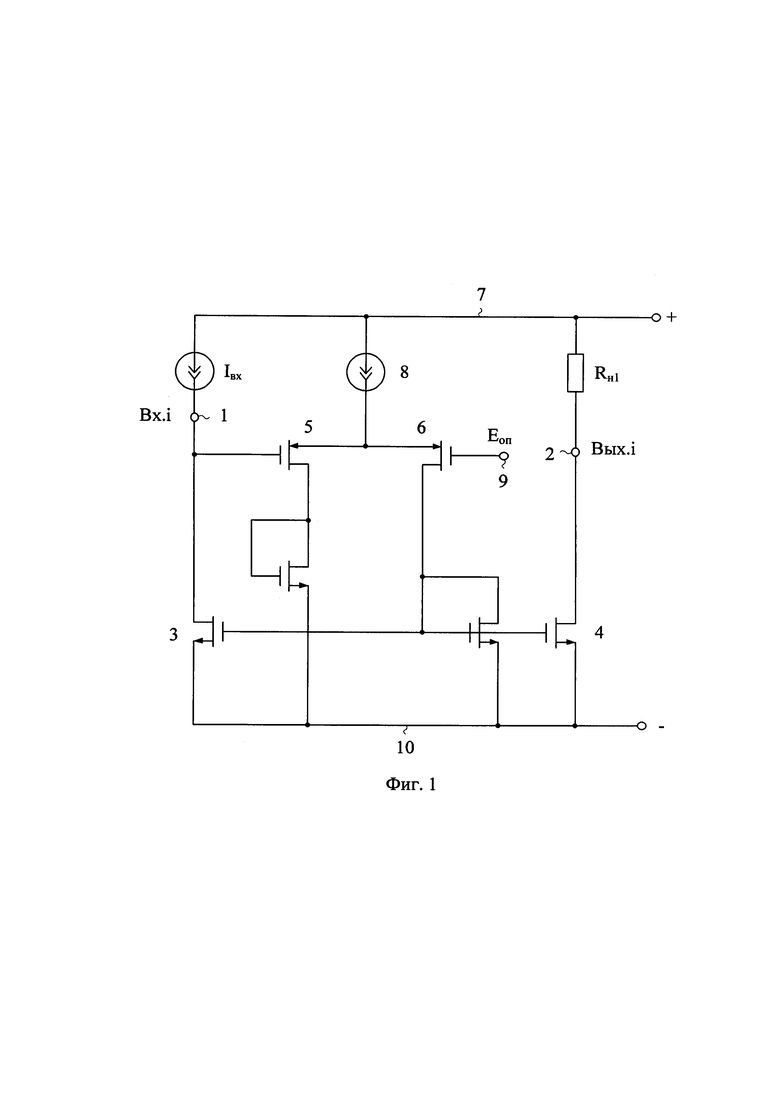

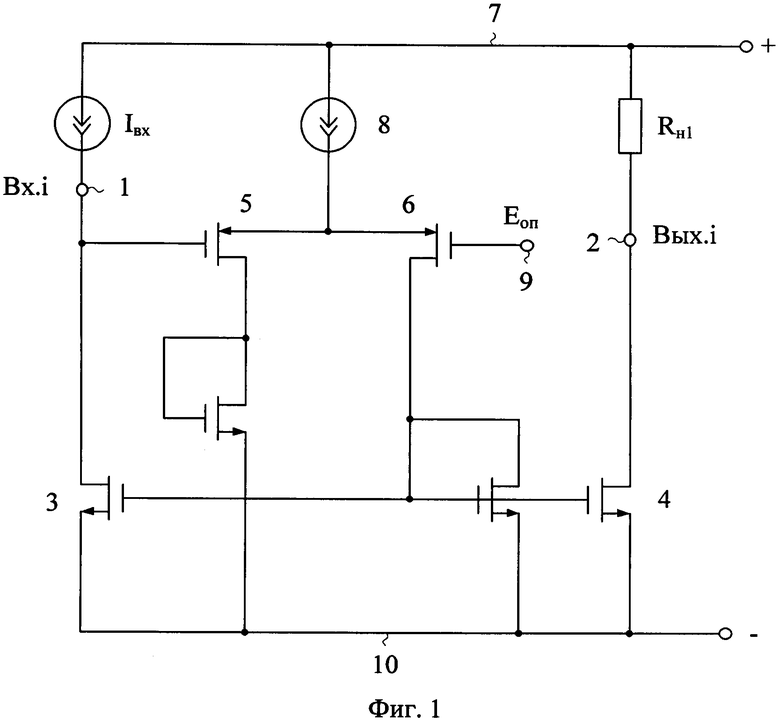

Ближайшим прототипом (фиг. 1) заявляемого устройства является токовое зеркало, описанное в патенте 2002 года US 6.492.796 (fig. 8) фирмы Analog Devices Inc., содержащее вход 1 и инвертирующий выход 2 устройства, первый 3 входной и первый 4 выходной полевые транзисторы, первый 5 и второй 6 вспомогательные полевые транзисторы, истоки которых объединены и подключены к первой 7 шине источника питания через первый 8 токостабилизирующий двухполюсник, причем затвор первого 5 вспомогательного полевого транзистора соединен со стоком первого 3 входного полевого транзистора и входом 1 устройства, затвор второго 6 вспомогательного полевого транзистора соединен с источником опорного напряжения 9, а сток первого 4 выходного полевого транзистора связан с инвертирующим выходом 2 устройства, вторую 10 шину источника питания.

Существенный недостаток известного токового зеркала состоит в том, что оно оказывается неработоспособным при реализации на JFet полевых транзисторах, обеспечивающих экстремально малый уровень шумов, высокую радиационную стойкость и стабильную работу аналоговых микросхем в диапазоне криогенных температур. Кроме этого известные ТЗ а также имеет только инвертирующий токовый выход.

Основная задача предполагаемого изобретения состоит в создании работоспособного в диапазоне низких температур и при воздействии потока нейтронов неинвертирующего токового зеркала на комплементарных полевых транзисторах с управляющим pn-переходом, обеспечивающего неинвертирующие преобразования входного токового сигнала с коэффициентом передачи по току больше единицы.

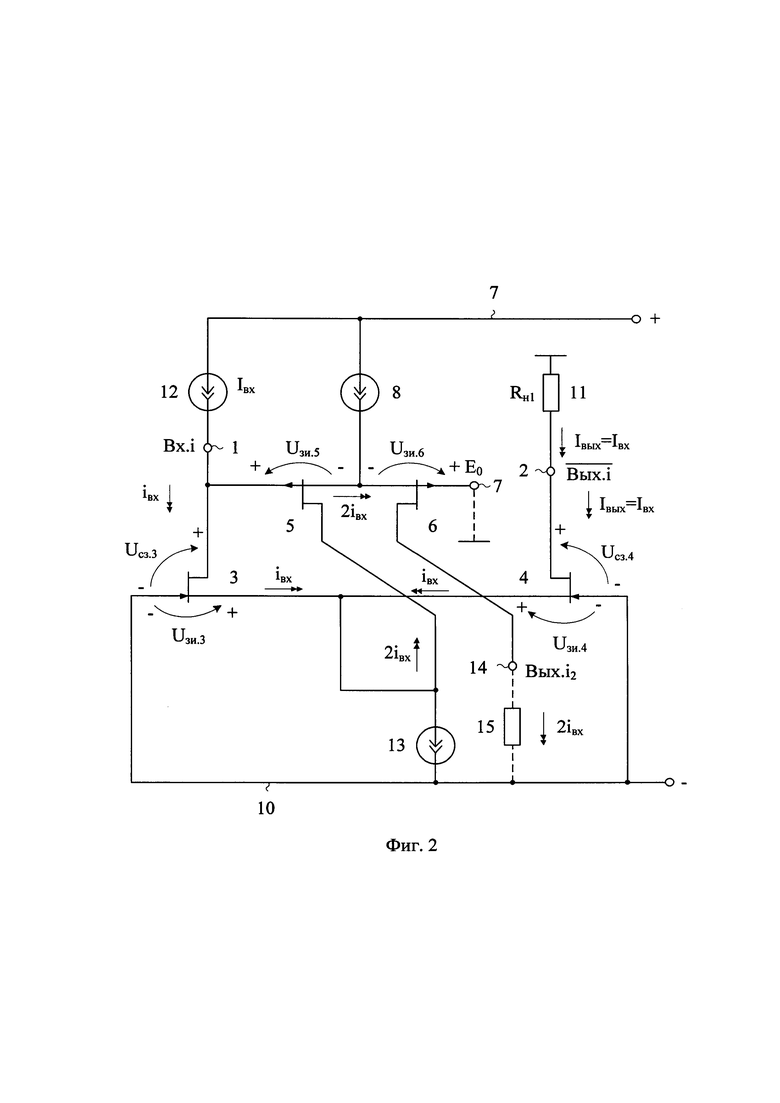

Поставленная задача решается тем, что в токовом зеркале фиг. 1, содержащем вход 1 и инвертирующий выход 2 устройства, первый 3 входной и первый 4 выходной полевые транзисторы, первый 5 и второй 6 вспомогательные полевые транзисторы, истоки которых объединены и подключены к первой 7 шине источника питания через первый 8 токостабилизирующий двухполюсник, причем затвор первого 5 вспомогательного полевого транзистора соединен со стоком первого 3 входного полевого транзистора и входом 1 устройства, затвор второго 6 вспомогательного полевого транзистора соединен с источником опорного напряжения 9, а сток первого 4 выходного полевого транзистора связан с инвертирующим выходом 2 устройства, вторую 10 шину источника питания, предусмотрены новые элементы и связи - качестве первого 3 входного и первого 4 выходного полевых транзисторов, а также первого 5 и второго 6 вспомогательных полевых транзисторов используются полевые транзисторы с управляющим pn-переходом JFET, сток первого 5 JFET вспомогательного полевого транзистора соединен со второй 10 шиной источника питания через второй 13 источник опорного тока и связан с объединенными истоками первого 3 JFET входного и первого 4 JFET выходного полевых транзисторов, затворы первого 3 JFET входного и первого 4 JFET выходного полевых транзисторов подключены ко второй 10 шине источника питания, сток второго 6 JFET вспомогательного полевого транзистора соединен с первым 14 дополнительным неинвертирующим выходом устройства.

На чертеже фиг. 1 представлена токовое зеркало прототип US 6.492.796, fig. 8, 2002 г., а на чертеже фиг. 2 приведена схема заявляемого CJFet токового зеркала в соответствии с п. 1 формулы изобретения.

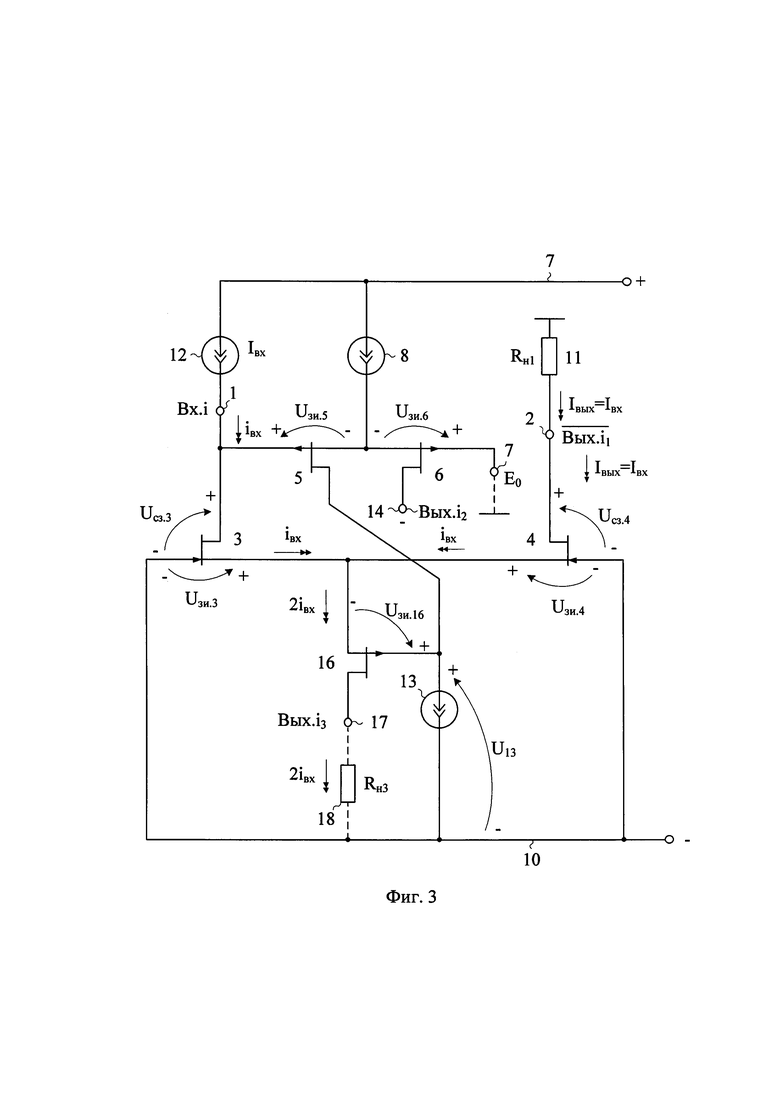

На чертеже фиг. 3 показана схема заявляемого устройства в соответствии с п. 2 формулы изобретения.

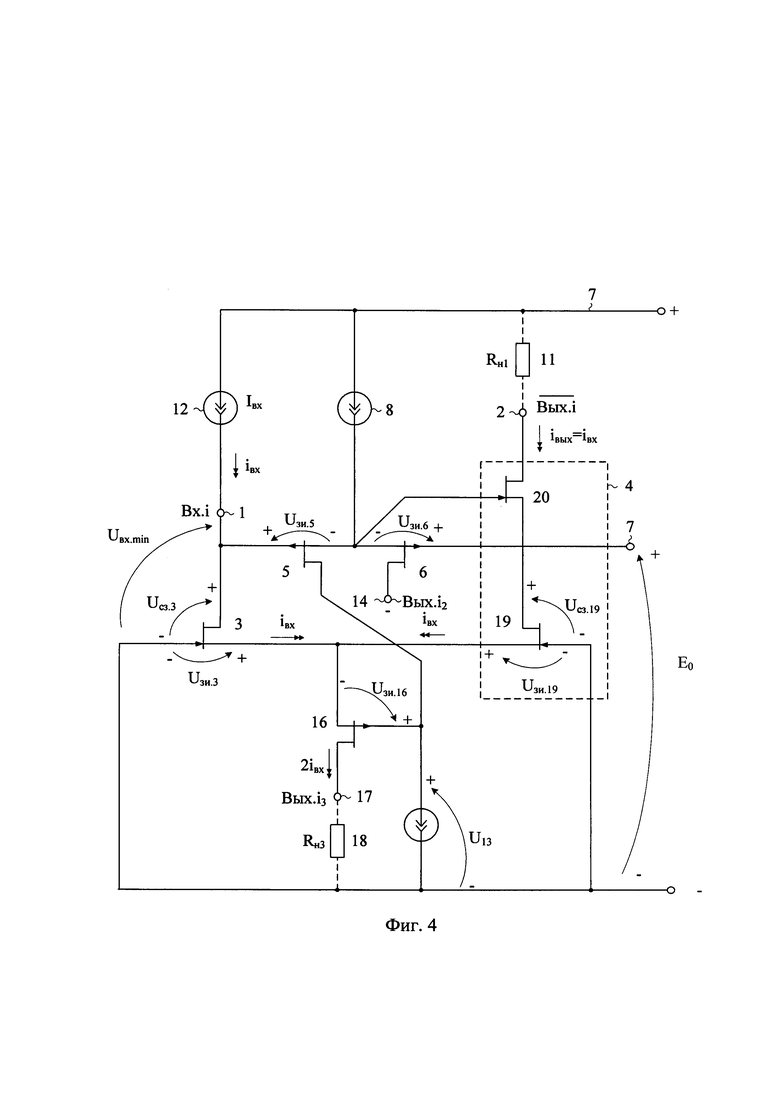

На чертеже фиг. 4 приведена схема заявляемого CJFet токового зеркала в соответствии с п. 3 формулы изобретения.

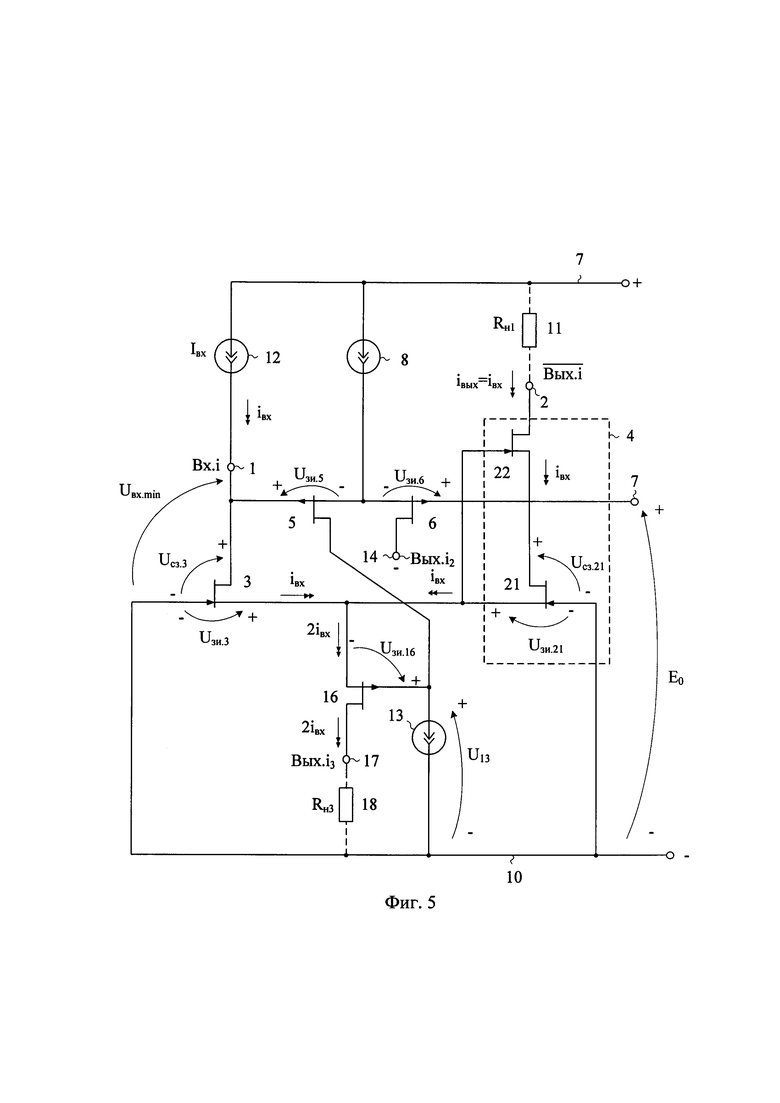

На чертеже фиг. 5 представлена заявляемое CJFet токовое зеркало с повышенным выходным сопротивлением в соответствии с п. 4 формулы изобретения.

На чертеже фиг. 6 показана схема CJFet токового зеркала с повышенным выходным сопротивлением в соответствии с п. 5 формулы изобретения.

На чертеже фиг. 7 показан статический режим токового зеркала фиг. 3 при температуре -197°С в среде среда LTSpiceXVII на комплементарных полевых транзисторах ОАО «Интеграл» (г. Минск) при токах Iвх=50 мкА, I1=200 мкA, I2=100 мкА.

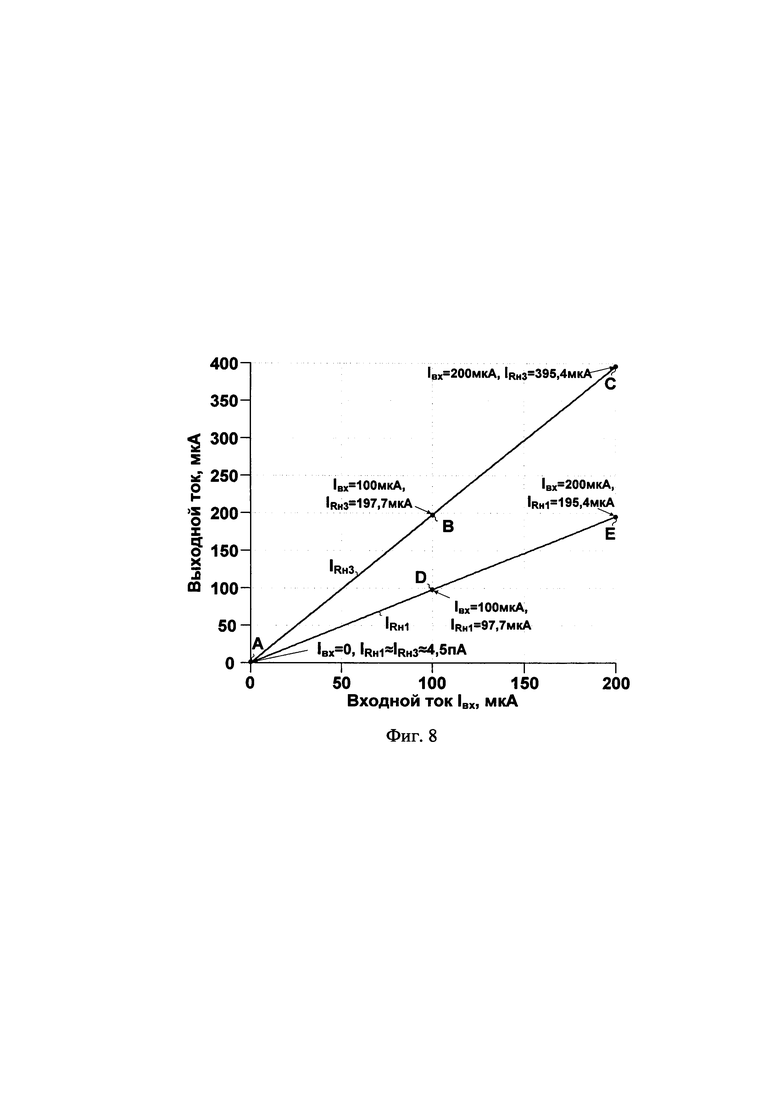

На чертеже фиг. 8 приведены зависимости выходных токов IRн1 (а) и IRн2 (б) токового зеркала фиг. 7 для температуры 27°С при разных входных токах Iвх=0÷200 мкА.

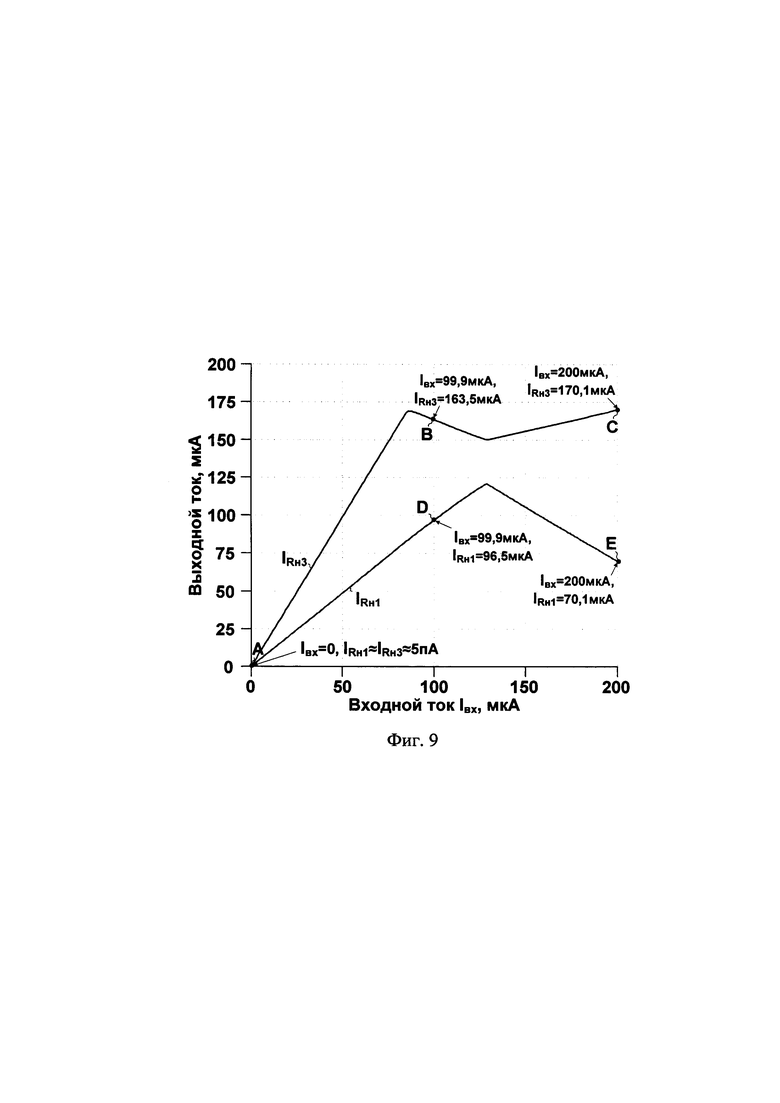

На чертеже фиг. 9 представлены зависимости выходных токов IRн1 (а) и IRн2 (б) токового зеркала фиг. 7 для температуры -197°С при разных входных токах Iвх=0÷200 мкА.

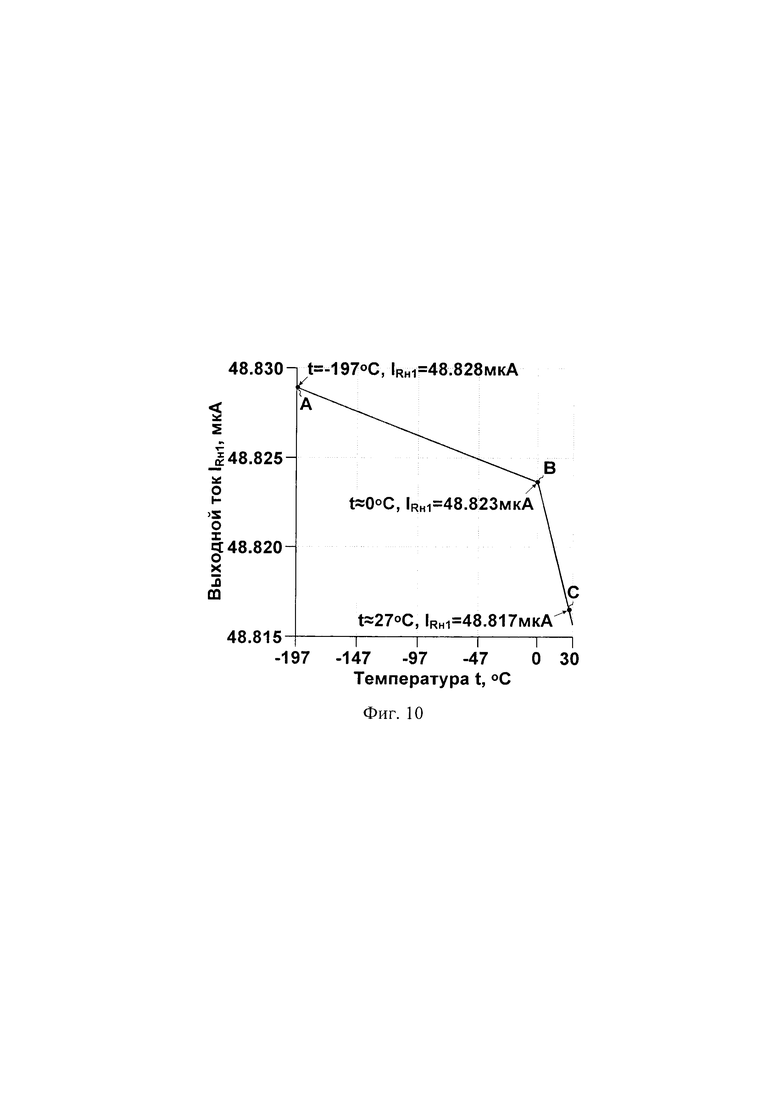

На чертеже фиг. 10 показаны зависимость выходного тока IRн1 ТЗ фиг. 7 в диапазоне температур от - 197°С до 30°С.

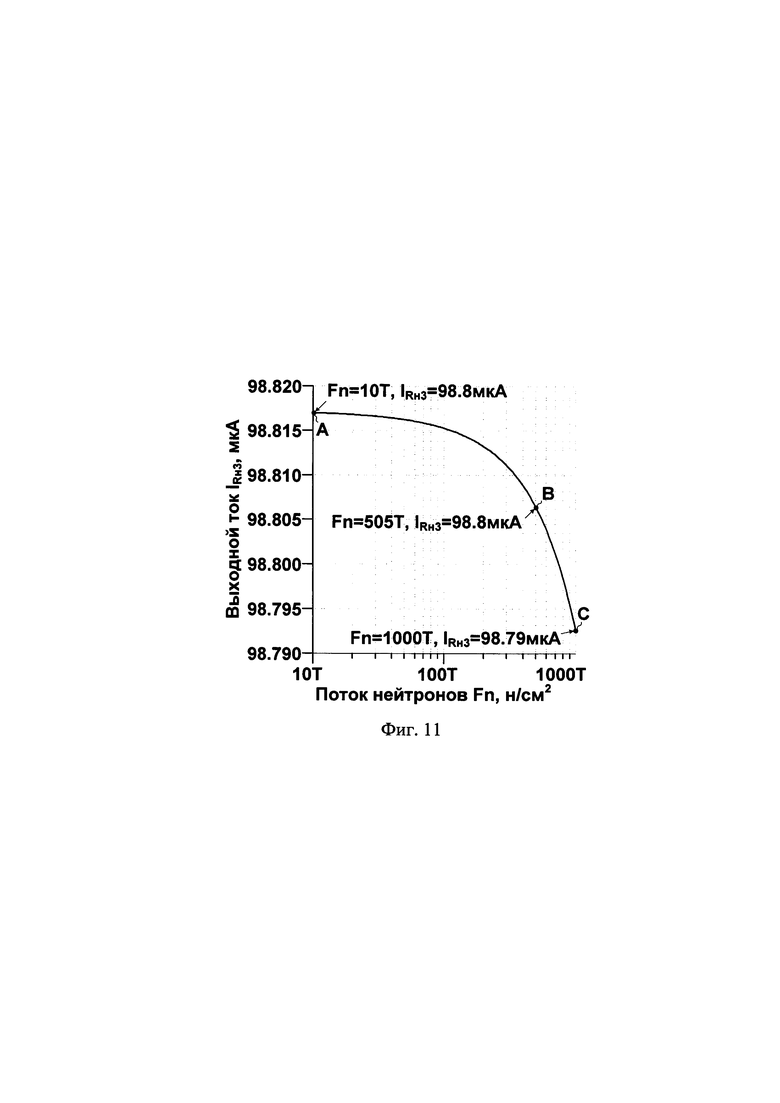

На чертеже фиг. 11 приведены зависимость выходного тока IRн2 ТЗ фиг. 7 в диапазоне потока нейтронов от 1е13 н/см2 до 1е15 н/см2.

Многофункциональное токовое зеркало на комплементарных полевых транзисторах с управляющим pn-переходом для работы при низких температурах фиг. 2 содержит вход 1 и инвертирующий выход 2 устройства, первый 3 входной и первый 4 выходной полевые транзисторы, первый 5 и второй 6 вспомогательные полевые транзисторы, истоки которых объединены и подключены к первой 7 шине источника питания через первый 8 токостабилизирующий двухполюсник, причем затвор первого 5 вспомогательного полевого транзистора соединен со стоком первого 3 входного полевого транзистора и входом 1 устройства, затвор второго 6 вспомогательного полевого транзистора соединен с источником опорного напряжения 9, а сток первого 4 выходного полевого транзистора связан с инвертирующим выходом 2 устройства, вторую 10 шину источника питания. В качестве первого 3 входного и первого 4 выходного полевых транзисторов, а также первого 5 и второго 6 вспомогательных полевых транзисторов используются полевые транзисторы с управляющим pn-переходом JFET, сток первого 5 JFET вспомогательного полевого транзистора соединен со второй 10 шиной источника питания через второй 13 источник опорного тока и связан с объединенными истоками первого 3 JFET входного и первого 4 JFET выходного полевых транзисторов, затворы первого 3 JFET входного и первого 4 JFET выходного полевых транзисторов подключены ко второй 10 шине источника питания, сток второго 6 JFET вспомогательного полевого транзистора соединен с первым 14 дополнительным неинвертирующим выходом устройства. В схеме фиг. 2 двухполюсник 12 моделирует входной ток ТЗ, а двухполюсники 11 и 15 свойства нагрузки, подключаемой к инвертирующему выходу 2 устройства и первому 14 дополнительному неинвертирующему выхому устройства.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, сток первого 5 JFET вспомогательного полевого транзистора связан с объединенными истоками первого 3 JFET входного и первого 4 JFET выходного полевых транзисторов через дополнительный истоковый повторитель напряжения, выполненный на дополнительном JFET полевом транзисторе 16, затвор которого соединен со стоком первого 5 JFET вспомогательного полевого транзистора, исток подключен к объединенным истокам первого 3 JFET входного и второго 6 JFET вспомогательного полевых транзисторов, а сток связан со вторым 17 дополнительным неинвертирующим выходом устройства, согласованным со второй 10 шиной источника питания. Здесь и далее двухполюсник 18 моделирует свойства нагрузки подключаемой ко второму 17 дополнительному неинвертирующему выходу устройства.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, первый 4 JFET выходной полевой транзистор выполнен по составной каскодной схеме на первом 19 JFET и втором 20 JFET дополнительных полевых транзисторах, причем затвор второго 20 JFET дополнительного полевого транзистора подключен к объединенными истоками первого 5 JFET и второго 6 JFET вспомогательного полевых транзисторов, а сток связан с инвертирующим выходом 2 устройства.

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, первый 4 JFET выходной полевой транзистор выполнен по составной каскодной схеме на третьем 21 JFET и четвертом 22 JFET дополнительных полевых транзисторах, причем затвор четвертого 22 JFET дополнительного полевого транзистора соединен с истокам первого 3 JFET входного полевого транзистора, а сток связан с инвертирующим выходом 2 устройства.

На чертеже фиг. 6, в соответствии с п. 5 формулы изобретения, первый 4 JFET выходной полевой транзистор выполнен по классической составной каскодной схеме на пятом 23 JFET и шестом 24 JFET дополнительных полевых транзисторах, причем затвор шестого 24 JFET дополнительного полевого транзистора соединен с объединенным истокам первого 5 JFET и второго 6 JFET вспомогательных полевых транзисторов, а сток связан с инвертирующим выходом 2 устройства.

Рассмотрим работу заявляемого ТЗ с учетом результатов его моделирования, представленных на чертежах фиг. 7 - фиг. 11.

Предлагаемое ТЗ имеет устойчивый статических режим (фиг. 7) при температуре до минус 197°С и воздействия потока нейтронов до 1е15 н/см2.

Зависимости выходного тока ТЗ фиг. 7, представленные на чертеже фиг. 8 и фиг. 9 для разных температурных условий (27°С и -197°С) в широком диапазоне изменения входных токов Iвх=0÷200 мкА показывают, что предлагаемое устройство обеспечивает высокую точность передачи тока на инвертирующий и неинвертирующий выходы.

Особенность схемы фиг. 7 состоит в том, что здесь коэффициент передачи по току строго равен единице по инвертирующему (IRн1), и двум единицам по неинвертирующему (IRн2) токовым выходам в широком диапазоне температур (фиг. 9, фиг. 10). Это позволяет создавать нетрадиционные схемотехнические решения на его основе для задач прецизионного усиления и фильтрации сигналов.

В схемах фиг. 4, фиг. 5 и фиг. 6 реализуются повышенные выходные сопротивления по инвертирующему выходу 2 устройства.

Компьютерное моделирование, представленное на чертеже фиг. 11 показывает, что данные качества сохраняются не только в диапазоне криогенных температур, но и при воздействии проникающей радиации (поток нейтронов Fn=1e13 н/см2 до 1е15 н/см2). Это значительно расширяет функциональные возможности предлагаемого схемотехнического решения при его использовании в экстремальной электронике.

Таким образом, заявляемо устройство имеет существенные преимущества в сравнении с аналогами.

Библиографический СПИСОК

1. Патент US №6.492.796, fig. 1, fig. 2, fig. 8, 2002 г.

2. Патент US №6.630.818, fig. 4, 2003 г.

3. Патент ЕР №2652872, fig. 2, 2015 г.

4. Патент US №7.869.285, fig. 1, 2011 г.

5. Патент US №7.312.651, 2007 г.

6. Патент RU №2544780, fig. 2, 2013 г.

7. Патент US №8.169.263, 2012 г.

8. Патент US №7.915.948, 2011 г.

9. Патент US №7.541.871, fig. 1, 2009 г.

10. Патент US №5.801.523, fig. 1, 1998 г.

11. Патент US №6.617.915, 2003 г.

12. Заявка на патент US №2007/0216484, fig. 15, 2007 г.

13. Патент US №6.639.452, fig. 1, 2003 г.

14. Патент US №5.515.010, 1996 г.

15. Заявка на патент US №2006/0232340, 2006 г..

16. Патент ЕР №1313211, fig. 3, 2001 г.

17. Патент US №6.842.050, fig. 3, 2005 г.

18. Патент US №6.980.054, fig. 7, 2005 г.

19. Авт. свид. SU 1529410, 1989 г.

20. Полезная модель 139042, 2014 г.

21. Токовые зеркала для проектирования КМОП аналоговых микросхем: основные модификации (ТЗ №1-№36) / Прокопенко Н.Н., Титов А.Е., Бутырлагин Н.В. // Библиотека схемотехнических решений. ИППМ РАН, 2019, С. 1-29. URL: http://www.ippm.ru/data/eljrnal/рареr/J4.pdf (режим доступа свободный).

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕИНВЕРТИРУЮЩЕЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720554C1 |

| ТОКОВОЕ ЗЕРКАЛО ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720365C1 |

| КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2020 |

|

RU2736548C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ УСИЛИТЕЛЬ ТОКА ДЛЯ ЗАДАЧ ПРОЕКТИРОВАНИЯ АКТИВНЫХ RC-ФИЛЬТРОВ | 2020 |

|

RU2727965C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ И РАДИАЦИОННО-СТОЙКИЙ КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2732950C1 |

| РАДИАЦИОННО-СТОЙКИЙ И НИЗКОТЕМПЕРАТУРНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2741056C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| СОСТАВНОЙ ТРАНЗИСТОР НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2710846C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

Изобретение относится к области радиотехники и может быть использовано в качестве функционального узла аналоговых микросхем (например, дифференциальных (ОУ) и мультидифференциальных операционных усилителях (МОУ), компараторах и т.п.) для задач усиления и фильтрации сигналов, в том числе в диапазоне низких температур и при воздействии проникающей радиации. Технический результат заключается в создании работоспособного в диапазоне низких температур неинвертирующего токового зеркала на комплементарных полевых транзисторах с управляющим pn-переходом, обеспечивающего неинвертирующие преобразования входного токового сигнала с коэффициентом передачи по току больше единицы. Многофункциональное токовое зеркало содержит полевые транзисторы, вспомогательные полевые транзисторы, токостабилизирующий двухполюcник, полевые транзисторы с управляющим pn-переходом (JFET). 4 з.п. ф-лы, 1 ил.

1. Многофункциональное токовое зеркало на комплементарных полевых транзисторах с управляющим pn-переходом для работы при низких температурах, содержащее вход (1) и инвертирующий выход (2) устройства, первый (3) входной и первый (4) выходной полевые транзисторы, первый (5) и второй (6) вспомогательные полевые транзисторы, истоки которых объединены и подключены к первой (7) шине источника питания через первый (8) токостабилизирующий двухполюcник, причем затвор первого (5) вспомогательного полевого транзистора соединен со стоком первого (3) входного полевого транзистора и входом (1) устройства, затвор второго (6) вспомогательного полевого транзистора соединен с источником опорного напряжения (9), а сток первого (4) выходного полевого транзистора связан с инвертирующим выходом (2) устройства, вторую (10) шину источника питания, отличающееся тем, что в качестве первого (3) входного и первого (4) выходного полевых транзисторов, а также первого (5) и второго (6) вспомогательных полевых транзисторов используются полевые транзисторы с управляющим pn-переходом (JFET), сток первого (5) JFET вспомогательного полевого транзистора соединен со второй (10) шиной источника питания через второй (13) источник опорного тока и связан с объединенными истоками первого (3) JFET входного и первого (4) JFET выходного полевых транзисторов, затворы первого (3) JFET входного и первого (4) JFET выходного полевых транзисторов подключены ко второй (10) шине источника питания, сток второго (6) JFET вспомогательного полевого транзистора соединен с первым (14) дополнительным неинвертирующим выходом устройства.

2. Многофункциональное токовое зеркало по п.1, отличающееся тем, что сток первого (5) JFET вспомогательного полевого транзистора связан с объединенными истоками первого (3) JFET входного и первого (4) JFET выходного полевых транзисторов через дополнительный истоковый повторитель напряжения, выполненный на дополнительном JFET полевом транзисторе (16), затвор которого соединен со стоком первого (5) JFET вспомогательного полевого транзистора, исток подключен к объединенным истокам первого (3) JFET входного и второго (6) JFET вспомогательного полевых транзисторов, а сток связан со вторым (17) дополнительным неинвертирующим выходом устройства, согласованным со второй (10) шиной источника питания.

3. Многофункциональное токовое зеркало по п.2, отличающееся тем, что первый (4) JFET выходной полевой транзистор выполнен по составной каскодной схеме на первом (19) JFET и втором (20) JFET дополнительных полевых транзисторах, причем затвор второго (20) JFET дополнительного полевого транзистора подключен к объединенным истокам первого (5) JFET и второго (6) JFET вспомогательного полевых транзисторов, а сток связан с инвертирующим выходом (2) устройства.

4. Многофункциональное токовое зеркало по п.3, отличающееся тем, что первый (4) JFET выходной полевой транзистор выполнен по составной каскодной схеме на третьем (21) JFET и четвертом (22) JFET дополнительных полевых транзисторах, причем затвор четвертого (22) JFET дополнительного полевого транзистора соединен с истоком первого (3) JFET входного полевого транзистора, а сток связан с инвертирующим выходом (2) устройства.

5. Многофункциональное токовое зеркало по п.1, отличающееся тем, что первый (4) JFET выходной полевой транзистор выполнен по классической составной каскодной схеме на пятом (23) JFET и шестом (24) JFET дополнительных полевых транзисторах, причем затвор шестого (24) JFET дополнительного полевого транзистора соединен с объединенными истоками первого (5) JFET и второго (6) JFET вспомогательных полевых транзисторов, а сток связан с инвертирующим выходом (2) устройства.

| US 6492796 B1, 10.12.2002 | |||

| ТОКОВОЕ ЗЕРКАЛО | 2008 |

|

RU2365969C1 |

| Повторитель тока | 1987 |

|

SU1529410A1 |

| US 7463013 B2, 09.12.2008. | |||

Авторы

Даты

2020-05-12—Публикация

2019-11-22—Подача