Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

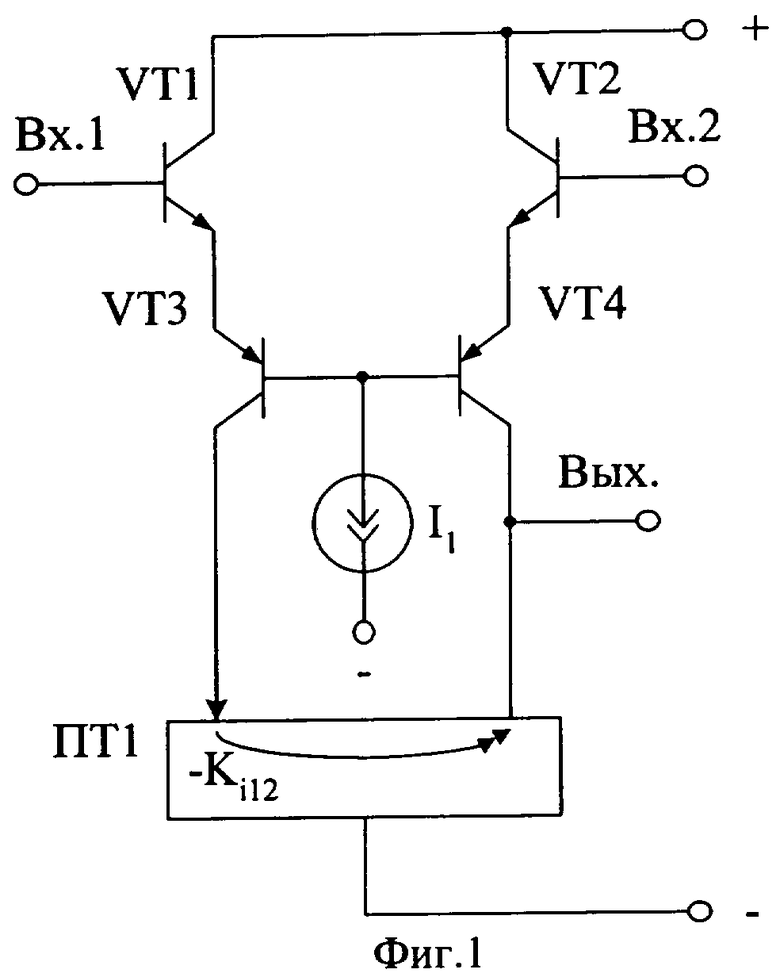

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах с так называемой «архитектурой входного каскада операционного усилителя μА741» [1-52] (фиг.1). На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом, стали основным усилительным элементом многих микросхем для аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

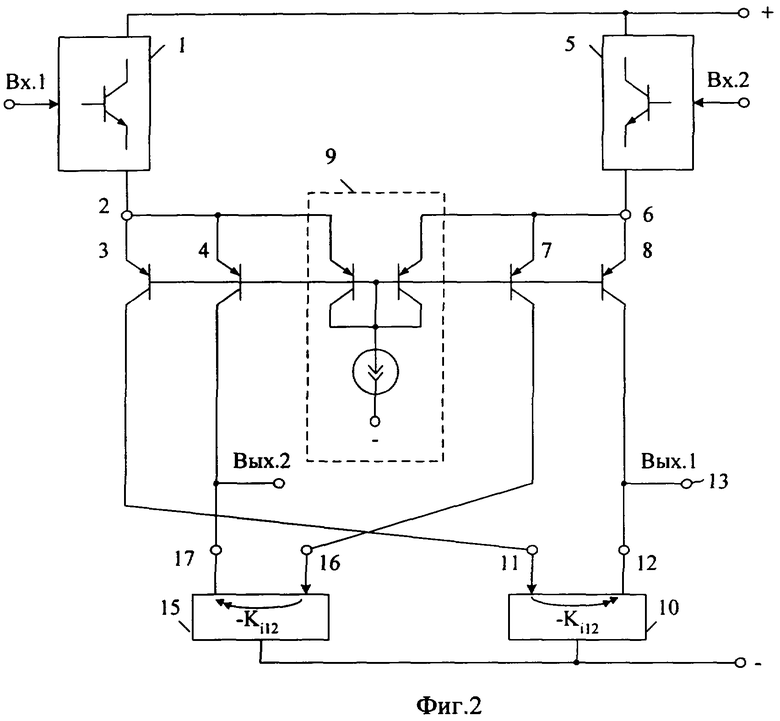

Ближайшим прототипом (фиг.2) заявляемого устройства является дифференциальный усилитель, описанный в патенте США № 4389579, содержащий первый входной каскад 1, выход 2 которого соединен с объединенными эмиттерами первого 3 и второго 4 выходных транзисторов, второй входной каскад 5, выход которого 6 соединен с объединенными эмиттерами третьего 7 и четвертого 8 выходных транзисторов, цепь установления 9 статического режима первого 3, второго 4, третьего 7 и четвертого 8 выходных транзисторов, связанная с их базами, первое токовое зеркало 10, вход 11 которого соединен с коллектором первого выходного транзистора 3, а выход 12 связан с коллектором четвертого выходного транзистора 8 и выходом 13 дифференциального усилителя, второе токовое зеркало 15, вход 16 которого соединен с коллектором третьего выходного транзистора 7, а выход 17 связан с коллектором второго выходного транзистора 4.

Существенный недостаток известного ДУ состоит в том, что он имеет повышенное значение напряжения смещения нуля (Uсм).

Основная цель предлагаемого изобретения состоит в уменьшении напряжения смещения нуля.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый входной каскад 1, выход 2 которого соединен с объединенными эмиттерами первого 3 и второго 4 выходных транзисторов, второй входной каскад 5, выход которого 6 соединен с объединенными эмиттерами третьего 7 и четвертого 8 выходных транзисторов, цепь установления 9 статического режима первого 3, второго 4, третьего 7 и четвертого 8 выходных транзисторов, связанная с их базами, первое токовое зеркало 10, вход 11 которого соединен с коллектором первого выходного транзистора 3, а выход 12 связан с коллектором четвертого выходного транзистора 8 и выходом 13 дифференциального усилителя, второе токовое зеркало 15, вход 16 которого соединен с коллектором третьего выходного транзистора 7, а выход 17 связан с коллектором второго выходного транзистора 4, предусмотрены новые связи - вход 11 первого токового зеркала 10 соединен с выходом 17 второго токового зеркала 15.

На фиг.1 показана обобщенная архитектура дифференциального усилителя рассматриваемого класса, содержащего n-p-n и p-n-p транзисторы, которая имеет более 50 практических реализаций [1-52].

На фиг.2 представлен дифференциальный усилитель-прототип.

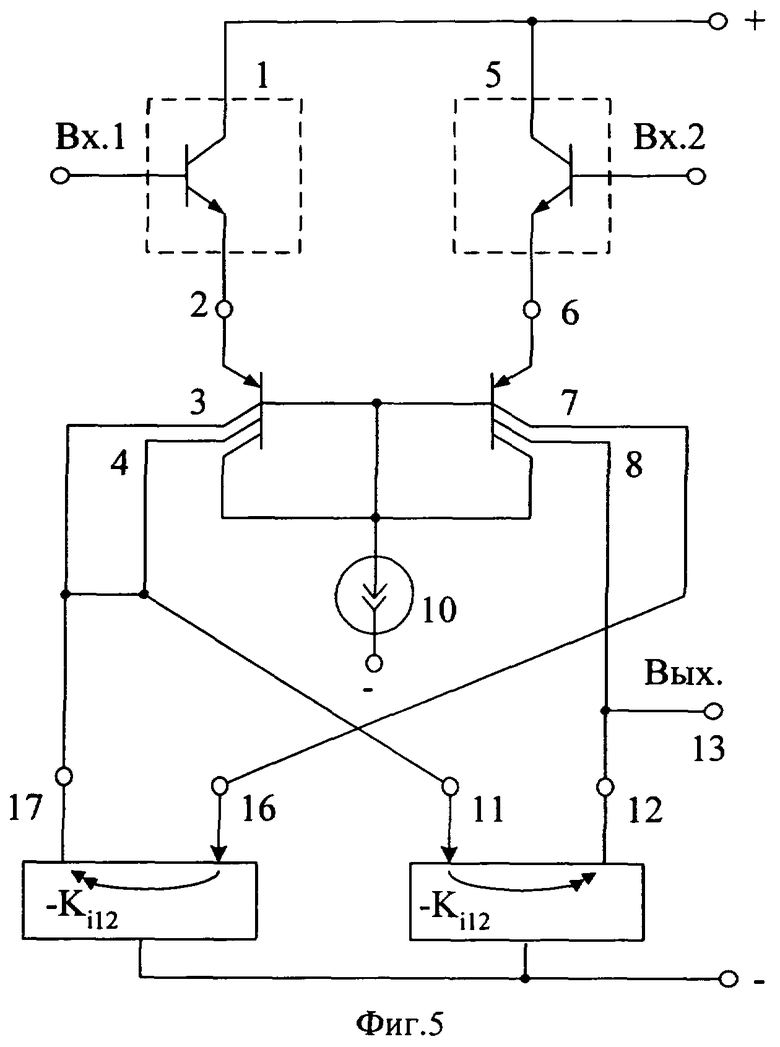

На фиг.3 показан заявляемый дифференциальный усилитель, у которого цепь установления статического режима 9 выполнена в частном случае по схеме без обратной связи.

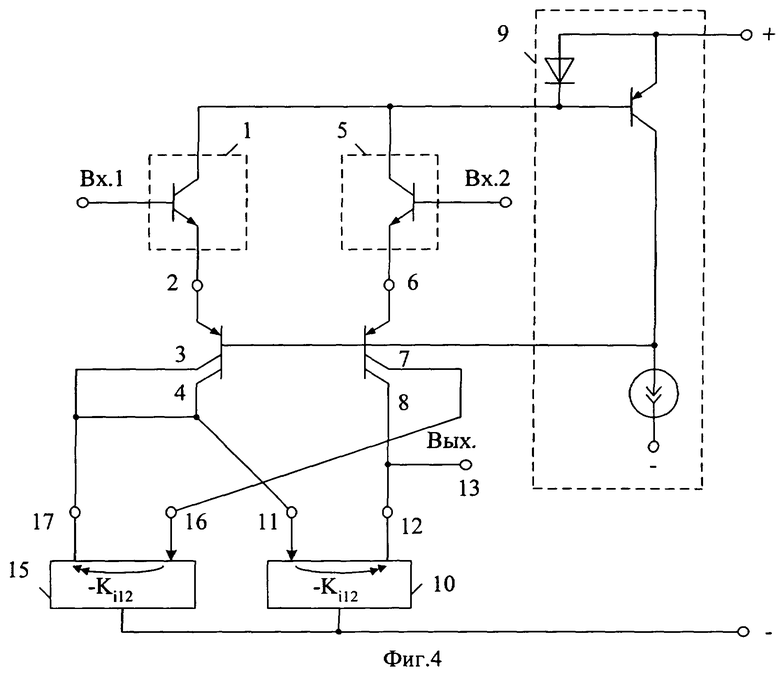

На фиг.4 показан заявляемый дифференциальный усилитель, у которого цепь установления статического режима 9 выполнена по схеме с отрицательной обратной связью по синфазному сигналу.

Дифференциальный усилитель фиг.5 является частным примером построения дифференциального усилителя фиг.3.

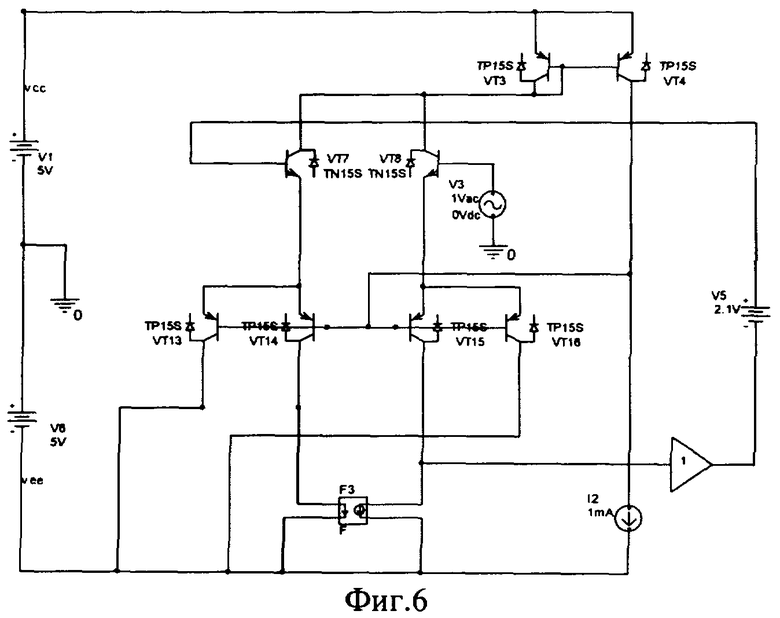

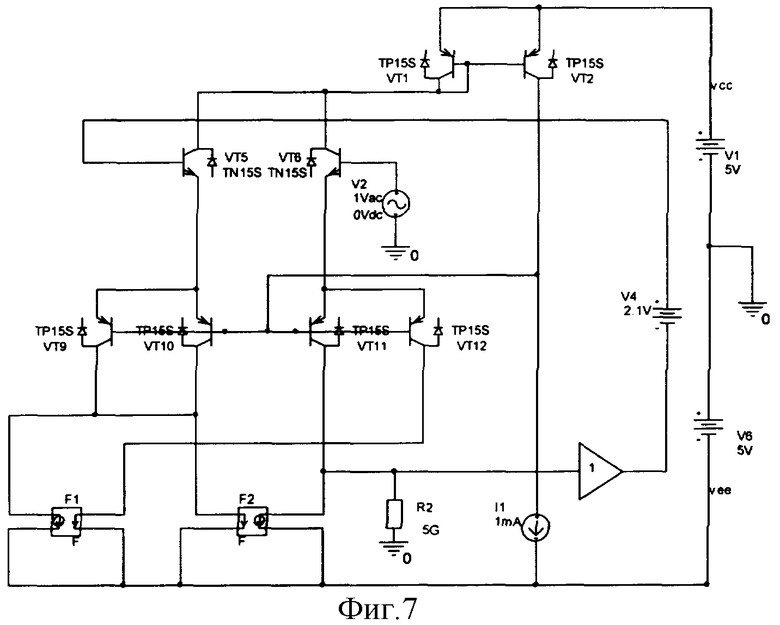

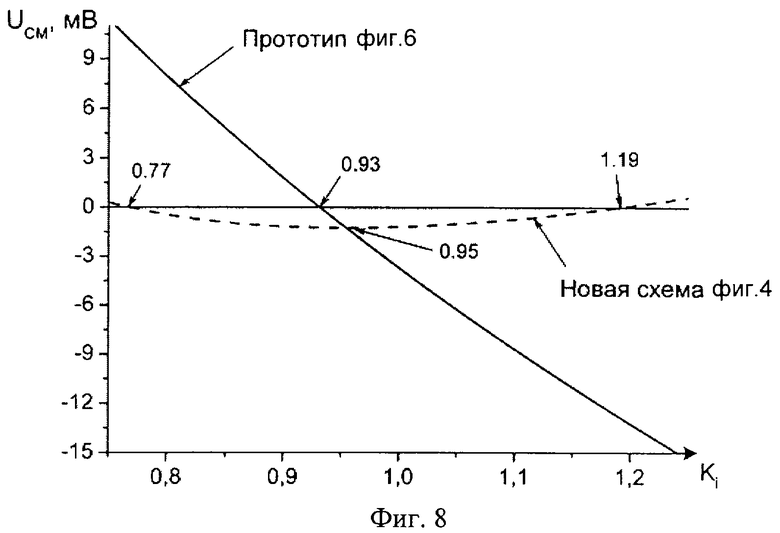

На фиг.6 и фиг.7 показаны схемы известного (фиг.6) и заявляемого (фиг.7) устройств в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар", а на фиг.8 - результаты расчета Uсм схемы фиг.6 и заявляемого ДУ фиг.7.

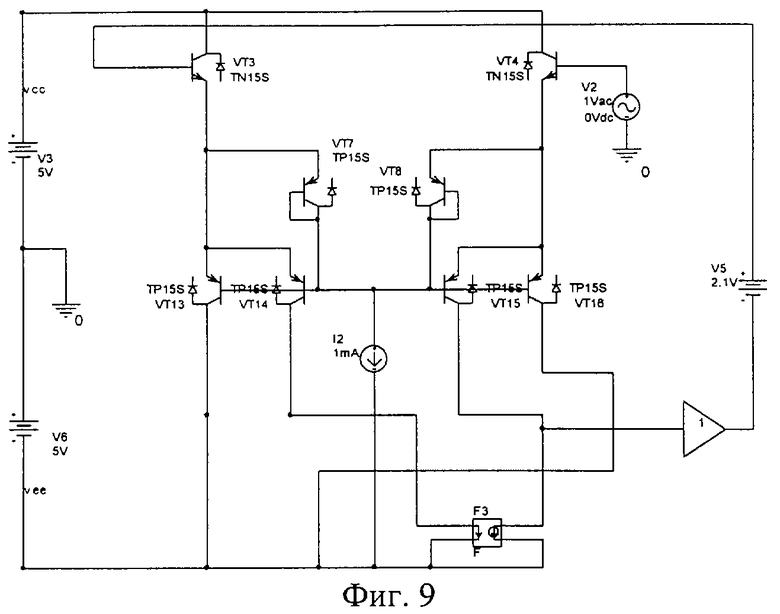

На фиг.9 представлена схема известного ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», которая сравнивалась по Uсм со схемой фиг.3. Результаты этого сравнительного расчета Uсм показаны на фиг.10.

Дифференциальный усилитель фиг.3 содержит первый входной каскад 1, выход 2 которого соединен с объединенными эмиттерами первого 3 и второго 4 выходных транзисторов, второй входной каскад 5, выход которого 6 соединен с объединенными эмиттерами третьего 7 и четвертого 8 выходных транзисторов, цепь установления 9 статического режима первого 3, второго 4, третьего 7 и четвертого 8 выходных транзисторов, связанная с их базами, первое токовое зеркало 10, вход 11 которого соединен с коллектором первого выходного транзистора 3, а выход 12 связан с коллектором четвертого выходного транзистора 8 и выходом 13 дифференциального усилителя, второе токовое зеркало 15, вход 16 которого соединен с коллектором третьего выходного транзистора 7, а выход 17 связан с коллектором второго выходного транзистора 4. Вход 11 первого токового зеркала 10 соединен с выходом 17 второго токового зеркала 15.

Рассмотрим работу заявляемого устройства фиг.3.

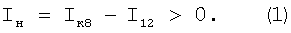

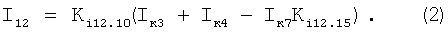

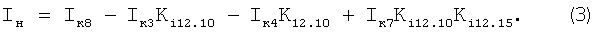

В статическом режиме при нулевом напряжении между входами Вх.1 и Вх.2 в цепи нагрузки Rн протекает статический ток ошибки Iн, обусловленный разностью

Составляющая тока I12 зависит от статических коллекторных токов транзисторов 3, 4 следующим образом

Таким образом

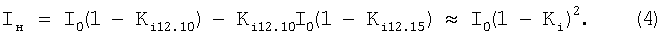

Учитывая, что коллекторные токи транзисторов 3, 4, 7, 8 приблизительно одинаковы Iк8=Iк3=Iк4=Iк7=I0, из (3) можно найти, что

В схеме ДУ-прототипа аналогичный ток в нагрузке Rн

Таким образом, статическая ошибка по выходу в заявляемом устройстве уменьшается в Ng-раз, где

Поэтому приведенное ко входу напряжение смещения нуля Uсм в заявляемом ДУ уменьшается

где SДУ - крутизна преобразования входного напряжения ДУ в его выходной ток.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice (фиг.8, 10).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 3786362.

2. Патент США № 4030044.

3. Патент США № 4059808.

4. Патент США № 4286227.

5. Авт. свид. СССР № 375754, H03f 3/38.

6. Авт. свид. СССР №.843164, H03f 3/30.

7. Патент США № 3660773.

8. Патент США № 4560948.

9. Патент РФ №930041, H03f 1/32.

10. Патент Японии № 57-5364, H03f 3/343.

11. Патент ЧССР № 134845, кл. 21а2 18/08.

12. Патент ЧССР № 134849, кл. 21а2 18/08.

13. Патент ЧССР № 135326, кл. 21а2 18/08.

14. Патент США № 4389579

15. Патент Англии № 1543361, Н3Т.

16. Патент США № 5521552 (фиг.3а).

17. Патент США № 3617859.

18. Патент США № 5789949.

19. Патент США № 4453134.

20. Патент США № 4760286.

21. Авт. свид. СССР № 1283946.

22. Патент РФ № 2019019.

23. Патент США № 4453092.

24. Патент США №.3566289.

25. Патент США № 3649859.

26. Патент США № 3649926.

27. Патент США № 4714894 (фиг.1).

28. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

29. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

30. Патент США № 3828268.

31. Патент США № 4074205.

32. Патент США № 4176308.

33. Патент США № 4536663.

34. Патент США № 4818897.

35. Патент США № 4855684.

36. Патент США № 5233289.

37. Патент США № 5401995.

38. Патент США № 5406222.

39. Патент США № 5455533.

40. Патент США № 5521553.

41. Патент США № 5910748.

42. Патент США № 5010303.

43. Патент США № 4749958.

44. Патент США № 442928445. Патентная заявка US 2006/0091952.

46. Авт. свид. СССР № 603097.

47. Авт. свид. СССР № 932591.

48. Авт. свид. СССР № 1259472.

49. Авт. свид. СССР № 1720146.

50. Авт. свид. СССР №.736119.

51. Патент ФРГ № 2633952.

52. Патент ФРГ №.2930041.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412536C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374758C1 |

| ТОКОВОЕ ЗЕРКАЛО | 2007 |

|

RU2343626C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2009 |

|

RU2416154C1 |

| ТОКОВОЕ ЗЕРКАЛО | 2007 |

|

RU2362202C1 |

Изобретение относится к области радиотехники и связи и может быть использовано для усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)). Технический результат заключается в уменьшении напряжения смещения нуля. Дифференциальный усилитель (ДУ) содержит первый входной каскад (1), выход (2) которого соединен с объединенными эмиттерами первого (3) и второго (4) выходных транзисторов (Т), второй входной каскад (5), выход которого (6) соединен с объединенными эмиттерами третьего Т (7) и четвертого Т (8), цепь установления (9) статического режима выходных Т (3, 4, 7, 8), связанная с их базами, первое токовое зеркало (ТЗ) (10), вход (11) которого соединен с коллектором Т (3), а выход (12) связан с коллектором Т (8) и выходом (13) ДУ, второе ТЗ (15), вход (16) которого соединен с коллектором Т (7), а выход (17) связан с коллектором Т (4). Вход (11) первого ТЗ (10) соединен с выходом (17) ТЗ (15). 10 ил.

Дифференциальный усилитель, содержащий первый входной каскад (1), выход (2) которого соединен с объединенными эмиттерами первого (3) и второго (4) выходных транзисторов, второй входной каскад (5), выход которого (6) соединен с объединенными эмиттерами третьего (7) и четвертого (8) выходных транзисторов, цепь установления (9) статического режима первого (3), второго (4), третьего (7) и четвертого (8) выходных транзисторов, связанная с их базами, первое токовое зеркало (10), вход (11) которого соединен с коллектором первого выходного транзистора (3), а выход (12) связан с коллектором четвертого выходного транзистора (8) и выходом (13) дифференциального усилителя, второе токовое зеркало (15), вход (16) которого соединен с коллектором третьего выходного транзистора (7), а выход (17) связан с коллектором второго выходного транзистора (4), отличающийся тем, что вход (11) первого токового зеркала (10) соединен с выходом (17) второго токового зеркала (15).

| US 4389579, 21.06.1983 | |||

| Дифференциальный усилитель | 1985 |

|

SU1385255A1 |

| Преобразователь напряжения в ток | 1987 |

|

SU1524161A2 |

| СПОСОБ ПРОИЗВОДСТВА ВЕТЧИНЫ, УПАКОВАННОЙ ПОД ВАКУУМОМ В ТЕРМОУСАДОЧНУЮ ПЛЕНКУ | 1999 |

|

RU2179814C2 |

| US 4429284, 31.01.1984. | |||

Авторы

Даты

2008-08-20—Публикация

2007-04-26—Подача