,/7

4/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих арифметик ческих устройствах для выполнения операции деления чисел. Цель изобретения - повышение быстродействия устройства за счет сокращения числа тактов его работы. Устройство содержит регистр 1 делимого, регистр 2 делителя, сумматор 3 частного, сумматор 9 принудительного округления делителя, блок 11 деления усеченных чисел, блок I умножения, три вычитателя два коммутатора 10,15, блок 16 управления и нововведенный третий коммутатор 8. 4 ил.

Ч

оа ел

00 4ь Ј

Изобретение относится к области вычислительной техники и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Известно устройство для деления, содержащее регистр делимого, регистр делителя, сумматор частного, сумматор принудительного округления, блок деления усеченных чисел, блок умноже-- ния, сумматор, вычитатель, коммута- т..р и блок управления.

Недостатком этого устройства является низкое быстродействие, вызванное большой длительностью такта формирования К цифр частного и остатка.

Известно также устройство для деления чисел, содержащее регистр делителя, регистр делимого, сумматор частного, сумматор принудительного округления делителя, блок деления усеченных чисел, блок умножения, два вычитателя, коммутатор и блок управления.

Хотя быстродействие данного устройства несколько выше по сравнению с рассмотренным, но и оно имеет низкое быстродействие из-за большой длительности такта.

Наиболее близким к изобретению по технической сущности является устройство для деления чисел, формирующее в каждом такте К цифр частного (2ё- n разрядность делимого и делителя; 3х Е ближайшее целое, большее или равное х) и содержащее регистр делимого, регистр делителя, сумматор частного, сумматор принудительного округления делителя, блок деления усеченных чисел, блок умножения, регистр цифр частного, три вычитателя, два коммутатора, бло управления, причем шина данных устройства соединена с информационными входами регистра делителя и с информационными входами первой группы первого коммутатора, выходы первого коммутатора соединены с информационными входами регистра делимого, выходы которого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения соответственно выходы разности и заема первого вычитателя соединены с входами уменьшаемог

ко

25

7358V 4

и вычитаемого второго вычитателя, выходы которого соединены с информационными входами второй группы первого коммутатора, входы первой группы блока умножения соединены с выходами регистра делителя, выходы старших разрядов которого соединены с входами сумматора принудительного округлеJQ ния делителяf вход переноса которого соединен с входом логической единицы устройства, выходы сумматора принудительного округления делителя соединены с входами делителя блока деле15 ния усеченных чисел, входы делимого которого соединены с выходами второго коммутатора, выходы блока деления усеченных чисел соединены с информационными входами регистра цифр част20 ного, выходы которого соединены с входами второй группы блока умножения и с входами младших разрядов сум- матора частного, выходы старших раз1- , рядов разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого третьего вычитателя соответственно, вход заема третьего вычитателя соединен с входом логической единицы устройства, выходы младших разрядов третьего вычитателя соединены с информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами старших разрядов шины данных устрой35 ства, вход синхронизации которого соединен с синхровходами регистров делимого и делителя, сумматора частного, регистра цифр частного и блока, управления, первый выход блока управ40 ления соединен с входом разрешения записи регистра делителя, второй выход блокэ управления соединен с первыми управляющими входами первого и второго коммутаторов и с входом уста45 новки в нуль сумматора частного} третий управляющий вход соединен с вторыми управляющими входами первого и второго коммутаторов и с входом . разрешения записи сумматора частного,

50 четвертый вход блока управления соединен с входом разрешения записи регистра делимого и регистра цифр частного, пятый выход блока управления является выходом сигнализации I

55 окончания деления устройства, выходы сумматора частного являются выходами частного устройства, выход старшего разряды третьего вычитателя соединен

30

с третьим управляющим входом второго коммутатора.

Недостаток известного устройства - относительно низкое быстродействие, так как старшие К цифр частного формируются в течение двух первых тактов его работы (в первом такте происходит загрузка регистра делителя, а во втором - загрузка регистра делимого и одновременное формирование К цифр частного).

Цель изобретения - повышение быстродействия устройства за счет сокращения числа тактов его работы.

Поставленная цель достигается тем, что в устройство для деления чисел, содэржащее регистр делимого, регистр делителя, сумматор частного сумматор принудительного округления делителя, блок деления усеченных чисел, блок умножения, регистр цифр частного, три вычитателя, два коммутатора и блок управления, причем выходы делителя и делимого через шину данных устройства соединены с информационными входами регистра делителя и с информационными входами первой группы первого коммутатора, выходы первого коммутатора соединены с информационными входами регистра делимого, выходы которого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и . второй групп блока умножения соответственно, выходы разности и заема пер iBoro вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя соответственно,выходы которого соединены с информационными входами второй группы первого коммутатора, входы первой группы блока умножения соединены с выходами регистра делителя, вход логической единицы устрой .ства соединен с входом пере- : носа, сумматора принудительного округления делителя, выходы которого соединены с входами делителя блока деления усеченных чисел, входы делимого которого соединены с выходами втррого коммутатора, выходы блока деления усеченных чисел соединены с информационными входами регистра цифр частного, выходы которого соединены с входами второй группы блока умножения и с входами младших раз- рядов сумматора частного, выходы ставших разрядов разности и заема

o

5

0

5

первого вычитателя соединены с входами уменьшаемого и вычитаемого третьего вычитателя соответственно, вход заема третьего вычитателя соединен с входом логической единицы устройства, выходы младших разрядов третьего вычитателя соединены с информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами старших разрядов делимого через шину данных устройства, вход синхронизации которого соединен с синхровходами регистров делителя и делимого, сумматора частного, регистра цифр частного и блока управления, первый выход блока управления соединен с входом разрешения записи регистра делителя и с входом установки в нуль сумматора частного, а также с первыми управляющими входами первого и второго коммутаторов, второй выход блока управления соединен с вторыми управляющими входами первого и второго коммутаторов и с входом разрешения записи сумматора частного, третий выход блока управления соединен с входом разрешения записи регист ра делимого и регистра цифр частного, четвертый выход блока управления является выходом сигнализации окончания деления устройства, выходы сумматора частного являются выходами v частного устройства, выход старшего разряда третьего вычитателя соединен с третьим управляющим входом второго коммутатора, дополнительно введен третий коммутатор, информационные входы первой группы которого соединены с выходами старших разрядов регистра делителя, а информационные входы второй группы - с выходами старших разрядов делителя через шину данных устройства, выходы третьего коммутатора соединены с входами сумматора принудительного округления делителя, первый и второй управляющие входы третьего коммутатора соединены с первым и вторым управляющими входа-, ми первого коммутатора соответственно.

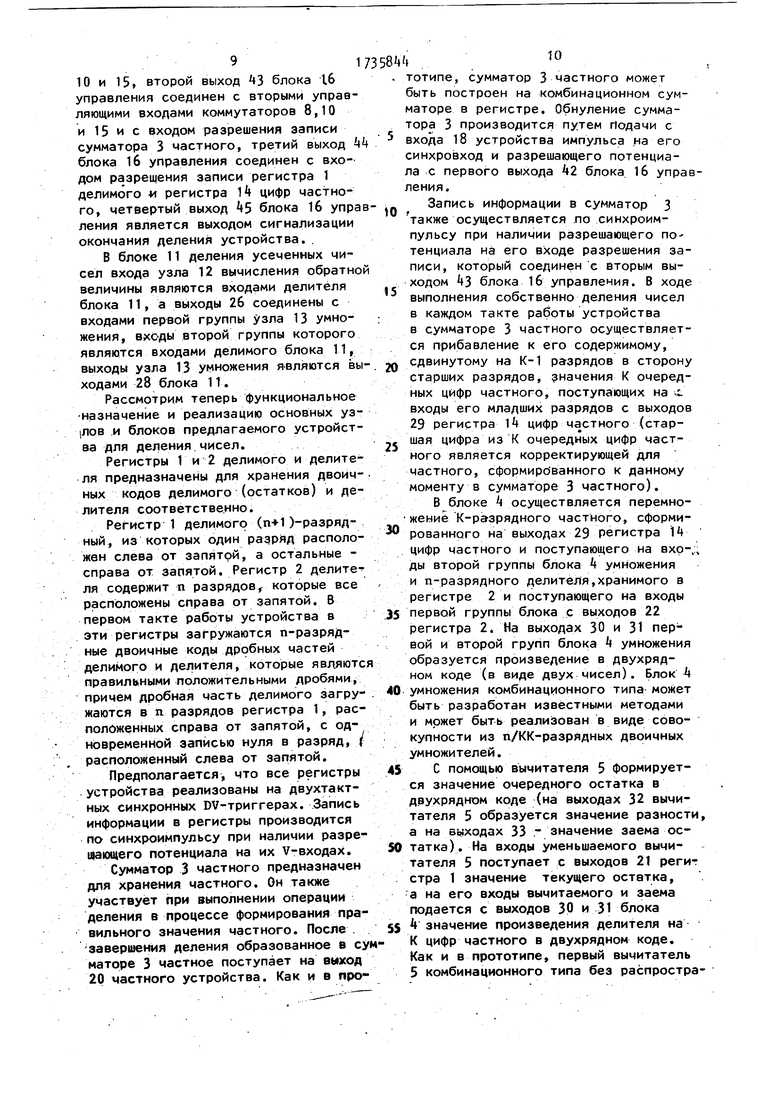

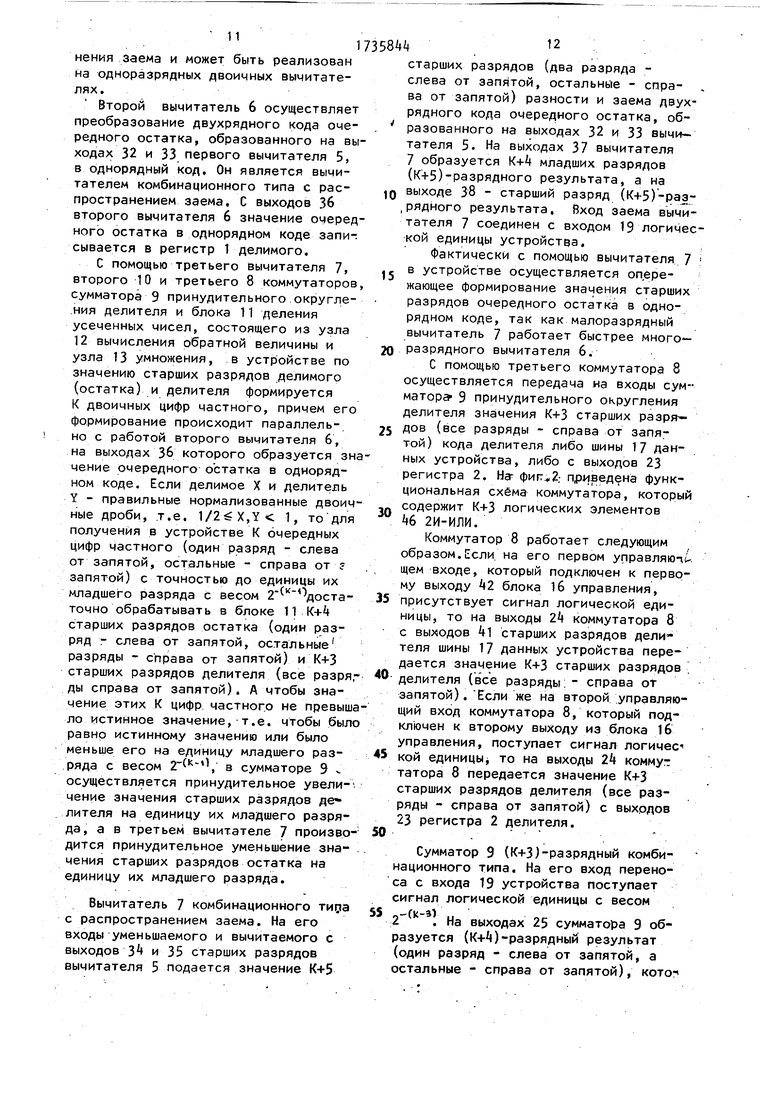

На фиг.1 приведена структурная схема устройства для деления чисел; -на фиг.2 - функциональная схема треть- его коммутатора; на фиг.З - функциональная схема блока управления; на фиг.k - микропрограмма работы устройства.

0

S

0

5

0

Устройство для деления содержит (фиг.1) регистр 1 делимого, регистр 2 делителя, сумматор 3 частного, бло 4 умножения, вычитатели 5-7 с первого по третий соответственно, третий коммутатор 8, сумматор 9 принудительного округления делителя, второй коммутатор 10, блок 11 деления усеченных чисел, состоящий из уз.ла 12 вычисления обратной величины и узла 13 умножения, регистр 14 цифр эстного, первый коммутатор 15, блок 16 управления, шину 17 данных устройства, вход 18 синхронизации устройства, вход 19 логической единицы устройства, выход 20 частного устройства, выходы 21 регистра 1 делимого, выходы 22 регистра 2 делителя, выходы 23 старших разрядов регистра 2 делителя, выходы 24 третьего коммутатора 8, выходы 25 сумматора 9 принудительного округления делителя, выходы 26 узла 12 вычисления обратной величины, выходы 26 узла 12 вычисления обратной величины, выходы 27 второго коммутатора 10, выходы 28 узла 13 умножения (они же являются и выходами блока 11 деления усеченных чисел), выходы 29 регистра 14 цифр частного, выходы 30 и 31 первой и второй групп блока 4 умножения соответственно, выходы 32 и 33 разности и заема первого вычитателя 5 соответственно, выходы 34 и 35 старших разрядов разности и заема первого вычитателя 5 соответственно, выходы 36 второго вычитателя 6, выходы 37 разрядов третьего вычитателя 7, выход 38 старшего разряда третьего . вычитателя 7 выходы 39 первого коммутатора 15, выходы 40 старших разрядов делимого шины 17 данных устройства, выходы 41 старших разрядов делителя шины 17 данных устройства, выходы 42-45 с первого по четвертый блока 16 управления соответственно.

Шина 17 данных устройства соединена с информационными входами разрядов регистра 2 делителя и с информационными входами первой группы первого коммутатора 15, информационные входы второй группы которого соединены с выходами 36 второго вычитателя 6, входы уменьшаемого и вычитаемого которого соединены с выходами 32 и 33 разности и заема первого вычитателя 5 соответственно, выходы 39 первого коммутатора 15 соединены

S

10

15

20

25

7358448

с информационными входами регистра 1 делимого, выходы 21 которого соединены с входами уменьшаемого первого вычитателя 5, входы вычитаемого и заема которого соединены с выходами 30 и 31 первой и второй групп блока 4 умножения соответственно, входы первой группы блока 4 умножения соединены с выходами 22 регистра 2 делителя, выходы 23 старших разрядов которого соединены с информационными входами первой группы третьего коммутатора 8, информационные входы второй группы которого соединены с выходами 41 старших разрядов-шины 17 данных устройства, выходы 24 третьего коммутатора 8 соединены с входами сумматора 9 принудительного округления делителя, вход переноса которого соединен с входом 19 логическойл- единицы устройства, выходы 25 сумматора 9 принудительного округления делителя соединены с входами делителя блока 11 деления усеченных чисел, входы делимого которого соединены с i выходами 27 второго коммутатора 10, .выходы 28 блока 11 деления усеченных чисел соединены с информационными

30 входами регистра 14 цифр частного, выходы 29 которого соединены с входами второй группы блока 4 умножения и с выходами младших разрядов сумматора 3 частного, Входы уменьшаемого и вычитаемого третьего вычитателя 7

35 соединены с выходами 34 и 35 старших разрядов разности и заема первого вычитателя 5 соответственно, выходы 37 младших разрядов третьего вычитателя 7 соединены с информационными входами первой группы второго коммутатора 10, информационные входы второй группы которого подключены к выходам старших разрядов шины 17 данных устройства, вход заема третьего вычитателя 7 соединен с входом 19 логической единицы устройства, выход 38 старшего разряда третьего вычитателя 7 соединен с третьим управляющим входом второго коммутатора 10, синхро- входы регистров 1,2 и 14, сумматора 3 частного и блока 16 управления соединены с входом 18 синхронизации устройства, первый выход 42 блока 16 управления соединен с входом разрешения записи регистра 2 делителя и с входом установки в нуль сумматора 3 частного, а также с первыми управляющими входами коммутатооов 8,

40

45

50

5

10 и 15, второй выход 3 блока 16 управления соединен с вторыми управляющими входами коммутаторов 8,10 и 15 и с входом разрешения записи сумматора 3 частного, третий выход 4 блока 16 управления соединен с входом разрешения записи регистра 1 делимого и регистра 14 цифр частного, четвертый выход 45 блока 16 упраления является выходом сигнализации окончания деления устройства.

В блоке 11 деления усеченных чисел входа узла 12 вычисления обратно величины являются входами делителя блока 11, а выходы 26 соединены с входами первой группы узла 13 умножения, входы второй группы которого являются входами делимого блока 11, выходы узла 13 умножения я-вляются выходами 28 блока 11.

Рассмотрим теперь функциональное назначение и реализацию основных уз- |Лов и блоков предлагаемого устройства для деления чисел.

Регистры 1 и 2 делимого и делителя предназначены для хранения двоичных кодов делимого (остатков) и делителя соответственно.

Регистр 1 делимого (п-Н разрядный, из которых один разряд расположен слева от запятой, а остальные - справа от запятой. Регистр 2 делителя содержит п разрядов, которые все расположены справа от запятой. В первом такте работы устройства в эти регистры загружаются п-разряд- ные двоичные коды дробных частей делимого и делителя, которые являютс правильными положительными дробями, причем дробная часть делимого загружаются в п разрядов регистра 1, расположенных справа от запятой, с одновременной записью нуля в разряд, ( расположенный слева от запятой.

Предполагается, что все регистры устройства реализованы на двухтактных синхронных DV-триггерах. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах.

Сумматор 3 частного предназначен для хранения частного. Он также участвует при выполнении операции деления в процессе формирования правильного значения частного. После завершения деления образованное в суматоре 3 частное поступает на выход 20 частного устройства. Как и в про0

5

0

5

тотипе, сумматор 3 частного может быть построен на комбинационном сумматоре в регистре. Обнуление сумматора 3 производится путем Подачи с входа 18 устройства импульса на его синхровход и разрешающего потенциала с первого выхода 42 блока 16 управления.

Запись информации в сумматор 3 также осуществляется по синхроимпульсу при наличии разрешающего по- тенциала на его входе разрешения записи, который соединен с вторым выходом 43 блока 16 управления. В ходе выполнения собственно деления чисел в каждом такте работы устройства в сумматоре 3 частного осуществляется прибавление к его содержимому, сдвинутому на К-1 разрядов в сторону старших разрядов, значения К очередных цифр частного, поступающих на i входы его младших разрядов с выходов 29 регистра 14 цифр частного (старшая цифра из К очередных цифр частного является корректирующей для частного, сформиро ванного к данному моменту в сумматоре 3 частного).

В блоке 4 осуществляется перемножение К-рэзрядного частного, сформированного на выходах 29 регистра 14 цифр частного и поступающего на вхо-., ды второй группы блока 4 умножения и n-разрядного делителя,хранимого в регистре 2 и поступающего на входы первой группы блока с выходов 22 регистра 2. На выходах 30 и 31 первой и второй групп блока 4 умножения образуется произведение в двухрядном коде (в виде двух чисел). Блок 4 умножения комбинационного типа может быть разработан известными методами и может быть реализован в виде совокупности из n/KK-разрядных двоичных умножителей.

С помощью вычитателя 5 формируется значение очередного остатка в двухрядном коде (на выходах 32 вычитателя 5 образуется значение разности, а на выходах 33 - значение заема ос- 0 татка). На входы уменьшаемого вычитателя 5 поступает с выходов 21 регистра 1 значение текущего остатка, а на его входы вычитаемого и заема подается с выходов 30 и 31 блока

4значение произведения делителя на К цифр частного в двухрядном коде. Как и в прототипе, первый вычитатель

5комбинационного типа без распростра0

5

0

5

S

нения заема и может быть реализован на одноразрядных двоичных вычитате- лях.

Второй вычитатель 6 осуществляет преобразование двухрядного кода очередного остатка, образованного на выходах 32 и 33 первого вычитателя 5, в однорядный код. Он является вычи- тателем комбинационного типа с распространением заема. С выходов 36 второго вычитателя 6 значение очередного остатка в однорядном коде запи-. сывается в регистр 1 делимого,

С помощью третьего вычитателя 7, второго 10 и третьего 8 коммутаторов, сумматора 9 принудительного округления делителя и блока 11 деления усеченных чисел, состоящего из узла 12 вычисления обратной величины и узла 13 умножения, в устройстве по значению старших разрядов делимого (остатка) и делителя формируется К двоичных цифр частного, причем его формирование происходит параллельно с работой второго вычитателя 6, на выходах 36 которого образуется значение очередного остатка в однорядном коде. Если делимое X и делитель Y - правильные нормализованные двоичные дроби, т.е. 1/2 X,У 1, то для получения в устройстве К очередных цифр частного (один разряд - слева от запятой, остальные - справа от запятой) с точностью до единицы их младшего разряда с весом 2 1С доста- точно обрабатывать в блоке 11 К+4 старших разрядов остатка (один разряд - слева от запятой, остальные разряды - справа от запятой) и К+3

10

15

20

старших разрядов (два разряда - слева от запятой, остальные - спр ва от запятой) разности и заема д рядного кода очередного остатка, разованного на выходах 32 и 33 вы тателя 5. На выходах 37 вычитател 7 образуется К+4 младших разрядов (К+5)-разрядного результата, а на выходе 38 - старший разряд (К+5)рядного результата. Вход заема в тателя 7 соединен с входом 19 лог кой единицы устройства.

Фактически с помощью вычитател в устройстве осуществляется опере жающее формирование значения стар разрядов очередного остатка в одн рядном коде, так как малоразрядны вычитатель 7 работает быстрее мно разрядного вычитателя 6.

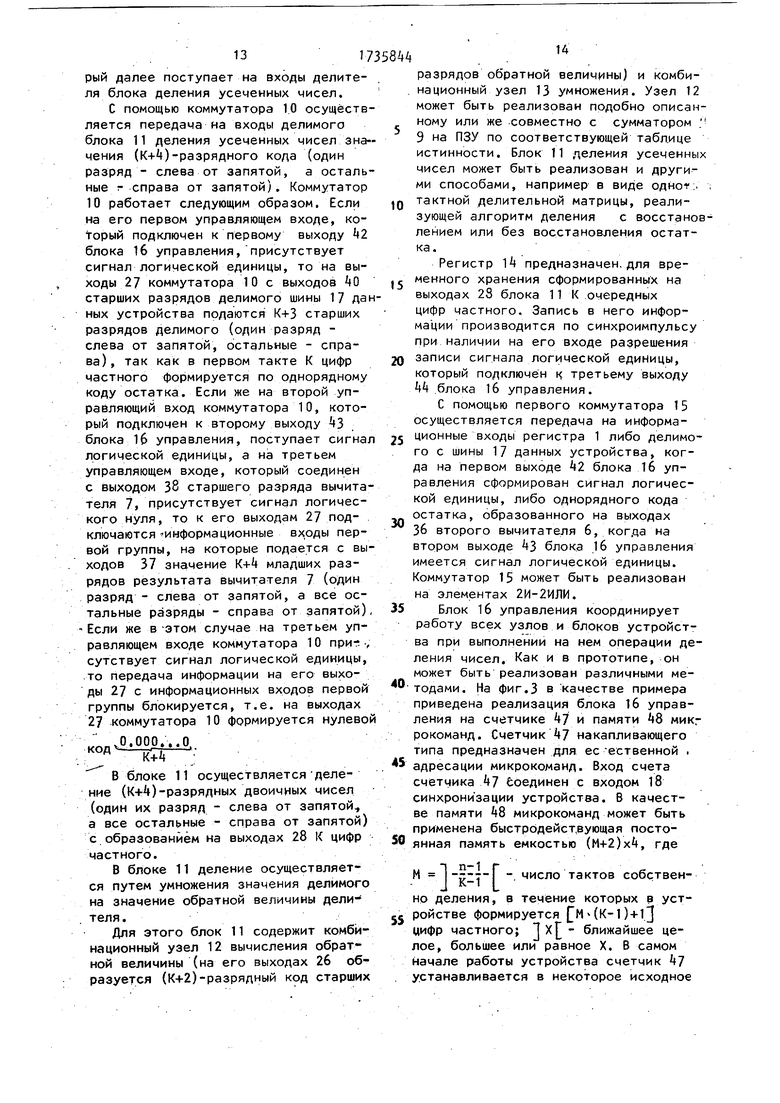

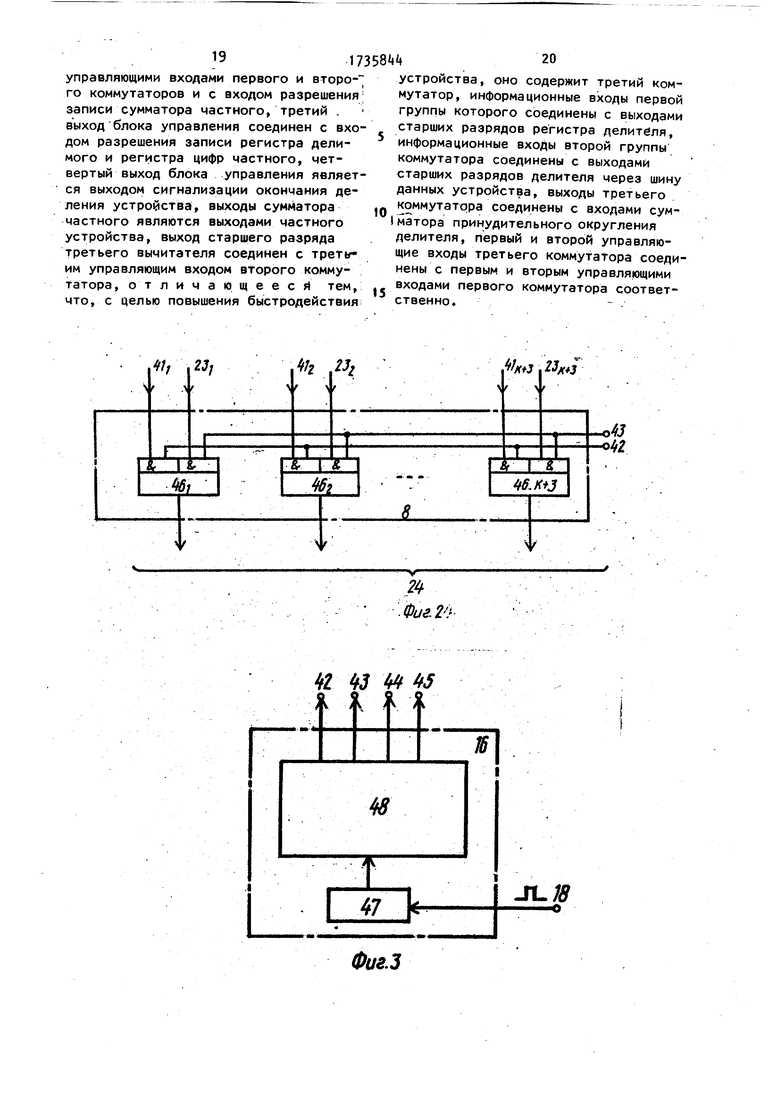

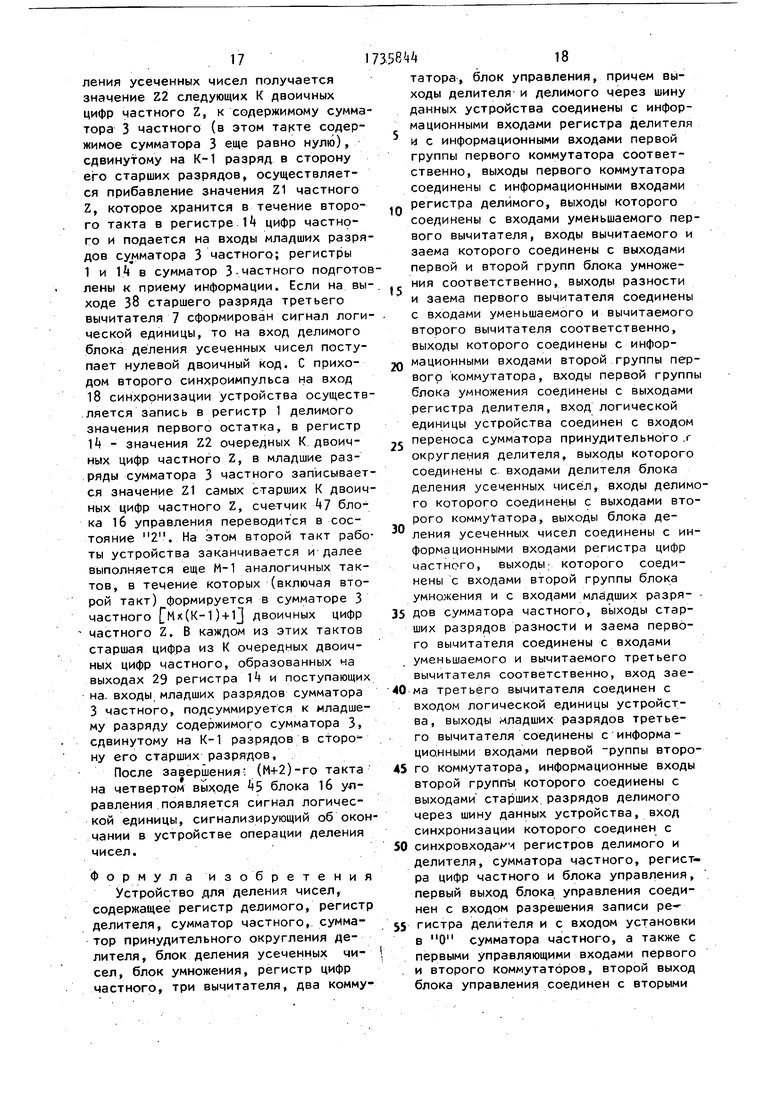

С помощью третьего коммутатора осуществляется передача на входы матора- 9 принудительного округлен делителя значения К+3 старших раз 25 дов (все разряды - справа от запя той) кода делителя либо шины 17 д ных устройства, либо с выходов 23 регистра 2. На- приведена фу циональная схема коммутатора, кот содержит К+3 логических элементов 46 2И-ИЛИ.

Коммутатор 8 работает следующи образом.Если на его первом управл щем входе, который подключен к пе му выходу 42 блока 16 управления, присутствует сигнал логической ед ницы, то на выходы 24 коммутатора с выходов 41 старших разрядов дели теля шины 17 данных устройства пе дается значение К+3 старших разряд

30

35

старших разрядов делителя (все разря,- 4& делителя (все разряды - справа от

ды справа от запятой). А чтобы значение этих К цифр частного не превышало истинное значение, т.е. чтобы было равно истинному значению или было меньше его на единицу младшего раз- 45 ряда с весом в сумматоре 9 - осуществляется принудительное увели- чение значения старших разрядов делителя на единицу их младшего разряда, а в третьем вычитателе 7 произво- 50 дится принудительное уменьшение значения старших разрядов остатка на единицу их младшего разряда.

Вычитатель 7 комбинационного типа 55 с распространением заема. На его входы уменьшаемого и вычитаемого с выходов 34 и 35 старших разрядов вычитателя 5 подается значение К+5

запятой). Если же на второй управл щий вход коммутатора 8, который по ключен к второму выходу из блока управления, поступает сигнал логич кой единицы, то на выходы 24 комму татора 8 передается значение К+3 старших разрядов делителя (все раз ряды - справа от запятой) с выходо 23 регистра 2 делителя.

Сумматор 9 (К+3)-разрядный комб национного типа. На его вход перен са с входа 19 устройства поступает сигнал логической единицы с весом

0

5

0

старших разрядов (два разряда - слева от запятой, остальные - справа от запятой) разности и заема двухрядного кода очередного остатка, образованного на выходах 32 и 33 вычи- тателя 5. На выходах 37 вычитателя 7 образуется К+4 младших разрядов (К+5)-разрядного результата, а на выходе 38 - старший разряд (К+5)раз рядного результата. Вход заема вычитателя 7 соединен с входом 19 логической единицы устройства.

Фактически с помощью вычитателя 7 в устройстве осуществляется опережающее формирование значения старших разрядов очередного остатка в однорядном коде, так как малоразрядный вычитатель 7 работает быстрее многоразрядного вычитателя 6.

С помощью третьего коммутатора 8 осуществляется передача на входы сумматора- 9 принудительного округления делителя значения К+3 старших разрет- 5 дов (все разряды - справа от запятой) кода делителя либо шины 17 данных устройства, либо с выходов 23 регистра 2. На- приведена функциональная схема коммутатора, который содержит К+3 логических элементов 46 2И-ИЛИ.

Коммутатор 8 работает следующим образом.Если на его первом управляют щем входе, который подключен к первому выходу 42 блока 16 управления, присутствует сигнал логической единицы, то на выходы 24 коммутатора 8 с выходов 41 старших разрядов делителя шины 17 данных устройства передается значение К+3 старших разрядов

0

5

& делителя (все разряды - справа от

делителя (все разряды - справа от

запятой). Если же на второй управляющий вход коммутатора 8, который подключен к второму выходу из блока 16 управления, поступает сигнал логичес-1 кой единицы, то на выходы 24 коммут татора 8 передается значение К+3 старших разрядов делителя (все разряды - справа от запятой) с выходов 23 регистра 2 делителя.

Сумматор 9 (К+3)-разрядный комбинационного типа. На его вход переноса с входа 19 устройства поступает сигнал логической единицы с весом

13

рый далее поступает на входы делителя блока деления усеченных чисел.

С помощью коммутатора 10 осуществляется передача на входы делимого блока 11 деления усеченных чисел зна чения (К+4)-разрядного кода (один разряд - слева от запятой, а остальные - справа от запятой). Коммутатор 10 работает следующим образом. Если на его первом управляющем входе, который подключен к первому выходу 42 блока 16 управления, присутствует сигнал логической единицы, то на выходы 27 коммутатора 10 с выходов 40 старших разрядов делимого шины 17 данных устройства подаются К+3 старших разрядов делимого (один разряд - слева от запятой, остальные - справа), так как в первом такте К цифр частного формируется по однорядному коду остатка. Если же на второй управляющий вход коммутатора 10, который подключен к второму выходу 43 блока 16 управления, поступает сигнал логической единицы, а на третьем управляющем входе, который соединен с выходом 38 старшего разряда вычита- теля 7, присутствует сигнал логического нуля, то к его выходам 27 подключаются -информационные входы первой группы, на которые подается с выходов 37 значение К+4 младших разрядов результата вычитателя 7 (один разряд - слева от запятой, а все остальные разряды - справа от запятой), - Если же в этом случае на третьем управляющем входе коммутатора 10 при-, сутствует сигнал логической единицы, то передача информации на его выходы 27 с информационных входов первой группы блокируется, т.е. на выходах 2 коммутатора 10 формируется нулевой

В блоке 11 осуществляется деление (К+4)-разрядных двоичных чисел (один их разряд - слева от запятой, а все остальные - справа от запятой) с образованием на выходах 28 К цифр частного.

В блоке 11 деление осуществляется путем умножения значения делимого на значение обратной величины делителя.

Для этого блок 11 содержит комбинационный узел 12 вычисления обратной величины (на его выходах 26 образуется (К+2)-разрядный код старших

10

15

20

25

35S441А

разрядов обратной величины) и комбинационный узел 13 умножения. Узел 12 может быть реализован подобно описанному или же совместно с сумматором 9 на ПЗУ по соответствующей таблице истинности. Блок 11 деления усеченных чисел может быть реализован и другими способами, например в виде одно тактной делительной матрицы, реализующей алгоритм деления с восстановлением или без восстановления остатка.

Регистр 14 предназначен для временного хранения сформированных на выходах 28 блока 11 К очередных цифр частного. Запись в него информации производится по синхроимпульсу при наличии на его входе разрешения записи сигнала логической единицы, который подключен к третьему выходу 44 блока 16 управления.

С помощью первого коммутатора 15 осуществляется передача на информационные входы регистра 1 либо делимого с шины 17 данных устройства, когда на первом выходе 42 блока 16 управления сформирован сигнал логической единицы, либо однорядного кода остатка, образованного на выходах 36 второго вычитателя 6, когда на втором выходе 43 блока 16 управления имеется сигнал логической единицы. Коммутатор 15 может быть реализован на элементах 2И-2ИЛИ.

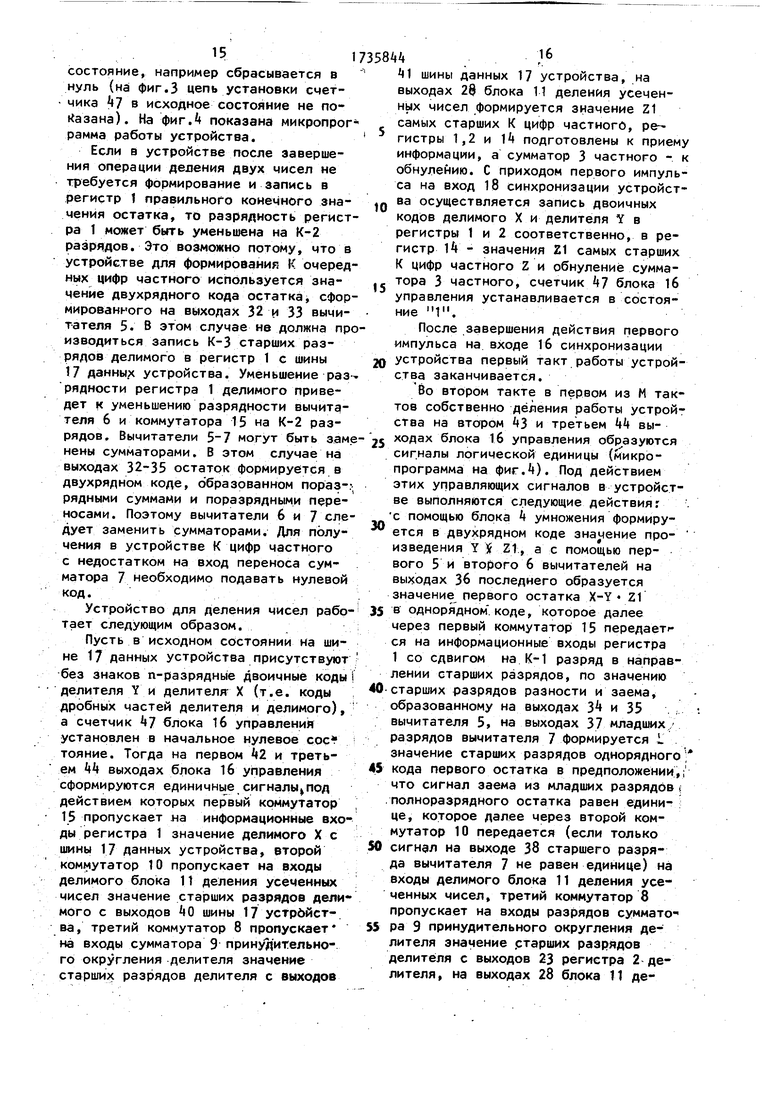

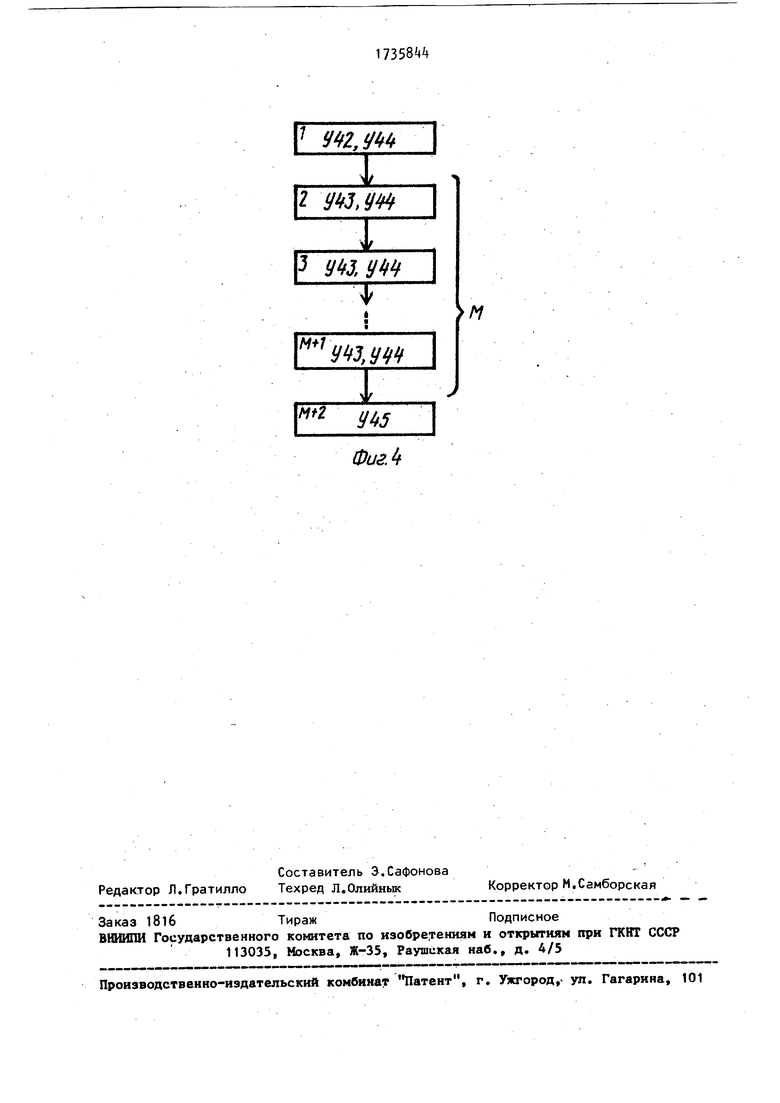

Блок 16 управления координирует работу всех узлов и блоков устройства при выполнении на нем операции деления чисел. Как и в прототипе, он может быть реализован различными ме- тодами. На фиг.З в качестве примера приведена реализация блока 16 управления на счетчике 47 и памяти 48 микрокоманд. Счетчик 47 накапливающего типа предназначен для ее ественной . адресации микрокоманд. Вход счета счетчика 47 соединен с входом 18 синхронизации устройства. В качестве памяти 48 микрокоманд может быть применена быстродействующая постоянная память емкостью (М+2)х4, где

30

35

45

50

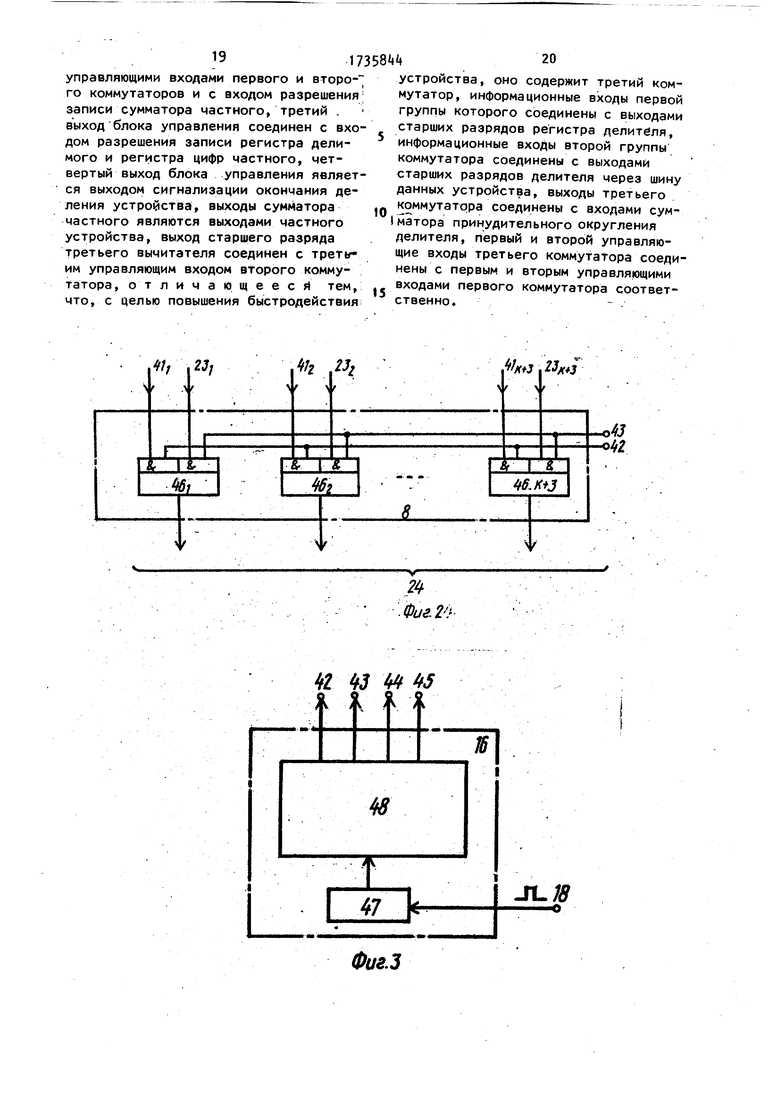

М числ° тактов собственно деления, в течение которых в уст- ройстве формируется Јм(К-1) + 1 цифр частного; 1 хЈ - ближайшее целое, большее или равное X. В самом начале работы устройства счетчик 47 устанавливается в некоторое исходное

15

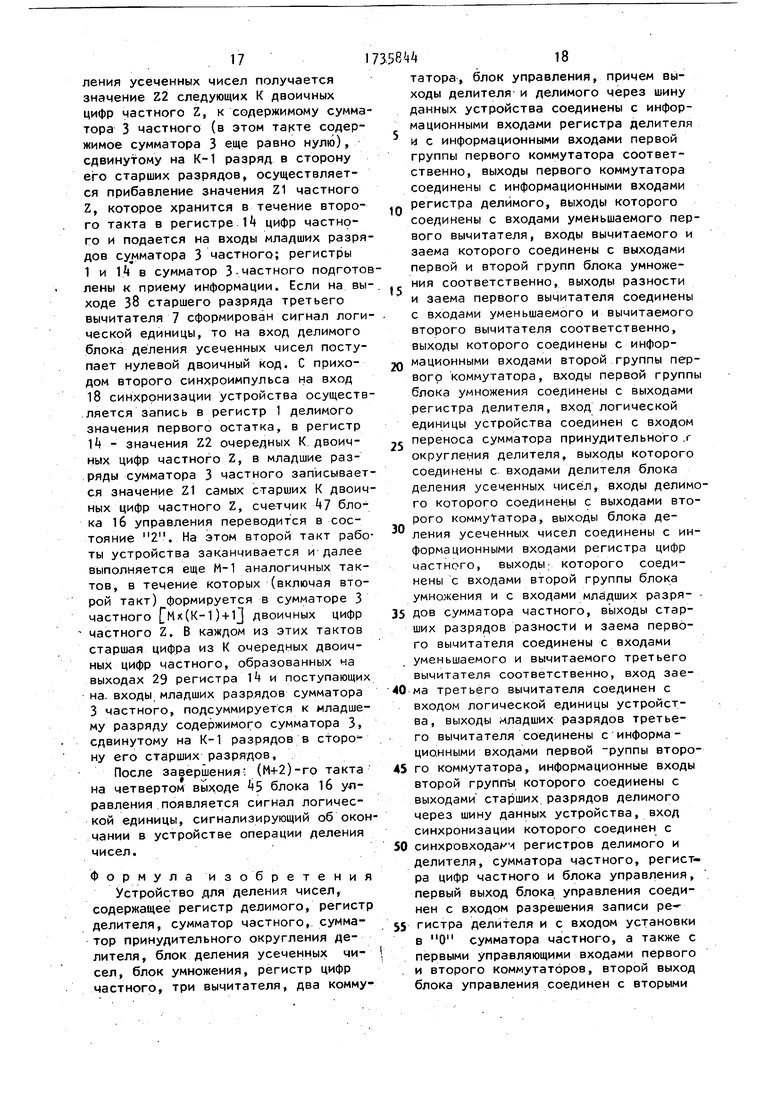

состояние, например сбрасывается в нуль (на фиг.З цепь установки счетчика 47 в исходное состояние не показана). На фиг.4 показана микропрограмма работы устройства.

Если в устройстве после завершения операции деления двух чисел не требуется формирование и запись в регистр правильного конечного значения остатка, то разрядность регистра 1 может быть уменьшена на К-2 разрядов. Это возможно потому, что в устройстве для формирования К очередных цифр частного используется значение двухрядного кода остатка, сформированного на выходах 32 и 33 вычи- тателя 5. В этом случае не должна производиться запись К-3 старших разрядов делимого в регистр 1 с шины 17 данных устройства. Уменьшение раз- рядности регистра 1 делимого приведет к уменьшению разрядности вычита- теля 6 и коммутатора 15 на К-2 раз41 шины данных 17 устройства, на выходах 28 блока 11 деления усеченных чисел формируется значение Z1 самых старших К цифр частного, ре-- гистры 1,2 и 14 подготовлены к прием информации, а сумматор 3 частного - обнулению. С приходом первого импуль са на вход 18 синхронизации устройст ва осуществляется запись двоичных кодов делимого X и делителя Y в регистры 1 и 2 соответственно, в регистр 14 - значения Z1 самых старших К цифр частного Z и обнуление сумматора 3 частного, счетчик 47 блока 16 управления устанавливается в состоя10

15

ние 1.

После завершения действия первого импульса на входе 16 синхронизации 20 устройства первый такт работы устрой ства заканчивается.

Во втором такте в первом из М так тов собственно деления работы устрой ства на втором 43 и третьем 44 вырядов. Вычитатели могут быть заме-Че ходах блока 16 управления образуются

is

нены сумматорами. В этом случае на выходах 32-35 остаток формируется в двухрядном коде, образованном пораз-.; рядными суммами и поразрядными переносами. Поэтому вычитатели 6 и 7 следует заменить сумматорами. Для получения в устройстве К цифр частного с недостатком на вход переноса сумматора 7 необходимо подавать нулевой код.

Устройство для деления чисел работает следующим образом.

Пусть в исходном состоянии на шине 17 данных устройства присутствуют без знаков n-разрядные двоичные коды i делителя Y и делителя X (т.е. коды дробных частей делителя и делимого), а счетчик 47 блока 16 управления установлен в начальное нулевое сое тояние. Тогда на первом 42 и третьем 44 выходах блока 16 управления сформируются единичные сигнальцпод действием которых первый коммутатор 15 пропускает на информационные входы регистра 1 значение делимого X с шины 17 данных устройства, второй коммутатор 10 пропускает на входы делимого блока 11 деления усеченных чисел значение старших разрядов делимого с выходов 40 шины 17 устройства , третий коммутатор 8 пропускает на входы сумматора 9 принудительного округления делителя значение старших разрядов делителя с выходов

30

35

40

45

50

55

сигналы логической единицы (микропрограмма на фиг.4). Под действием этих управляющих сигналов в устройст ве выполняются следующие действия: с помощью блока 4 умножения формируется в двухрядном коде значение про- изведения Y % Z1, а с помощью первого 5 и второго 6 вычитателей на выходах 36 последнего образуется значение первого остатка X-Y Z1 в однорядном коде, которое далее через первый коммутатор 15 передает ся на информационные входы регистра 1 со сдвигом на К-1 разряд в направлении старших разрядов, по значению старших разрядов разности и заема, образованному на выходах 3 и 35 вычитателя 5, на выходах 37 младших - разрядов вычитателя 7 формируется L значение старших разрядов однорядного кода первого остатка в предположении что сигнал заема из младших разрядов полноразрядного остатка равен единице, которое далее через второй коммутатор 10 передается (если только сигнал на выходе 38 старшего разряда вычитателя 7 не равен единице) на входы делимого блока 11 деления усеченных чисел, третий коммутатор 8 пропускает на входы разрядов суммато ра 9 принудительного округления делителя значение .старших разрядов делителя с выходов 23 регистра 2- делителя, на выходах 28 блока 11 де

35844,16

41 шины данных 17 устройства, на выходах 28 блока 11 деления усеченных чисел формируется значение Z1 самых старших К цифр частного, ре-- гистры 1,2 и 14 подготовлены к приему информации, а сумматор 3 частного - к обнулению. С приходом первого импульса на вход 18 синхронизации устройства осуществляется запись двоичных кодов делимого X и делителя Y в регистры 1 и 2 соответственно, в регистр 14 - значения Z1 самых старших К цифр частного Z и обнуление сумматора 3 частного, счетчик 47 блока 16 управления устанавливается в состоя10

15

ние 1.

После завершения действия первого импульса на входе 16 синхронизации устройства первый такт работы устройства заканчивается.

Во втором такте в первом из М тактов собственно деления работы устройства на втором 43 и третьем 44 выходах блока 16 управления образуются

is

сигналы логической единицы (микропрограмма на фиг.4). Под действием этих управляющих сигналов в устройстве выполняются следующие действия: с помощью блока 4 умножения формируется в двухрядном коде значение про- изведения Y % Z1, а с помощью первого 5 и второго 6 вычитателей на выходах 36 последнего образуется значение первого остатка X-Y Z1 в однорядном коде, которое далее через первый коммутатор 15 передает ся на информационные входы регистра 1 со сдвигом на К-1 разряд в направлении старших разрядов, по значению старших разрядов разности и заема, образованному на выходах 3 и 35 вычитателя 5, на выходах 37 младших - разрядов вычитателя 7 формируется L значение старших разрядов однорядного кода первого остатка в предположении,, что сигнал заема из младших разрядов i полноразрядного остатка равен единице, которое далее через второй коммутатор 10 передается (если только сигнал на выходе 38 старшего разряда вычитателя 7 не равен единице) на входы делимого блока 11 деления усеченных чисел, третий коммутатор 8 пропускает на входы разрядов суммато4 ра 9 принудительного округления делителя значение .старших разрядов делителя с выходов 23 регистра 2- делителя, на выходах 28 блока 11 де17

ления усеченных чисел получается значение Z2 следующих К двоичных цифр частного Z, к содержимому сумматора 3 частного (в этом такте содержимое сумматора 3 еще равно нулю), сдвинутому на К-1 разряд в сторону его старших разрядов, осуществляется прибавление значения Z1 частного Z, которое хранится в течение второго такта в регистре И цифр частного и подается на входы младших разрядов сумматора 3 частного; регистры 1 и И в сумматор 3 частного подготовлены к приему информации. Если на выходе 38 старшего разряда третьего вычитателя 7 сформирован сигнал логической единицы, то на вход делимого блока деления усеченных чисел поступает нулевой двоичный код. С приходом второго синхроимпульса на вход 18 синхронизации устройства осуществляется запись в регистр 1 делимого значения первого остатка, в регистр - значения Z2 очередных К двоичных цифр частного Z, в младшие разряды сумматора 3 частного записывается значение Z1 самых старших К двоичных цифр частного Z, счетчик kj блока 16 управления переводится в состояние 2. На этом второй такт работы устройства заканчивается и далее выполняется еще М-1 аналогичных тактов, в течение которых (включая второй такт) формируется в сумматоре 3 частного ЈMx(K-1)+lJ двоичных цифр частного Z. В каждом из этих тактов старшая цифра из К очередных двоичных цифр частного, образованных на выходах 29 регистра I1 и поступающих на входы младших разрядов сумматора 3 частного, подсуммируется к младшему разряду содержимого сумматора 3, сдвинутому на К-1 разрядов в сторону его старших разрядов,

После завершения- (М+2)-го такта на четвертом выходе kS блока 16 управления появляется сигнал логической единицы, сигнализирующий об окончании в устройстве операции деления чисел.

Формула изобретения

Устройство для деления чисел, содержащее регистр делимого, регистр делителя, сумматор частного, сумматор принудительного округления делителя, блок деления усеченных чисел, блок умножения, регистр цифр частного, три вычитателя, два комму17

10

15

20

25

7358М18

татора, блок управления, причем выходы делителя и делимого через шину данных устройства соединены с информационными входами регистра делителя и с информационными входами первой группы первого коммутатора соответственно, выходы первого коммутатора соединены с информационными входами регистра делимого, выходы которого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения соответственно, выходы разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого второго вычитателя соответственно, выходы которого соединены с информационными входами второй группы первого коммутатора, входы первой группы блока умножения соединены с выходами регистра делителя, вход логической единицы устройства соединен с входом переноса сумматора принудительного г округления делителя, выходы которого соединены с входами делителя блока деления усеченных чисел, входы делимого которого соединены с выходами второго коммутатора, выходы блока деления усеченных чисел соединены с информационными входами регистра цифр частного, выходы которого соединены с входами второй группы блока умножения и с входами младших разря35 дов сумматора частного, выходы старших разрядов разности и заема первого вычитателя соединены с входами уменьшаемого и вычитаемого третьего вычитателя соответственно, вход зае40 ма третьего вычитателя соединен с входом логической единицы устройства, выходы младших разрядов третьего вычитателя соединены с информационными входами первой руппы второ45 го коммутатора, информационные входы второй группы которого соединены с выходами старших разрядов делимого через шину данных устройства, вход синхронизации которого соединен с

50 синхровходамм регистров делимого и делителя, сумматора частного, регистра цифр частного и блока управления, первый выход блока управления соединен с входом разрешения записи ре-- гистра делителя и с входом установки

30

55

в О сумматора частного, а также с первыми управляющими входами первого и второго коммутаторов, второй выход блока управления соединен с вторыми

19

управляющими входами первого и второ- го коммутаторов и с входом разрешения записи сумматора частного, третий выход блока управления соединен с входом разрешения записи регистра делимого и регистра цифр частного, четвертый выход блока управления является выходом сигнализации окончания деления устройства, выходы сумматора частного являются выходами частного устройства, выход старшего разряда третьего вычитателя соединен с третьим управляющим входом второго комму173

устройства, оно содержит третий коммутатор, информационные входы первой группы которого соединены с выходами старших разрядов регистра делителя, информационные входы второй группы коммутатора соединены с выходами старших разрядов делителя через шину данных устройства, выходы третьего 10 коммутатора соединены с входами сум- Iматора принудительного округления делителя, первый и второй управляющие входы третьего коммутатора соединены с первым и вторым управляющими

татора, отличающееся} тем, j- входами первого коммутатора соответ- что, с целью повышения быстродействия ственно.

tl ft W К

1 4

Гг

7

ЙЕ

устройства, оно содержит третий коммутатор, информационные входы первой группы которого соединены с выходами старших разрядов регистра делителя, информационные входы второй группы коммутатора соединены с выходами старших разрядов делителя через шину данных устройства, выходы третьего 10 коммутатора соединены с входами сум- Iматора принудительного округления делителя, первый и второй управляющие входы третьего коммутатора соединены с первым и вторым управляющими

#

Фиг. 2 }

v I i

-П-#

Фиг.З

у т, ум

2 mm

i

р т ум

i

Г тда

i

ум

i

Фиг 4

| Устройство для деления | 1978 |

|

SU802962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР tf , кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ | |||

Авторы

Даты

1992-05-23—Публикация

1990-08-29—Подача