ва, когда на выходе 44 блока 17 управ- (k+40 разрядов обратной величины;

ления формируется сигнал логической 1, либо значения поразрядных разностей двухрядного кода остатка, образованного на выходах 40 вычитателя

(х,-р) значение усеченного остат

полученного приведением к однорядн коду старших разрядов двухрядного да остатка, где , если в старши

(k+40 разрядов обратной величины;

(х,-р) значение усеченного остатка,

полученного приведением к однорядному коду старших разрядов двухрядного кода остатка, где , если в старшие

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

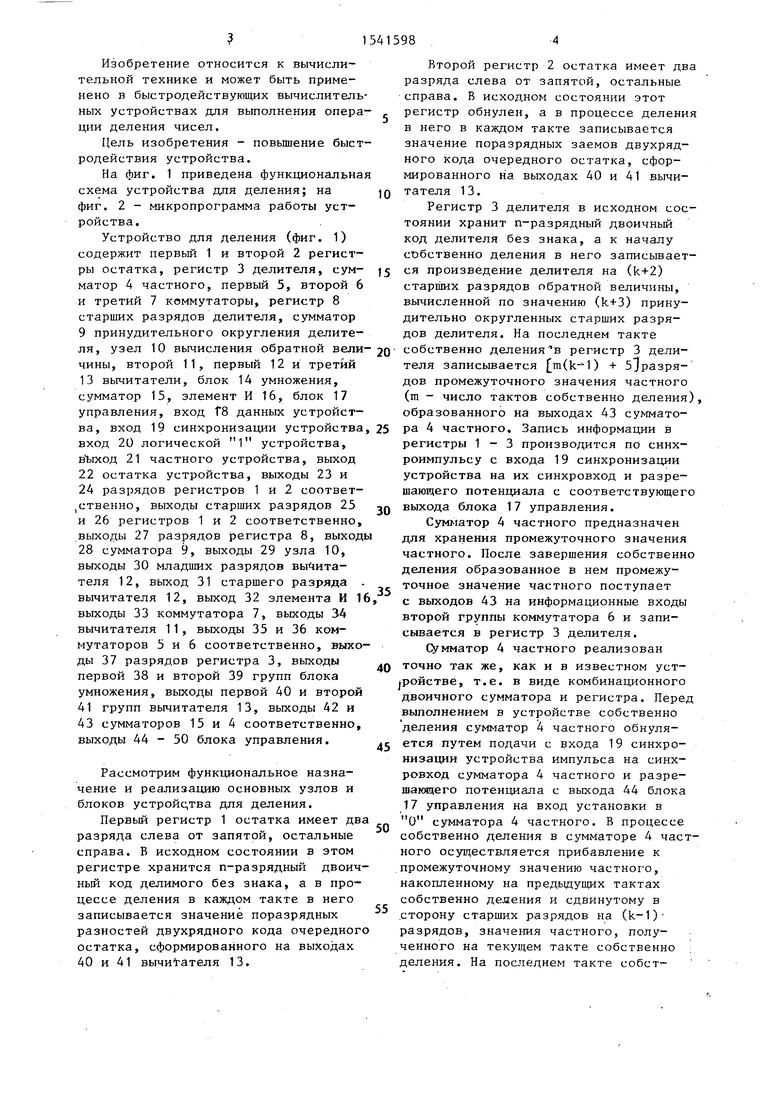

Изобретение относится к области вычислительной техники и может быть применено в быстродействующих вычислительных устройствах для выполнения операции деления чисел. Целью изобретения является повышение быстродействия устройства. Устройство содержит два регистра 1, 2 остатка, регистр 3 делителя, сумматор 4 частного, три коммутатора 5-7, два вычитателя 11 -12, регистр 8 старших разрядов делителя, сумматор 9 принудительного округления делителя, узел 10 вычисления обратной величины, блок 14 умножения, блок 17 управления и элемент И 16. Новым является введение сумматора 15 и третьего вычитателя 13, которые позволяют сократить длительность такта работы за счет исключения времени формирования произведения в однорядном коде. 2 ил.

25

30

35

40

к однорядному коду придет заем из

o-fk- i младших разрядов, и , если

не придет; р - величина, на которую отличается значение усеченного остатка, полученного приведением к одноряд ному коду старших разрядов двухрядного кода остатка и принудительно уменьшенная на единицу младшего разряда в вычитателе 12, от значения старших разрядов остатка, получаемого приведением к однорядному коду всех разрядов двухрядного кода остатка в вычитателе 11. На подготовительном этапе деления формируется произведение делителя у на значение старших (k+2) разрядов обратной величины w у-с(. При выполнении собственно деления следующий остаток вычисляется

13, когда на выходе 45 блока 17 управ- 20 разряды остатка х при приведении его ления формируется сигнал логической

II 4 II I .

С помощью коммутатора 6 осуществляется передача на информационные входы регистра 3 делителя, либо делителя с входа 18 данных устройства, когда на выходе 48 блока 17 управления формируется сигнал логической 1, либо значения суммы, образован- ной на выходах 42 сумматора 15, KOI- да на выходе 49 блока 17 управления формируется сигнал логической 1, либо промежуточного значения частного, образованного на выходах 43 сумматора 4 частного, .когда на выходе 45 блока 17 управления формируется сигнал логической 1.

С помощью коммутатора 7 осуществляется передача на его выходы 33 либо значения старших (k+2) разрядов обратной величины от принудительно округленного значения старших (k+З) разрядов делителя, образованного на выходах 29 узла 10, когда на выходе 49 блока 17 управления формируется сигнал логической 1, либо значения однорядного кода (k+4) старших разрядов остатка, поступающего с выходов 30 младших разрядов вычитателя 12, когда на выходе элемента И 16 формируется сигнал логической 1.

Формирование цифр частного и остатка на каждом такте работы устройства для деления производится следующим образом. Пусть делимое х и делитель у есть положительные нормализованные двоичные дроби, т.е. и 1/2 /. у - 1.

х( . Параллельно

45

50

55

по формуле х х - w с вычислением остатка в сумматоре 4 частного производится накапливание промежуточного значения частного х, являющегося суммой всех ( р), полученных на каждом такте работы устройства и сдвинутых один относительно другого на (k-1) разрядов. После выполнения собственно деления значение х умножается на значение с(. Старшие n-р азрядов этого произведения и являются значением частного z.

Регистр 8 старших разрядов делителя (k+З)-разрядный и предназначен для хранения у (старших (k+З) разрядов делителя у без знака). Запись информации в регистр производится по синхроимпульсу при наличии разрешающего потенциала.

Сумматор 9 принудительного округления делителя является комбинацион

к однорядному коду придет заем из

o-fk- i младших разрядов, и , если

не придет; р - величина, на которую отличается значение усеченного остатка, полученного приведением к однорядному коду старших разрядов двухрядного кода остатка и принудительно уменьшенная на единицу младшего разряда в вычитателе 12, от значения старших разрядов остатка, получаемого приведением к однорядному коду всех разрядов двухрядного кода остатка в вычитателе 11. На подготовительном этапе деления формируется произведение делителя у на значение старших (k+2) разрядов обратной величины w у-с(. При выполнении собственно деления следующий остаток вычисляется

разряды остатка х при приведении его

0

х( . Параллельно

5

0

5

по формуле х х - w с вычислением остатка в сумматоре 4 частного производится накапливание промежуточного значения частного х, являющегося суммой всех ( р), полученных на каждом такте работы устройства и сдвинутых один относительно другого на (k-1) разрядов. После выполнения собственно деления значение х умножается на значение с(. Старшие n-р азрядов этого произведения и являются значением частного z.

Регистр 8 старших разрядов делителя (k+З)-разрядный и предназначен для хранения у (старших (k+З) разрядов делителя у без знака). Запись информации в регистр производится по синхроимпульсу при наличии разрешающего потенциала.

Сумматор 9 принудительного округления делителя является комбинационной схемой. В нем осуществляется принудительное округление значения старших (k+J) разрядов делителя у, путем прибавления единицы в его младший разряд, поступающей на вход переноса сумматора 9 принудительного округления делителя через вход 20 логической 1 устройства (т.е. в сумматоре 9 вычисляется значение ). На выходах 28 сумматора

9образуется значение старших разрядов делителя, увеличенное на единицу младшего разряда. Этим самым устраняется возможность получения на выходе 21 частного устройства частного с избытком. Узел 10 вычисления обратной величины производит вычисление значения старших (k+2)- разрядов обратной величины с, от принудительно округленного значения старших разрядов делителя, поступающего на входы узла

10с выходов 28 сумматора 9 принудительного округления делителя. На выходах 29 узла 10 вычисления обратной в-еличины формируется значение старших (k+2) разрядов обратной величины принудительно округленного усеченного делителя. В данном случае предполагается реализация узла 10 совместно с сумматором 9 принудительного округления делителя на ПЗУ.

С помощью вычитателя 11 производится вычитание из значения поразрядных разностей двухрядного кода остатка, поступающих на входы уменьшаемого вычитателя 11 с выходов 23 разрядов первого регистра 1 остатка, значений поразрядных заемов двухрядного кода остатка, поступающих на входы вычитаемого вычитателя 11 с выходов 24 разрядов второго регистра 2 остатка, в результате чего и формируется текущий остаток в однорядном коде, который поступает на выход 34 вычитателя 11, а на последнем такте работы устройства остаток от деления поступает и на выход 22 остатка устройства. Вычитатель 11 комбинационного типа с ускоренным распространением заема может быть заменен быстродействующим сумматором, если информацию, поступающую на его входы вычитаемого, проинвертировать, а на вход переноса сумматора подать сигнал логической 1.

Вычитатель 12 комбинационного тип ос уществляет преобразование (k+5)

0

5

0

5

0

5

0

5

0

5

старших разрядов двухрядного кода остатка, хранящегося в регистрах 1 и 2 остатка, в однорядный код (два разряда слева от запятой и (k+3)-ro разряда справа от запятой). При этом в вы- читателе 12 осуществляется принудительное уменьшение значения усеченного остатка на единицу младшего разряда, поступающую на вход заема вычитателя 12 через вход 20 логической единицы устройства, в результате чего формируется значение . На выходах

30младших разрядов вычитателя 12 образуется однорядный код (k+4) старших разрядов остатка (один разряд слева от запятой и (k+3)-ro разряда справа от запятой), а на выходе 31 старшего разряда вычитателя 12 образуется старший разряд остатка. Так как в устройстве при формировании частного используются старшие разряды остатка, полученные при приведении

на вычитателе 12 к однорядному коду старших разрядов двухрядного кода остатка и принудительно уменьшенные на единицу младшего разряда, становится возможным образование неправильного значения частного.

Так, если значение старших разрядов приведенного отстатка, полученного на выходах 34 вычитателя 11, равно нулю, то при формировании однорядного кода старших разрядов остатка путем приведения к однорядному коду старших разрядов двухрядного кода остатка, принудительно уменьшенных на единицу младшего разряда, возможно получение зна чения разности на выходах 30 младших разрядов вычитателя 12, меньшего, чем нуль, на единицу младшего разряда, т.е. значения 1, 1 ... 1. Но в этом случае на выходе 31 старшего разряда вычитателя 12 формируется единица, а в случае, если значение старших разрядов приведенного остатка, полученного на выходах 34 вычитателя 11, не равно нулю, на выходе 31 старшего разряда вычитателя 12 формируется логический О. Для исключения возможности получения в первом случае неверного значения частного в устройстве предусмотрена блокировка (формирование значения старших разрядов остатка х, -р, равного нулю). Это производится путем подачи на инверсный вход элемента И 16 единичного сигнала с выхода

31старшего разряда вычитателя 12.

915

В этом случае на выходе 32 элемента И 16, независимо от значения сигнала на его прямом входе, формируется сигнал логического О, который запре- щает прохождение значения х,-р с информационных входов второй группы коммутатора 7 на его выходы 33 (фор- , мируется значение О, О ... 0). В случае когда на инверсный вход элемента И 16 подается сигнал логического О с выхода 31 старшего разряда вычита- теля 12, а на прямой вход элемента И 16 подается сигнал логической 1 с выхода 45 блока 17 управления, значение разрядов остатка () с информационных входов второй группы коммутатора 7 поступает на его выходы 33.

В вычитателе 13 осуществляется вычитание из , сформированного в однорядном коде на выходах 34 вычитателя 11, произведения, образованного в двухрядном коде на выходах 38 и 39 первой и второй групп блока 14 умножения. Результат этого вычитания является очередным остатком и получается на выходах 40 и 41 первой и второй групп вычитателя 13 в двухрядном коде. Вычитатель 13 комбинационного типа и выполнен по принципу запоминания заема.

Блок 14 умножения производит умножение содержимого регистра 3 делителя на значение величины, сформированной ня выходах 33 третьего коммутатора 7. На его выходах 38 и 39 первой и второй групп образуется произведение в двухрядном коде (в виде двух чисел). Блок 14 умножения - комбинационного типа.

Сумматор 15 комбинационного типа с ускоренным распространением переноса осуществляет приведение двухрядного кода произведения, поступающего на зходы первого и второго слагаемых сумматора 15 с выходов 38 и 39 первой и второй групп блока 14 умножения соответственно к однорядному коду. Однорядный код произведения с выходов 42 сумматора поступает на информационные входы третьей группы коммутатора 6, а на последнем такте работы устройства однорядный код произведения является частным, которое поступает на выход 21 частного устройства.

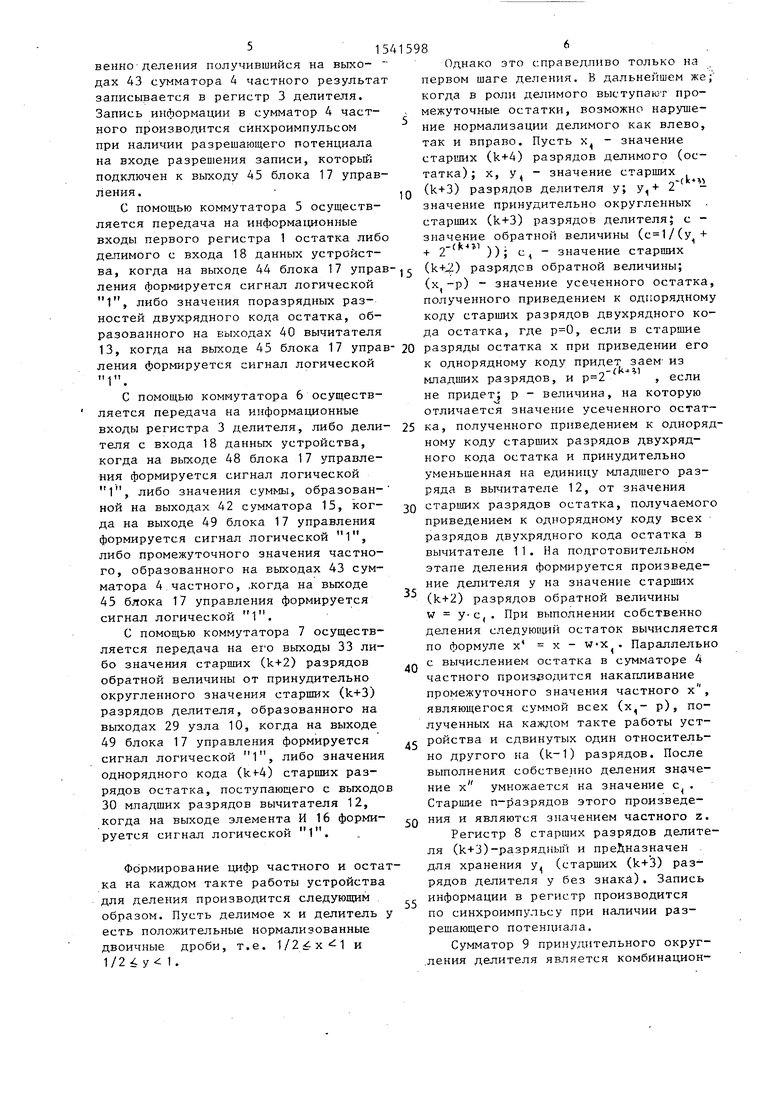

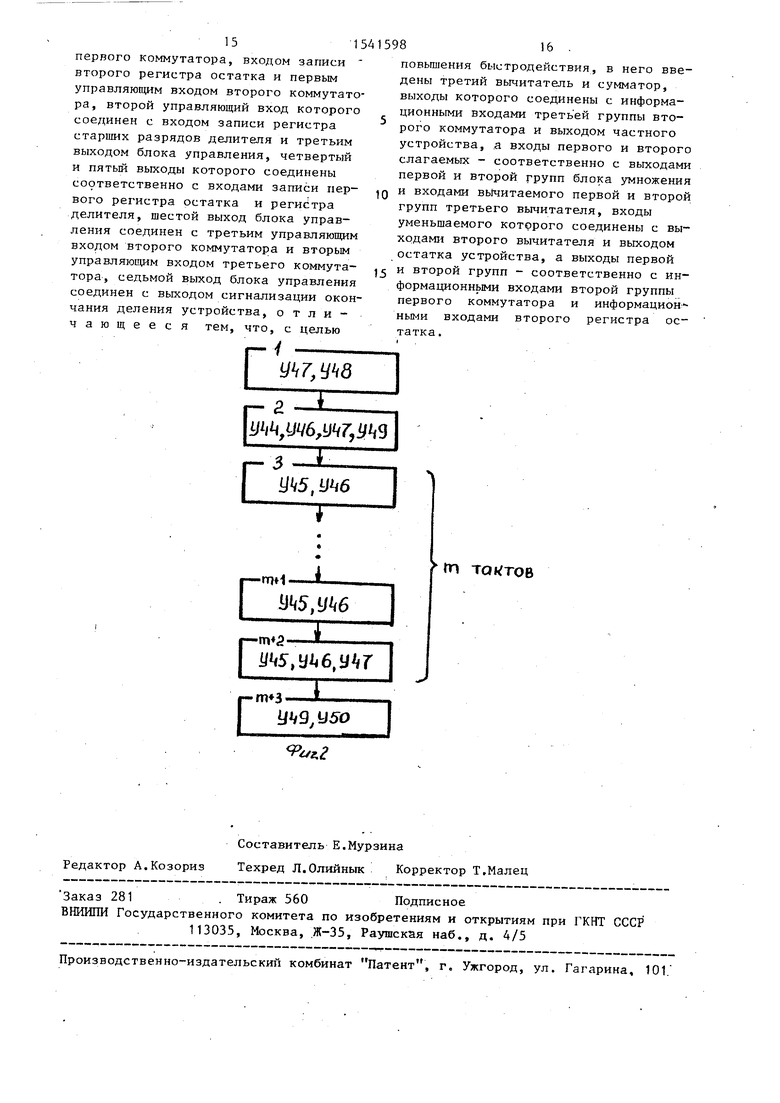

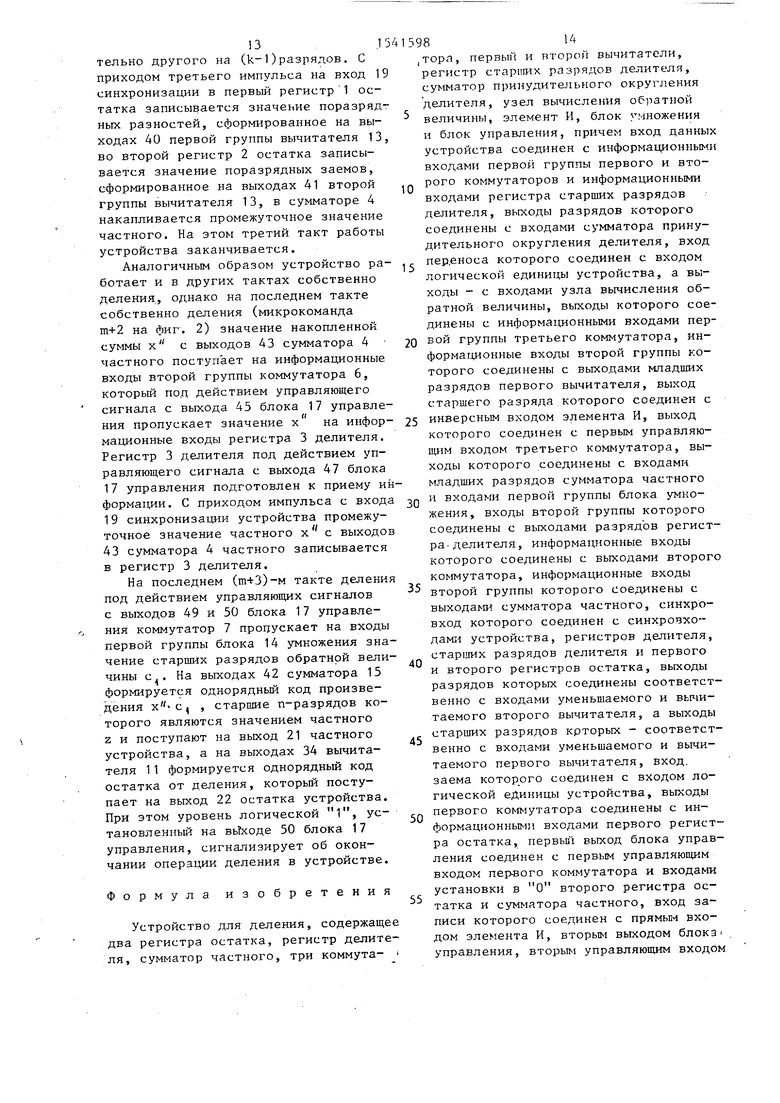

Блок 17 управления координирует работу узлов и блоков устройства при

598Ю

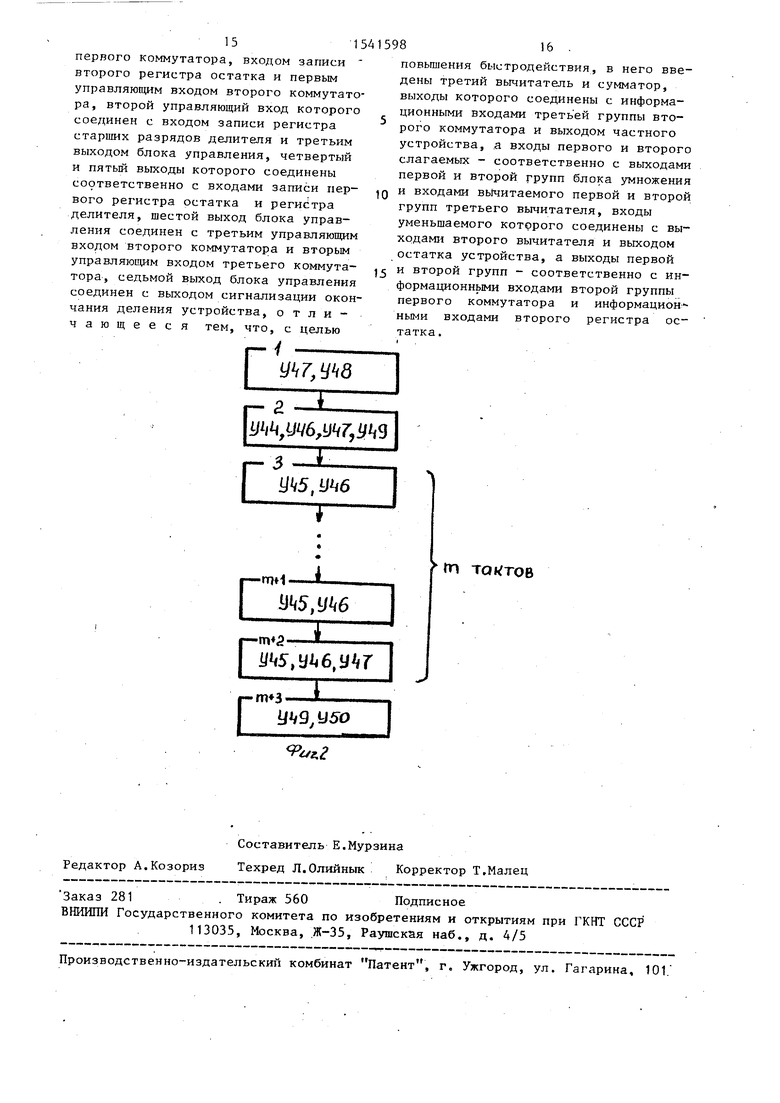

выполнении в нем операции деления чисел. Микропрограмма работы устройства представлена на фиг, 2.

Устройство для деления работает следующим образом.

Пусть на вход 18 данных устройства уже поступил n-разрядный двоичный код делителя у (делимое х и делитель

Q у - правильные нормализованные положительные дроби). Под действием.управляющих сигналов с выходов 47 и 48 блока 17 управления коммутатор 6 пропускает на информационные входы ре5 гис-тра 3 делителя делитель у с входа 18 данных устройства, а регистр 3 делителя и регистр 8 старших разрядов делителя подготовлены к приему информации, так как на их входах разреше0 ния записи присутствуют потенциалы логической 1. С приходом первого импульса на вход 19 синхронизации устройства производится запись двоичного кода делителя у в регистр 3 дели5 теля и двоичного кода старших разрядов делителя у в регистр 8 старших разрядов делителя. С момента окончания синхроимпульса заканчивается пер- вый такт работы устройства.

0 Во втором такте работы устройства под действием управляющих сигналов с выходов 44, 46, 47 и 49 блока 17 управления коммутатор 5 пропускает на на информационные входы первого регистра 1 остатка делимое х с входа 18 данных устройства, первый регистр 1 остатка подготовлен к приему информации, третий коммутатор 7 пропускает на входы первой группы блока 14 умножения значение старших разрядов обратной величины с , сформированное на выходах 29 узла 10 вычисления обратной величины по значению принудительно округленных в сумматоре 9 принудительного округления делителя старших разрядов делителя у( . хранящихся в регистре 8 старших разрядов делителя. На выходах 38 и 39 первой и второй групп блока 14 умножения формируется произведение

Q n-разрядного делителя у на значение с, (w сд-у) в двухрядном коде, которое приводится к однорядному коду с помощью сумматора 15. Под действием управляющего сигнала с выхода 49 блока 17 управления коммутатор 6 пропус« кает на информационные входы регистра 3 делителя значение этого произведения w в однорядном коде с выходов 42 сумматора 15. Под действием управляю5

0

5

5

П15

щего сигнала с выхода 47 блока 17 управления регистр 3 делителя подготовлен к приему информации. Кроме этого, сумматор 4 частного и второй регистр 2 остатка настроены на обну ление. С приходом второго импульса на вход 17 синхронизации устройства производится запись двоичных кодов делимого х и произведения w в регистры соответственно 1 и 3, а также обнуление сумматора 4 частного и второг регистра 2 остатка. С момента окончания действия второго импульса на входе 19 синхронизации устройства заканчивается второй такт и вместе с ним подготовительный этап работы устройства и начинается собственно деление, в процессе которого в течение m тактов формируется m(k-1)+5l двоичных цифр промежуточного значения частного.

В первом такте собственно деления под действием управляющих сигналов с выходов 45 и 46 блока 17 управления коммутатор 5 пропускает на информационные входы первого регистра 1 остатка значение поразрядных разностей с выходов 40 первой группы вычитателя 13, первый 1 и второй 2 регистры остатка и сумматор 4 частного подготовлены к приему информации. Если сигнал на выходе 31 старшего разряда вычи- та.теля 12 соответствует уровню логического О, то, так как на прямом входе элемента И 16 присутствует единичный сигнал с выхода 45 блока 17 управления, коммутатор 7 пропускает на входы первой группы блока 14 умножения значение разрядов остатка ix,-p с выходов 30 младших разрядов вычитателя 12. Если же сигнал на выходе 31 старшего разряда вычитателя 12 соответствует уровню логической 1, то коммутатор 7 формирует на выходах 33 значение, равное нулю. Это позволяет произвести в устройстве следуюшле вычисления. На выходах 38 и 39 первой и второй групп блока 14 умножения формируется в двухрядном коде произведение, величины w у-с, , хранящейся в регистре 3 делителя и поступающей на входы второй группы блока 14 умножения с выходов 37 разрядов регистра 3 делителя, на значение разрядов остатка (), поступающих на входы первой группы блока 14 умножения, формируемых в вычита- теле 12 по значению старших разрядов

59812

двухрядного кода остатка, поступающего на входы уменьшаемого и вычитаемого вычитателя 12 с выходов 25 и 26 старших разрядов соответственно первого 1 и второго 2 регистров остатка.

При этом в вычитателе 12 производится принудительное уменьшение значения старших разрядов остатка на единицу младшего разряда. В результате этого на выходах 38 и 39 блока 14 умножения образуется значение (x,-p).yic,, в двухрядном коде. Одно5 временно с этим на выходах 34 вычитателя 11 формируется значение предыдущего остатка в однорядном коде по значению поразрядных разностей и поразрядных заемов, хранящихся соот0 ветственно в первом 1 и втором 2 регистрах остатка и поступающих на входы уменьшаемого и вычитаемого вычитателя 11 с выходов 23 и 24 разрядов первого 1 и второго 2 регистров

5 остатка. Значение текущего остатка в двухрядном коде формируется в вычитателе 13 по значению предыдущего остатка х в однорядном коде, поступающему на входы уменьшаемого вычитате0 ля 13 с выходов 34 вычитателя 11, и значению произведения (х -р)-У С, в двухрядном коде, поступающему на входы вычитаемого первой и второй групп вычитателя 13 с выходов 38 и 39 первой и второй групп блока 14 умножения соответственно.

Значение текущего остатка х - (х,-р)«У С в двухрядном коде поступает с выходов 40 и 41 первой и второй групп вычитателя 13 со сдвигом на (k-1) разрядов в сторону старших разрядов на информационные входы второй группы первого коммутатора 5 и информационные входы второго рес гистра 2 остатка соответственно. Параллельно с работой блока 14 умножения и вычитателя 13 значение старших разрядов остатка (xt-p) поступает на информационные входы младших разрядов

0 сумматора 4 частного с выходов 33 коммутатора 7 и подсуммируется к младшим разрядам его старших разрядов (на первом такте собственно деления в устройстве сумматор 4 частного обнулен). В результате в сумматоре 4 частного накапливается промежуточное значение частного х, как сумма (х,-р) полученных на каждом такте собственно деления и сдвинутых один относи5

0

5

1315

тельно другого на (k-1)разрядов. С приходом третьего импульса на вход 19 синхронизации в первый регистр 1 остатка записывается значение поразрядных разностей, сформированное на выходах 40 первой группы вычитателя 13, во второй регистр 2 остатка записывается значение поразрядных заемов, сформированное на выходах 41 второй группы вычитателя 13, в сумматоре 4 накапливается промежуточное значение частного. На этом третий такт работы устройства заканчивается.

Аналогичным образом устройство работает и в других тактах собственно деления, однако на последнем такте собственно деления (микрокоманда т+2 на фиг. 2) значение накопленной суммы х с выходов 43 сумматора 4 частного поступает на информационные входы второй группы коммутатора 6, который под действием управляющего сигнала с выхода 45 блока 17 управления пропускает значение х на информационные входы регистра 3 делителя. Регистр 3 делителя под действием управляющего сигнала с выхода 47 блока 17 управления подготовлен к приему информации. С приходом импульса с входа 19 синхронизации устройства промежуточное значение частного х с выходов 43 сумматора 4 частного записывается в регистр 3 делителя.

На последнем (пН-З)-м такте деления под действием управляющих сигналов с выходов 49 и 50 блока 17 управления коммутатор 7 пропускает на входы первой группы блока 14 умножения значение старших разрядов обратной величины с . На выходах 42 сумматора 15 формируется однорядный код произведения х;/ с , старшие n-разрядов которого являются значением частного z и поступают на выход 21 частного устройства, а на выходах 34 вычитателя 11 формируется однорядный код остатка от деления, который поступает на выход 22 остатка устройства. При этом уровень логической 1, установленный на вьЬсоде 50 блока 17 управления, сигнализирует об окончании операции деления в устройстве.

Формула изобретения

Устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, три коммута-

10

15

159814

(тора, первый и второй вычитатели, регистр старших разрядов делителя, сумматор принудительного округления делителя, узел вычисления обратной

5 величины, элемент И, блок умножения и блок управления, причем вход данных устройства соединен с информационными входами первой группы первого и второго коммутаторов и информационными входами регистра старших разрядов делителя, выходы разрядов которого соединены с входами сумматора принудительного округления делителя, вход пер.еноса которого соединен с входом логической единицы устройства, а выходы - с входами узла вычисления обратной величины, выходы которого соединены с информационными входами пер20 вой группы третьего коммутатора, информационные входы второй группы которого соединены с выходами младших разрядов первого вычитателя, выход старшего разряда которого соединен с

25 инверсным входом элемента И, выход которого соединен с первым управляющим входом третьего коммутатора, выходы которого соединены с входами младших разрядов сумматора частного

OQ и входами первой группы блока умножения, входы второй группы которого соединены с выходами разрядов регистра-делителя, информационные входы которого соединены с выходами второго коммутатора, информационные входы второй группы которого Соединены с выходами сумматора частного, синхро- вход которого соединен с синхровхо- дами устройства, регистров делителя, старших разрядов делителя и первого и второго регистров остатка, выходы разрядов которых соединены соответственно с входами уменьшаемого и вычитаемого второго вычитателя, а выходы старших разрядов крторых - соответственно с входами уменьшаемого и вычитаемого первого вычитателя, вход, заема которого соединен с входом логической единицы устройства, выходы

35

40

45

первого коммутатора соединены с информационными входами первого регистра остатка, первый выход блока управления соединен с первым управляющим входом первого коммутатора и входами установки в О второго регистра остатка и сумматора частного, вход записи которого соединен с прямым входом элемента И, вторым выходом блокаi управления, вторым управляющим входом

1515

первого коммутатора, входом записи второго регистра остатка и первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с входом записи регистра старших разрядов делителя и третьим выходом блока управления, четвертый и пятый выходы которого соединены со9тветственно с входами записи первого регистра остатка и регистра делителя, шестой выход блока управления соединен с третьим управляющим входом второго коммутатора и вторым управляющим входом третьего коммутатора, седьмой выход блока управления соединен с выходом сигнализации окончания деления устройства, отличающееся тем, что, с целью

с

f

УЬ7,Мд

с

±

УМ,УЧ6&1799Ю

г

1

м, 1Лб

ГтИ-

J.

Л5,

MS

I

М5,УЬ6,МТ

Г

ЦЬ9,У50

Ъъг

повышения быстродействия, в него введены третий вычитатель и сумматор, выходы которого соединены с информационными входами третьей группы второго коммутатора и выходом частного устройства, а входы первого и второго слагаемых - соответственно с выходами первой и второй групп блока умножения

и входами вычитаемого первой и второй групп третьего вычитателя, входы уменьшаемого которого соединены с выходами второго вычитателя и выходом остатка устройства, а выходы первой

и второй групп - соответственно с информационными входами второй группы первого коммутатора и информацией ными входами второго регистра остатка .

т тактов

| Карцев М.А.,„Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Советское радио, 1981, с | |||

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-06—Подача