Изобретение относится к вычислительной технике и может быть использовано для повышения четкости изображения, поступающего с видеодатчика, при движении видеодатчика или нахождении в кадре движущихся объектов.

Известен способ устранения размытости изображения вследствие движения объектов на цифровом изображении (Tull D.L. Preventing blur caused by motion of the subject in a digital image, 2002, патент США №6441848). Способ включает в себя получение изображения матричным фоточувствительным приемником излучения (МФПИ) в течение заданного времени накопления; вычисление значения переменной, пропорциональной интенсивности потока излучения для каждого пикселя; вычисление второй производной указанной переменной для каждого пикселя; сравнения значения второй производной указанной переменной с пороговым значением, достижение которого соответствует обнаружению движения; вычисление времени накопления для каждого пикселя в процентном соотношении к текущему времени накопления; изменение времени накопления для каждого пикселя согласно вычисленному значению процентного соотношения.

Недостатками данного способа являются:

- наличие искажений на результирующем изображении, вызванных перепадами яркости на границах областей с различным временем накопления;

- его неприменимость для приемников изображения на основе приборов с зарядовой связью (ПЗС), для которых невозможно изменение времени накопления каждого пикселя в отдельности.

Известно устройство, реализующее функцию устранения размытости изображения вследствие движения объектов на цифровом изображении (Tull D.L. Preventing blur caused by motion of the subject in a digital image, 2002, патент США №6441848), содержащее матричный фоточувствительный приемник излучения, в состав каждого элементарного фотосенсора (ЭФ) которого входит схема определения движения; фокусирующую линзу; схему памяти, подключенную к матричному фоточувствительному приемнику излучения, которая хранит значения времени накопления для каждого элементарного фотосенсора.

Недостатками данного устройства являются:

- высокая сложность его технологического исполнения, связанная с необходимостью встраивания в каждый пиксель схемы определения движения;

- снижение коэффициента заполнения пикселя (отношение светочувствительной поверхности пикселя к его общей площади) вследствие встраивания в каждый пиксель схемы определения движения, что приводит к снижению чувствительности устройства и повышению уровня геометрического шума и шума фиксированной разводки.

Наиболее близким к изобретению является способ компенсации размытости изображения, вызванной движением или насыщением элементарного фотосенсора, с одновременным расширением динамического диапазона на основе синтеза изображения по серии кадров (Liu et. all, Motion/saturation detection system and method for synthesizing high dynamic range motion blur free images from multiple captures, 2006, патент США №7061524). Согласно способу рассчитывают разность между измеренной яркостью пикселей изображения и ранее полученной ее оценкой на основе последовательности предыдущих кадров, обнаруживают движение путем сравнения полученной разности с пороговой величиной, при отсутствии движения принимают полученные измерения яркости за истинное изображение, при наличии движения измеренные значения яркости корректируются на основе полученных оценок.

Основным недостатком данного способа является обработка как минимум четырех кадров для получения изображения с достаточной степенью компенсации размытости, что накладывает значительные ограничения на быстродействие устройства, реализующего способ, и в некоторых случаях вследствие формирования современными видеодатчиками изображений с большой разрешающей способностью приводит к невозможности функционирования устройства в режиме реального времени.

Наиболее близким к предлагаемому является устройство компенсации размытости изображения, вызванной движением или насыщением ЭФ (Liu et. all, Motion/saturation detection system and method for synthesizing high dynamic range motion blur free images from multiple captures, 2006, патент США №7061524). Устройство состоит из: датчика изображения, каждый ЭФ которого содержит средства обнаружения движения/насыщения между предыдущим кадром и текущим кадром; блока обработки, определяющего, принимать ли для каждого ЭФ выборку изображения, зафиксированную в течение текущего кадра; блока оценки яркости в течение глобального времени экспозиции; блока определения разности между измеренной яркостью, полученной во время текущего кадра, и оценкой яркости, сгенерированной в течение предыдущего кадра, для каждого ЭФ; блока сравнения вычисленной разности с пороговым значением для каждого ЭФ; блока модификации оценки яркости для каждого ЭФ; блока формирования выходного изображения на основе заключительной оценки яркости для каждого ЭФ.

Недостатком данного устройства является низкий коэффициент заполнения пикселя (не более 10%), что существенно ухудшает чувствительность видеодатчика, высокая сложность его технологического исполнения и высокая структурная сложность, связанные с необходимостью встраивания в каждый пиксель схемы обнаружения движения.

Технической задачей изобретения является компенсация размытости изображения движущихся объектов в режиме реального времени для МФПИ любого типа (ПЗС, на основе полупроводниковых комплементарных пар металл-оксид-полупроводник (КМОП)) с одновременным снижением технологического исполнения устройства и снижением его структурной сложности.

Задача решается тем, что в известный способ компенсации размытости изображения, вызванной движением, включающий определение межкадровой разности яркости изображения, определение движения для каждого пикселя изображения, корректировку яркости только движущихся пикселей, согласно изобретению введены определение направления движения для каждого пикселя путем обработки смежных кадров скользящим окном 3×3 элемента и анализа суммарных значений элементов межкадровых разностей, объединение движущихся в одном направлении смежных пикселей в объект на основе анализа расстояния между двумя пикселями с одинаковым направлением движения, подчеркивание контуров движущихся объектов путем сложения исходного изображения движущегося объекта с его градиентным изображением.

Техническая задача решается тем, что в устройство, содержащее датчик изображения, введены контроллер, модуль обнаружения движения МОД, модуль определения объектов, модуль коррекции, первое ОЗУ, второе ОЗУ, третье ОЗУ, счетчик, элемент ИЛИ, первый компаратор, второй компаратор, первая константа, вторая константа, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, пятый мультиплексор, шестой мультиплексор, седьмой мультиплексор, первый демультиплексор, второй демультиплексор, третья константа.

Изобретение может быть использовано для компенсации размытости изображения движущихся объектов в режиме реального времени в различных видеодатчиках и системах технического зрения, выполненных на базе твердотельных МФПИ различных типов.

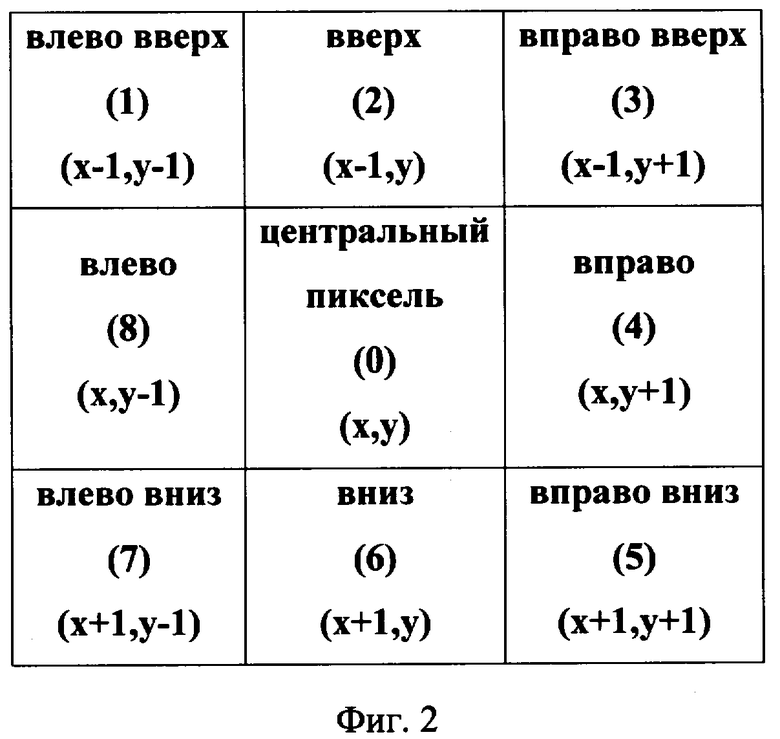

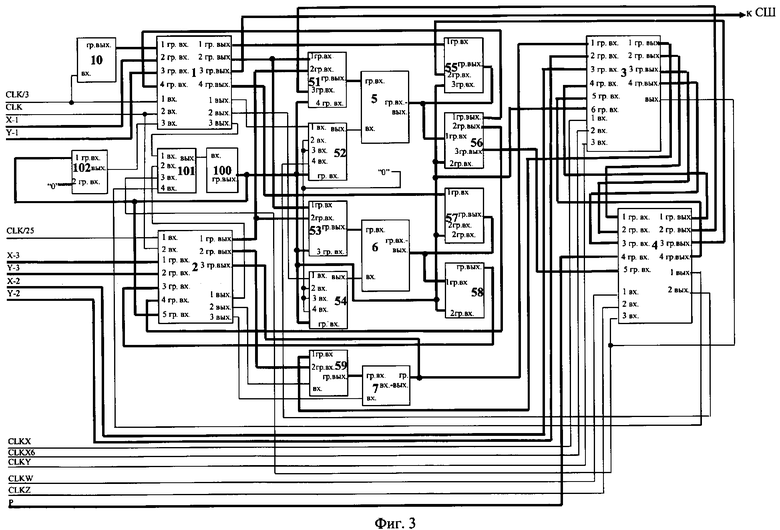

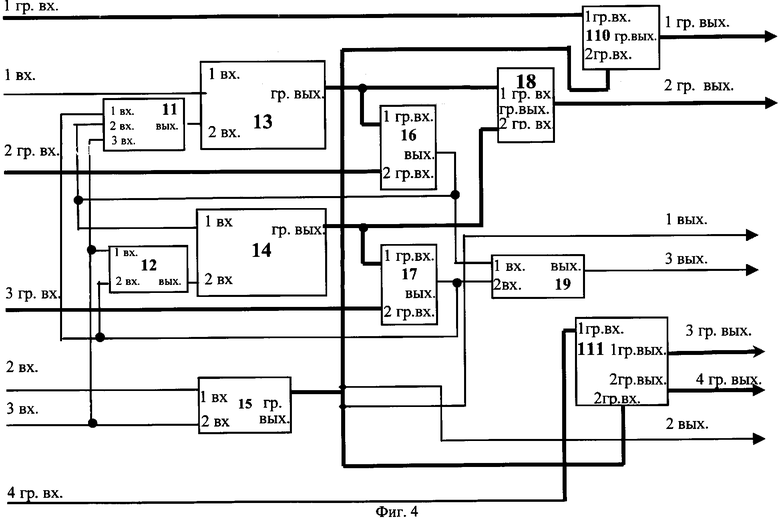

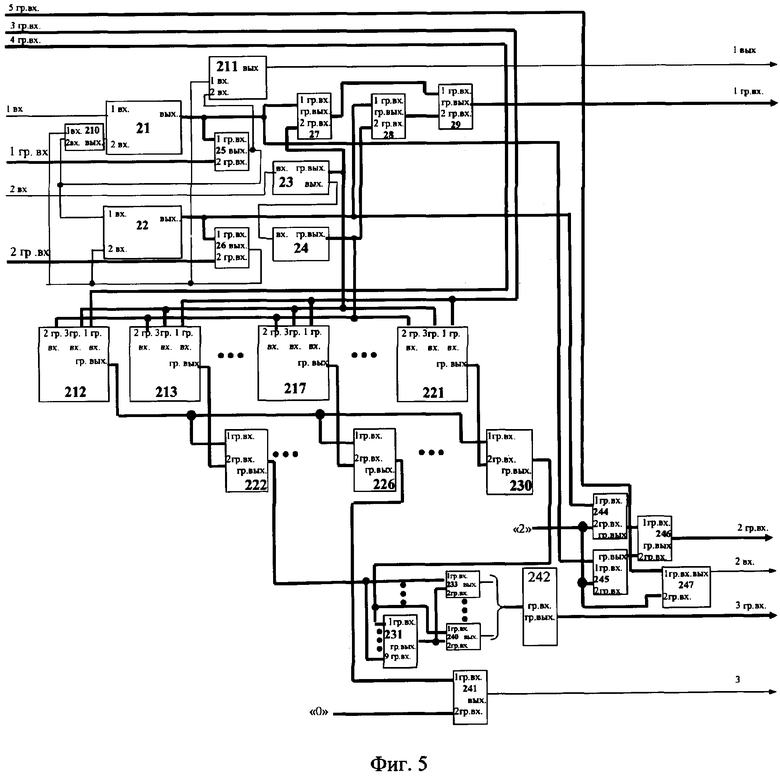

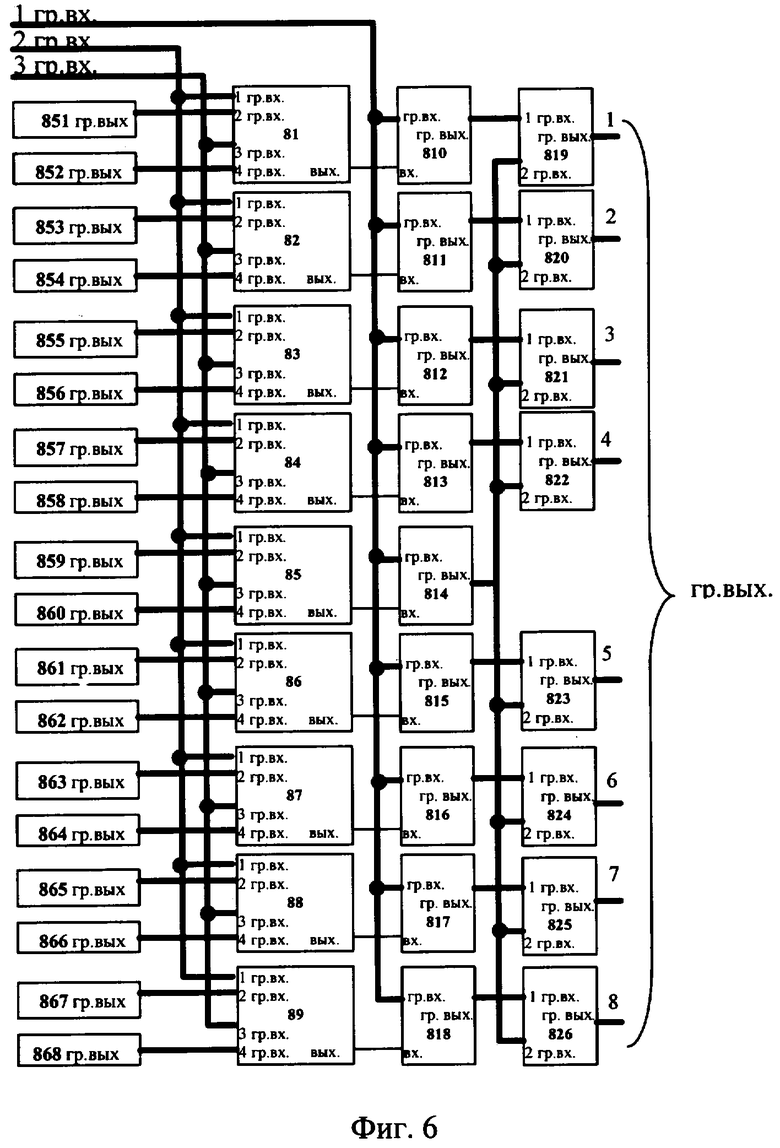

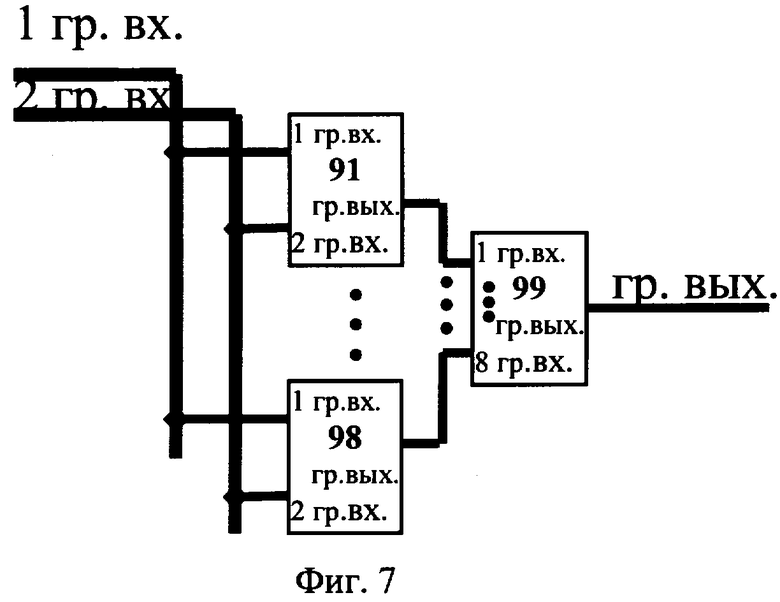

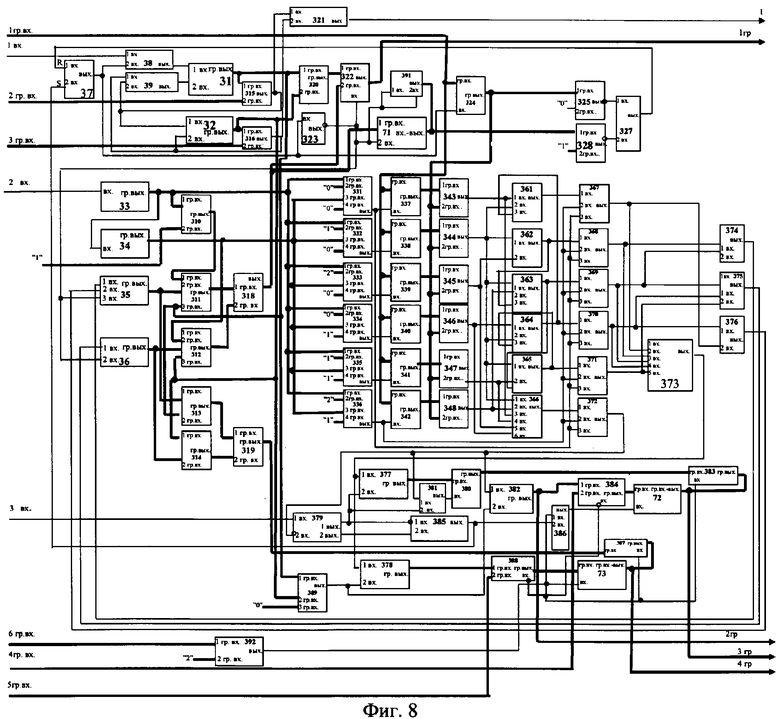

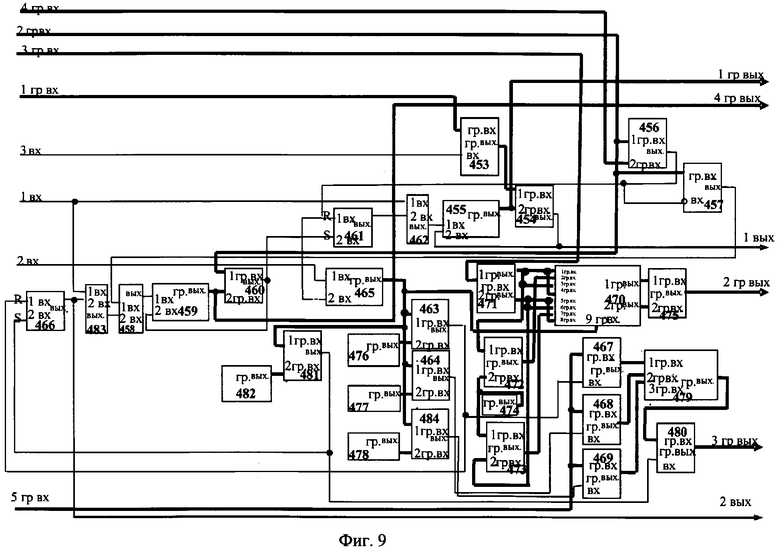

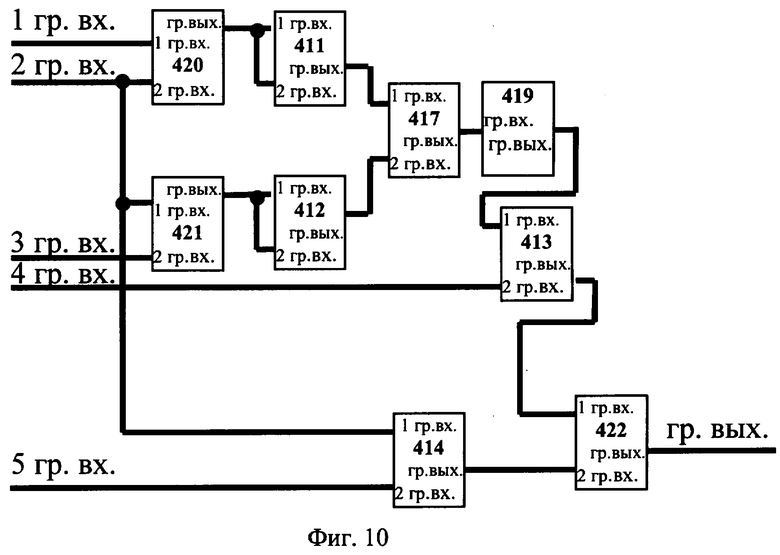

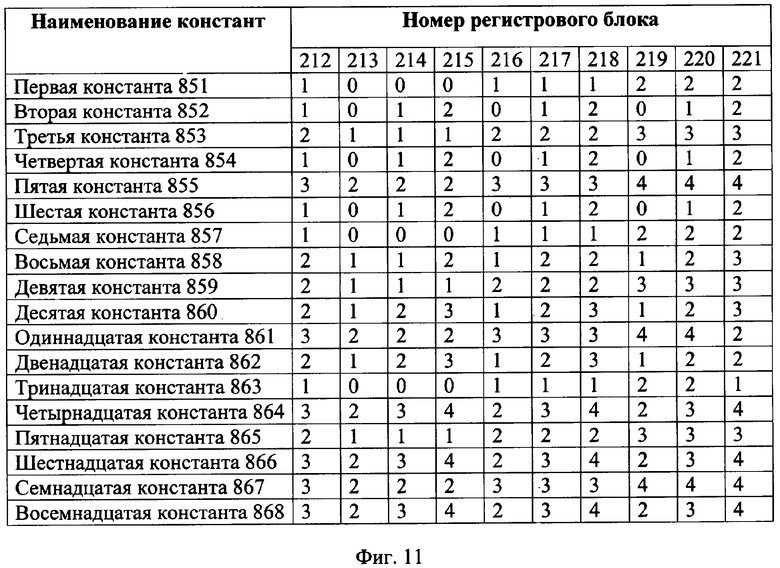

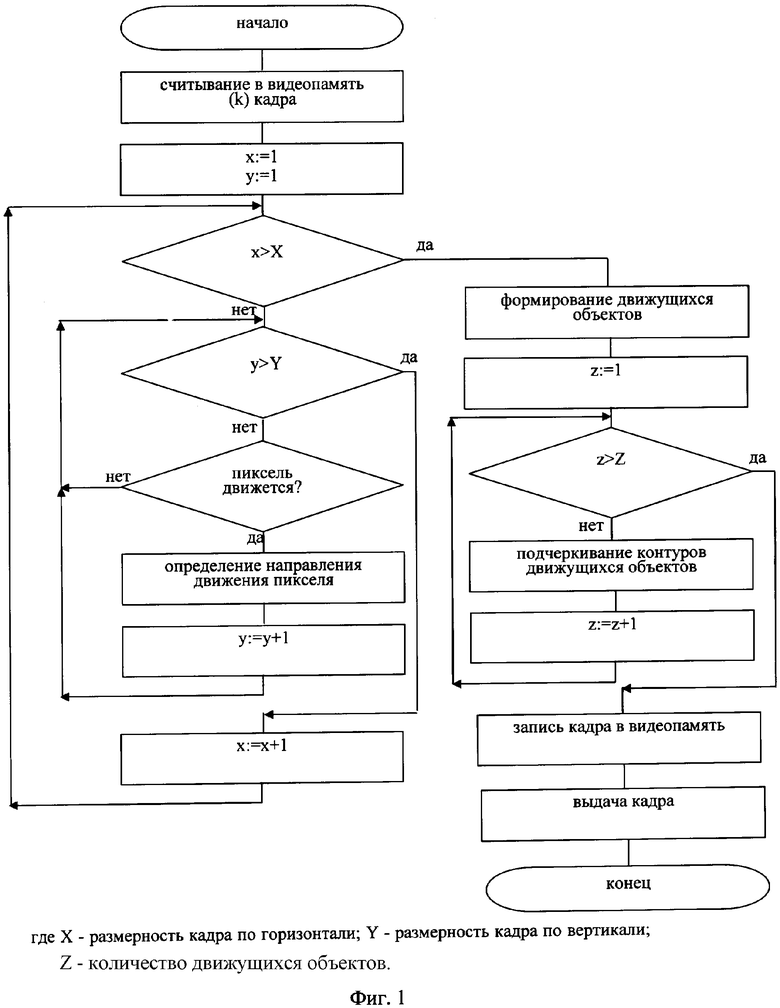

Сущность изобретения поясняется чертежами, где на фиг.1 приведен алгоритм способа компенсации размытости изображения, на фиг.2 - коды направления перемещения пикселя в восьмисвязной окрестности, на фиг.3 - структурная схема устройства компенсации размытости изображения движущихся объектов, на фиг.4 - структурная схема контроллера, на фиг.5 - структурная схема модуля обнаружения движения, на фиг.6 - структурная схема регистрового блока, на фиг.7 - структурная схема суммирующего блока, на фиг.8 - структурная схема модуля определения объектов, на фиг.9 - структурная схема модуля коррекции, на фиг.10 - структурная схема модуля подчеркивания контуров, на фиг.11 - значения констант регистрового блока.

Процесс компенсации размытости изображения (фиг.1) состоит из нескольких этапов: считывание изображения, выделение на изображении движущихся пикселей на основе анализа межкадровой разности, определение направления движения каждого пикселя, объединение движущихся в одном направлении смежных пикселей в объект, подчеркивание контуров движущихся объектов для компенсации размытия изображения путем сложения их исходного и градиентного изображений, формирование выходного изображения.

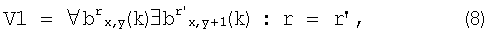

Движение каждого пикселя относительно текущего k-го кадра определяется по принципу межкадрового вычитания: значение разности яркостей статичных пикселей на смежных кадрах равно 0 (при условии неизменной освещенности). Расчет производится для восьмисвязной окрестности каждого пикселя, каждому из восьми возможных направлений движения присваивается определенный код.

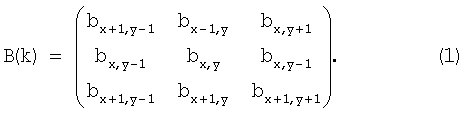

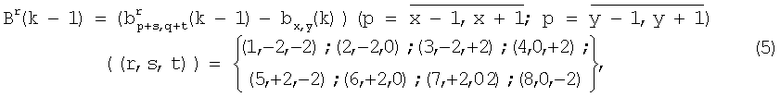

Для определения номера направления перемещения r (фиг.2) каждого пикселя (х,у) кадр обрабатывается скользящим окном размера 3×3 следующим образом: для каждого пикселя (х,у) текущего кадра составляется матрица яркости В(k) смежных с ним пикселей по 8 направлениям:

Элементы матрицы В(k), индексы которых равны 0, (Х+1) или (Y+1), принимаются равными 0, где X, Y - размеры кадра по горизонтали и вертикали соответственно.

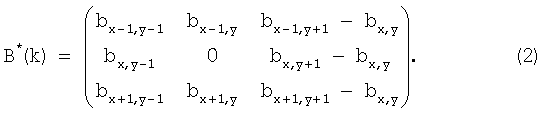

Далее матрица В(k) преобразуется в матрицу В*(k) путем вычитания из яркостей смежных пикселей яркости центрального пикселя:

Данное преобразование позволяет учесть возможные изменения внешней освещенности сцены с одним и тем же расположением объектов в текущем кадре относительно предыдущего кадра.

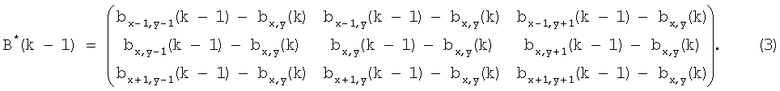

Аналогичным образом для обработки предыдущего (k-1)-го кадра составляется матрица В*(k-1):

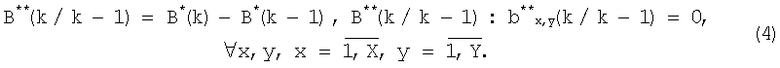

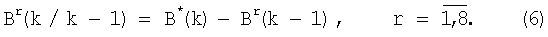

Результат вычитания матрицы B*(k-1) из матрицы В*(k) позволяет судить о том, остался ли центральный пиксель неподвижным на смежных кадрах, если равен нулю центральный пиксель результирующей матрицы В**(k/k-1), т.е. выполняется следующее условие:

Если центральный пиксель результирующей матрицы В**(k/k-1) не равен 0, делается вывод о движении данного пикселя.

Далее производится определение направления движения каждого пикселя. Для этого из матрицы B*(k-1) формируются 8 матриц, сдвинутых на 1 пиксель по каждому из 8 направлений (недостающие строки и/или столбцы заполняются нулями). Матрицы определения перемещения центрального пикселя на текущем кадре относительно предыдущего задаются в общем виде следующим образом:

Для формирования 8 результирующих матриц перемещений по каждому из 8 направлений необходимо вычесть каждую матрицу определения направления из матрицы В*(k). Результирующие матрицы яркости изображения, вычисляющие перемещение пикселя на текущем кадре, задаются в общем виде следующим образом:

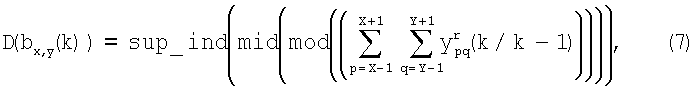

За направление движения пикселя принимается то направление, для которого суммарное значение изменений яркости (сумма всех элементов результирующих матриц) по модулю является минимальным.

где sup_ind(*) - функция, значением которой является величина верхнего индекса матрицы Вr(k/k-1).

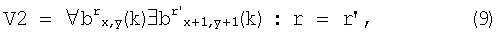

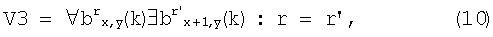

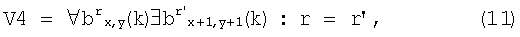

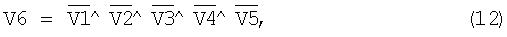

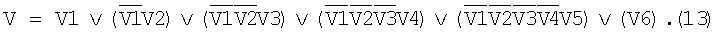

Затем производится определение движущихся объектов. Для этого необходимо найти соседние пиксели с одинаковым направлением движения, поиск которых осуществляется в соответствии с формулами (8)-(13)

Соседние пиксели с одинаковым направлением движения группируются в объекты в соответствие с формулами:

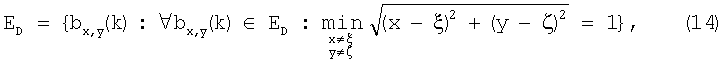

где ξ,ς - координаты пикселя; Np+1 - минимальное количество точек в объекте.

Под объектом ED понимается совокупность отличных от фона точек изображения с направлением движения D, таких, что для каждой точки найдется не менее одной соседней точки, расположенной на расстоянии 1 пиксель, причем количество таких точек в объекте должно превышать пороговое значение Np.

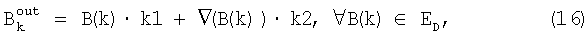

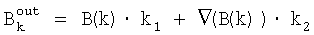

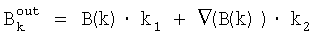

После этого реализуется коррекция яркостей движущихся объектов путем подчеркивания их контуров (сложения исходного изображения с градиентным изображением). Выходные значения яркостей пикселей рассчитывается следующим образом:

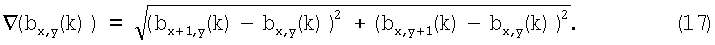

где ▿(bx,y(k)) - градиентное изображение, такое что

Значения яркости статичных областей изображения остаются неизменными.

Устройство компенсации размытости изображения (фиг.3) содержит датчик изображения ДИ 10, контроллер 1, модуль обнаружения движения МОД 2, модуль определения объектов МОО 3, модуль коррекции МК 4, первое ОЗУ 5, второе ОЗУ 6, третье ОЗУ 7, счетчик 100, элемент ИЛИ 101, первый компаратор 102, первый мультиплексор 51, второй мультиплексор 52, третий мультиплексор 53, четвертый мультиплексор 54, пятый мультиплексор 55, шестой мультиплексор 57, седьмой мультиплексор 59, первый демультиплексор 56, второй демультиплексор 58, причем вход CLK/3 предназначен для подачи тактирующего сигнала в ДИ 10 и подключен к первому входу контроллера 1, групповой выход ДИ 10 подключен к первому групповому входу контроллера 1, второй групповой выход контроллера 1 подключен к первым групповым входам первого мультиплексора 51 и третьего мультиплексора 53, групповой выход первого мультиплексора 51 подключен к групповому входу первого ОЗУ 5, групповой вход-выход первого ОЗУ 5 подключен к групповому входу первого демультиплексора 56 и к групповому выходу пятого мультиплексора 55, первый групповой выход демультиплексора 56 подключен к четвертому групповому входу контроллера 1, групповой вход-выход второго ОЗУ 6 подключен к групповому входу второго демультиплексора 58 и к групповому выходу шестого мультиплексора 57, третий групповой выход контроллера 1 подключен к системной шине, четвертый групповой выход контроллера 1 подключен к первому групповому входу шестого мультиплексора 57, первый групповой выход контроллера 1 подключен к первому групповому входу пятого мультиплексора 55, первый выход контроллера 1 подключен к первому входу второго мультиплексора 52, выход второго мультиплексора 52 подключен к входу первого ОЗУ 5, второй выход контроллера 1 подключен к первому входу четвертого мультиплексора 54, выход которого подключен к входу второго ОЗУ 6, второй и третий групповые входы контроллера 1 предназначены для подачи констант (Х-1) и (Y-1) соответственно (где X, Y - размерность изображения по горизонтали и вертикали), второй вход контроллера 1 предназначен для подачи тактового сигнал CLK и соединен со вторым входом МОД 2, третий вход контроллера 1 подключен к выходу первого компаратора 102, первый групповой вход которого подключен к групповому выходу счетчика 100 и пятому групповому входу МОД 2, на второй групповой вход первого компаратора 102 подана константа 0, третий выход контроллера 1 подключен к первому входу элемента ИЛИ 101, первый вход МОД 2 предназначен для подачи тактового сигнала CLK/25, первый и второй групповые входы МОД 2 предназначены для подачи констант (Х-3) и (Y-3) соответственно, третий групповой вход МОД 2 подключен к групповому выходу второго демультиплексора 58, четвертый групповой вход МОД 2 подключен ко второму групповому выходу первого демультиплексора 56, первый групповой выход МОД 2 подключен ко вторым групповым входам первого мультиплексора 51 и третьего мультиплексора 53, второй групповой выход МОД 2 подключен к второму групповому входу седьмого мультиплексора 59, третий групповой выход МОД 2 подключен к групповому входу-выходу ОЗУ 7 и первому групповому входу МОО 3, первый выход МОД 2 подключен к второму входу элемента ИЛИ 101, второй выход МОД 2 подключен к входу седьмого мультиплексора 59, третий выход МОД 2 подключен к входу третьего ОЗУ 7, второй и третий групповые входы МОО 3 предназначены для подачи констант (Х-2) и (Y-2) соответственно, четвертый групповой вход МОО 3 подключен к первому групповому выходу МК 4, пятый групповой вход МОО 3 подключен к четвертому групповому выходу МК 4, шестой групповой вход МОО 3 подключен к групповому выходу счетчика 100, первый, второй и третий входы МОО 3 предназначены для подачи тактовых сигналов CLKX, CLKX6, CLKY соответственно, первый групповой выход МОО 3 подключен к первому групповому входу седьмого мультиплексора 59, групповой выход которого соединен с групповым входом третьего ОЗУ 7, второй групповой выход МОО 3 подключен к первому групповому входу МК 4, третий групповой выход МОО 3 подключен к второму групповому входу МК 4, четвертый групповой выход MOO 3 подключен к третьему групповому входу МК 4, выход МОО 3 подключен к третьему входу элемента ПЛИ 101 и к третьему входу МК 4, четвертый вход элемента ИЛИ 101 подключен к выходу МК 4, второй групповой выход МК 4 подключен к третьему групповому входу первого мультиплексора 51, третий групповой выход МК 4 подключен к второму групповому входу пятого мультиплексора 55, четвертый групповой вход МК 4 предназначен для подачи порогового значения Р, определяющего минимально допустимое количество пикселей в объекте, пятый групповой вход МК 4 подключен к третьему групповому выходу первого демультиплексора 56, первый и второй входы МК 4 предназначены для подачи тактовых сигналов CLKW и CLKZ соответственно, на второй вход второго мультиплексора 52 подана константа 0, групповой выход счетчика 100 подключен к четвертому групповому входу первого мультиплексора 51, групповому входу второго мультиплексора 52, третьему групповому входу третьего мультиплексора 53, пятому групповому входу четвертого мультиплексора 54, третьему групповому входу пятого мультиплексора 55, к второму групповому входу шестого мультиплексора 57, а также к вторым групповым входам первого демультиплексора 56 и второго демультиплексора 58, на второй, третий, четвертый входы четвертого мультиплексора 54 подается константа 0, при этом первый мультиплексор 51 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его четвертом групповом входе, со своего второго группового входа - при значении «1», со своего третьего группового входа - при значении «3», второй мультиплексор 52 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «3», третий мультиплексор 53 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «1», четвертый мультиплексор 54 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его пятом групповом входе, со своего второго группового входа - при значении «1», со своего третьего группового входа - при значении «2», со своего четвертого группового входа - при значении «3», пятый мультиплексор 55 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «3», шестой мультиплексор 57 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его втором групповом входе, первый демультиплексор 56 обеспечивает прохождение сигнала со своего группового входа на первый групповой выход при значении «0» на его втором групповом входе, при значении «1» - на свой второй групповой выход, при значении «3» - на свой третий групповой выход, второй демультиплексор 58 обеспечивает прохождение сигнала со своего группового входа на свой групповой выход при значении «1» на его втором групповом входе, седьмой мультиплексор 59 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его входе, и со второго группового входа - при значении «1».

Контроллер 1 (фиг.4) содержит: первый элемент ИЛИ 11, второй элемент ИЛИ 12, первый счетчик 13, второй счетчик 14, третий счетчик 15, первый компаратор 16, второй компаратор 17, формирователь адреса 18, элемент И 19, буфер 110 и демультиплексор 111, причем первый вход первого счетчика 13 является первый входом контроллера 1 и предназначен для подачи тактового сигнала CLK/3, первый групповой выход первого счетчика 13 подключен к первым групповым входам первого компаратора 16 и формирователя адреса 18, групповой выход формирователя 18 является вторым групповым выходом контроллера 1, второй групповой вход первого компаратора 16 является вторым групповым входом контроллера 1, выход первого компаратора 16 подключен ко второму входу первого элемента ИЛИ 11, к первому входу второго счетчика 14 и к первому входу элемента И 19, групповой выход второго счетчика 14 подключен к второму групповому входу формирователя адреса 18 и к первому групповому входу второго компаратора 17, второй групповой вход компаратора 17 является третьим групповым входом контроллера 1, выход компаратора 17 подключен ко второму входу элемента И 19, к второму входу второго элемента ИЛИ 12 и первому входу первого элемента ИЛИ 11, третий вход первого элемента ИЛИ 11, первый вход второго элемента ИЛИ 12 и второй вход третьего счетчика 15 подключены к третьему входу контроллера 1, первый вход третьего счетчика 15 является вторым входом контроллера 1 и предназначен для подачи тактового сигнала CLK, групповой выход третьего счетчика 15 подключен к второму групповому входу буфера 110 и второму групповому входу демультиплексора 111, первый групповой вход буфера 110 является первым групповым входом контроллера, групповой выход буфера 110 является первым групповым выходом контролера 1, первый групповой вход демультиплексора 111 является четвертым групповым входом контроллера 1, первый групповой выход демультиплексора 111 является третьим групповым выходом контроллера 1, второй групповой выход демультиплексора 111 является четвертым групповым выходом контроллера 1, старший разряд группового выхода третьего счетчика 15 является первым выходом контроллера 1, выход элемента И 19 является третьим выходом контроллера 1, младший разряд группового выхода третьего счетчика 15 является вторым выходом контроллера 1.

Модуль обнаружения движения МОД 2 (фиг.5) включает первый счетчик 21, второй счетчик 22, третий счетчик 23, четвертый счетчики 24, первый компаратор 25, второй компаратор 26, первый сумматор 27, второй сумматор 28, первый формирователь адреса 29, элемент ИЛИ 210, элемент И 211, первый регистровый блок 212, второй регистровый блок 213, третий регистровый блок 214, четвертый регистровый блок 215, пятый регистровый блок 216, шестой регистровый блок 217, седьмой регистровый блок 218, восьмой регистровый блок 219, девятый регистровый блок 220, десятый регистровый блок 221, первый суммирующий блок 222, второй суммирующий блок 223, третий суммирующий блок 223, четвертый суммирующий блок 225, пятый суммирующий блок 226, шестой суммирующий блок 227, седьмой суммирующий блок 228, восьмой суммирующий блок 229, девятый суммирующий блок 230, схема определения минимума 231, третий компаратор 233, четвертый компаратор 234, пятый компаратор 235, шестой компаратор 236, седьмой компаратор 237, восьмой компаратор 238, девятый компаратор 239, десятый компаратор 240, одиннадцатый компаратор 241, шифратор 242, третий сумматор 244, четвертый сумматор 245, второй формирователь адреса 246, двенадцатый компаратор 247, причем первый вход первого счетчика 21 является первым входом МОД 2 и предназначен для подачи тактирующего сигнала с частотой CLK/25, второй вход первого счетчика 21, являющийся входом сброса, подключен к выходу элемента ИЛИ 210, выход первого компаратора 25 подключен ко второму входу элемента ИЛИ 210 и первому входу второго счетчика 22, групповой выход первого счетчика 21 подключен к первому групповому входу первого компаратора 25, первому групповому входу первого сумматора 27 и первому групповому входу четвертого сумматора 245, групповой выход второго счетчика 22 подключен к первому групповому входу второго компаратора 26, первому групповому входу второго сумматора 28 и первому групповому входу третьего сумматора 244, второй групповой вход первого компаратора 25 является первым групповым входом МОД 2 и предназначен для подачи постоянной величины (Х-3), второй групповой вход второго компаратора 26 является вторым групповым входом МОД 2 и предназначен для подачи постоянной величины (Y-3) выход второго компаратора 26 подключен ко второму входу второго счетчика 22, являющимся входом сброса, и к первому входу элемента ИЛИ 210, вход третьего счетчика 23, являющийся вторым входом МОД 2, предназначен для подачи тактового сигнала CLK, групповой выход третьего счетчика 23 подключен ко второму групповому входу первого сумматора 27, выход третьего счетчика 23 подключен к входу четвертого счетчика 24, групповой выход которого подключен к второму групповому входу второго сумматора 28, групповой выход первого сумматора 27 подключен к первому групповому входу первого формирователя адреса 29, а групповой выход второго сумматора 28 подключен ко второму групповому входу первого формирователя адреса 29, выход первого формирователя адреса 29 является первым групповым выходом МОД 2, первый групповой вход первого регистрового блока 212 является четвертым групповым входом МОД 2, третий групповой вход МОД 2 подключен к первым групповым входам второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221, вторые групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к групповому выходу четвертого счетчика 24, третьи групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к групповому выходу третьего счетчика 23, группа выходов первого регистрового блока 212 подключена к первым группам входов первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230, группы выходов второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к вторым групповым входам первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230, групповые выходы первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230 подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому, восьмому, девятому входам блока определения минимума 231, а также к первым групповым входам третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240, вторые групповые входы которых подключены к групповому входу схемы определения минимума 231, групповой выход пятого суммирующего блока 226 подключен к первому групповому входу одиннадцатого компаратора 241, на второй групповой вход которого подается константа 0, выходы третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240 подключены к групповому входу шифратора 242, групповой выход которого является третьим групповым выходом МОД 2, выход одиннадцатого компаратора 241 является третьим выходом МОД 2, вторые групповые входы третьего сумматора 244, четвертого сумматора 245 и двенадцатого компаратора 247 подключены к константе 2, групповые выходы третьего сумматора 244 и четвертого сумматора 245 подключены к групповым входам второго формирователя адреса 246, групповой выход которого является вторым групповым выходом МОД 2, первый групповой вход двенадцатого компаратора 247 является пятым групповым входом МОД 2, входы элемента И 211 подключены к выходам первого компаратора 25 и второго компаратора 26 соответственно, выход элемента И 211 является первым выходом МОД 2.

Каждый регистровый блок 212÷221 (фиг.6) состоит из первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818, первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826, первой константы 851, второй константы 852, третьей константы 853, четвертой константы 854, пятой константы 855, шестой константы 856, седьмой константы 857, восьмой константы 858, девятой константы 859, десятой константы 860, одиннадцатой константы 861, двенадцатой константы 862, тринадцатой константы 863, четырнадцатой константы 864, пятнадцатой константы 865, шестнадцатой константы 866, семнадцатой константы 867, восемнадцатой константы 868, причем первый групповой вход регистрового блока подключен к групповым входам первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818, второй групповой вход регистрового блока подключен к первым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, третий групповой вход регистрового блока подключен к третьим групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, выходы первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 подключены ко входам первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818 соответственно, групповые выходы первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818 подключены к первым групповым входам первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826 соответственно, групповой выход пятого регистра 814 подключен ко вторым групповым входам первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826, выходы первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826 представляют собой группу выходов регистрового блока, выход пятого сумматора 823 является пятым выходом группы выходов регистрового блока, выход седьмого сумматора 825 является седьмым выходом группы выходов регистрового блока, первая константа 851, третья константа 853, пятая константа 855, седьмая константа 857, девятая константа 859, одиннадцатая константа 861, тринадцатая константа 863, пятнадцатая константа 865, семнадцатая константа 867 подключены ко вторым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 соответственно, вторая константа 851, четвертая константа 854, шестая константа 856, восьмая константа 858, десятая константа 860, двенадцатая константа 862, четырнадцатая константа 864, шестнадцатая константа 866, восемнадцатая константа 868 подключены к четвертым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 соответственно. Значения первой константы 851, второй константы 852, третьей константы 853, четвертой константы 854, пятой константы 855, шестой константы 856, седьмой константы 857, восьмой константы 858, девятой константы 859, десятой константы 860, одиннадцатой константы 861, двенадцатой константы 862, тринадцатой константы 863, четырнадцатой константы 864, пятнадцатой константы 865, шестнадцатой константы 866, семнадцатой константы 867, восемнадцатой константы 868 определяется по таблице, изображенной на фиг.11.

Каждый суммирующий блок 222-230 (фиг.7) состоит из первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 894, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98, девятого сумматора 99, причем выходы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 подключены к первому, второму, третьему, четвертому, пятому, шестому, седьмому, восьмому входам девятого сумматора 99 соответственно, первые входы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 являются первой группой входов суммирующего блока, вторые входы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 являются второй группой входов суммирующего блока, групповой выход девятого сумматора 99 является групповым выходом суммирующего блока.

Модуль определения объектов МОО 3 (фиг.8) состоит из первого счетчика 31, второго счетчика 32, третьего счетчика 33, четвертого счетчика 34, пятого счетчика 35, шестого счетчика 36, триггера 37, первого элемента И 38, первого элемента ИЛИ 39, первого сумматора 310, второго сумматора 311, третьего сумматора 312, четвертого сумматора 313, пятого сумматора 314, первого компаратора 315, второго компаратора 316, второго формирователя адреса 318, преобразователя данных 319, первого формирователя адреса 320, второго элемента И 321, первого мультиплексора 322, первого элемента НЕ 323, первого регистра 324, третьего компаратора 325, третьего элемента И 327, четвертого компаратора 328, пятого компаратора 331, шестого компаратора 332, седьмого компаратора 333, восьмого компаратора 334, девятого компаратора 335, десятого компаратора 336, второго регистра 337, третьего регистра 338, четвертого регистра 339, пятого регистра 340, шестого регистра 341, седьмого регистра 342, одиннадцатого компаратора 343, двенадцатого компаратора 344, тринадцатого компаратора 345, четырнадцатого компаратора 346, пятнадцатого компаратора 347, шестнадцатого компаратора 348, четвертого элемента И 361, пятого элемента И 362, шестого элемента И 363, седьмого элемента И 364, восьмого элемента И 365, девятого элемента И 366, восьмого регистра 367, девятого регистра 368, десятого регистра 369, одиннадцатого регистра 370, двенадцатого регистра 371, тринадцатого регистра 372, второго элемента ИЛИ 373, третьего элемента ИЛИ 374, четвертого элемента ИЛИ 375, пятого элемента ИЛИ 376, седьмого счетчика 377, восьмого счетчика 378, девятого счетчика 379, четырнадцатого регистра 380, десятого элемента И 381, десятого счетчика 382, буферного элемента 383, второго мультиплексора 384, одиннадцатого элемента И 385, двенадцатого элемента И 386, второго буферного элемента 387, третьего мультиплексора 388, семнадцатого компаратора 389, третьего буферного элемента 391, восемнадцатого компаратора 392, первого ОЗУ 71, второго ОЗУ 72, третьего ОЗУ 73, причем первый вход первого элемента И 38 является первым входом МОО 3 и предназначен для подачи тактового сигнала CLKX, выход триггера 37 подключен ко второму входу первого элемента И 38, выход первого элемента И 38 подключен к первому входу первого счетчика 31, групповой выход первого счетчика 31 подключен к первому групповому входу первого формирователя адреса 320 и к первому групповому входу первого компаратора 315, второй групповой вход МОО 3 подключен ко второму групповому входу первого компаратора 315, выход первого компаратора 315 подключен к первому входу второго элемента И 321, к второму входу первого элемента ИЛИ 39 и к первому входу второго счетчика 32, выход первого элемента ИЛИ 39 подключен ко второму входу первого счетчика 31, групповой выход второго счетчика 32 подключен к первому групповому входу второго компаратора 316 и второму групповому входу первого формирователя адреса 320, чей выход подключен к первому групповому входу первого мультиплексора 322, третий групповой вход МОО 3 подключен к второму групповому входу второго компаратора 316, выход второго компаратора 316 подключен к второму входу второго элемента И 321, к второму входу второго счетчика 32 и к первому входу первого элемента ИЛИ 39, выход второго элемента И 321 является выходом МОО 3, выход триггера 37 подключен к входу первого элемента НЕ 323 и к входу первого регистра 324, выход первого элемента НЕ 323 подключен к входу первого мультиплексора 322, к третьему входу пятого счетчика 35, к второму входу шестого счетчика 36 и к первому и второму входам третьего буферного элемента 391, чей выход подключен к входу/выходу первого ОЗУ 71, первый групповой вход МОО 3 подключен к групповому входу первого регистра 324, групповой выход первого регистра 324 подключен к первому групповому входу третьего компаратора 325, на чей второй групповой вход подается константа 0, выход третьего компаратора 325 подключен к первому входу третьего элемента И 327, выход которого подключен к первому входу триггера 37, вход/выход первого ОЗУ 71 подключен к первому входу четвертого компаратора 328, на чей второй вход подается константа 1, выход четвертого компаратора 328 подключен к второму входу третьего элемента И 327, вход третьего счетчика 33 является вторым входом МОО 3 и предназначен для подачи тактового сигнала CLKX6, групповой выход третьего счетчика 33 подключен к входу четвертого счетчика 34, групповой выход третьего счетчика 33 подключен к первому групповому входу первого сумматора 310, на чей второй групповой вход подается константа 1, выход первого сумматора 310 подключен к первому групповому входу второго сумматора 311, чей второй групповой вход подключен к групповому выходу пятого счетчика 35, третий групповой вход второго сумматора 311 подключен к групповому выходу первого счетчика 31, первый групповой вход третьего сумматора 312 подключен к групповому выходу четвертого счетчика 34, второй групповой вход третьего сумматора 312 подключен к групповому выходу шестого счетчика 36, третий групповой вход третьего сумматора 312 подключен к групповому выходу второго счетчика 32, групповые выходы второго сумматора 311 и третьего сумматора 312 подключены соответственно к первому и второму групповым входам второго формирователя адреса 318, групповой выход которого подключен к второму групповому входу первого мультиплексора 322 и к групповому входу первого ОЗУ 71, групповой выход третьего счетчика 33 подключен к первым групповым входам пятого компаратора 331, шестого компаратора 332, седьмого компаратора 333, восьмого компаратора 334, девятого компаратора 335, десятого компаратора 336, групповой выход четвертого счетчика 34 подключен к третьим групповым входам пятого компаратора 331, шестого компаратора 332, седьмого компаратора 333, восьмого компаратора 334, девятого компаратора 335, десятого компаратора 336, на второй групповой вход и на четвертый групповой вход пятого компаратора 331 подается константа 0, на второй групповой вход и на четвертый групповой вход шестого компаратора 332 подаются соответственно константа 1 и константа 0, на второй групповой вход и на четвертый групповой вход седьмого компаратора 333 подаются соответственно константа 2 и константа 0, на второй групповой вход и на четвертый групповой вход восьмого компаратора 334 подаются соответственно константа 0 и константа 1, на второй групповой вход и на четвертый групповой вход девятого компаратора 335 подается константа 1, на второй групповой вход и на четвертый групповой вход десятого компаратора 336 подаются соответственно константа 2 и константа 1, выход пятого компаратора 331 подключен к входу второго регистра 337, выход шестого компаратора 332 подключен к входу третьего регистра 338, выход седьмого компаратора 333 подключен к входу четвертого регистра 339, выход восьмого компаратора 334 подключен к входу пятого регистра 340, выход девятого компаратора 335 подключен к входу шестого регистра 341, выход десятого компаратора 336 подключен к входу седьмого регистра 342, первые групповые входы второго регистра 337, третьего регистра 338, четвертого регистра 339, пятого регистра 340, шестого регистра 341, седьмого регистра 342 подключены к первому групповому входу МОО 3, групповые выходы второго регистра 337, третьего регистра 338, четвертого регистра 339, пятого регистра 340, шестого регистра 341, седьмого регистра 342 подключены соответственно к первым групповым входам одиннадцатого компаратора 343, двенадцатого компаратора 344, тринадцатого компаратора 345, четырнадцатого компаратора 346, пятнадцатого компаратора, 347 и шестнадцатого компаратора 348, чьи вторые групповые входы подключены к групповому выходу первого регистра 324, выход одиннадцатого компаратора 343 подключен к первому входу четвертого элемента И 361 и к третьему входу девятого элемента И 366, выход двенадцатого компаратора 344 подключен к первому входу пятого элемента И 362, к второму входу четвертого элемента И 361, к первому входу шестого элемента И 363, к второму входу седьмого элемента И 364, к первому входу восьмого элемента И 365 и к первому входу девятого элемента И 366, выход тринадцатого компаратора 345 подключен к второму входу пятого элемента И 362 и пятому входу девятого элемента И 366, выход четырнадцатого компаратора 346 подключен к первому входу седьмого элемента И 364 и шестому входу девятого элемента И 366, выход пятнадцатого компаратора 347 подключен к второму входу восьмого элемента И 365 и четвертому входу девятого элемента И 366, выход шестнадцатого компаратора 348 подключен к второму входу шестого элемента И 363 и второму входу девятого элемента И 366, выход пятого элемента И 362 подключен к третьему входу шестого элемента И 363, чей выход подключен к третьему входу восьмого элемента И 365, чей выход подключен к третьему входу седьмого элемента И 364, чей выход подключен к третьему входу четвертого элемента И 361, выходы четвертого элемента И 361, пятого элемента И 362, шестого элемента И 363, седьмого элемента И 364, восьмого элемента И 365, девятого элемента И 366 подключены соответственно к первым входам восьмого регистра 367, девятого регистра 368, десятого регистра 369, одиннадцатого регистра 370, двенадцатого регистра 371, тринадцатого регистра 372, чьи вторые входы подключены к выходу десятого компаратора 336, а третьи входы данных регистров подключены к выходу пятого компаратора 331, выход восьмого регистра 367 подключен к второму входу пятого элемента ИЛИ 376 и к первому входу второго элемента ИЛИ 373, выход девятого регистра 368 подключен к первому входу третьего элемента ИЛИ 374 и к второму входу второго элемента ИЛИ 373, выход десятого регистра 369 подключен к первому входу четвертого элемента ИЛИ 375 и к третьему входу второго элемента ИЛИ 373, выход одиннадцатого регистра 370 подключен к первому входу пятого элемента ИЛИ 376 и к четвертому входу второго элемента ИЛИ 373, выход двенадцатого регистра 371 подключен к третьему входу четвертого элемента ИЛИ 375 и к пятому входу второго элемента ИЛИ 373, чей выход подключен к первому входу седьмого счетчика 377 и к первому входу восьмого счетчика 378, выход третьего элемента ИЛИ 374 подключен к первому входу пятого счетчика 35, выход четвертого элемента ИЛИ 375 подключен к первому входу шестого счетчика 36, выход пятого элемента ИЛИ 376 подключен к второму входу пятого счетчика 35, выход тринадцатого регистра 372 подключен к второму входу девятого счетчика 379, являющимся инверсным входом, к первому входу десятого элемента И 381 и к первому входу десятого счетчика 382, первый вход девятого счетчика 379, является третьим входом МОО 3 и предназначен для подачи тактового сигнала CLKY, первый выход девятого счетчика 379 подключен к второму входу десятого элемента И 381, выход десятого элемента И 381 подключен к входу четырнадцатого регистра 380, групповой выход седьмого счетчика 377 подключен к групповому входу четырнадцатого регистра 380, групповой выход четырнадцатого регистра 380 подключен к групповому входу буферного элемента 383, чей выход подключен к групповому входу-выходу второго ОЗУ 72, групповой выход десятого счетчика 382 подключен к первому групповому входу второго мультиплексора 384, чей второй групповой вход является четвертым групповым входом МОО 3, групповой выход второго мультиплексора 384 подключен к групповому входу второго ОЗУ 72, первый и второй выходы девятого счетчика 379 подключены соответственно к первому и второму входам одиннадцатого элемента И 385, первый вход которого является инверсным, а выход подключен к второму входу двенадцатого элемента И 386, чей выход подключен ко входу второго ОЗУ 72, первый групповой вход четвертого сумматора 313 подключен к групповому выходу пятого счетчика 35, второй групповой вход четвертого сумматора 313 подключен к групповому выходу первого счетчика 31, первый групповой вход пятого сумматора 314 подключен к групповому выходу второго счетчика 32, второй групповой вход пятого сумматора 314 подключен к групповому выходу шестого счетчика 36, групповые выходы четвертого сумматора 313 и пятого сумматора 314 подключены соответственно к первому и второму групповым входам преобразователя данных 319, чей выход подключен к групповому входу второго буферного элемента 387, групповой выход которого подключен к групповому входу-выходу третьего ОЗУ 73, групповой выход восьмого счетчика 378 подключен к первому групповому входу третьего мультиплексора 388, второй групповой вход третьего мультиплексора 388 является пятым групповым входом МОО 3, групповой выход третьего мультиплексора 388 подключен к групповому входу третьего ОЗУ 73, первый групповой вход семнадцатого компаратора 389 подключен к групповому выходу первого счетчика 31, второй групповой вход семнадцатого компаратора 389 подключен к групповому выходу второго счетчика 32, на третий групповой вход семнадцатого компаратора 389 подается константа 0, выход семнадцатого компаратора 389 подключен к второму входу восьмого счетчика 378 и к второму входу десятого счетчика 382, шестой групповой вход МОО 3 подключен к первому групповому входу восемнадцатого компаратора 392, на второй групповой вход которого подается константа 2, выход восемнадцатого компаратора 392 подключен к первому входу двенадцатого элемента И 386, входу второго мультиплексора 384 и входу третьего мультиплексора 388, групповой выход первого мультиплексора 322 является первым групповым выходом МОО 3, групповой выход десятого счетчика 382 является вторым групповым выходом МОО 3, групповой вход/выход второго ОЗУ 72 является третьим групповым выходом МОО 3, групповой вход/выход третьего ОЗУ 73 является четвертым групповым выходом МОО 3, при этом триггер 37 является RS-триггером, первый вход которого является R-входом, второй вход - S-входом, первый выход девятого счетчика 379 является младшим разрядом его выходного значения, второй выход - страшим разрядом, входы второго мультиплексора 324 и третьего мультиплексора 388 являются инверсными входами, данные первого ОЗУ 71 являются однобитными.

Модуль коррекции МК 4 (фиг.9) состоит из первого регистра 453, первого компаратора 454, первого счетчика 455, второго компаратора 456, генератора импульсов 457, второго элемента И 458, второго счетчика 459, третьего компаратора 460, первого триггера 461, первого элемента И 462, четвертого компаратора 463, пятого компаратора 464, третьего счетчика 465, второго триггера 466, второго регистра 467, третьего регистра 468, четвертого регистра 469, мультиплексора 470, преобразователя данных 471, первого сумматора 472, второго сумматора 473, первой константы 474, равной 1, формирователя адреса 475, второй константы 476, равной 0, третьей константы 477, равной 1, четвертой константы 478, равной 2, модуля подчеркивания контуров 479, пятого регистра 480, седьмого компаратора 481, пятой константы 482, равной 3, третьего элемента И 483, шестого компаратора 484, причем вход первого регистра 453 является третьим входом МК 4, первый групповой вход МК 4 подключен к групповому входу первого регистра 453, групповой выход первого регистра 453 подключен к первому групповому входу первого компаратора 454, выход первого компаратора 454 подключен к второму входу первого счетчика 455 и к первому выходу МК 4, первый групповой выход МК 4 подключен к групповому выходу первого счетчика 455, второй групповой вход МК 4 подключен к первому групповому входу второго компаратора 456, к первому групповому входу третьего компаратора 460 и к первому групповому входу генератора импульсов 457, четвертый групповой вход МК 4 подключен к второму групповому входу второго компаратора 456, выход второго компаратора 456 подключен к входу генератора импульсов 457, к второму входу третьего счетчика 465 и к первому входу первого триггера 461, выход генератора импульсов 457 подключен к первому входу второго элемента И 458, чей выход подключен к первому входу второго счетчика 459, чей групповой выход, являющийся четвертым групповым выходом МК 4, подключен к второму групповому входу третьего компаратора 460, чей выход подключен к второму входу первого триггера 461 и к второму входу второго счетчика 459, выход первого триггера 461 подключен к второму входу первого элемента И 462, выход первого элемента И 462 подключен к первому входу первого счетчика 455, первый вход МК 4 предназначен для подачи тактового сигнала CLKW и подключен к первому входу первого элемента И 462 и первому входу третьего элемента И 483, второй вход которого подключен к выходу второго триггера 466, а выход третьего элемента И 483 подключен к второму входу второго элемента И 458, второй вход МК 4 предназначен для подачи тактового сигнала CLKZ и подключен к первому входу третьего счетчика 465, групповой выход третьего счетчика 465 подключен к групповому входу четвертого компаратора 463, чей выход подключен к первому входу второго триггера 466 и к входу второго регистра 467, групповой вход которого подключен к пятому групповому входу модуля МК 4, групповые входы третьего регистра 468 и четвертого регистра 469 также подключены к пятому групповому входу модуля МК 4, групповой выход третьего счетчика 465 подключен к девятому групповому входу мультиплексора 470, третий групповой вход МК 4 подключен к групповому входу преобразователя данных 471, чей первый групповой выход подключен к первому, третьему и четвертому групповым входам мультиплексора 470 и первому входу первого сумматора 472, второй групповой выход преобразователя данных 471 подключен к пятому, шестому и восьмому групповым входам мультиплексора 470 и второму групповому входу второго сумматора 473, на второй групповой вход первого сумматора 472 и на первый групповой вход второго сумматора 473 подается третья константа 474, равная 1, групповой выход первого сумматора 472 подключен к второму групповому входу мультиплексора 470, групповой выход второго сумматора 473 подключен к седьмому групповому входу мультиплексора 470, первый и второй групповые выходы мультиплексора 470 подключены соответственно к первому и второму входам формирователя адреса 475, чей групповой выход является вторым групповым выходом МК 4, выход пятого компаратора 464 подключен к входу третьего регистра 468, выход шестого компаратора 484 подключен к входу четвертого регистра 469, на вторые групповые входы четвертого компаратора 463, пятого компаратора 464, шестого компаратора 484 подаются постоянные значения, задаваемые второй константой 476, третьей константой 477, четвертой константой 478, равным 0, 1 и 2 соответственно, групповые выходы второго регистра 467, третьего регистра 468 и четвертого регистра 469 подключены соответственно к первому, второму и третьему групповым входам модуля подчеркивания контуров 479, чей групповой выход подключен к групповому входу пятого регистра 480, выход третьего счетчика 465 подключен к первому групповому входу седьмого компаратора 481, на чей второй вход подается пятая константа 482, равная 3, выход седьмого компаратора 481 подключен к второму входу второго триггера 466 и к входу пятого регистра 480, чей групповой выход является третьим групповым выходом МК 4, выход второго триггера 466 является вторым выходом МК 4.

Модуль подчеркивания контуров МПК 479 (фиг.10) состоит из первого умножителя 411, второго умножителя 412, третьего умножителя 413, четвертого умножителя 414, третьего сумматора 417, модуля выделения квадратного корня 419, первого сумматора 420, второго сумматора 421, четвертого сумматора 422, причем первый групповой вход МПК 479 подключен к первому групповому входу первого сумматора 420, второй групповой вход МПК 479 подключен к второму групповому входу первого сумматора 420 и к первому групповому входу второго сумматора 421, третий групповой вход МПК 479 подключен к второму групповому входу второго сумматора 421, групповой выход первого сумматора 420 подключен к первому и второму групповым входам первого умножителя 411, групповой выход второго сумматора 421 подключен к первому и второму групповым входам второго умножителя 412, групповые выходы первого умножителя 411 и второго умножителя 412 подключены соответственно к первому и второму групповым входам третьего сумматора 417, чей групповой выход подключен к групповому входу модуля выделения квадратного корня 419, групповой выход модуля выделения квадратного корня 419 подключен к первому групповому входу третьего умножителя 413, второй групповой вход которого является четвертым групповым входом МПК 479 и предназначен для подачи постоянной величины k1 (где k1 - первый целочисленный весовой коэффициент, определяющий степень подчеркивания контуров), групповой выход третьего умножителя 413 подключен к первому групповому входу четвертого сумматора 422, второй групповой вход МПК 479 подключен к первому групповому входу четвертого умножителя 414, второй групповой вход которого является пятым групповым входом МПК 479 и предназначен для подачи постоянной величины k2 (где k2 - второй целочисленный весовой коэффициент, определяющий степень подчеркивания контуров), групповой выход четвертого умножителя 414 подключен к второму групповому входу четвертого сумматора 422, групповой выход четвертого сумматора 422 является групповым выходом МПК 479, при этом первый сумматор 420 и второй сумматор 421 выполняют функцию вычитания.

Устройство компенсации размытости изображения работает в четырех режимах, задаваемых значением на групповом выходе счетчика 100. Режимы работы устройства последовательно чередуются с 0 по 3 для каждого поступающего с ДИ 10 кадра. В нулевом режиме производится выдача обработанного кадра на системную шину и запись данных от ДИ 10. В первом режиме производится обнаружение и определение направления движения для каждого пикселя. Во втором режиме пиксели с одинаковым направлением движения группируются в объекты. В третьем режиме для найденных движущихся объектов производится расчет и коррекция яркостей пикселей с целью компенсации размытости изображения.

В нулевом режиме на вход ДИ 10 поступает входной сигнал CLK/3. С группового выхода ДИ 10 на первый групповой вход контроллера 1 последовательно передаются яркости пикселей текущего кадра изображения.

Контроллер 1 работает в трех режимах, которые чередуются последовательно от 2 до 0 для каждого пикселя, и обеспечивает: в режиме 2 - выдачу данных из первого ОЗУ 5 на системную шину СШ, в режиме 1 - перезапись кадра из первого ОЗУ 5 во второе ОЗУ 6, в режиме 0 - запись данных, поступающих от датчика изображения, в первое ОЗУ 5. Во всех режимах работы контроллера 1 обработка данных первого ОЗУ 5 и второго ОЗУ 6 производится по адресу, сформированному на втором групповом выходе контроллера 1.

В режиме 2 контроллер 1 производит считывание значения яркости пикселя из первого ОЗУ 5 и выдачу его на системную шину. Для этого контроллер 1 на своем втором групповом выходе формирует значение адреса и передает его на первый групповой вход первого мультиплексора 51, с группового выхода которого он поступает на групповой вход первого ОЗУ 5. По данному адресу значение яркости пикселя текущего кадра с группового входа-выхода первого ОЗУ 5 считывается и поступает на первый групповой вход первого демультиплексора 56, с первого группового выхода которого оно передается на четвертый групповой вход контроллера 1 и далее поступает с третьего группового выхода контроллера 1 на системную шину.

Далее в режиме 1 контроллер 1 производит запись считанного из первого ОЗУ 5 значения яркости пикселя во второе ОЗУ 6. Значение яркости пикселя считывается по ранее сформированному адресу и передается с группового входа-выхода первого ОЗУ 5 на первый групповой вход первого демультиплексора 56, с выхода которого оно поступает на четвертый групповой вход контроллера 1. С четвертого группового выхода контроллера 1 значение яркости пикселя поступает на первый групповой вход шестого мультиплексора 57, с группового выхода которого оно поступает на групповой вход-выход второго ОЗУ 6.

Далее в режиме 0 контроллер 1 производит запись значения яркости текущего пикселя, поступившего от ДИ 10, в первое ОЗУ 5. Для этого ранее сформированное на втором групповом выходе контроллера 1 значение адреса пикселя поступает на первый групповой вход первого мультиплексора 51 и далее с группового выхода первого мультиплексора 51 на групповой вход первого ОЗУ 5. С первого группового выхода контроллера 1 значение яркости текущего пикселя поступает на групповой вход пятого мультиплексора 55, с группового выхода которого значение яркости текущего пикселя передается на вход-выход первого ОЗУ 5. Чтение/запись данных из первого ОЗУ 5 и второго ОЗУ 6 для всех режимов работы устройства производится аналогично нулевому режиму.

На второй и третий групповые входы контроллера 1 поступают константы (Х-1) и (Y-1) соответственно.

На первом выходе контроллера 1 формируется сигнал, определяющий режим работы первого ОЗУ 5: чтение или запись данных. Для этого сигнал с первого выхода контроллера 1 поступает на первый вход второго мультиплексора 52, с выхода которого он передается на вход первого ОЗУ 5. На втором выходе контроллера 1 формируется сигнал, определяющий режим работы второго ОЗУ 6: чтение или запись данных. Для этого сигнал с второго выхода контроллера 1 поступает на первый вход четвертого мультиплексора 54, с выхода которого он передается на вход второго ОЗУ 6.

По сигналу на третьем выходе контроллера 1, поступающему на первый вход элемента ИЛИ 101 и далее с его выхода на вход счетчика 100, производится инкрементирование значения на групповом выходе счетчика 100 и переключение режима работы устройства из нулевого в первый. С группового выхода счетчика 100 сигнал поступает на первый групповой вход первого компаратора 102, на второй групповой вход которого подана константа 0. Первый компаратор 102 выполняет функцию «не равно» и выдает значение 0 на своем выходе при неравенстве режима работы нулю. С выхода первого компаратора 102 сигнал поступает на третий вход контроллера 1. При единичном значении данного сигнала производится сброс и запрещение работы контроллера 1, при нулевом значении данного сигнала - разрешение работы контроллера.

Номер режима работы устройства с группового выхода счетчика 100 поступает на четвертый групповой вход первого мультиплексора 51, групповой вход второго мультиплексора 52, третий групповой вход третьего мультиплексора 53, групповой вход четвертого мультиплексора 54, третий групповой вход пятого мультиплексора 55 и второй групповой вход шестого мультиплексора 57, а также на вторые групповые входы первого демультиплексора 56 и второго демультиплексора 58.

В первом режиме работы устройства МОД 2 производит обнаружение и определение направления движения для каждого пикселя.

На первый и второй групповые входы МОД 2 поступают константы (X-3) и (Y-3) соответственно. На первый вход МОД 2 поступает тактовая частота CLK/25.

На первом групповом выходе МОД 2 последовательно формируется значение адреса текущего обрабатываемого пикселя, которое поступает на вторые групповые входы первого мультиплексора 51 и третьего мультиплексора 53, с групповых выходов которых оно далее поступает на групповые входы ОЗУ 5 и ОЗУ 6 соответственно. На четвертый групповой вход МОД 2 со второго группового выхода первого демультиплексора 56 поступает значение яркости пикселя текущего кадра, на вход которого данное значение поступило с группового входа-выхода ОЗУ 5. На третий групповой вход МОД 2 со второго группового выхода второго демультиплексора 58 поступает значение яркости пикселя предыдущего кадра, на вход которого данное значение поступило с группового входа-выхода ОЗУ 6.

На пятый групповой вход МОД 2 с группового выхода счетчика 100 подается номер режима работы устройства. При первом режиме работы устройства на втором выходе МОД 2 формируется нулевой сигнал, а при остальных режимах работы устройства - единичный сигнал, который подается на вход седьмого мультиплексора 59. Со второго группового выхода МОД 2 на второй групповой вход седьмого мультиплексора 59 поступает значение адреса текущего пикселя, которое с группового выхода седьмого мультиплексора 59 передается на групповой вход третьего ОЗУ 7. На групповой вход-выход третьего ОЗУ 7 с третьего группового выхода МОД 2 поступает значение направления движения текущего пикселя, которое при единичном значении на третьем выходе МОД 2, подаваемом на вход третьего ОЗУ 7, записывается в данное ОЗУ. По завершению обработки последнего пикселя кадра на первом выходе МОД 2 формируется единичный сигнал, поступающий на второй вход элемента ИЛИ 101 и переводящий устройство в следующий (второй) режим работы.

В третьем режиме работы устройства МОО 3 последовательно анализирует направление движения каждого пикселя и группирует пиксели с одинаковым направлением движения в объекты.

На второй и третий групповые входы МОО 3 поступают константы (X-2) и (Y-2) соответственно. На первый вход МОО 3 поступает тактовая частота CLKX. На второй вход МОО 3 поступает тактовая частота CLKX6. На третий вход МОО 3 поступает тактовая частота CLKY.

На шестой групповой вход МОО 3 с группового выхода счетчика 100 поступает номер режима работы устройства. С первого группового выхода МОО 3 значение адреса текущего анализируемого пикселя поступает на первый групповой вход седьмого мультиплексора 59 и далее с его выхода на групповой вход третьего ОЗУ 7. С группового входа-выхода третьего ОЗУ 7 значение направления движения текущего пикселя поступает на первый групповой вход МОО 3. По завершении обработки последнего пикселя кадра на выходе МОО 3 формируется единичный сигнал, поступающий на третий вход элемента ИЛИ 101 и переводящий устройство в следующий (четвертый) режим работы, а также на третий вход МК 4 и обеспечивающий запись значения количества объектов, формируемого на втором групповом выходе МОО 3 и подаваемого на первый групповой вход МК 4.

В четвертом режиме работы устройства МК 4 последовательно для всех сформированных МОО 3 объектов производит определение количества пикселей, составляющих объект, расчет скорректированных значений яркостей пикселей движущихся объектов и запись скорректированных значений яркостей пикселей в первое ОЗУ 5.

На первый вход МК 4 поступает тактовая частота CLKW, второй вход МК 4 - тактовая частота CLKZ.

В процессе своей работы МК 4 на первом групповом выходе формирует значение адреса, по которому в МОО 3 записано количество пикселей текущего анализируемого объекта, и подает его на четвертый групповой вход МОО 3. На четвертом групповом выходе МК 4 формируется значение адреса, по которому из МОО 3 считываются значения координат текущего обрабатываемого пикселя, и поступают на пятый групповой вход МОО 3. С третьего группового выхода МОО 3 на второй групповой вход МК 4 поступает количество точек текущего анализируемого объекта. С четвертого группового выхода МОО 3 на третий групповой вход МК 4 поступают координаты текущего пикселя текущего анализируемого объекта.

На пятый групповой вход МК 4 поступают данные (яркости пикселей корректируемой области) с четвертого группового выхода первого демультиплексора 56, считываемые с группового входа-выхода первого ОЗУ 5 по адресу, сформированному на втором групповом выходе МК 4 и поданному на четвертый групповой вход первого мультиплексора 51, с выхода которого он передается на групповой вход первого ОЗУ 5, и поданные на первый групповой вход первого демультиплексора 56.

В процессе работы МК 4 на своем втором групповом выходе формирует значение адреса, определяющего координаты пикселя со скорректированным значением яркости, и подает его на четвертый групповой вход первого мультиплексора 51, с группового выхода которого данное значение адреса поступает на групповой вход первого ОЗУ 5. На третьем групповом выходе МК 4 формируется скорректированное значение яркости пикселя, которое поступает на четвертый групповой вход пятого мультиплексора 55, с группового выхода которого оно подается на групповой вход-выход первого ОЗУ 5 и записывается в него.

На четвертый групповой вход МК 4 подается пороговое значение, определяющее минимально допустимое количество пикселей в объекте. На выходе МК 4 формируется единичный сигнал, поступающий на четвертый вход элемента ИЛИ 101 и переводящий устройство в нулевой режим работы.

Контроллер 1 работает следующим образом. На первый вход первого счетчика 13, который определяет координату х текущего обрабатываемого пикселя, поступает тактовый сигнал CLK/3, по которому значение на групповом выходе первого счетчика 13 увеличивается на единицу и поступает на первый групповой вход первого компаратора 16. На второй групповой вход первого компаратора 16 подается константа (Х-1), где Х - размер кадра по горизонтали. С выхода первого компаратора 16 сигнал поступает на второй вход первого элемента ИЛИ 11, с выхода которого подается на второй вход первого счетчика 13. При единичном значении данного сигнала обеспечивается сброс первого счетчика 13. Одновременно с этим сигнал с выхода первого компаратора 16 поступает на первый вход второго счетчика 14, определяющего координату у текущего обрабатываемого пикселя, с выхода которого сигнал подается на первый групповой вход второго компаратора 17, на второй групповой вход которого подана константа (Y-1), где Y - размер кадра по вертикали. С выхода второго компаратора 17 сигнал поступает на второй вход второго элемента ИЛИ 12 и на первый вход первого элемента ИЛИ 11. С выхода второго элемента ИЛИ 12 сигнал подается на второй вход второго счетчика 14. При единичном значении данного сигнала обеспечивается сброс второго счетчика 14. Таким образом, обеспечивается последовательный перебор координат (х,у) пикселей, где x∈[0,Х-1], у∈[0,Y-1].

С группового выхода первого счетчика 13 и группового выхода второго счетчика 14 координаты (х,у) текущего пикселя поступают соответственно на первый и второй групповые входы формирователя адреса 18, чей групповой выход, на котором формируется значение адреса текущего пикселя, является вторым групповым выходом контроллера 1.

Третий счетчик 15, предназначенный для задания текущего режима работы контроллера, обеспечивает формирование на своем двубитном групповом выходе значений от 0 до 2. На первый вход третьего счетчика 15 поступает тактовый сигнал CLK, который обеспечивает инкрементирование значения на выходе счетчика. С группового выхода третьего счетчика 15 сигнал поступает на второй групповой вход буфера 110, на первый групповой вход которого подается сигнал от датчика изображения 10. При значении 0 на втором групповом входе буфера 110 обеспечивается пропускание сигнала от ДИ 10 на групповой выход буфера 110, который является первым групповым выходом контроллера 1. При остальных значениях на втором групповом входе буфера 110 его групповой выход находится в третьем высокоимпедансном состоянии.

С выхода первого компаратора 16, с выхода второго компаратора 17 и старшего разряда группового выхода третьего счетчика 15 сигналы поступают на первый, второй и третий входы элемента И 19, с выхода которого сигнал поступает на третий выход контроллера 1 и означает завершение 0 режима работы устройства компенсации размытости изображения.

С группового выхода третьего счетчика 15 сигнал поступает на второй групповой вход демультиплексора 111, первый групповой вход которого является четвертым групповым входом контроллера 1. При значении 0 на втором групповом входе демультиплексора 111 обеспечивается пропускание сигнала с его первого группового входа на его первый групповой выход, являющийся третьим групповым выходом контроллера 1. При значении 1 на втором групповом входе демультиплексора 111 обеспечивается подключение его первого группового входа на его второй групповой выход, являющийся четвертым групповым выходом контроллера 1.

На третий вход первого элемента ИЛИ 11, первый вход второго элемента ИЛИ 12 и второй вход третьего счетчика 15 поступает сигнал, единичное значение которого блокирует работу контроллера 1.

Сигнал со второго выхода контроллера 1 используется для управления режимом чтение/запись второго ОЗУ 6.

Модуль обнаружения движения 2 работает следующим образом. На первый вход первого счетчика 21 поступает тактовый сигнал CLK/25, по которому первый счетчик 21 инкрементирует свое значение. С группового выхода первого счетчика 21 координата x текущего обрабатываемого пикселя подается на первый групповой вход первого сумматора 27 и первый групповой вход первого компаратора 25, на второй групповой вход которого поступает величина (Х-3). При совпадении значений на своих обоих групповых входах первый компаратор 25 подает сигнал на второй вход элемента ИЛИ 210, с выхода которого сигнал поступает на второй вход первого счетчика 21 и сбрасывает первый счетчик 21 в нулевое состояние. Одновременно с этим с выхода первого компаратора 25 сигнал поступает на первый вход второго счетчика 22, с группового выхода которого сигнал поступает на первый групповой вход второго компаратора 26, на второй групповой вход которого поступает величина (Y-3). При совпадении значений на обоих своих групповых входах второй компаратор 26 формирует единичный сигнал, поступающий на второй вход второго счетчика 22 и первый вход элемента ИЛИ 210 и далее с его выхода на второй вход первого счетчика 21, тем самым сбрасывая первый счетчик 21 и второй счетчик 22 в нулевое состояние. Таким образом, на групповом выходе первого счетчика 21 последовательно формируется координата х текущего обрабатываемого пикселя, принимающая значения от 0 до (Х-3); на выходе второго счетчика 22 последовательно формируется координата у текущего обрабатываемого пикселя, принимающая значения от 0 значения до (У-3).

На вход третьего счетчика 23 поступает тактовый сигнал CLK, на групповом выходе третьего счетчика 23 последовательно формируются значения i от 0 до 4 включительно, которые поступают на второй групповой вход первого сумматора 27. При переполнении третьего счетчика 23 на его втором выходе формируется сигнал, поступающий на вход четвертого счетчика 24 и инкрементирующий его выходное значение. С группового выхода четвертого счетчика 24 значения j от 0 до 4 включительно поступают на второй групповой вход второго сумматора 28. С групповых выходов первого счетчика 21 и второго счетчика 22 значения х и у поступают на первые групповые входы первого сумматора 27 и второго сумматора 28. На групповых выходах первого сумматора 27 и второго сумматора 28 формируются значения, определяющие координаты (x+i, у+j) текущего пикселя, которые поступают на первый и второй групповые входы первого формирователя адреса 29. Первый формирователь адреса 29 производит на своем групповом выходе формирование адреса А в соответствии с формулой A=(x+i)+(у+j)*X и подает адрес А на первый групповой выход МОД 2.

На первый групповой вход первого регистрового блока 212 с четвертого группового входа МОД 2 поступает значение яркости текущего пикселя текущего кадра. На первые групповые входы второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 с третьего группового входа МОД 2 поступает значение яркости текущего пикселя предыдущего кадра. На вторые групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 поступают значения j с группового выхода четвертого счетчика 24. На третьи групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 поступают значения i с группового выхода третьего счетчика 23.

На групповом выходе первого регистрового блока 212 формируются элементы матрицы В(k) в соответствии с формулой (1) и поступают на первые групповые входы первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блок 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230.

На групповых выходах второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 формируются элементы матрицы В*(k) для каждого из 8 направлений движения в соответствии с формулой (2) и поступают на вторые групповые входы первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230.

На групповых выходах первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230 формируются элементы матрицы В*(k-1) в соответствии с формулой (3).

Значение с группового выхода пятого суммирующего блока 226 поступает на первый групповой вход одиннадцатого компаратора 241, на второй групповой вход которого подается пороговая величина, при сравнении с которой определяется факт наличия движения текущего пикселя текущего кадра. С выхода одиннадцатого компаратора 241 сигнал поступает на третий выход МОД 2.

Значения с групповых выходов первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230 поступают на соответствующие групповые входы блока определения минимума 231 и на первые групповые входы третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240. На вторые групповые входы третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240 поступает величина с группового выхода блока определения минимума 231.

Таким образом, на выходах третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240. На вторых групповых входах третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240 в коде «1 из N» формируются направления движения текущего пикселя текущего кадра, которые подаются на групповой вход шифратора 242. На выходе шифратора 242, который является третьим групповым выходом МОД 2, формируются значения направлений движений в двоичном коде.

С группового выхода первого счетчика 21 координата х текущего пикселя поступает на первый групповой вход четвертого сумматора 245. С группового выхода второго счетчика 22 координата у текущего пикселя поступает на первый групповой вход третьего сумматора 244. На вторые групповые входы третьего сумматора 244 и четвертого сумматора 245, а также на второй групповой вход двенадцатого компаратора 247 поступает константа 2. С групповых выходов третьего сумматора 244 и четвертого сумматора 245 значения координат текущего пикселя (х+2, у+2) поступают на первый и второй групповые входы второго формирователя адреса 246, групповой выход которого является вторым групповым выходом МОД 2.

С выхода первого компаратора 25 и с выхода второго компаратора 26 сигналы поступают на первый и второй входы элемента И 211, с выхода которого сигнал поступает на первый выход МОД 2. Данный сигнал инкрементирует значение режима устройства компенсации размытости изображения.