Изобретение относится к авиации и предназначено для применения в катапультном кресле типа К36Л-3,5Я (далее по тексту - КК) и выполняет функции электронного парашютного устройства (ЭУКК).

Известно изобретение US 4505444 А [1], система посадки воздушного судна, которая включает в себя средство для катапультирования основного парашюта в конце задержки после выброса кресла и механизм переключения режимов, способный обеспечить развертывание парашюта в более короткое заданное время после выброса, если выброс происходит на низкой скорости и малой высоте. Механизм выбора режимов включает в себя поршень, скользящий вдоль отверстия, для управления стреляющим штифтом для замыкания контактов реле и, таким образом, обеспечивает более раннее раскрытие парашюта.

Система посадки воздушного судна, имеющая катапультное кресло для размещения летчика и главного парашюта для опускания летчика на землю, средство для катапультирования упомянутого основного парашюта в конце задержки после инициирования выброса катапультного кресла и пилота, причем данное средство включает в себя парашют с дросселем, функционально связанный с указанным посадочным местом и средство для временной задержки в течение заданного времени после упомянутого инициирования выброса; а также средство выбора режима для определения, по меньшей мере, одного заданного условия и для разрешения катапультирования основного парашюта за время до истечения задержки при условии, что определено заданное условие, причем средство механизма выбора режима включает в себя средство для определения замедления положения катапультного кресла и пилота, с помощью парашюта и средство для торможения работы механизма переключения, приводящее к раскрытию основного парашюта после указанного времени до истечения задержки.

Известно изобретение US 4527758 А [2], электронная система для выбора последовательности правильного режима и правильной последовательности катапультирования. Система измеряет высоту, скорость, истинную скорость и сравнивает их с заданными опорными сигналами. Система также включает логические схемы и схемы задержки времени. Логические схемы организованы так, чтобы выбирать одну из четырех временных задержек в зависимости от состояния различных параметров относительно опорных сигналов. Целью данного изобретения является оптимизация последовательности развертывания парашюта, выбора момента катапультирования, выбор правильной временной последовательности для инициирования развертывания парашюта, использование истинной скорости самолета, а также высоты и скорости в выборе правильной последовательности синхронизации для начала развертывания парашюта, создание системы катапультирования, подходящей для установки на самолет, создание системы выброса парашюта, подходящей для использования с существующими датчиками. Вышеупомянутые функции реализованы в настоящем изобретении с помощью электронных схем для сравнения входных сигналов скорости полета, воздушной скорости и истинной скорости с заданными значениями. Эта схема, в свою очередь, передает сигнал или сигналы на множество электронных логических схем. Эти логические схемы также получают сигналы включения, когда инициируется момент выброса парашюта. Логические схемы выбирают соответствующую задержку времени, когда принимается правильная комбинация входных и разрешающих сигналов. Задержка времени выполняется с помощью электронных схем задержки времени, каждая из которых имеет разную ширину импульса. Кроме того, предусмотрены электронные схемы для блокировки дополнительных входных сигналов датчика после выбора временной задержки. Сигнал «открытого парашюта» генерируется, когда обнаружен задний фронт импульса временной задержки.

Существенными недостатками каждого из этих устройств является низкая надежность и недостаточное качество катапультирования.

Наиболее близким по технической сущности к изобретению (прототип) является микропроцессорное устройство осуществляющее катапультирование [3], содержащее процессор, ОЗУ, ПЗУ, переключатель (Time Zero Switch), часы (clock), таймер, выключатель (Power switch), первый, второй и третий датчики давления, мультиплексор и АЦП, пиропатрон выброса парашюта, автономный источник питания и фильтр, первый и второй выходы которого соединены с первым и вторым входами выключателя, выход которого соединен со входом пиропатрона выброса парашюта, причем выходы переключателя, часов и таймера соединены с первым, вторым и третьим входами процессора, первый, второй, третий и четвертый выходы которого соединены со входами часов, таймера переключателя и выключателя, причем группа выходов процессора соединена с группой входов ОЗУ, группа выходов которого соединена с группой входов процессора, вторая группа входов которого соединена с группой выходов ПЗУ, причем пятый и шестой выходы процессора соединены с источником питания и с управляющим входом мультиплексора, первый, второй и третий входы которого соединены с выходами первого, второго и третьего датчиков, выход мультиплексора соединен со входом АЦП, выход которого соединен с пятым входом процессора, причем выход источника питания соединен со входом фильтра.

Описанное устройство как наиболее близкое к предполагаемому принято за прототип.

Недостатком устройства является низкая надежность и недостаточное качество катапультирования.

Задачей изобретения является улучшение качества катапультирования и повышение надежности за счет использования структуры канал-модель, которая реализует функцию выброса парашюта при совпадении результатов вычислений канала и модели в диапазоне. В случае несовпадения вычислений в диапазоне в устройстве предусмотрена дублированная схема горячего резерва выработки сигнала выброса парашюта по предельно допустимым параметрам.

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг. 1…фиг. 25, где

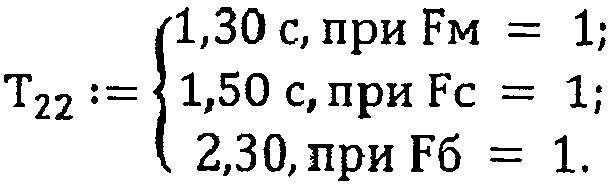

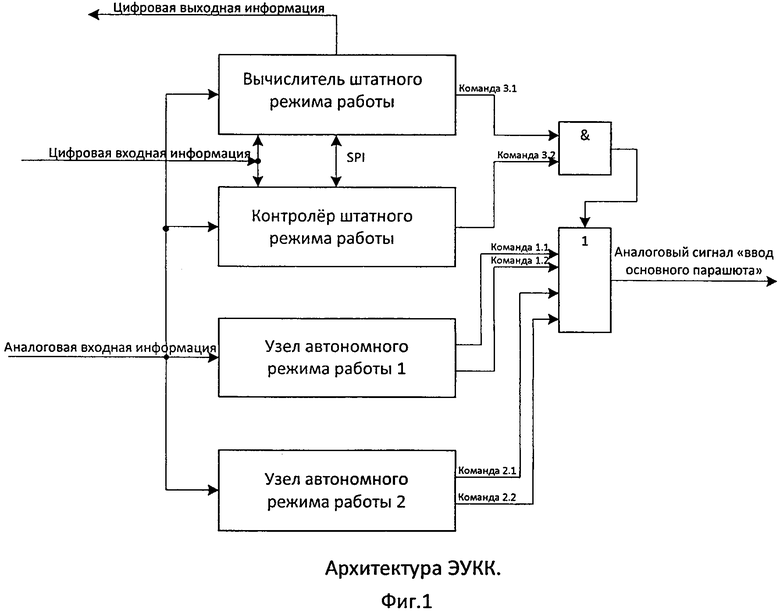

• на фиг. 1 представлена архитектура электронного устройства катапультного кресла для самолета;

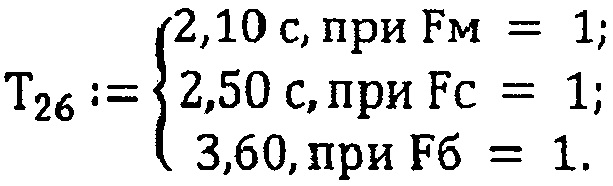

• на фиг. 2 представлена структурная схема электронного устройства катапультного кресла для самолета;

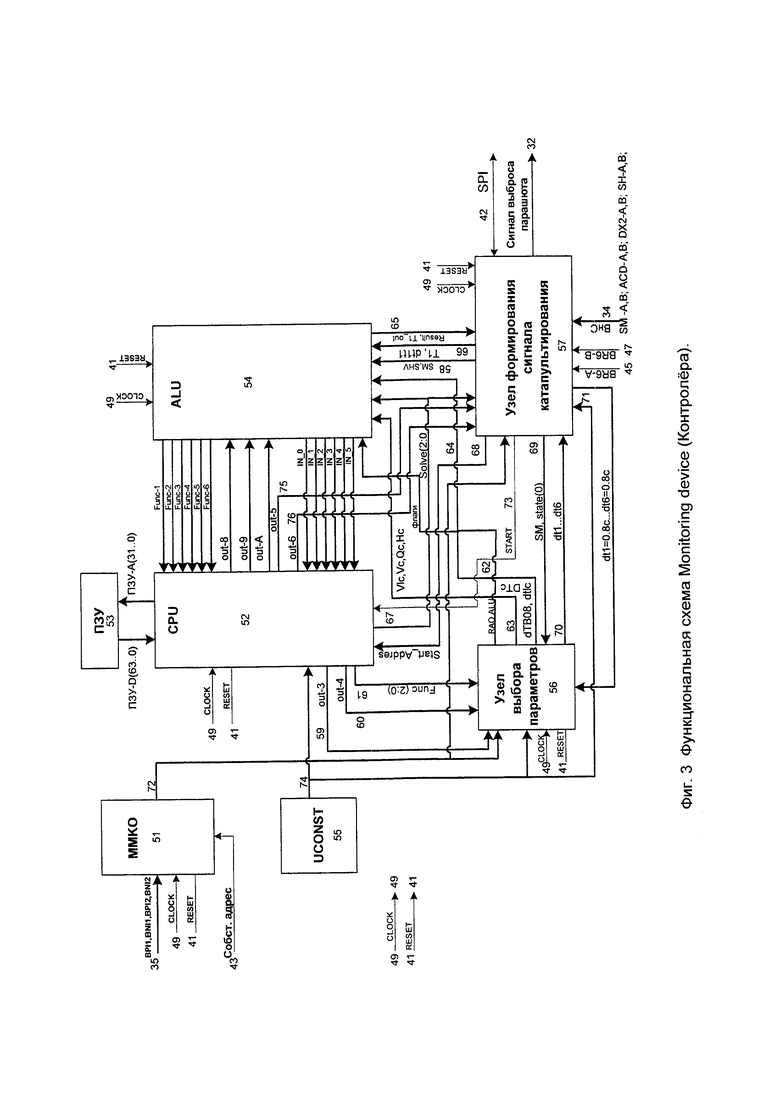

• на фиг. 3 представлена функциональная схема Monitoring device (Контролера);

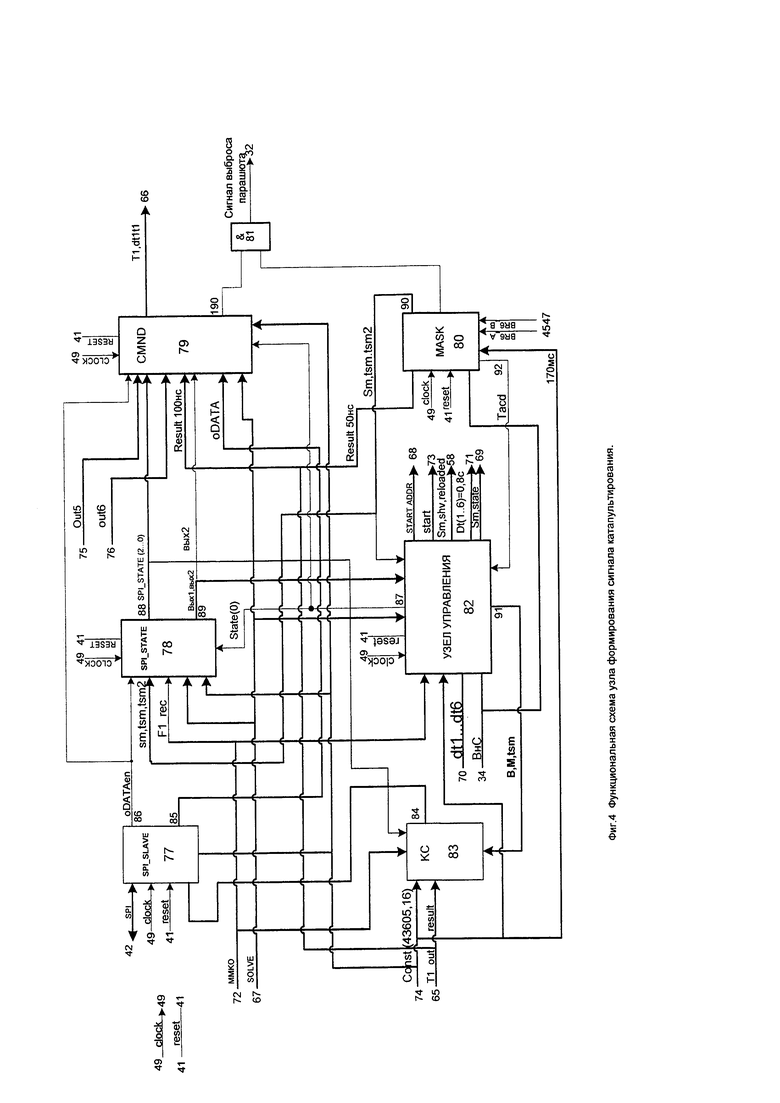

• на фиг. 4 представлена функциональная схема узла формирования сигнала катапультирования;

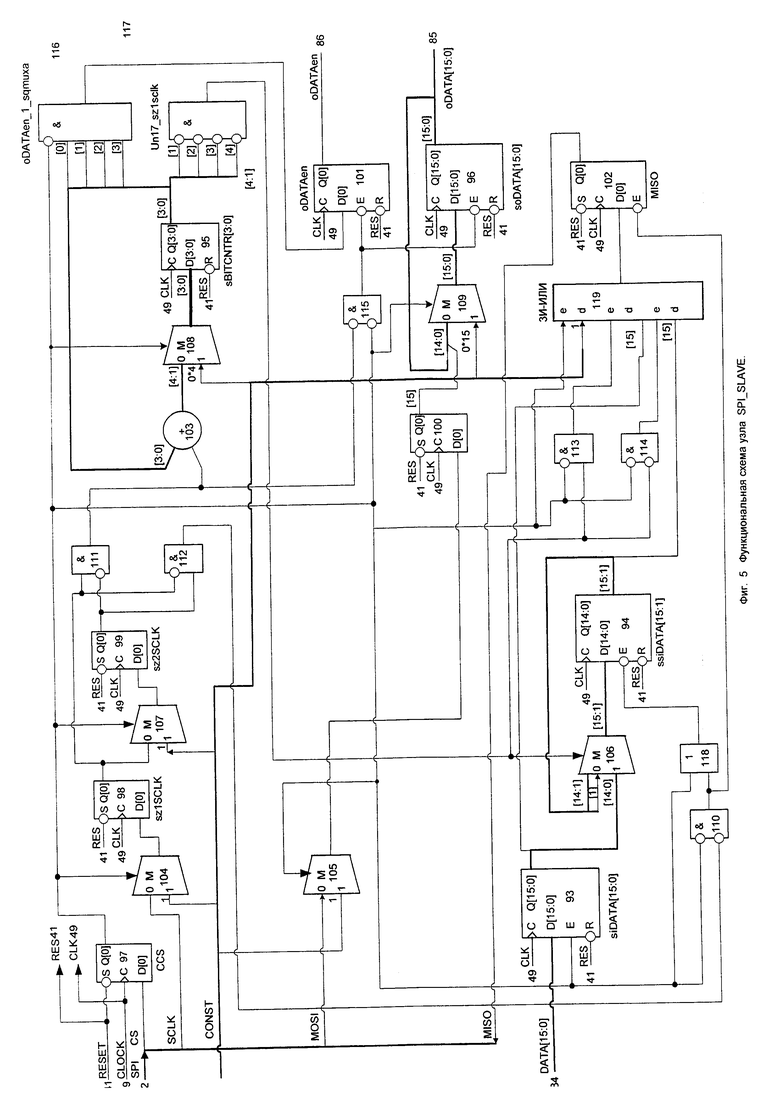

• на фиг. 5 представлена функциональная схема узла SPI_SLAVE;

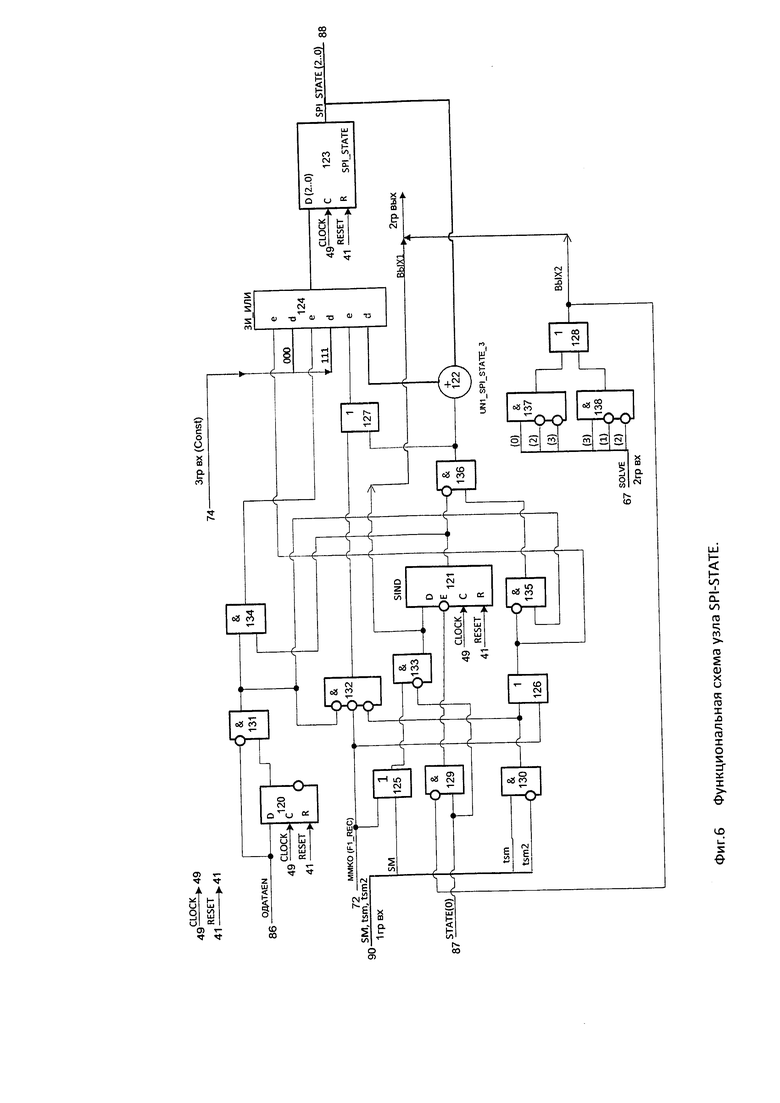

• на фиг. 6 представлена функциональная схема узла SPI-STATE;

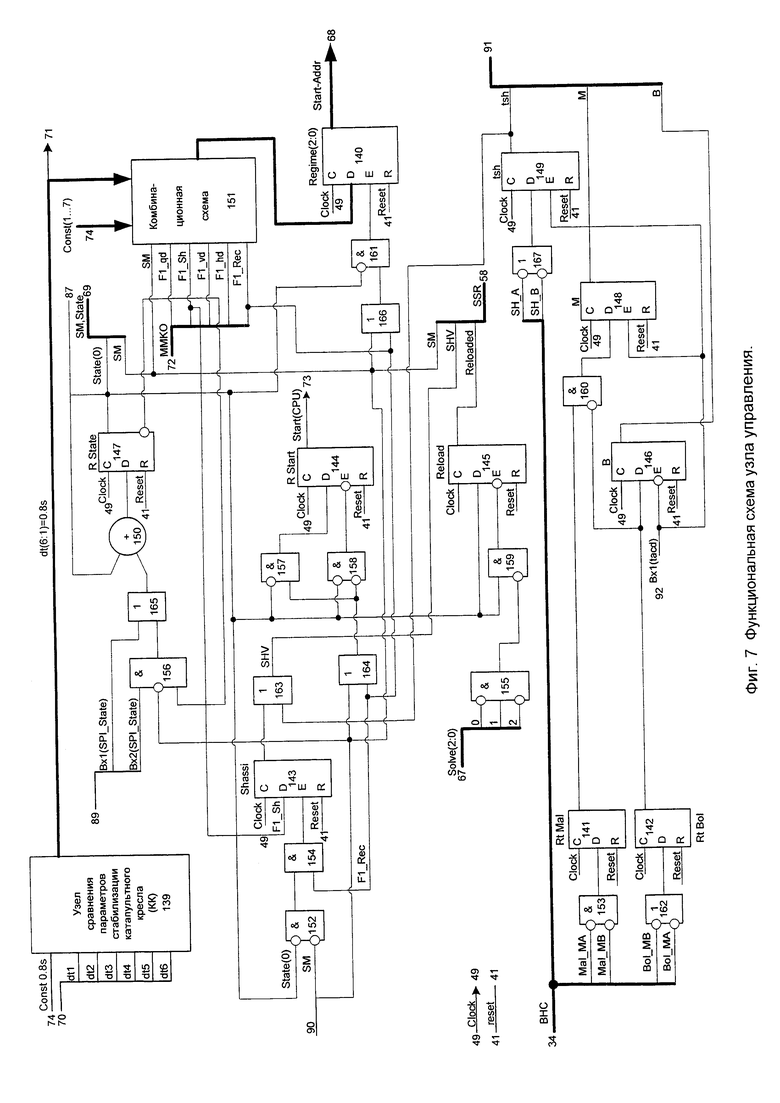

• на фиг. 7 представлена функциональная схема узла управления;

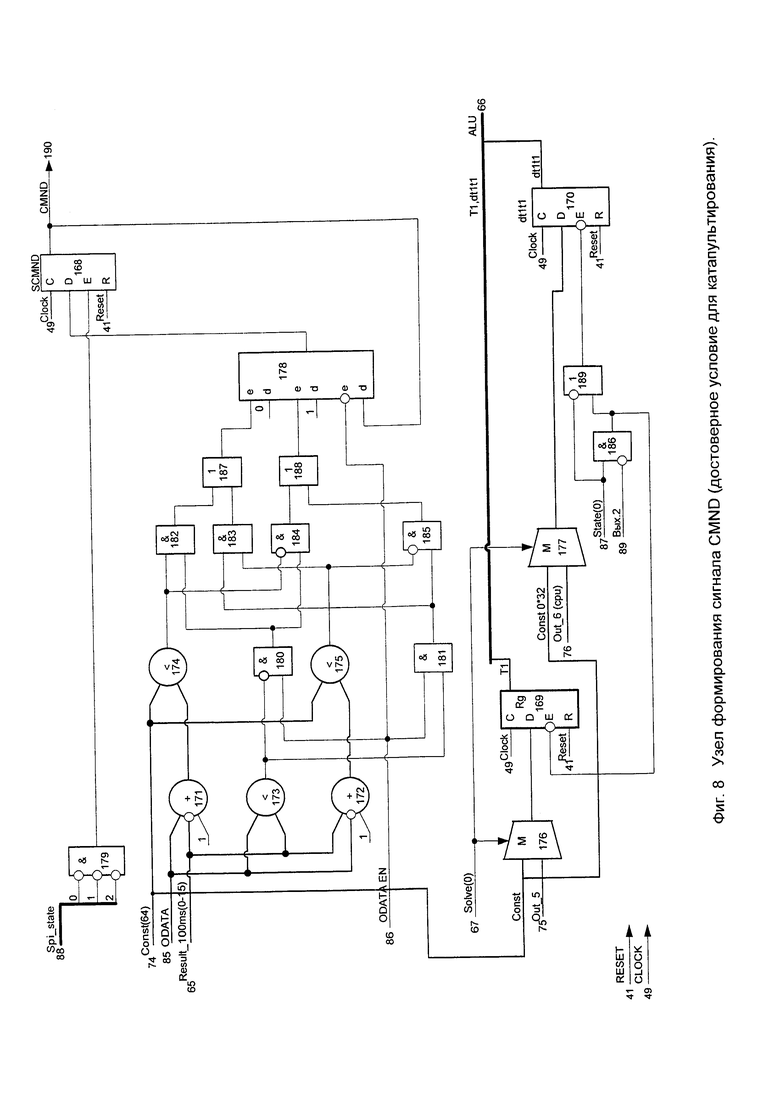

• на фиг. 8 представлена функциональная схема узла формирования сигнала CMND;

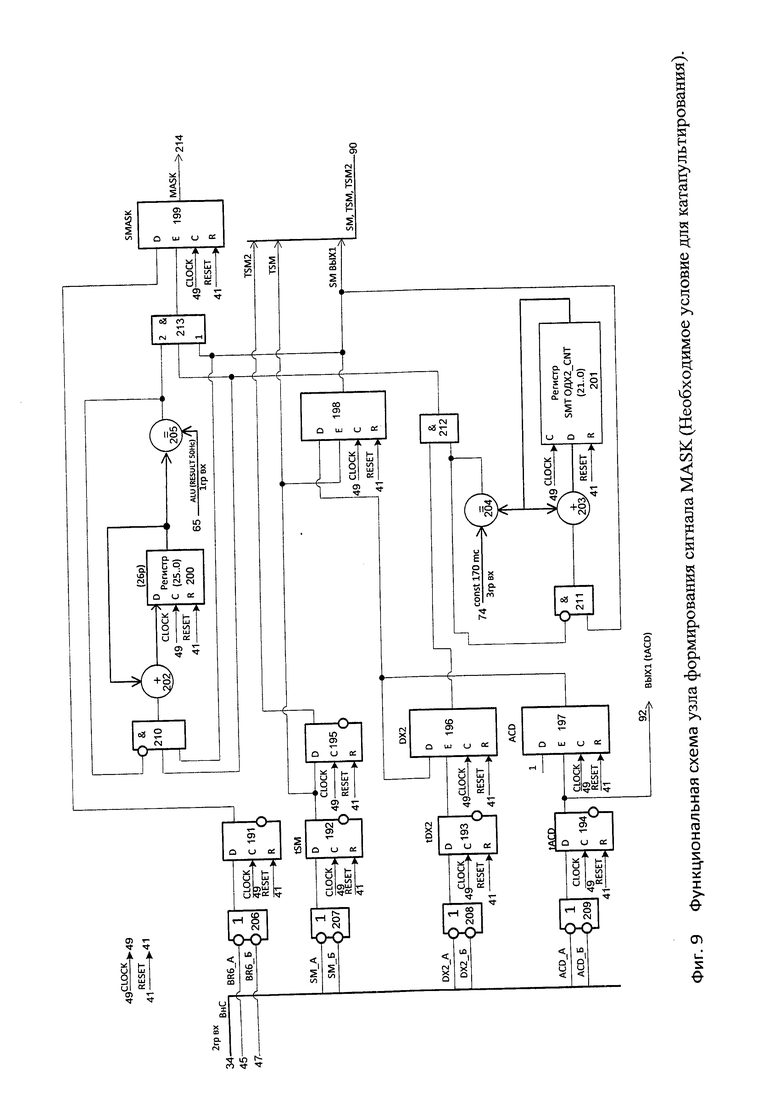

• на фиг. 9 представлена функциональная схема узла формирования сигнала MASK;

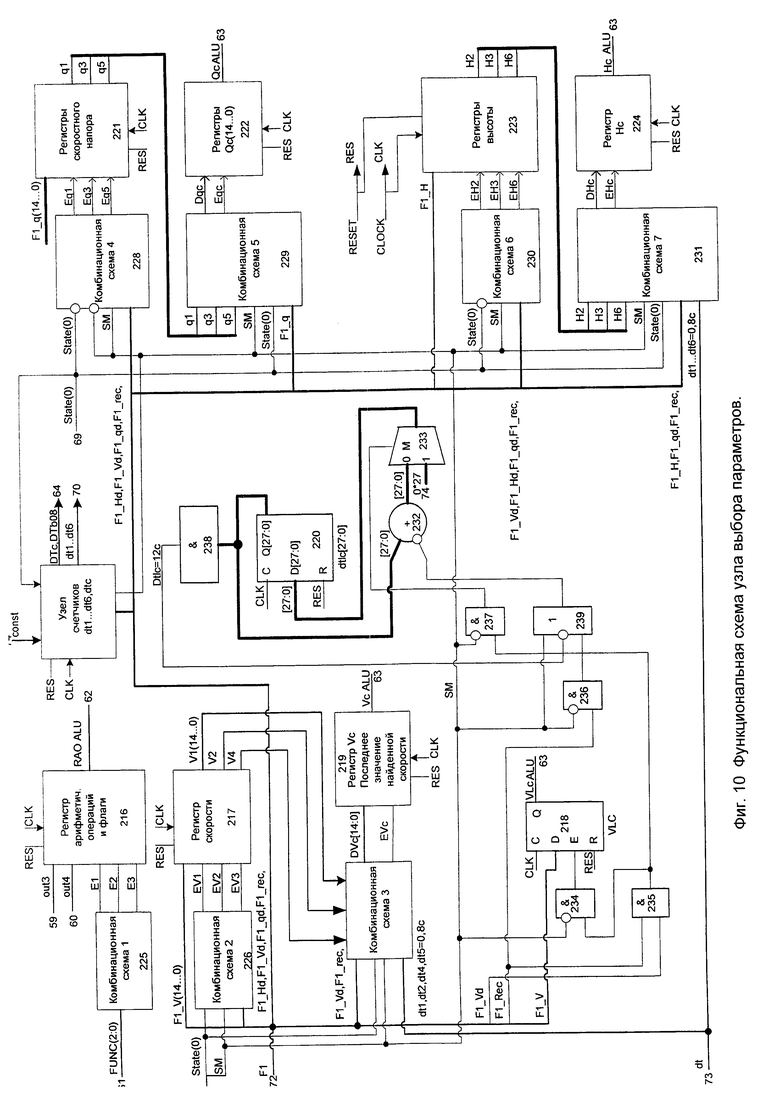

• на фиг. 10 представлена функциональная схема узла выбора параметров;

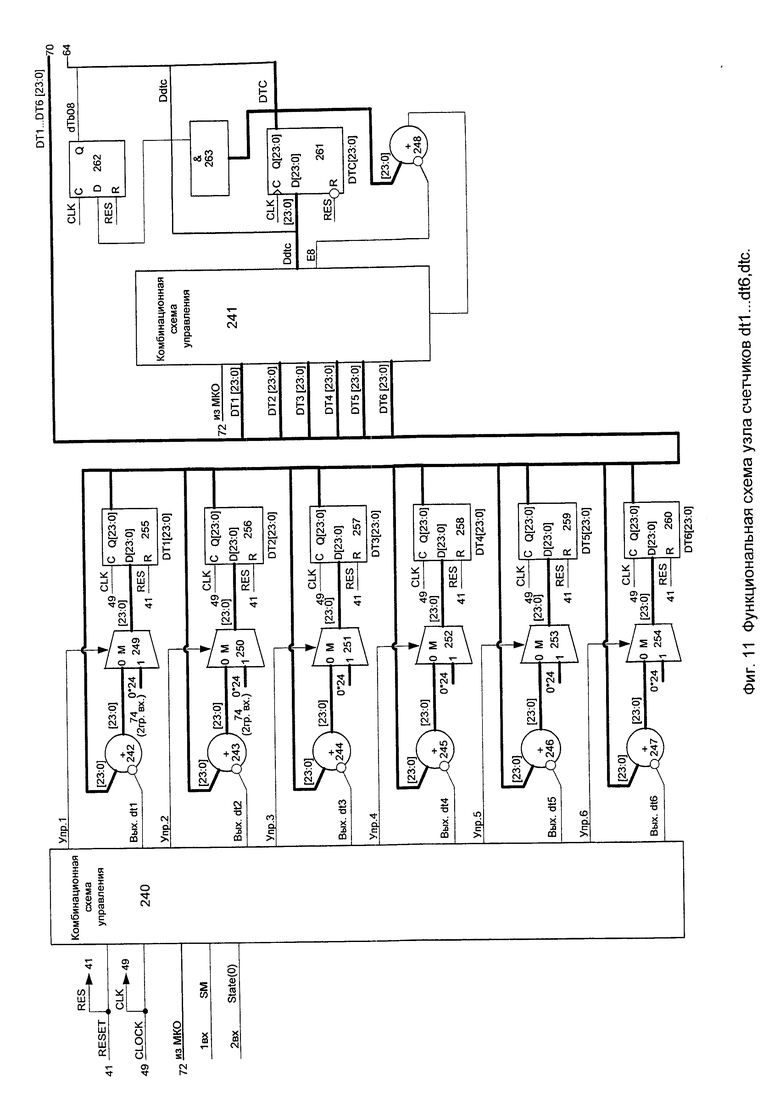

• на фиг. 11 представлена функциональная схема узла счетчиков dt1…dt6, dtc;

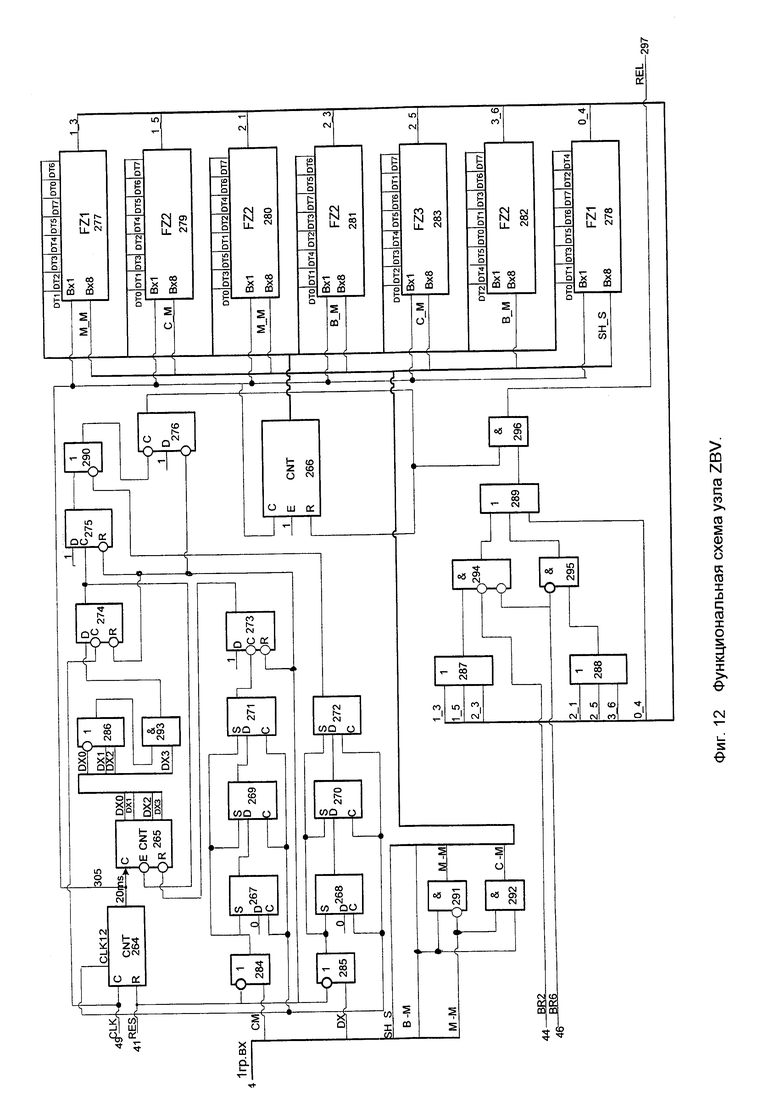

• на фиг. 12 представлена функциональная схема узла ZBV;

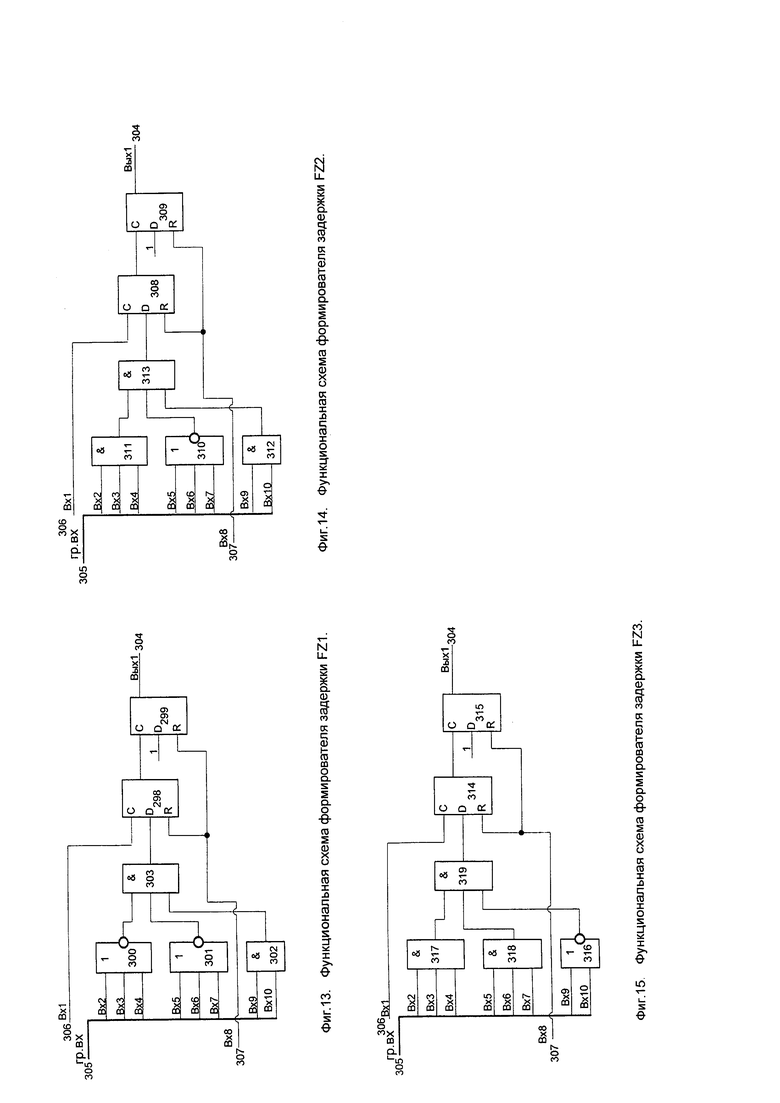

• на фиг. 13 представлена функциональная схема формирователя задержки FZ1;

• на фиг. 14 представлена функциональная схема формирователя задержки FZ2;

• на фиг. 15 представлена функциональная схема формирователя задержки FZ3;

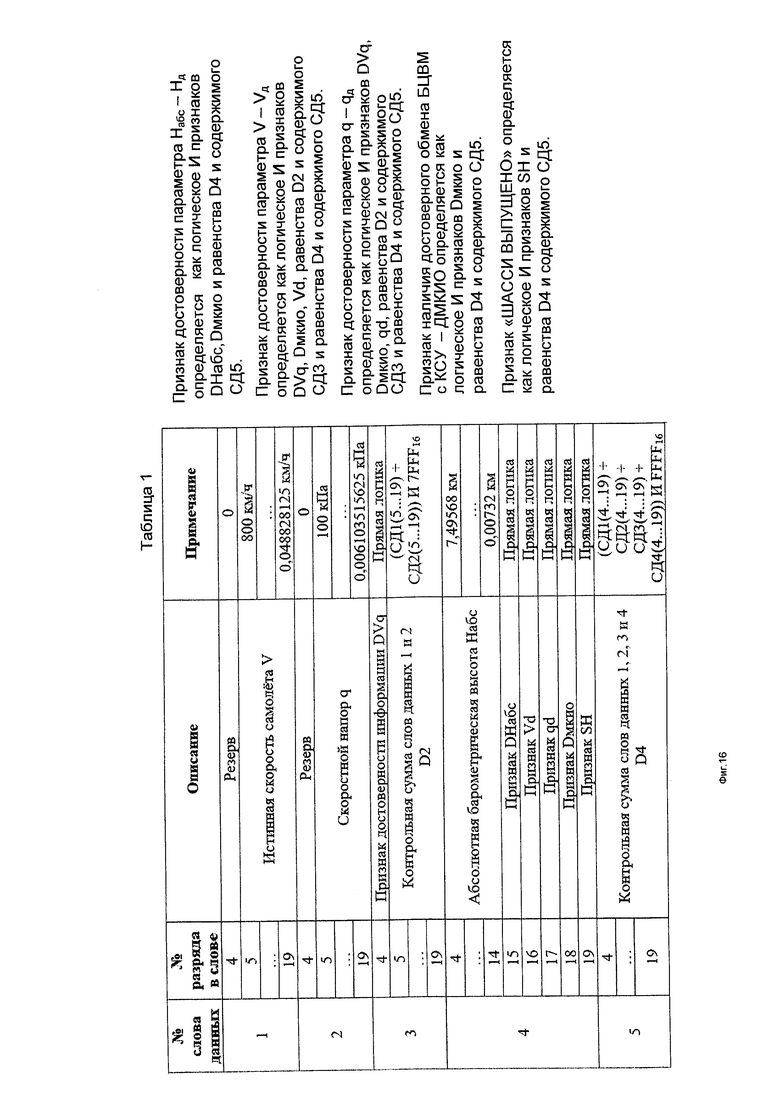

• на фиг. 16 представлена таблица 1, входная цифровая информация;

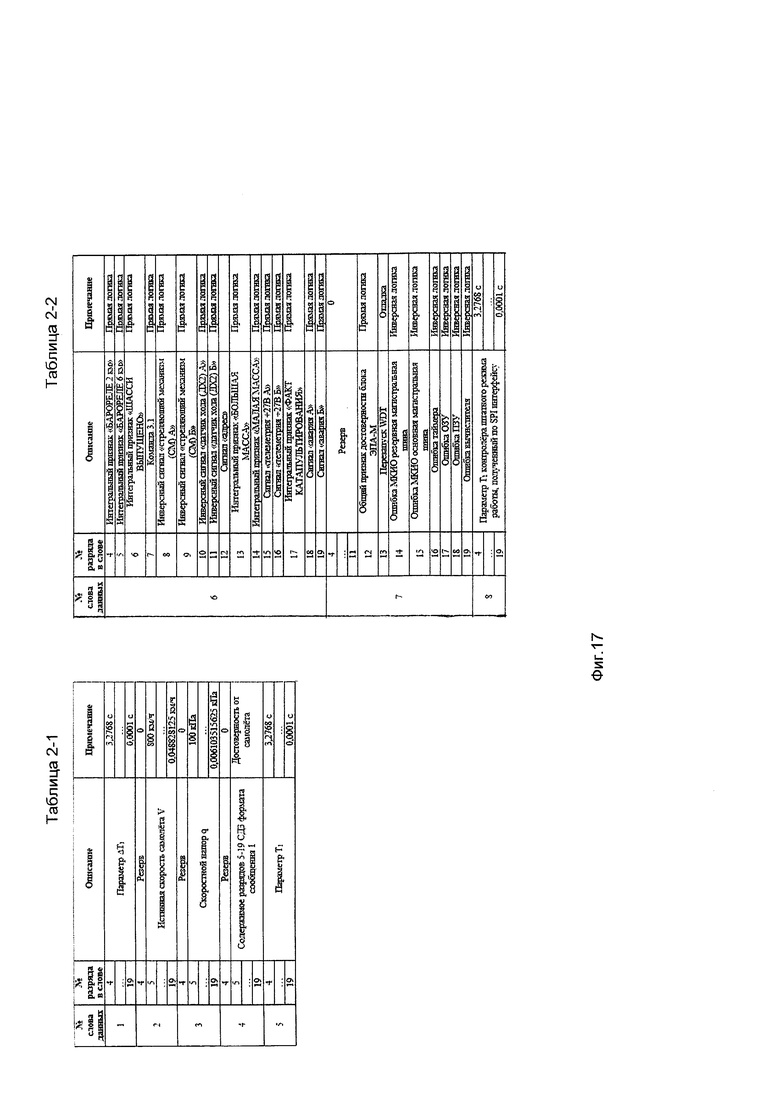

• на фиг. 17 представлены таблица 2-1 и таблица 2-2, выходная цифровая информация;

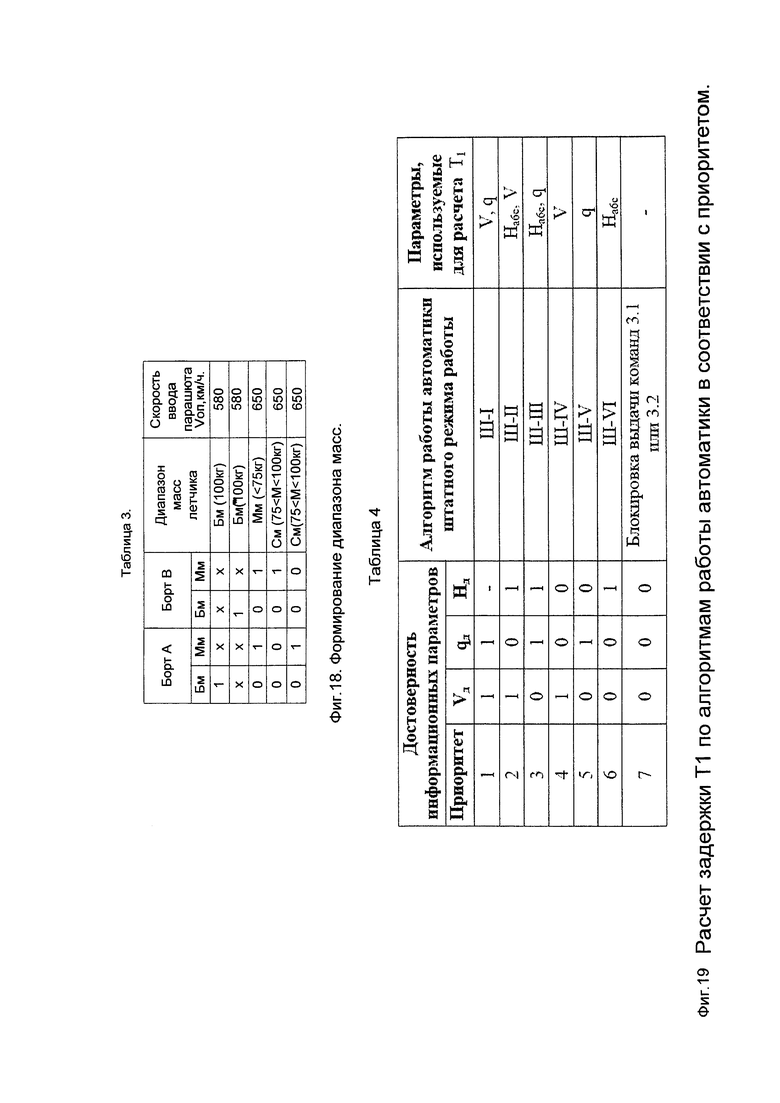

• на фиг. 18 представлена таблица 3, формирование диапазона масс;

• на фиг. 19 представлена таблица 4, расчет задержки Т1 по алгоритмам работы автоматики в соответствии с приоритетом.;

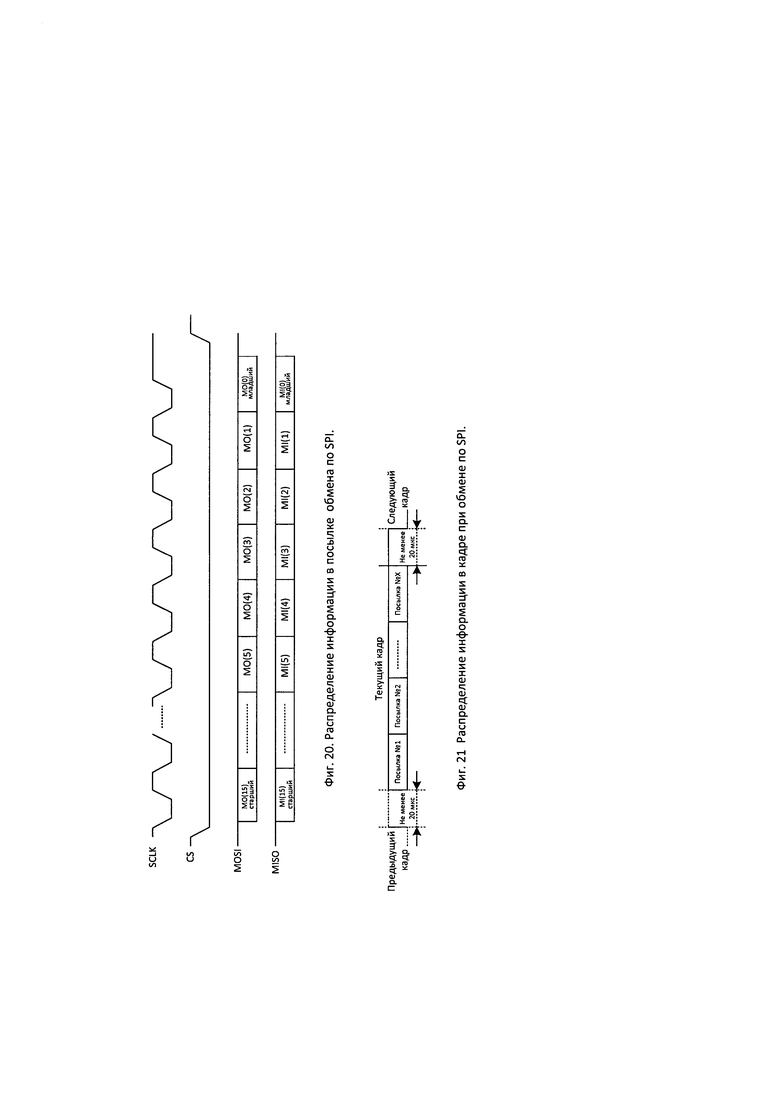

• на фиг. 20 представлено распределение информации в посылке обмена SPI;

• на фиг. 21 представлено распределение информации в кадре обмена SPI;

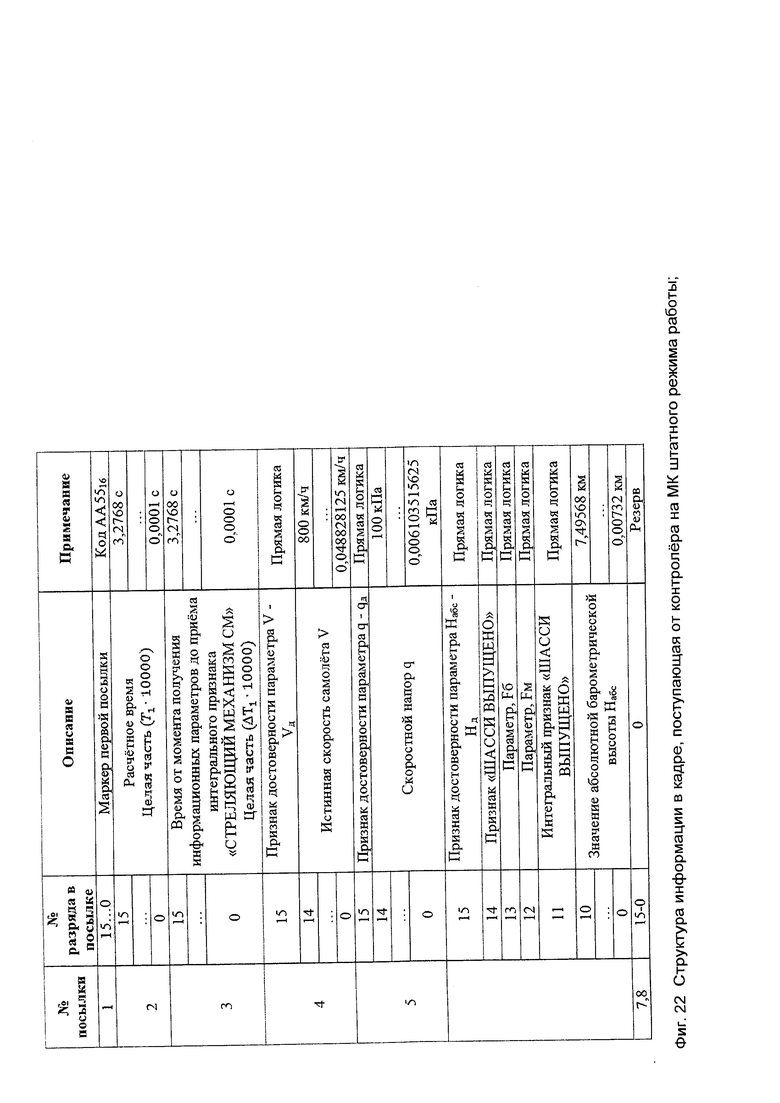

• на фиг. 22 представлена структура информации в кадре, поступающая от контролера на МК штатного режима работы;

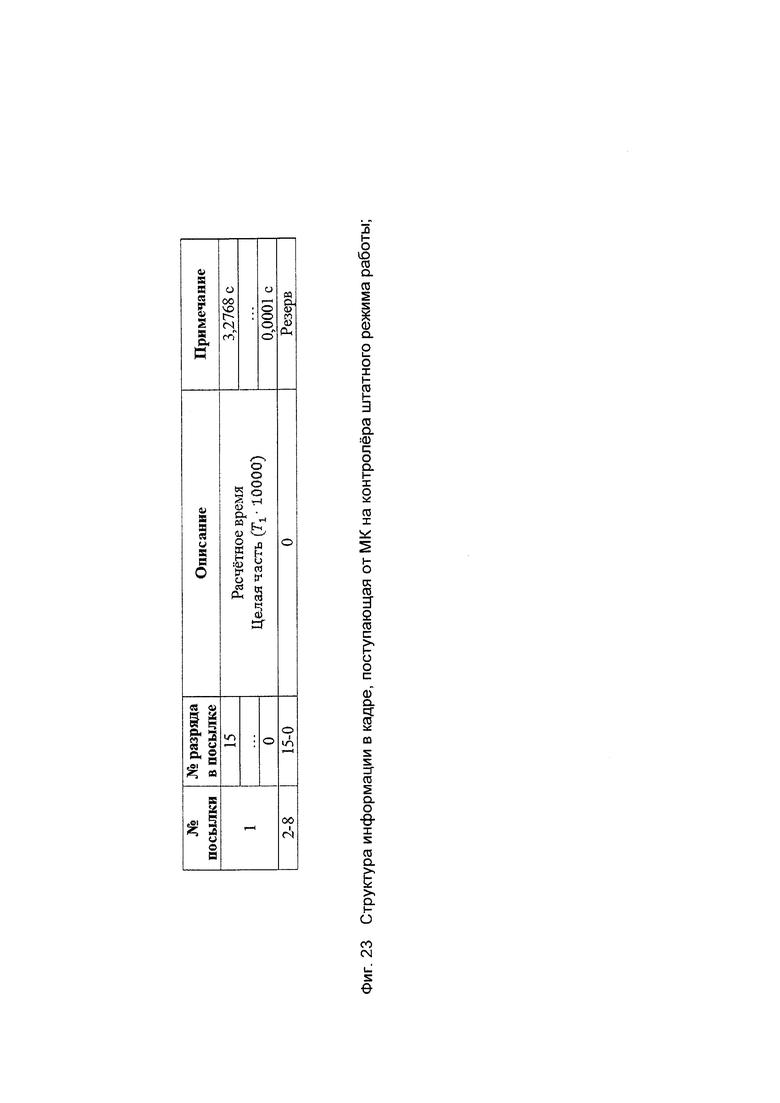

• на фиг. 23 представлена структура информации в кадре, поступающая от МК на контролера штатного режима работы;

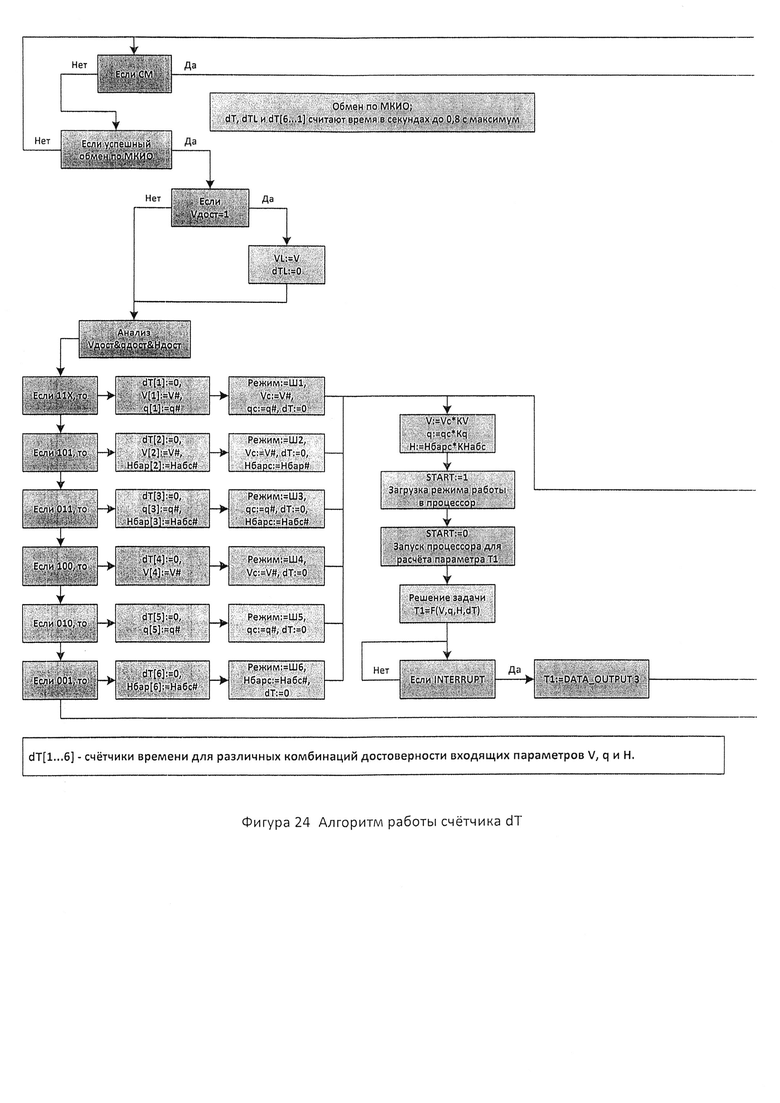

• на фиг. 24 представлен алгоритм работы счетчиков dT;

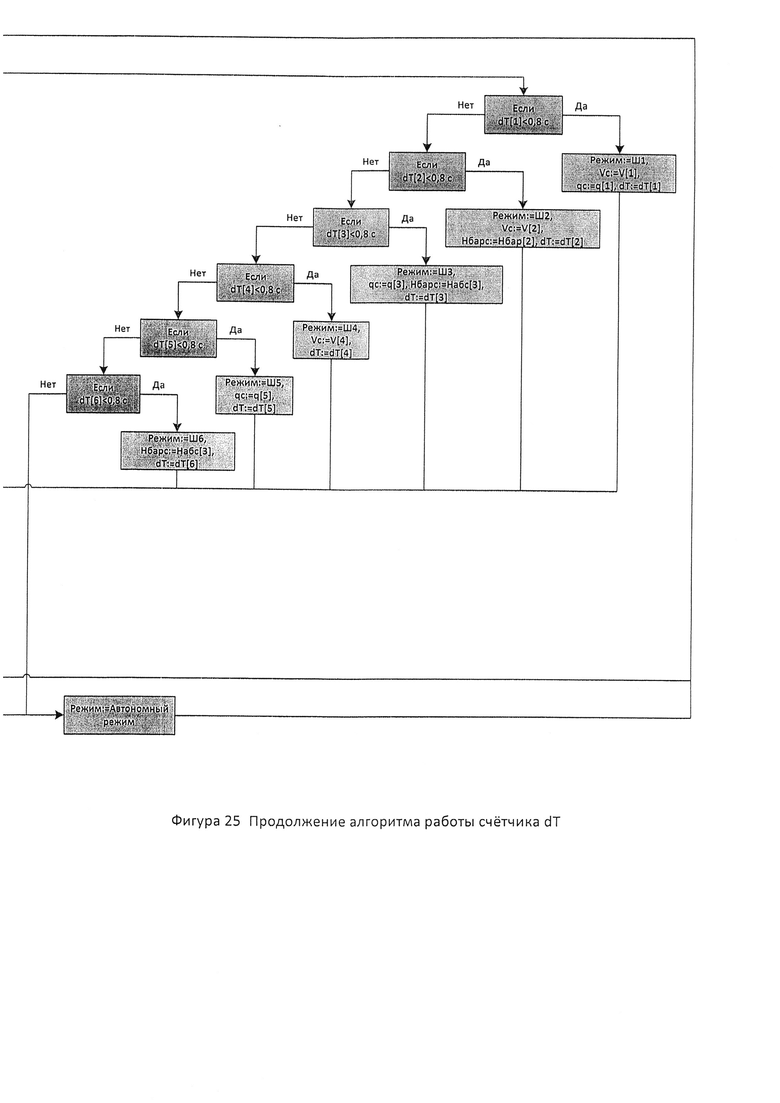

• на фиг. 25 представлено продолжение алгоритма работы счетчиков dT.

Указанные преимущества заявляемого электронного устройства катапультного кресла для самолета перед прототипом достигаются за счет того, что в электронное устройство катапультного кресла для самолета содержащее процессор (CPU) 1, ОЗУ (RAM) 2, ПЗУ (ROM) 3, переключатель 4 (Time Zero Switch), часы 5 (clock), таймер 6, выключатель 7 (Power switch), первый 8, второй 9 и третий 10 датчики давления (PS1-PS3), причем выходы переключателя 4, часов 5 и таймера 6 соединены с первым, вторым и третьим входами процессора 1, первый, второй и третий выходы которого соединены со входами часов 5, таймера 6 и выключателя 7, причем группа входов-выходов процессора 1 соединена с группой входов-выходов ОЗУ 2, группа входов которого соединена с группой выходов процессора 1, группа входов которого соединена с группой выходов ПЗУ 3, дополнительно введены контроллер МКО 11, контролер 12 (Monitoring device), группа оптронов 13, четвертый 14 датчик давления (PS4), первый 15, второй 16, третий 17 и четвертый 18 оптроны, первая 19, вторая 20 и третья 21 схемы сброса по питанию, первый 22, второй 23, третий 24 и четвертый 25 генераторы, первый 26 и второй 27 узлы ZBV (затвора баровременного), первый 28 и второй 29 элементы И, элемент ИЛИ 30, ключ 31, выход которого является выходом 32 ЭУКК, первая 33 группа входов которого соединена с группой оптронов 13, группа выходов 34 которой соединена с первыми группами входов контролера 12, первым 26 и вторым 27 узлами ZBV (затвора баровременного), выходы которых соединены с первым и вторым входами элемента ИЛИ 30, выход которого соединен со входом ключа 31, причем вторая 35 группа входов ЭУКК соединена с первой группой входов контроллера МКО 11 и второй группой входов контролера 12, первый 36 выход которого соединен с первыми входами первого 28 и второго 29 элементов И, выходы которых соединены с третьим и четвертым входами элемента ИЛИ 30, причем первый вход первого узла ZBV (затвора баровременного) 26 соединен с выходом 37 первого генератора 22, выход 38 второго генератора 23 соединен с первым входом второго узла ZBV (затвора баровременного) 27, второй вход которого соединен с выходом 39 второй схемы сброса по питанию 20, выходы 40, 41 первой 19 и третьей 21 схем сброса по питанию соединены со вторым входом первого узла ZBV (затвора баровременного) 26 и с четвертым входом процессора 1 и первым входом контролера 12 соответственно, шина SPI 42 которого соединена с шиной SPI процессора 1, первая группа выходов которого соединена с группой входов ОЗУ 2, причем первый вход 43 ЭУКК соединен с первым, со вторым и пятым входами контроллера МКО 11, контролера 12 и процессора 1, причем третий вход первого узла ZBV (затвора баровременного) 26 соединен с выходом 44 первого оптрона 15, вход которого соединен с выходом первого датчика давления 8, выход второго датчика давления 9 соединен со входом второго оптрона 16, выход 45 которого соединен с третьими входами контролера 12 и второго узла ZBV (затвора баровременного) 27 и с шестым входом процессора 1, причем четвертый вход первого узла ZBV (затвора баровременного) 26 соединен с выходом 46 третьего оптрон 17, вход которого соединен с выходом третьего датчика давления 10, причем выход четвертого датчика давления 14 соединен со входом четвертого оптрона 18, выход 47 которого соединен с четвертым входом второго узла ZBV (затвора баровременного) 27, с четвертым входом контролера 12 и с седьмым входом процессора 1, шина процессора 48 соединена с контроллером МКО 11, причем пятый вход контролера 12 соединен с выходом 49 третьего генератора 24, выход выключателя 7 соединен со вторыми входами первого 28 и второго 29 элементов И, причем выход 50 четвертого генератора 25 соединен с восьмым входом процессора 1.

Контролер (Monitoring device) 12 содержит монитор МКО 51, процессор (CPU) 52, ПЗУ 53, арифметико-логическое устройство (ALU) 54, узел констант (UCONST) 55, узел выбора параметров 56, узел формирования сигнала катапультирования 57, SPI шина 42 которого соединена с SPI шиной контролера 12, выход 32 (сигнал выброса парашюта) которого соединен с первым выходом узла формирования сигнала катапультирования 57, первая 58 группа выходов которого соединена с первой группой входов ALU 54, первая, вторая, третья, четвертая, пятая, шестая группы выходов которого соединены с первой, второй, третьей, четвертой, пятой и шестой группами входов процессора 52, информационная группа входов которого соединена с группой выходов ПЗУ 53, группа входов которого соединена с адресной группой выходов процессора 52, первая, вторая, третья группы выходов которого соединены со второй, третьей и четвертой группами входов ALU 54, седьмая, восьмая, девятая, десятая, одиннадцатая, двенадцатая группы выходов которого соединены с седьмой, восьмой, девятой, десятой, одиннадцатой, двенадцатой группами входов процессора 52, четвертая 59, пятая 60 и шестая 61 группы выходов которого соединены с первой, второй и третьей группами входов узла выбора параметров 56, первая 62, вторая 63 и третья 64 группы выходов которого соединены с пятой, шестой и седьмой группами входов ALU 54, тринадцатая 65 группа выходов которого соединена с первой группой входов узла формирования сигнала катапультирования 57, вторая 66 группа выходов которого соединена с восьмой группой входов ALU 54, девятая группа входов которого соединена со второй группой входов узла формирования сигнала катапультирования 57 и с седьмой 67 группой выходов процессора 52, тринадцатая группа входов которого соединена с третьей 68 группой выходов узла формирования сигнала катапультирования 57, четвертая 69 группа выходов которого соединена с четвертой группой входов узла выбора параметров 56, четвертая 70 группа выходов которого соединена с третьей группой входов узла формирования сигнала катапультирования 57, пятая 71 группа выходов которого соединена с пятой группой входов узла выбора параметров 56, шестая группа входов которого соединена с четвертой группой входов узла формирования сигнала катапультирования 57 и с выходом 72 монитора МКО 51, группа входов которого соединена со второй 35 группой входов контролера 12, второй 43 вход которого соединен со входом монитора МКО 51, тактовый 49 и сбросовый 41 входы которого соединены с тактовыми и сбросовыми входами процессора 52, ALU 54, узла формирования сигнала катапультирования 57, узла выбора параметров 56 и контролера 12, первая 34 группа входов которого соединена с пятой группой входов узла формирования сигнала катапультирования 57, второй 73 выход которого соединен со входом процессора 52, четырнадцатая группа входов которого соединена с седьмой группой входов узла выбора параметров 56, с шестой группой входов узла формирования сигнала катапультирования 57 и с выходом 74 узла констант (UCONST) 55, причем восьмая 75 и девятая 76 группы выходов процессора 52 соединены с седьмой и восьмой группами входов узла формирования сигнала катапультирования 57, первый и второй входы которого являются третьим 45 и четвертым 47 входами контролера 12.

Узел формирования сигнала катапультирования 57 содержит узел SPI_SLAVE 77, узел SPI_STATE 78, узел CMND 79, узел MASK 80, элемент И 81, узел управления 82 и комбинационную схему 83, группа выходов 84 которой соединена с первой группой входов узла SPI_SLAVE 77, группа выходов 85 которого соединена с первой группой входов узла CMND 79, группа выходов которого является второй 66 группой выходов узла формирования сигнала катапультирования 57, шина SPI 42 которого соединена с шиной SPI узла SPI_SLAVE 77, выход 86 которого соединен с первыми входами узлов SPI_STATE 78 и CMND 79, выход 190 которого соединен с первым входом элемента И 81, выход которого является первым выходом 32 узла формирования сигнала катапультирования 57, второй выход 73 которого соединен с первым выходом узла управления 82, второй выход 87 которого соединен со вторыми входами узлов SPI_STATE 78 и CMND 79, вторая группа входов которого соединена с пятой группой входов комбинационной схемы 83, с первой группой выходов 88 узла SPI_STATE 78, вторая 89 группа выходов которого соединена с первой группой входов узла управления 82 и третьим входом узла CMND 79, третья и четвертая группы входов которого соединены с седьмой 75 и восьмой 76 группами входов узла формирования сигнала катапультирования 57, первая 58 группа выходов которого соединена со второй группой выходов узла управления 82, третья и четвертая группы выходов которого соединены с пятой 71 и четвертой 69 группами выходов узла формирования сигнала катапультирования 57, первая 65 группа входов которого соединена с первой группой входов комбинационной схемы 83, с пятой и первой группами входов узлов CMND 79 и MASK 80, группа выходов 90 которого соединена со второй и первой группами входов узла управления 82 и узла SPI_STATE 78, вторая группа входов которого соединена с третьей и шестой группами входов узлов управления 82 и CMND 79 и является второй 67 группой входов узла формирования сигнала катапультирования 57 соответственно, пятая 34 группа входов которого соединена со второй группой входов узла MASK 80 и с четвертой группой входов узла управления 82, пятая 91 группа выходов которого соединена со второй группой входов комбинационной схемы 83, третья группа входов которой является четвертой 72 группой входов узла формирования сигнала катапультирования 57 и соединена с третьим входом узла SPI_STATE 78 и пятой группой входов узла управления 82, первая группа выходов которого является третьей 68 группой выходов узла формирования сигнала катапультирования 57, третья 70 группа входов которого соединена с седьмой группой входов узла управления 82, шестая 74 группа входов узла формирования сигнала катапультирования 57 соединена с четвертой группой входов комбинационной схемы 83, с третьими группами входов узлов MASK 80 и SPI_STATE 78, со второй группой входов узла SPI_SLAVE 77, с седьмой группой входов узла CMND 79 и с шестой группой входов узла управления 82, первый вход которого соединен с первым выходом 92 узла MASK 80, второй 130 выход которого соединен со вторым входом элемента И 81, причем тактовый 49 и сбросовый 41 входы узла формирования сигнала катапультирования 57 соединены с тактовыми и сбросовыми входами узла SPI_SLAVE 77, узла SPI_STATE 78, узла управления 82, узла CMND 79 и узла MASK 80, первый и второй входы которого являются первым 45 и вторым 47 входами узла формирования сигнала катапультирования 57.

Узел SPI_SLAVE 77 содержит первый регистр 93, второй регистр 94, третий регистр 95 и четвертый регистр 96, первый триггер 97, второй триггер 98, третий триггер 99, четвертый триггер 100, пятый триггер 101 и шестой триггер 102, сумматор 103, первый мультиплексор 104, второй мультиплексор 105, третью группу мультиплексоров 106, четвертый мультиплексор 107, пятую группу мультиплексоров 108 и шестую группу мультиплексоров 109, первый элемент И 110, второй элемент И 111, третий элемент И 112, четвертый элемент И 113, пятый элемент И 114, шестой элемент И 115, седьмой элемент И 116 и восьмой элемент И, 117 элемент ИЛИ 118 и элемент 3И-ИЛИ 119, выход которого соединен с информационным входом шестого триггера 102, выход которого является четвертым сигналом шины SPI 42, первый, второй и третий сигналы которой соединены с информационным входом первого триггер 97, с первым входом первого мультиплексора 104, с первым входом второго мультиплексора 105 соответственно, выход которого соединен с информационным входом четвертого триггера 100, выход которого является пятнадцатым разрядом первой группы входов шестой группы мультиплексоров 109, а с нулевого по четырнадцатый разряды которой соединены с группой выходов четвертого регистра 96 и являются группой выходов 85 узла SPI_SLAVE 77, выход 86 которого соединен с выходом пятого триггера 101, инверсный разрешающий вход которого соединен с инверсным разрешающим входом четвертого регистра 96 и выходом шестого элемента И 115, первый инверсный вход которого соединен со входом сумматора 103 и выходом второго элемента И 111, прямой вход которого соединен с выходом второго триггера 98, с инверсным входом третьего элемента И 112 и первым входом четвертого мультиплексора 107, выход которого соединен с информационным входом третьего триггера 99, выход которого соединен с инверсным входом второго элемента И 111 и прямым входом третьего элемента И 112, выход которого соединен с первым инверсным входом первого элемента И 110, выход которого соединен с инверсным разрешающим входом шестого триггера 102 и первым входом элемента ИЛИ 118, выход которого соединен с инверсным разрешающим входом второго регистра 94, группа выходов которого соединена с группой входов третьей группы мультиплексоров 106, а пятнадцатый разряд соединен с первым входом элемента 3И-ИЛИ 119, второй вход которого соединен с выходом пятого элемента И 114, первый инверсный вход которого соединен с инверсным входом четвертого элемента И 113, с третьим входом элемента 3И-ИЛИ 119, управляющими входами первого 104, второго 105, четвертого 107, пятой 108 и шестой 109 группами мультиплексоров, со вторым инверсным входом шестого элемента И 115, с инверсным входом седьмого элемента И 116, с разрешающим входом первого регистра 93, со вторым входом элемента ИЛИ 118, со вторым инверсным входом первого элемента И 110 и выходом первого триггера 97, тактовый вход которого соединен с тактовыми входами второго 98, третьего 99, четвертого 100, пятого 101 и шестого 102 триггеров, с тактовыми входами первого 93, второго 94, третьего 95 и четвертого 96 регистров и с тактовым входом 49 узла SPI_SLAVE 77, сбросовый вход 41 которого соединен с инверсными, установочными входами первого 97, второго 98, третьего 99, четвертого 100 и шестого 102 триггеров и с инверсными сбросовыми входами первого 93, второго 94, третьего 95 и четвертого 96 регистров и пятого триггера 101, информационный вход которого соединен с выходом седьмого элемента 116, первый, второй, третий и четвертый входы которого соединены с инверсной группой входов восьмого элемента И 117, с группой входов сумматора 103 и с группой выходов третьего регистра 95, информационная группа входов которого соединена с группой выходов пятой группы мультиплексоров 108, первая группа входов которой соединена с группой выходов сумматор 103, вторая группа входов пятой группы мультиплексоров 108 соединена с группой входов шестой группы мультиплексоров 109 (константа 0) и с группой входов CONST 74, которая (константа 1) соединена со вторыми входами первого 104, второго 105 и четвертого 107 мультиплексоров и с четвертым входом элемента 3И-ИЛИ 119, пятый вход которого соединен с выходом четвертого элемента И 113, прямой вход которого соединен со вторым инверсным входом пятого элемента И 114, с выходом восьмого элемента И 117 и управляющим входом третьей группы мультиплексоров 106, вторая группа входов которой соединена с группой выходов первого регистра 93, а пятнадцатый разряд которого соединен с шестым входом элемента 3И-ИЛИ 119, причем группа выходов третьей группы мультиплексоров 106 соединена с информационной группой входов второго регистра 94, выход первого мультиплексора 104 соединен с информационным входом второго триггера 98, группа выходов шестой группы мультиплексоров 109 соединена с информационной группой входов четвертого регистра 96, первая группа входов 84 узла SPI_SLAVE 77 соединена с информационной группой входов первого регистра 93.

Узел SPI_STATE 78 содержит первый триггер 120, второй триггер 121, сумматор 122, регистр 123, группу элементов 3И-ИЛИ 124, первый элемент ИЛИ 125, второй элемент ИЛИ 126, третий элемент ИЛИ 127, четвертый элемент ИЛИ 128, первый элемент И 129, второй элемент И 130, третий элемент И 131, четвертый элемент И 132, пятый элемент И 133, шестой элемент И 134, седьмой элемент И 135, восьмой элемент И 136, девятый элемент И 137 и десятый элемент И 138, выход которого соединен с первым входом четвертого элемента ИЛИ 128, выход которого соединен с инверсным входом первого элемента И 129 и является вторым сигналом второй группы выходов 89 узла SPI_STATE 78, первый сигнал которой соединен с информационным входом второго триггера 121 и выходом пятого элемента И 133, прямой вход которого соединен с выходом первого элемента ИЛИ 125, первый вход которого соединен с первым инверсным входом четвертого элемента И 132, с первым входом второго элемента ИЛИ 126 и является первым сигналом четвертой группы входов 72 узла SPI_STATE 78, первая группа выходов 88 которого соединена с группой входов сумматора 122 и группой выходов регистра 123, информационная группа входов которого соединена с группой выходов группы элементов 3И-ИЛИ 124, первый разрешающий вход которой соединен с инверсным входом седьмого элемента И 135 и выходом второго элемента ИЛИ 126, второй вход которого соединен со вторым инверсным входом четвертого элемента И 132 и выходом второго элемента И 130, прямой и инверсный входы которого являются вторым и третьим сигналами первой группы входов 90 узла SPI_STATE 78, первый сигнал которой соединен со вторым входом первого элемента ИЛИ 125, причем вторая группа входов 67 узла SPI_STATE 78 соединена следующим способом: нулевой разряд соединен с прямым входом девятого элемента И 137, первый разряд соединен с первым инверсным входом десятого элемента И 138, второй разряд соединен с первым и вторым инверсными входами девятого 137 и десятого элементов И 138, третий разряд соединен со вторым инверсным и прямым входами девятого 137 и десятого 138 элементов И соответственно, выход девятого элемента И 137 соединен со вторым входом четвертого элемента ИЛИ 128, причем первый вход 86 узла SPI_STATE 78 соединен с информационным входом первого триггера 120 и инверсным входом третьего элемента И 131, выход которого соединен с прямым входом седьмого элемента И 135, третьим инверсным входом четвертого элемента И 132 и первым входом шестого элемента И 134, выход которого соединен со вторым разрешающим входом группы элементов 3И-ИЛИ 124, первая (000) и вторая (111) информационные группы которых являются третьей группой входов 74 узла SPI_STATE 78, второй вход 87 которого соединен с инверсным входом пятого 133 и прямым входом первого 129 элементов И соответственно, выход которого соединен с инверсным разрешающим входом второго триггера 121, выход которого соединен со вторым входом шестого элемента И 134 и инверсным входом восьмого элемента И 136, выход которого соединен с разрешающим входом сумматора 122 и первым входом третьего элемента ИЛИ 127, выход которого соединен с третьим разрешающим входом группы элементов 3И-ИЛИ 124, третья информационная группа входов которого соединена с группой выходов сумматора 122, причем тактовый 49 и сбросовый 41 входы узла SPI_STATE 78 соединены с тактовыми и сбросовыми входами первого 120 и второго 121 триггеров и регистра 123, выход первого триггера 120 соединен с прямым входом третьего элемента И 131, причем выход четвертого элемента И 132 соединен со вторым входом третьего элемента ИЛИ 127, выход седьмого элемента И 135 соединен с прямым входом восьмого элемента И 136.

Узел управления 82 содержит узел сравнения параметров стабилизации КК 139, регистр 140, первый триггер 141, второй триггер 142, третий триггер 143, четвертый триггер 144, пятый триггер 145, шестой триггер 146, седьмой триггер 147, восьмой триггер 148, девятый триггер 149, сумматор 150, комбинационную схему 151, первый элемент И 152, второй элемент И 153, третий элемент И 154, четвертый элемент И 155, пятый элемент И 156, шестой элемент И 157, седьмой элемент И 158, восьмой элемент И 159, девятый элемент И 160, десятый элемент И 161, первый элемент ИЛИ 162, второй элемент ИЛИ 163, третий элемент ИЛИ 164, четвертый элемент ИЛИ 165, пятый элемент ИЛИ 166, шестой элемент ИЛИ 167, выход которого соединен с информационным входом девятого триггер 149, выход которого соединен с первым входом второго элемента ИЛИ 163 и является первым сигналом пятой группы выходов 91 узла управления 82, второй и третий сигналы которой соединены с выходами восьмого 148 и шестого 146 триггеров, информационный вход шестого триггера 146 соединен с инверсным входом девятого элемента И 160 и выходом второго триггера 142, информационный вход которого соединен с выходом первого элемента ИЛИ 162, инверсные входы которого являются первым и вторым сигналами пятой группы входов 34 узла управления 82, третий, четвертый, пятый и шестой сигналы которой соединены с инверсными входами второго элемента И 153 и шестого элемента ИЛИ 167, причем выход второго элемента И 153 соединен с информационным входом первого триггера 141, выход которого соединен с прямым входом девятого элемента И 160, выход которого соединен с информационным входом восьмого триггера 148, разрешающий вход которого соединен с разрешающим входом девятого триггера 149, с инверсным разрешающим входом шестого триггера 146 и является первым входом 92 узла управления 82, первая группа выходов 68 которого соединена с группой выходов регистра 140, информационная группа входов которого соединена с группой выходов комбинационной схемы 151, группа входов которой является четвертой группой входов 72 узла управления 82, второй сигнал которой соединен с информационным входом третьего триггера 143, а первый сигнал соединен с первыми входами пятого 166 и третьего 164 элементов ИЛИ и третьего элемента И 154, выход которого соединен с разрешающим входом третьего триггера 143, выход которого соединен со вторым входом второго элемента ИЛИ 163, выход которого является первым сигналом второй группы выходов 58, второй сигнал которой соединен со вторыми входами третьего 164 и пятого 166 элементов ИЛИ, с первым инверсным входом первого элемента И 152, с инверсным входом пятого элемента И 156, с первым входом комбинационной схемы 151, со второй группой входов 90 узла управления 82 и является первым сигналом четвертой группы выходов 69 узла управления 82, причем третий сигнал второй группы выходов 58 узла управления 82 соединен с выходом пятого триггера 145, информационный вход которого соединен с прямым входом восьмого элемента И 159, с инверсными входами шестого 157, седьмого 158 и десятого 161 элементов И, со вторым инверсным входом первого элемента И 152, с первым входом сумматора 150, с выходом седьмого триггера 147, является вторым сигналом четвертой группы выходов 69 и вторым выходом 87 узла управления 82, третья группа выходов 71 которого соединена со второй группой входов комбинационной схемы 151 и группой выходов узла сравнения параметров стабилизации КК 139, первая группа входов которого соединена с третьей группой входов комбинационной схемы 151 и является пятой группой входов 74 узла управления 82, первая группа входов 89 которого соединена с первыми входами четвертого элемента ИЛИ 165 и пятого элемента И 156, выход которого соединен со вторым входом четвертого элемента ИЛИ 165, выход которого соединен со вторым входом сумматора 150, выход которого соединен с информационным входом седьмого триггера 147, инверсный выход которого соединен со вторым входом пятого элемента И 156, причем вторая группа входов 67 узла управления 82 соединена с первым и вторым инверсными входами и прямым входом четвертого элемента И 155, выход которого соединен с инверсным входом восьмого элемента И 159, выход которого соединен с инверсным разрешающим входом пятого триггера 145, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами первого 141, второго 142, третьего 143, четвертого 144, шестого 146, седьмого 147, восьмого 148, девятого 149 триггеров, регистра 140 и являются тактовым 49 и сбросовым 41 входами узла управления 82, шестая группа входов 70 которого соединена со второй группой входов узла сравнения параметров стабилизации КК 139, причем выход первого элемента И 152 соединен со вторым входом третьего элемента И 154, выход третьего элемента ИЛИ 164 соединен со вторым инверсным входом седьмого элемента И 158 и прямым входом шестого элемента И 157, выход которого соединен с информационным входом четвертого триггера 144, инверсный разрешающий вход которого соединен с выходом седьмого элемента И 158, а выход является первым выходом 73 узла управления 82, причем выход пятого элемента ИЛИ 166 соединен с прямым входом десятого элемента И 161, выход которого соединен с разрешающим входом регистра 140.

Узел формирования сигнала CMND 79 содержит триггер 168, первый регистр 169, второй регистр 170, первый сумматор 171, второй сумматор 172, первый компаратор 173, второй компаратор 174, третий компаратор 175, первую группу мультиплексоров 176, вторую группу мультиплексоров 177, элемент 3И-ИЛИ 178, первый элемент И 179, второй элемент И 180, третий элемент И 181, четвертый элемент И 182, пятый элемент И 183, шестой элемент И 184, седьмой элемент И 185, восьмой элемент И 186, первый элемент ИЛИ 187, второй элемент ИЛИ 188, третий элемент ИЛИ 189, выход которого соединен с инверсным разрешающим входом второго регистра 170, группа выходов которого является первой группой выходов группы выходов 66 узла формирования сигнала CMND 79, вторая группа выходов которой соединена с группой выходов первого регистра 169, информационные входы которого соединены с группой выходов первой группы мультиплексоров 176, первая группа входов которой соединена с первыми группами входов второго 174 и третьего 175 компараторов, с первой группой входов второй группы мультиплексоров 177 и является седьмой группой входов 74 узла формирования сигнала CMND 79, первый выход 190 которого соединен с первым входом элемента 3И-ИЛИ 178 и выходом первого триггера 168, информационный вход которого соединен с выходом элемента 3И-ИЛИ 178, второй вход которого соединен с «питанием», третий вход которого соединен с «корпусом», первый и второй разрешающие входы которого соединены с выходами первого 187 и второго 188 элементов ИЛИ, первый вход второго элемента ИЛИ 188 соединен с выходом шестого элемента И 184, инверсный вход которого соединен с выходом второго компаратора 174 и первым входом четвертого элемента И 182, выход которого соединен с первым входом первого элемента ИЛИ 187, второй вход которого соединен с выходом пятого элемента И 183, первый вход которого соединен с прямым входом седьмого элемента И 185 и выходом третьего элемента И 181, первый вход которого соединен с третьем инверсным разрешающим входом элемента 3И-ИЛИ 178, прямым входом второго элемента И 180 и является первым входом 86 узла формирования сигнала CMND 79, первая группа входов 85 которого соединена с прямой группой входов первого сумматора 171, с первой группой входов первого компаратора 173 и с инверсной группой входов второго сумматора 172, группа выходов которого соединена со второй группой входов третьего компаратора 175, выход которого соединен со вторым входом пятого элемента И 183 и инверсным входом седьмого элемента И 185, выход которого соединен со вторым входом второго элемента ИЛИ 188, причем вторая группа входов 88 узла формирования сигнала CMND 79 соединена с первым, вторым и третьим инверсными входами первого элемента И 179, выход которого соединен с разрешающим входом триггера 168, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами первого 169 и второго 170 регистров и являются тактовым 49 и сбросовым 41 входами узла формирования сигнала CMND 79, третья группа входов 75 которого соединена со второй группой входов первой группы мультиплексоров 176, разрешающий вход которой соединен с разрешающим входом второй группы мультиплексоров 177 и является первым сигналом шестой группы входов 67 узла формирования сигнала CMND 79, четвертая группа входов 76 которого соединена со второй группой входов второй группы мультиплексоров 177, группа выходов которой соединена с информационными входами второго регистра 170, пятая группа входов 65 узла формирования сигнала CMND 79 соединена с прямой и инверсной группами входов второго 172 и первого 171 сумматоров соответственно и со второй группой входов первого компаратора 173, выход которого соединен со вторым входом третьего элемента И 181 и с инверсным входом второго элемента И 180, выход которого соединен с прямым входом шестого элемента И 184 и вторым входом четвертого элемента И 182, второй вход 87 узла формирования сигнала CMND 79 соединен с инверсным входом третьего элемента ИЛИ 189 и прямым входом восьмого элемента И 186, выход которого соединен с прямым входом третьего элемента ИЛИ 189 и с инверсным разрешающим входом первого регистра 169, третий вход 89 узла формирования сигнала CMND 79 соединен с инверсным входом восьмого элемента И 186, причем группа выходов первого сумматора 171 соединена со второй группой входов второго компаратора 174, причем разрешающие входы первого 171 и второго 172 сумматоров соединены с «питанием».

Узел формирования сигнала MASK 80 содержит первый триггер 191, второй триггер 192, третий триггер 193, четвертый триггер 194, пятый триггер 195, шестой триггер 196, седьмой триггер 197, восьмой триггер 198, девятый триггер 199, первый регистр 200, второй регистр 201, первый сумматор 202, второй сумматор 203, первую схему сравнения 204, вторую схему сравнения 205, первый элемент ИЛИ 206, второй элемент ИЛИ 207, третий элемент ИЛИ 208, четвертый элемент ИЛИ 209, первый элемент И 210, второй элемент И 211, третий элемент И 212, четвертый элемент И 213, выход которого соединен с разрешающим входом девятого триггера 199, выход 214 которого является вторым выходом узла формирования сигнала MASK 80, группа выходов 90 которого состоит из трех сигналов: первый сигнал соединен с выходом пятого триггера 195, второй сигнал соединен с информационным и разрешающим входами пятого 195 и восьмого 198 триггеров и выходом второго триггера 192, третий сигнал соединен с первыми входами первого 210 и четвертого 213 элементов И, с прямым входом второго элемента И 211 и выходом восьмого триггера 198, информационный вход которого соединен с информационным входом шестого триггера 196 и выходом седьмого триггера 197, разрешающий вход которого соединен с выходом четвертого триггера 194 и является первым выходом 92 узла формирования сигнала MASK 80, первая группа входов 65 которого соединена с первой группой входов второй схемы сравнения 205, выход которой соединен со вторым входом четвертого элемента И 213 и инверсным входом первого элемента И 210, выход которого соединен с разрешающим входом первого сумматора 202, группа выходов которого соединена с информационной группой входов первого регистра 200, группа выходов которого соединена со второй группой входов второй схемы сравнения 205 и группой входов первого сумматора 202, причем вторая группа входов 34 узла формирования сигнала MASK 80 соединена с инверсными входами второго 207, третьего 208 и четвертого 209 элементов ИЛИ, выходы которых соединены с информационными входами второго 192, третьего 193 и четвертого 194 триггеров соответственно, тактовый и сбросовый входы которых соединены с тактовыми и сбросовыми входами первого 191, пятого 195, шестого 196, седьмого 197, восьмого 198 и девятого 199 триггеров, с тактовыми и сбросовыми входами первого 200 и второго 201 регистров и являются тактовым 49 и сбросовым 41 входами узла формирования сигнала MASK 80, третья группа входов 74 которого соединена с первой группой входов первой схемы сравнения 204, выход которой соединен с инверсным входом второго элемента И 211 и первым входом третьего элемента И 212, выход которого соединен со вторым входом первого элемента И 210 и третьим входом четвертого элемента И 213, причем первый 45 и второй 47 входы узла формирования сигнала MASK 80 соединены с первым инверсным и вторым инверсным входами первого элемента ИЛИ 206, выход которого соединен с информационным входом первого 191 триггера, выход которого соединен с информационным входом девятого 199 триггера, выход третьего триггера 193 соединен с разрешающим входом шестого триггера 196, выход которого соединен со вторым входом третьего элемента И 212, причем группа выходов второго регистра 201 соединена со второй группой входов первой схемы сравнения 204 и группой входов второго сумматора 203, группа выходов которого соединена с информационной группой входов второго регистра 201, а разрешающий вход с выходом второго элемента И 211, информационный вход седьмого триггера 197 соединен с «питанием».

Узел выбора параметров 56 содержит узел счетчиков 215, первый регистр 216, второй регистр 217, третий регистр 218, четвертый регистр 219, пятый регистр 220, шестой регистр 221, седьмой регистр 222, восьмой регистр 223, девятый регистр 224, первую комбинационную схему 225, вторую комбинационную схему 226, третью комбинационную схему 227, четвертую комбинационную схему 228, пятую комбинационную схему 229, шестую комбинационную схему 30, седьмую комбинационную схему 231, сумматор 232, группу мультиплексоров 233, первый элемент И 234, второй элемент И 235, третий элемент И 236, четвертый элемент И 237, пятый элемент И 238, элемент ИЛИ 239, выход которого соединен с инверсным входом сумматора 232, группа выходов которого соединена с первой группой входов группы мультиплексоров 233, группа выходов которой соединена с информационной группой пятого регистра 220, группа выходов которого соединена с группой входов пятого элемента И 238 и с группой входов сумматора 232, третья группа выходов 64 узла выбора параметров 56 соединена с первой группой выходов узла счетчиков 215, вторая группа выходов которого является четвертой группой выходов 70 узла выбора параметров 56, первая группа выходов 62 соединена с группой выходов первого регистра 216, первая и вторая группы входов которого соединены с первой 59 и второй 60 группами входов узла выбора параметров 56, вторая группа выходов 63 которого состоит из групп выходов с третьего 218, четвертого 219, седьмого 222 и девятого регистров 224, третья группа входов 61 узла выбора параметров 56 соединена с группой входов первой комбинационной схемы 225, первый, второй и третий выходы которой соединены с первым, вторым и третьим входами первого регистра 216, первый сигнал четвертой группы входов 69 узла выбора параметров 56 соединен с первыми входами второй 226, третьей 227, пятой 229 и седьмой 231 комбинационными схемами, с инверсными входами четвертой 228 и шестой 230 комбинационными схемами и первым входом узла счетчиков 215, второй вход которого соединен со вторыми входами второй 226, третьей 227, пятой 229 и седьмой 231 комбинационными схемами, с прямым и вторым инверсным входами четвертой комбинационной схемы 228, с прямым входом шестой комбинационной схемы 230, с инверсными входами первого 234, третьего 236 и четвертого 237 элементов И, с первым входом элемента ИЛИ 239 и является вторым сигналом четвертой группы входов 69 узла выбора параметров 56, пятая группа входов 73 которого соединена с первыми группами входов третьей 227 и седьмой 231 комбинационными схемами, группа выходов и выход седьмой комбинационной схемы 231 соединены с группой входов и входом девятого регистра 224, шестая группа входов 72 узла выбора параметров 56 соединена с первыми группами входов второй 226, четвертой 228, пятой 229 и шестой 230 комбинационными схемами и вторым регистром 217, шестым регистром 221 и восьмым регистром 223, со вторыми группами входов третьей 227 и седьмой 231 комбинационными схемами, с первой группой входов узла счетчиков 215, группа сигналов F1_V и сигналы F1_Vd, F1_Rec шестой группы входов соединены с информационным входом третьего регистра 218, первым и вторым входами второго 235 элемента И и прямым входом третьего элемента И 236 соответственно, седьмая группа входов 74 узла выбора параметров 56 соединена со вторыми группами входов группы мультиплексоров 233 и узла счетчиков 215, тактовый и сбросовый входы которого соединены с тактовыми и сбросовыми входами первого 216, второго 217, третьего 218, четвертого 219, пятого 220, шестого 221, седьмого 222, восьмого 223, девятого 224 регистров и являются тактовым 49 и сбросовым 41 входами узла выбора параметров 56, причем первый, второй и третий выходы второй комбинационной схемы 226 соединены с первым, вторым и третьим входами второго регистра 217, первая группа выходов которого соединена с третьей группой входов третьей комбинационной схемой 227, вторая и третья группы входов которой соединены со второй и третьей группами выходов второго регистра 217, причем группа выходов и выход третьей комбинационной схемы 227 соединены с группой входов и входом четвертого регистра 219, выход второго элемента И 235 соединен с прямыми входами четвертого 237 и первого 234 элементов И, выход которого соединен с разрешающим входом третьего регистра 218, выход третьего элемента И 236 соединен со вторым входом элемента ИЛИ 239, инверсный вход которого соединен с выходом пятого элемента И 238, первый, второй и третий выходы четвертой комбинационной схемы 228 соединены с первым, вторым и третьим входами шестого регистра 221, первая, вторая и третья группы выходов которого соединены со второй, третьей и четвертой группами входов пятой комбинационной схемы 229, группа выходов и выход которой соединены с группой входов и входом седьмого регистра 222, первый, второй и третий выходы шестой комбинационной схемы 230 соединены с первым, вторым и третьим входами восьмого регистра 223, первая, вторая и третья группы выходов которого соединены с третьей, четвертой и пятой группами входов седьмой комбинационной схемы 231, причем выход четвертого элемента И 237 соединен с управляющим входом группы мультиплексоров 233.

Узел счетчиков 215 содержит первую комбинационную схему 240, вторую комбинационную схему 241, первый сумматор 242, второй сумматор 243, третий сумматор 244, четвертый сумматор 245, пятый сумматор 246, шестой сумматор 247, седьмой сумматор 248, первую группу мультиплексоров 249, вторую группу мультиплексоров 250, третью группу мультиплексоров 251, четвертую группу мультиплексоров 252, пятую группу мультиплексоров 253, шестую группу мультиплексоров 254, первый регистр 255, второй регистр 256, третий регистр 257, четвертый регистр 258, пятый регистр 259, шестой регистр 260, седьмой регистр 261, триггер 262 и элемент И 263, выход которого соединен с информационным входом триггера 262, выход которого является первым сигналом первой группы выходов 64 узла счетчиков 215, первая и вторая группы выходов которой соединены с группой входов элемента И 263, с группой входов седьмого сумматора 248, с группой выходов седьмого регистра 261 и информационной группой входов седьмого регистра 261, с группой выходов второй комбинационной схемы 241 соответственно, выход которой соединен с разрешающим входом седьмого регистра 261 и с инверсным входом седьмого сумматора 248, выход которого соединен со входом второй комбинационной схемы 241, первая группа входов которой соединена с группой входов первой комбинационной схемы 240 и является первой группой входов 72 узла счетчиков 215, вторая группа выходов которого соединена со второй, третьей, четвертой, пятой, шестой и седьмой группами входов второй комбинационной схемы 241, с группами входов первого 242, второго 243, третьего 244, четвертого 245, пятого 246 и шестого 247 сумматоров и с группами выходов первого 255, второго 256, третьего 257, четвертого 258, пятого 259 и шестого 260 регистров, информационные входы которых соединены с группами выходов первой 249, второй 250, третьей 251, четвертой 252, пятой 253 и шестой 254 группами мультиплексов, первые группы входов которых соединены между собой и являются второй группой входов 74 узла счетчиков 215, первый и второй входы которого соединены с первым и вторым входами первой комбинационной схемы 240, первый, второй, третий, четвертый, пятый и шестой выходы которой соединены с инверсными входами первого 242, второго 243, третьего 244, четвертого 245, пятого 246 и шестого 247 сумматоров, группы выходов которых соединены со вторыми группами входов первых 249, вторых 250, третьих 251, четвертых 252, пятых 253 и шестых 254 групп мультиплексоров, управляющие входы которых соединены с седьмым, восьмым, девятым, десятым, одиннадцатым и двенадцатым выходами первой комбинационной схемы 240 соответственно, причем тактовый 49 и сбросовый 41 входы узла счетчиков 215 соединены с тактовыми и инверсными сбросовыми входами первого 255, второго 256, третьего 257, четвертого 258, пятого 259, шестого 260, седьмого 261 регистров и триггера 262.

Узел ZBV (затвор баровременной) 26 (27) содержит первый счетчик 264, второй счетчик 265, третий счетчик 266, первый триггер 267, второй триггер 268, третий триггер 269, четвертый триггер 270, пятый триггер 271, шестой триггер 272, седьмой триггер 273, восьмой триггер 274, девятый триггер 275, десятый триггер 276, первый формирователь задержки FZ1 277, второй формирователь задержки FZ1 278, первый формирователь задержки FZ2 279, второй формирователь задержки FZ2 280, третий формирователь задержки FZ2 281, четвертый формирователь задержки FZ2 282, формирователь задержки FZ3 283, первый элемент ИЛИ 284, второй элемент ИЛИ 285, третий элемент ИЛИ 286, четвертый элемент ИЛИ 287, пятый элемент ИЛИ 288, шестой элемент ИЛИ 289, седьмой элемент ИЛИ 290, первый элемент И 291, второй элемент И 292, третий элемент И 293, четвертый элемент И 294, пятый элемент И 295, шестой элемент И 296, выход которого является выходом 297 узла ZBV 26, первая 34 группа входов которого соединена с прямым входом первого элемента ИЛИ 285 (первый сигнал СМ), с прямым входом второго элемента ИЛИ 285 (второй сигнал DX), с восьмым входом второго формирователя задержки FZ1 278 (третий сигнал SH_S), с прямым входом первого элемента И 291, с первым входом второго элемента И 292, с восьмыми входами третьего 281 и четвертого 282 формирователей задержки FZ2 (четвертый сигнал В_М), с инверсным и вторым входом первого 291 и второго 292 элементов И (пятый сигнал М_М), выход первого элемента И 291 соединен с восьмыми входами первого 277 и второго 280 формирователей задержки FZ1 и FZ2, выход второго элемента И 292 соединен с восьмыми входами первого формирователя задержки FZ2 279 и формирователя задержки FZ3 283, группы входов которых соединены с группами входов первого 277 и второго 278 формирователей задержки FZ1, второго 280, третьего 281 и четвертого 282 формирователей задержки FZ2 и группой выходов третьего счетчика 266, тактовый вход которого соединен с первыми входами первого 277 и второго 278 формирователей задержки FZ1, первого 279, второго 280, третьего 281 и четвертого 282 формирователей задержки FZ2 и формирователя задержки FZ3 283, с тактовым входом второго счетчика 265 и выходом первого счетчика 264, тактовый вход которого соединен с инверсным тактовым входом восьмого триггера 274 и является первым входом 49 узла ZBV 26, первый вход шестого элемента И 296 соединен со сбросовым входом третьего счетчика 266 и выходом десятого триггера 276, инверсный тактовый вход которого соединен с выходом седьмого элемента ИЛИ 290, прямой вход которого соединен с выходом девятого триггера 275, информационный вход которого соединен с «питанием», с разрешающим входом третьего счетчика 266, с информационными входами седьмого 273 и десятого 276 триггеров, инверсный сбросовый вход которого соединен с инверсными сбросовыми входами седьмого 273, восьмого 274 и девятого 275 триггеров, с инверсными входами первого 284 и второго 285 элементов ИЛИ, со сбросовым входом первого счетчика 264 и является вторым входом 41 узла ZBV 26, третий вход 44 которого соединен с первым инверсным входом четвертого элемента И 294, выход которого соединен с первым входом шестого элемента ИЛИ 289, выход которого соединен со вторым входом шестого элемента И 296, причем четвертый вход 46 узла ZBV 26 соединен с инверсным входом пятого элемента И 295 и со вторым инверсным входом четвертого элемента И 294, прямой вход которого соединен с выходом четвертого элемента ИЛИ 287, первый, второй и третий входы которого соединены с выходами первого формирователя задержки FZ1 277, первого 279 и третьего 281 формирователей задержки FZ2 соответственно, второй 280 и четвертый 282 формирователи задержки FZ2 и формирователь задержки FZ3 283 соединены со входами пятого элемента ИЛИ 288, выход которого соединен с прямым входом пятого элемента И 295, выход которого соединен со вторым входом шестого элемента ИЛИ 289, третий вход которого соединен с выходом второго формирователя задержки FZ1 278, причем второй выход первого счетчика 264 соединен с тактовыми входами первого 267, второго 268, третьего 269, четвертого 270, пятого 271 и шестого 272 триггеров, установочные входы которых соединены с выходами первого 284 и второго 285 элементов ИЛИ, причем с «корпусом» соединены информационные входы первого 267 и второго 268 триггеров, выходы которых соединены с информационными входами третьего 269 и четвертого 270 триггеров, выходы которых соединены с информационными входами пятого 271 и шестого 272 триггеров, выходы которых соединены с инверсным тактовым входом седьмого триггера 273 и инверсным входом седьмого элемента ИЛИ 290 соответственно, выход восьмого триггера 274 соединен с тактовым входом девятого триггера 275 и инверсным разрешающим входом второго счетчика 265, выход седьмого триггера 273 соединен с инверсным сбросовым входом второго счетчика 265, группа выходов которого соединена с группой входов третьего элемента ИЛИ 286 и первым входом третьего элемента И 293, второй вход которого соединен с выходом третьего элемента ИЛИ 286, а выход соединен с информационным входом восьмого триггера 274.

Формирователь задержки FZ1 277 содержит первый триггер 298, второй триггер 299, первый элемент ИЛИ-НЕ 300, второй элемент ИЛИ-НЕ 301, первый элемент И 302, второй элемент И 303, выход которого соединен с информационным входом первого триггера 298, выход которого соединен с тактовым входом второго триггера 299, выход которого является выходом 304 формирователя задержки FZ1 277, группа входов 305 которого соединена с группами входов первого 300 и второго 301 элементов ИЛИ-НЕ и первого элемента И 302, выходы которых являются входами второго элемента И 303, причем первый вход 306 формирователя задержки FZ1 277 соединен с тактовым входом первого триггера 298, сбросовый вход которого является восьмым входом 307 формирователя задержки FZ1 277 и соединен со сбросовым входом второго триггера 299, информационный вход которого соединен с «питанием».

Формирователь задержки FZ2 279 содержит первый триггер 308, второй триггер 309, элемент ИЛИ-НЕ 310, первый элемент И 311, второй элемент И 312 и третий элемент И 313, выход которого соединен с информационным входом первого триггера 308, выход которого соединен с тактовым входом второго триггера 309, выход которого является выходом 304 формирователя задержки FZ2 279, группа входов 305 которого соединена с группами входов первого 311 и второго 312 элементов И и элемента ИЛИ-НЕ 310, выходы которых являются входами третьего элемента И 313, причем первый вход 306 формирователя задержки FZ2 279 соединен с тактовым входом первого триггера 308, сбросовый вход которого является восьмым входом 307 формирователя задержки FZ2 279 и соединен со сбросовым входом второго триггера 309, информационный вход которого соединен с «питанием».

Формирователь задержки FZ3 283 содержит первый триггер 314, второй триггер 315, элемент ИЛИ-НЕ 316, первый элемент И 317, второй элемент И 318 и третий элемент И 319, выход которого соединен с информационным входом первого триггера 314, выход которого соединен с тактовым входом второго триггера 315, выход которого является выходом 304 формирователя задержки FZ3 283, группа входов 305 которого соединена с группами входов первого 317 и второго 318 элементов И и элемента ИЛИ-НЕ 316, выходы которых являются входами третьего элемента И 319, причем первый вход 306 формирователя задержки FZ3 283 соединен с тактовым входом первого триггера 314, сбросовый вход которого является восьмым входом 307 формирователя задержки FZ3 283 и соединен со сбросовым входом второго триггера 315, информационный вход которого соединен с «питанием».

Электронное устройство катапультного кресла для самолета (ЭУКК) работает следующим образом.

Принцип работы ЭУКК заключается в получении информации от систем самолета о параметрах полета самолета в момент катапультирования, таких как: скорость, скоростной напор и высота полета, состояние шасси и выработки временной задержки на ввод парашюта в зависимости от установленной массы пилота в соответствии с архитектурой представленной на фиг. 1, состоящей из вычислителя штатного режима работы, работающего в качестве оконечного устройства (ОУ) по магистральному последовательному интерфейсу системы электронных модулей ГОСТ Р 52070-2003 (далее - МКИО) осуществляющего точный расчет времени выброса основного парашюта КК по алгоритмам Ш-I, Ш-II, Ш-III, Ш-IV, Ш-V, Ш-VI и выдающий команду 3.1; контролера штатного режима работы, работающего в качестве монитора шины (МШ) (Monitoring device) по МКИО осуществляющего расчет времени выброса основного парашюта КК по алгоритмам Ш-I, Ш-II, Ш-III, Ш-IV, Ш-V, Ш-VI и выдающий команду 3.2; двух идентичных вычислителей автономного режима работы, осуществляющих упрощенный расчет времени выброса основного парашюта по автономному алгоритму, и выдающих команды 1.1, 1.2, 2.1 и 2.2. Вычислитель и контролер штатного режима работы после расчетов времени выброса основного парашюта КК обмениваются результатами расчетов и только при их совпадении (с некоторой точностью) выдают команды 3.1 и 3.2 соответственно.

Быстрый алгоритм

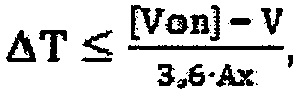

При наличии интегрального признака «ШАССИ ВЫПУЩЕНО» время T1=0,4 с. Если при отсутствии интегрального признака «ШАССИ ВЫПУЩЕНО» до момента появления интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)» во временном диапазоне  где Ах=15,1 [м/с2] - принятое максимально возможное ускорение движения самолета при V<Vоп, последнее принятое достоверное значения было такое, что V<Vоп, то T1=0,4 с. В остальных случаях в данном алгоритме время T1 определено быть не может.

где Ах=15,1 [м/с2] - принятое максимально возможное ускорение движения самолета при V<Vоп, последнее принятое достоверное значения было такое, что V<Vоп, то T1=0,4 с. В остальных случаях в данном алгоритме время T1 определено быть не может.

Алгоритм Ш-I

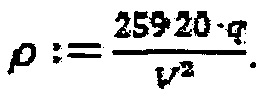

Шаг 1: рассчитывается плотность атмосферы ρ [кг/м3] по формуле:

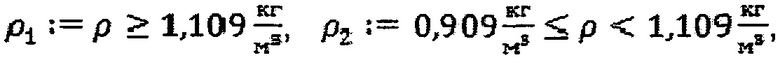

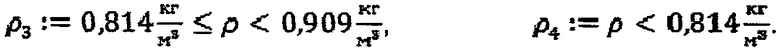

Шаг 2: рассчитываются логические коэффициенты по формулам:

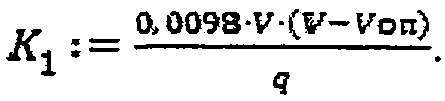

Шаг 3: рассчитывается коэффициент K1 [км2/кПа] по формуле:

Шаг 4: рассчитывается прогнозируемая скорость V* [км/ч] по формуле:

V*:=V+ΔV, где ΔV:=43,5 км/ч.

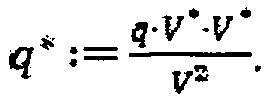

Шаг 5: рассчитываются прогнозируемый скоростной напор q* [кПа] по формуле:

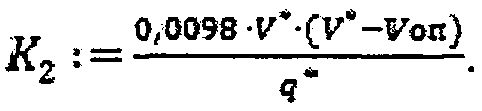

Шаг 6: рассчитывается коэффициент K2 [км2/кПа] по формуле:

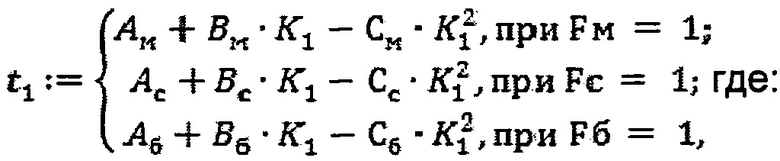

Шаг 7: рассчитывается задержка t1 [с] по формуле:

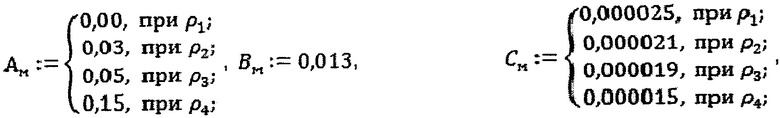

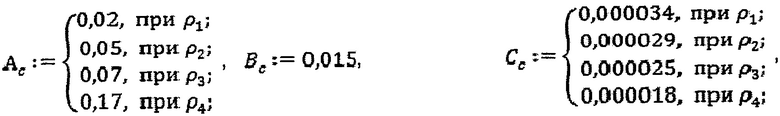

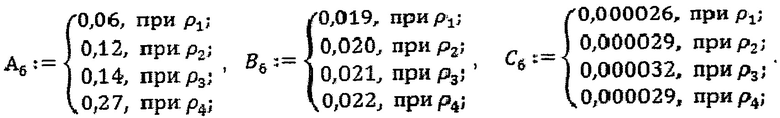

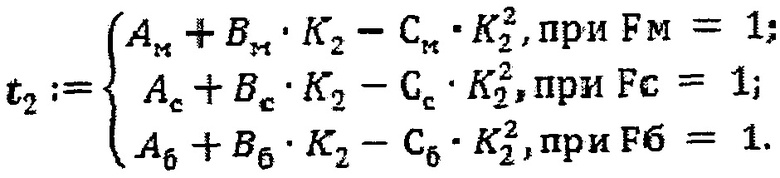

Шаг 8: рассчитывается задержка t2 [с] по формуле:

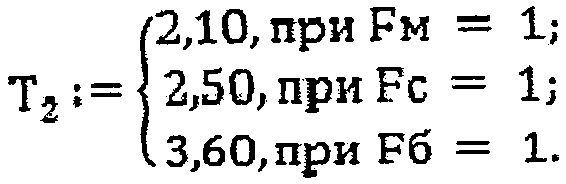

Шаг 9: рассчитывается параметр Т2 [с] по формуле:

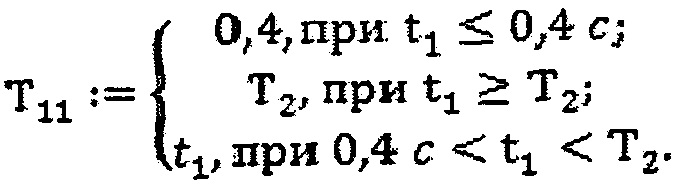

Шаг 10: рассчитывается параметр Т11 [с] по формуле:

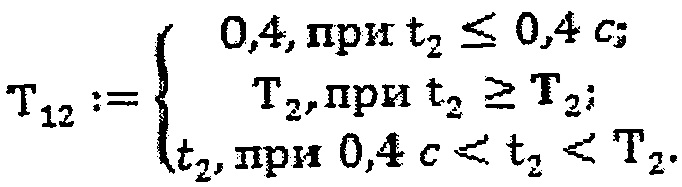

Шаг 11: рассчитывается параметр Т12 [с] по формуле:

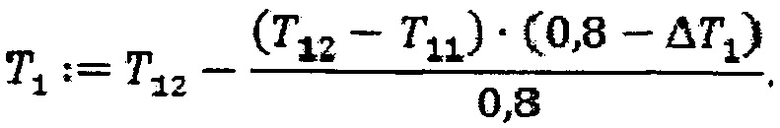

Шаг 12: рассчитывается время T1 [с] по формуле:

Алгоритм Ш-II

Шаг 1: рассчитывается плотность атмосферы ρНабс [кг/м3] по формуле:

ρНабс:=1,090-0,088⋅Hабс+0,0004⋅Набс2.

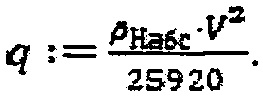

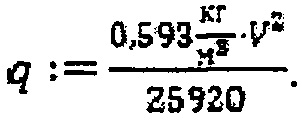

Шаг 2: рассчитывается скоростной напор q [кПа] по формуле:

Шаг 3: вычисляем время T1 по алгоритму Ш-I.

Алгоритм Ш-III

Шаг 1: рассчитывается плотность атмосферы ρНабс [кг/м3] по формуле:

ρНабс:=1,090-0,088⋅Набс+0,0004⋅Набс2.

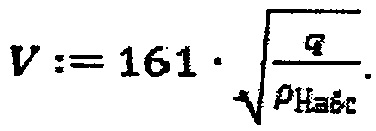

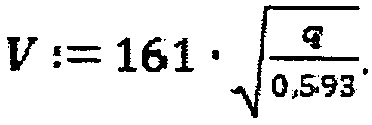

Шаг 2: рассчитывается истинная скорость самолета V [км/ч] по формуле:

Шаг 3: вычисляем время T1 по алгоритму Ш-I.

Алгоритм Ш-IV

Шаг 1: рассчитывается скоростной напор q [кПа] по формуле:

Шаг 2: вычисляем время T1 по алгоритму Ш-I.

Алгоритм Ш-V

Шаг 1: рассчитывается истинная скорость самолета V [км/ч] по формуле:

Шаг 2: вычисляем время T1 по алгоритму Ш-I.

Алгоритм Ш-VI

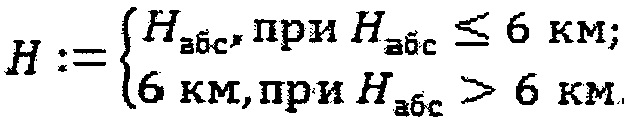

Шаг 1: рассчитывается значение высоты Н [км] по формуле:

Шаг 2: рассчитывается время T1 [с] по следующей формуле:

Структурная схема ЭУКК представлена на фиг. 2.

ЭУКК состоит из трех независимых узлов: узел вычислительного режима (процессор 1, RAM 2, ROM 3, контролер 12), узел автономного режима борта A (ZBV 26), узел автономного режима борта В (ZBV 27).

ЭУКК основного режима имеет в своем составе:

- МКИО основного и резервного канала на базе приемо передатчиков 5559ИН74Т манчестерского кода по ГОСТ Р 52070-2003;

- вычислитель на базе микроконтроллера (МК) 1986ВЕ1Т;

- контролер на базе перепрограммируемой микросхемы (ПЛИС) А3РЕ1500-1PQG208I;

МК и контролер принимают данные по МКИО от систем самолета, производят расчет в соответствии с алгоритмами Ш-I, Ш-II, Ш-III, Ш-IV, Ш-V, Ш-VI в основном режиме и обмениваются данными по шине «SPI».

В случае, если рассчитанный МК программным способом интервал не совпадает с полученным в контролере (ПЛИС), с учетом допустимого отклонения, не более чем на 0,0064 с, сигнал на выброс парашюта блокируется.

Таким образом реализуется выполнение функции канала (МК) - Модель (ПЛИС).

Также сигнал на выброс парашюта блокируется при первом включении питания на время (10±5) мс.

В ЭУКК постоянно поступает аналоговая информация по борту А и по борту В:

- сигналы «шасси выпущено А» и «шасси выпущено В», определяющие факт нахождения самолета на земле;

- сигналы «малая масса А» и «малая масса В», определяющие массу пилота как малую;

- сигналы «большая масса А» и «большая масса В», определяющие массу пилота как большую;

- сигналы «авария А» и «авария В», определяющие начало процедуры аварийного покидания самолета пилотом;

- сигналы «стреляющий механизм (СМ) А» и «стреляющий механизм В», определяющие факт срабатывания пиропатронов;

- сигналы «датчик хода (ДХ2) А» и «датчик хода В», определяющие факт начала движения КК;

- сигналы «телеметрия +27В А» и «телеметрия +27В В», определяющие факт наличия основного питания;

- сигналы «факт катапультирования (ФК) А» и «факт катапультирования В», определяющие факт работы механизма катапультирования;

- сигналы «барореле 6 км А» и «барореле 6 км В», определяющие факт того, что КК находится ниже высоты 6 км;

- сигналы «барореле 2 км А» и «барореле 2 км В», определяющие факт того, что КК находится ниже высоты 2 км.

В ЭУКК постоянно поступает аналоговая конфигурационная информация: сигнал «адрес», определяющий младший разряд собственного адреса ОУ и МШ.

Аналоговая информация, поступающая в ЭУКК в виде сигналов типа «сухой контакт» / «обрыв», перекодируется в значения логическая единица «1» / логический ноль «0» соответственно и используется далее в математике алгоритма.

ЭУКК по результатам своей работы по настоящему алгоритму выдает аналоговый сигнал «ввод основного парашюта» типа «сухой контакт» / «обрыв», определяющий начало процедуры ввода основного парашюта КК.

ОУ и МШ имеют собственный адрес 4 или 5, в зависимости от сигнала «адрес» и к ним регулярно поступает запрос на прием цифровой информации от борта самолета по формату 1 и подадресу 8. ОУ и МШ принимают эту информацию, структура слов данных (СД) которой представлена в таблице 1 фиг. 16. По результатам приема информации ОУ в соответствии с МКИО выдает ответное слово (ОС) с результатами приема.

К ОУ и МШ регулярно поступает запрос на передачу цифровой информации борту самолета по формату 2 и подадресу 12. ОУ и МШ принимают запрос, ОУ выдает ОС с результатом приема запроса и выдает информацию, структура СД которой представлена в таблице 2, а МШ контролирует ее.

Интегральный признак «ШАССИ ВЫПУЩЕНО» вычислителя и контролера штатного режима работы определяется логическим «ИЛИ» 167 признака «ШАССИ ВЫПУЩЕНО» (Тг 149) и защелок «шасси выпущено А» и «шасси выпущено В».

Значения защелок «шасси выпущено А» и «шасси выпущено В» вычислителя и контролера штатного режима работы при отсутствии интегрального признака «АВАРИЯ» повторяют значения аналоговых сигналов «шасси выпушено А» и «шасси выпущено В» соответственно, а при наличии интегрального признака «АВАРИЯ» (ИЛИ 209, Тг197) их значения не меняются.

Значения защелок «шасси выпущено А» и «шасси выпущено В» узлов автономного режима работы запоминаются при их включении на основе значений аналоговых сигналов «шасси выпущено А» и «шасси выпущено В» соответственно.

Диапазоны масс «МАЛАЯ МАССА», «СРЕДНЯЯ МАССА», «БОЛЬШАЯ МАССА», определяются в соответствии с табл. 3 формирование диапазона масс.

«МАЛАЯ МАССА» и «СРЕДНЯЯ МАССА» формируются на элементах И 291 и И 292 фиг. 12 соответственно.

Значения защелок «МАЛАЯ МАССА А» и «МАЛАЯ МАССА В», «БОЛЬШАЯ МАССА А» и «БОЛЬШАЯ МАССА В» вычислителя и контролера штатного режима работы при отсутствии интегрального признака «АВАРИЯ» повторяют значения аналоговых сигналов «МАЛАЯ МАССА А» и «МАЛАЯ МАССА В» и «БОЛЬШАЯ МАССА А» и «БОЛЬШАЯ МАССА В» соответственно, а при наличии интегрального признака «АВАРИЯ» их значения не меняются.

Значения защелок «МАЛАЯ МАССА А» и «МАЛАЯ МАССА В», «БОЛЬШАЯ МАССА А» и «БОЛЬШАЯ МАССА В» узлов автономного режима работы запоминаются при их включении на основе значений аналоговых сигналов «МАЛАЯ МАССА А» и «МАЛАЯ МАССА В», «БОЛЬШАЯ МАССА А» и «БОЛЬШАЯ МАССА В» «малая масса А» и «малая масса Б» соответственно.

В зависимости от значений масс «МАЛАЯ МАССА» и «БОЛЬШАЯ МАССА» принимаются следующие значения скорости ввода парашюта Vоп, представленные в таблице 3 на фиг. 18.

Интегральный признак «ДАТЧИК ХОДА 2 (ДХ2)» (ИЛИ 208 фиг. 9) вычислителя штатного режима работы инициирует процедуру сохранения в энергонезависимую память ROM 3 следующих информационных параметров:

- истинная скорость самолета V;

- скоростной напор q;

- значение абсолютной барометрической высоты Набс;

- признак достоверности параметра V - Vд;

- признак достоверности параметра q - qд;

- признак достоверности параметра Набс - Н;

- алгоритм работы автоматики штатного режима работы (название);

- собственное расчетное значение параметра Т1;

- расчетное значение параметра Т1 контролера штатного режима работы;

- телеметрию сигнала «шасси выпущено А»;

- телеметрию сигнала «малая масса А»;

- телеметрию сигнала «большая масса А»;

- телеметрию сигнала «авария А»;

- телеметрию сигнала «стреляющий механизм (СМ) А»;

- телеметрию сигнала «датчик хода (ДХ2) А»;

- телеметрию сигнала «телеметрия +27В А»;

- телеметрию сигнала «факт катапультирования (ФК) А»;

- телеметрию сигнала «барореле 6 км А»;

- телеметрию сигнала «барореле 2 км А»;

- телеметрию сигнала «шасси выпущено В»;

- телеметрию сигнала «малая масса В»;

- телеметрию сигнала «большая масса В»;

- телеметрию сигнала «авария В»;

- телеметрию сигнала «стреляющий механизм (СМ) В»;

- телеметрию сигнала «датчик хода (ДХ) В»;

- телеметрию сигнала «телеметрия +27В В»;

- телеметрию сигнала «факт катапультирования (ФК) В»;

- телеметрию сигнала «барореле 6 км В»;

- телеметрию сигнала «барореле 2 км В»;

- телеметрию сигнала «адрес».

При приеме информации по МКИО с ДМКИО = «1» (признак наличия достоверного обмена) микроконтроллером (1-7, 11, 25) и контролером (12) штатного режима работы осуществляется расчет временной задержки Т1 в соответствии с быстрым алгоритмом. Если быстрый алгоритм не может вычислить задержку Т1, то расчет осуществляется в соответствии с алгоритмами указанными в таблице 4 на фиг. 19 в зависимости от параметров Vд, qд, Нд. МК штатного режима работы инициирует обмен информацией с контролером штатного режима работы по SPI интерфейсу не позднее, чем через 5 мс после приема информации по МКИО с ДМКИО = «1». При этом под временем ΔТ1 (0 с <=ΔТ1<=0,8 с) подразумевается интервал времени от момента получения выбранных параметров по МКИО до выполнения расчета.

При передаче информации по МКИО контролер осуществляет проверку достоверности передаваемой информации МК штатного режима работы.

В случаях, если обмен по SPI интерфейсу не произошел или временная задержка Т1 различается более, чем на 0,0064 с МК и/или контролер штатного режима работы блокирует выдачу команд 3.1 и/или 3.2 соответственно, в зависимости от того, кто из них обнаружил указанное нарушение. В случае если контролер штатного режима работы обнаружил несоответствие передаваемой информации по МКИО своим ожиданиям, то он блокирует выдачу команды 3.2.

Если на момент приема интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)» (ИЛИ 207, Тг 192) в предшествующем временном интервале 0,8 с присутствуют информационные сообщения, то расчет МК и контролером штатного режима работы временной задержки Т1 осуществляется в соответствии с быстрым алгоритмом. Если МК по быстрому алгоритму не может вычислить задержку Т1, то расчет осуществляется по алгоритмам в соответствии с приоритетом, указанным в таблице 4 фиг. 19. При этом под временем ΔТ1 (0 с <=ΔТ1<=0,8 с) подразумевается интервал времени от момента получения достоверных информационных параметров, выбранных в соответствии с приоритетом, до приема интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)». Если в предшествующем временном интервале 0,8 с нет информационных сообщений, то осуществляется блокировка выдачи команд 3.1 и/или 3.2. МК штатного режима работы инициирует обмен информацией с контролером штатного режима работы по SPI интерфейсу не позднее, чем через 5 мс после приема информации по МКИО с ДМКИО = «1».

Узлы ZBV (26, 27) автономного режима работы при наличии интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)» вычисляют временную задержку по автономному алгоритму.

МК штатного режима работы является главным (Master), а контролер штатного режима работ является подчиненным (Slave) блоком в SPI-интерфейсе, представляемым на физическом уровне 4-х проводным интерфейсом, содержащим следующие сигналы:

- SCLK - сигнал тактовой частоты, выдаваемой блоком Master;

- CS - сигнал выбора блока Slave (активный «0»);

- MOSI - сигнал, содержащий данные, идущие от блока Master;

- MISO - сигнал, содержащий данные, идущие от блока Slave.

Временная диаграмма, показывающая распределение двоичных разрядов информации в посылке обмена SPI 42 представлена на фиг. 20.

Одна посылка обмена передает в оба блока по 16 двоичных разрядов.

Взаимодействие блоков Master и Slave на канальном уровне представляет собой посылку кадров по SPI-интерфейсу 42, разделенных синхронизирующей паузой между собой (фиг. 21).

Кадр состоит из X посылок, где X может быть в диапазоне от 1 до 8. При инициировании блоком Master и более посылок информация в них циклически повторяется (с обновлением).

Кадр автоматически начнется с посылки №1 при возникновении интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)», а также после приема достоверных данных с правильной контрольной суммой по формату 1 интерфейса ГОСТ Р 52070-2003 для МК и контролера штатного режима работы.

Структура информации в кадре, поступающая от контролера 12 на МК штатного режима работы представлена в таблице 5 фиг. 22.

Структура информации в кадре, поступающая от МК на контролера 12 штатного режима работы представлена в таблице 6 фиг. 23.

Функциональная схема контролера 12 представлена на фиг. 3.

Контролер состоит из процессора 52, ALU 54, ПЗУ53, узла констант 55, монитор МКО 51, узел выбора параметров 56, узел формирования сигнала катапультирования 57.

Процессор 52, ALU 54 и ПЗУ53 обеспечивают выполнение быстрого алгоритма и алгоритмов работы автоматики штатного режима работы.

Узел МКИО 51 обеспечивает обмен данными по МК между ЭУКК и системой самолета.

Узел выбора параметров 56 предназначен для выбора и хранения параметров из протокола МКО, для определения максимального времени безопасного катапультирования в быстром алгоритме.

Узел формирования сигнала катапультирования 57 предназначен для формирования необходимого и достаточного признака катапультирования.

Функциональная схема узла формирования сигнала катапультирования 57 представлена на фиг. 4.

Узел формирования сигнала катапультирования 57 состоит из узлов SPI_SLAVE 77, SPI_STATE 78, CMND 79, MASK 80, узла управления 82 и комбинационной схемы 83.

Узел SPI_SLAVE 77 предназначен для обмена данными между процессором 1 и контролером 12 по шине SPI 42, временная диаграмма обмена представлена на фиг. 20.

Узел SPI_STATE 78 предназначен для передачи кадра по шине SPI 42 (фиг. 21).

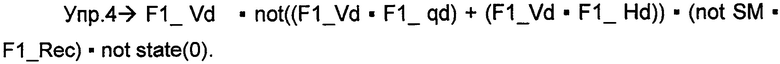

Узел CMND 79 предназначен для формирования достоверного условия для катапультирования.

Узел MASK 80 предназначен для формирования разрешения на катапультирование.

Узел управления 82 обеспечивает управление узлами узла формирования сигнала катапультирования 57 и формирование сигнала START (73).

Комбинационная схема 83 обеспечивает формирование данных для узла SPI_SLAVE 77.

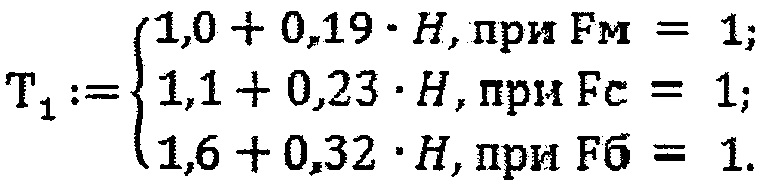

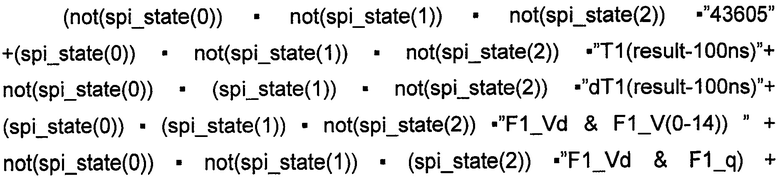

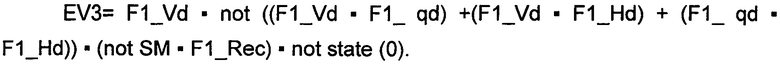

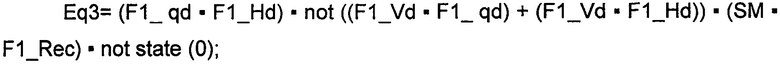

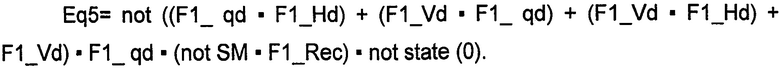

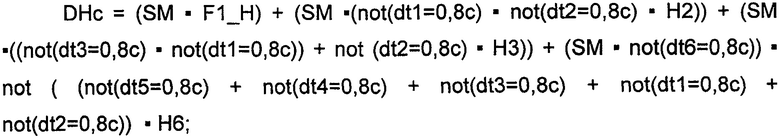

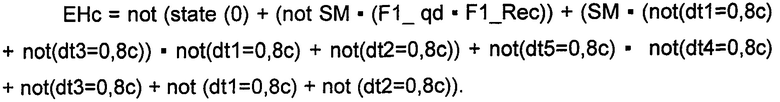

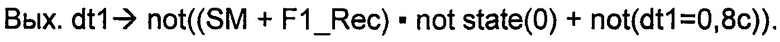

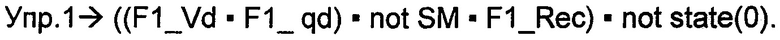

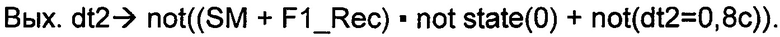

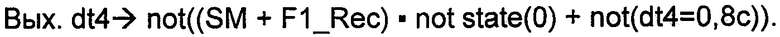

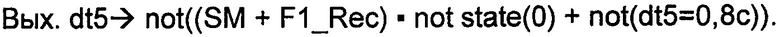

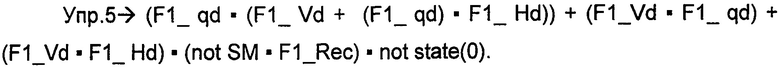

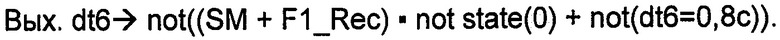

Комбинационная схема 83 имеет следующую формулу:

где « » - логическое И, «+» - логическое ИЛИ.

» - логическое И, «+» - логическое ИЛИ.

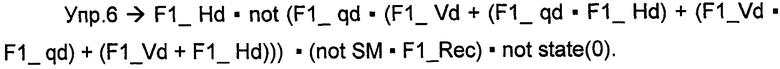

Функциональная схема узла выбора параметров 56 представлена на фиг. 9.

Узел выбора параметров 56 состоит из узлов регистра арифметических операций и флагов 216, регистра скорости V 217, регистра последнего значения найденной скорости Vc 219, регистра скорости из МКО Vlc 218, регистра скоростного напора Q 221, регистра скоростного напора из МКО Qc 222, регистра высоты Н 223 и регистра высоты из МКО Нc 224 первая комбинационная схема 225, вторая комбинационная схема 226, третья комбинационная схема 227, четвертая комбинационная схема 228, пятая комбинационная схема 229, шестая комбинационная схема 230, седьмая комбинационная схема 231, узла счетчиков dt1..dt6, dtc, счетчика предельного значения Δt (регистр 220, сумматор 232 и мультиплексор 233).

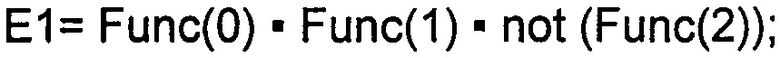

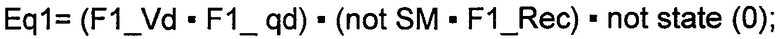

Первая комбинационная схема 225 узла выбора параметров 56 обеспечивает формирование разрешающих сигналов Е1, Е2, Е3 для приема данных в регистр арифметических операций и флагов.

Первая комбинационная схема 225 имеет следующую формулу:

Е3=Е1+Е2.

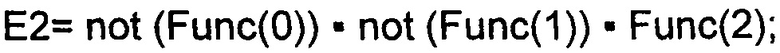

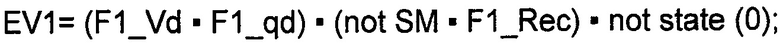

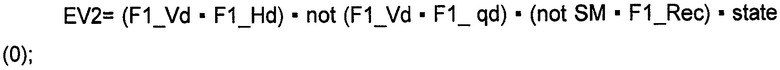

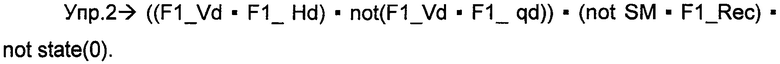

Вторая комбинационная схема 226 узла выбора параметров 56 обеспечивает формирование разрешающих сигналов EV1, EV2, EV3 для приема данных в регистры скорости 217 в зависимости от параметров достоверности представленных в таблице 4 (регистр V1 → (достоверна скорость Vд и скоростной напор qд), регистр V2 → (достоверна скорость Vд и высота Нд), регистр V3 → (достоверна скорость Vд)).

Вторая комбинационная схема 226 имеет следующую формулу:

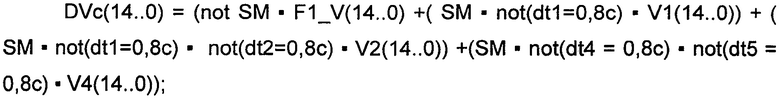

Третья комбинационная схема 227 узла выбора параметров 56 обеспечивает формирование разрешающего сигнала EVc для приема данных и данные DVc(14..0) в регистр Vc, в котором хранится последнее значение найденной скорости.

Третья комбинационная схема 227 имеет следующую формулу:

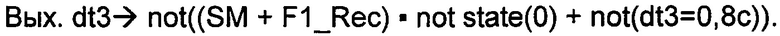

Четвертая комбинационная схема 228 узла выбора параметров 56 обеспечивает формирование разрешающих сигналов Eq1, Eq3, Eq5 для приема данных в регистры скоростного напора 221 в зависимости от параметров достоверности, представленных в таблице 4 (регистр q1 → (достоверна скорость Vд и скоростной напор qд), регистр q3 → (достоверна высота Нд и скоростной напор qд), регистр q5 → (достоверен скоростной напор qд)).

Четвертая комбинационная схема 228 имеет следующую формулу:

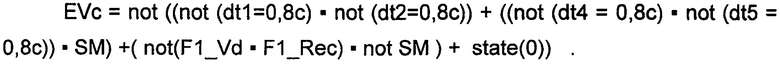

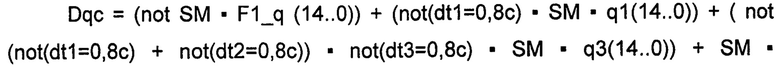

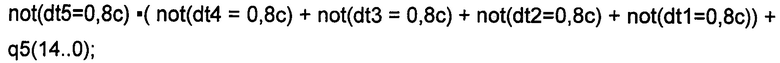

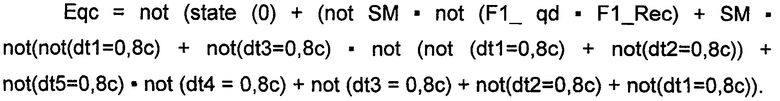

Пятая комбинационная схема 229 узла выбора параметров 56 обеспечивает формирование разрешающего сигнала Eqc для приема данных и данные Dqc в регистр Qc, в котором хранится последнее значение скоростного напора.

Пятая комбинационная схема 229 имеет следующую формулу:

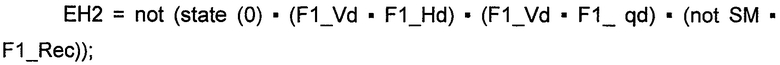

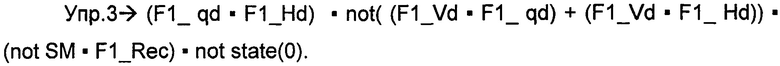

Шестая комбинационная схема 230 узла выбора параметров 56 обеспечивает формирование разрешающих сигналов ЕН2, ЕН3, ЕН6 для приема данных в регистры высоты 223 в зависимости от параметров достоверности, представленных в таблице 4 (регистр Н2 → (достоверна скорость Vд и высота Нд), регистр Н3 → (достоверна высота Нд и скоростной напор qд), регистр Н6 → (достоверна высота Нд)).

Шестая комбинационная схема 230 имеет следующую формулу:

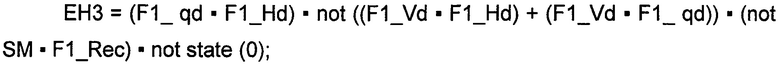

Седьмая комбинационная схема 231 узла выбора параметров 56 обеспечивает формирование разрешающего сигнала ЕНс для приема данных и данные DHc в регистр Нc, в котором хранится последнее значение высоты.

Седьмая комбинационная схема 231 имеет следующую формулу:

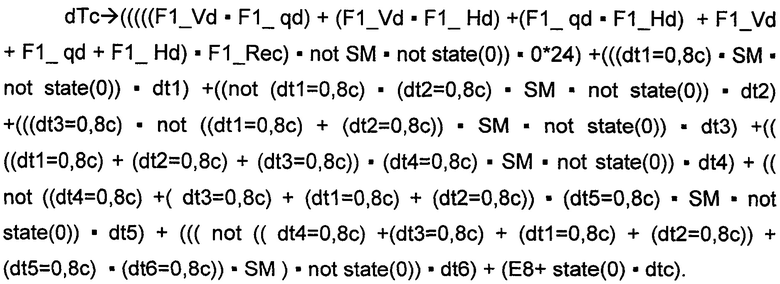

Функциональная схема узла счетчиков 215 представлена на фиг. 11.

Узел счетчиков 215 состоит из шести счетчиков dt (сумматоры 242-247, мультиплексоры 249-254, регистры 255-260), счетчика DTC (регистр 261, сумматор 248), первой комбинационной схемы 240, второй комбинационной схемы 241, элемента И 263 и триггера 262.

Счетчики dt определяют временной период достоверных информационных параметров. Алгоритм работы счетчиков dT представлен на фиг. 24, 25.

Счетчик DTC, элемент И 263 и триггер 262 определяют интервал времени от момента получения достоверных информационных параметров, выбранных в соответствии с приоритетом, до приема интегрального признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)». Если в предшествующем временном интервале 0,8 с нет информационных сообщений, то осуществляется блокировка выдачи команд 3.1 и/или 3.2.

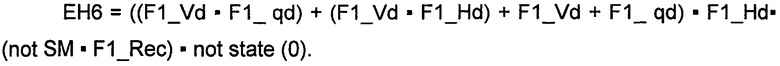

Первая комбинационная схема 240 обеспечивает формирование управляющих сигналов для счетчиков dt. Первая комбинационная схема 240 имеет следующую формулу:

Вторая комбинационная схема 241 обеспечивает формирование разрешающего сигнала для приема данных Edtc и данные Ddtc в регистр DTC 261, который совместно с элементом И и триггером 262 определяют время, когда нужно перейти к расчету Т1.

Вторая комбинационная схема 241 имеет следующую формулу:

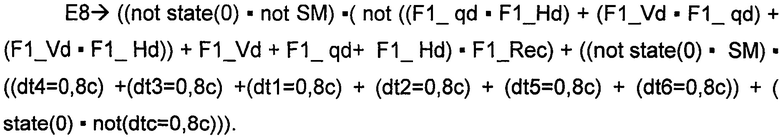

Функциональная схема узлов ZBV (затвор баровременной) 26, 27 представлена на фиг. 12.

Узел ZBV (затвор баровременной) 26, (27) автономного режима работы при наличии признака «СТРЕЛЯЮЩИЙ МЕХАНИЗМ (СМ)» осуществляет упрощенный расчет времени выброса основного парашюта по автономному алгоритму и выдает команды 1.1, 1.2, 2.1 и 2.2.

Узел ZBV (затвор баровременной) 26, (27) содержит первый счетчик 264, второй счетчик 265, третий счетчик 266, первый триггер 267, второй триггер 268, третий триггер 269, четвертый триггер 270, пятый триггер 271, шестой триггер 272, седьмой триггер 273, восьмой триггер 274, девятый триггер 275, десятый триггер 276, первый формирователь задержки FZ1 277, второй формирователь задержки FZ1 278, первый формирователь задержки FZ2 279, второй формирователь задержки FZ2 280, третий формирователь задержки FZ2 281, четвертый формирователь задержки FZ2 282, формирователь задержки FZ3 283, первый элемент ИЛИ 284, второй элемент ИЛИ 285, третий элемент ИЛИ 286, четвертый элемент ИЛИ 287, пятый элемент ИЛИ 288, шестой элемент ИЛИ 289, седьмой элемент ИЛИ 290, первый элемент И 291, второй элемент И 292, третий элемент И 293, четвертый элемент И 294, пятый элемент И295, шестой элемент И 296.

Признак «АВАРИЯ» формируется как логическое ИЛИ сигналов «авария А» и «авария В». По данному сигналу на ЭУКК самолета подается питание для узлов ZBV автономного режима работы.

Значения защелок «шасси выпущено А» и «шасси выпущено В» поступают в узлы ZBV 26 и 27 соответственно. Значения защелок «шасси выпущено А» и «шасси выпущено В» узлов ZBV автономного режима работы запоминаются при их включении на основе значений аналоговых сигналов «шасси выпущено А» и «шасси выпущено В» соответственно.

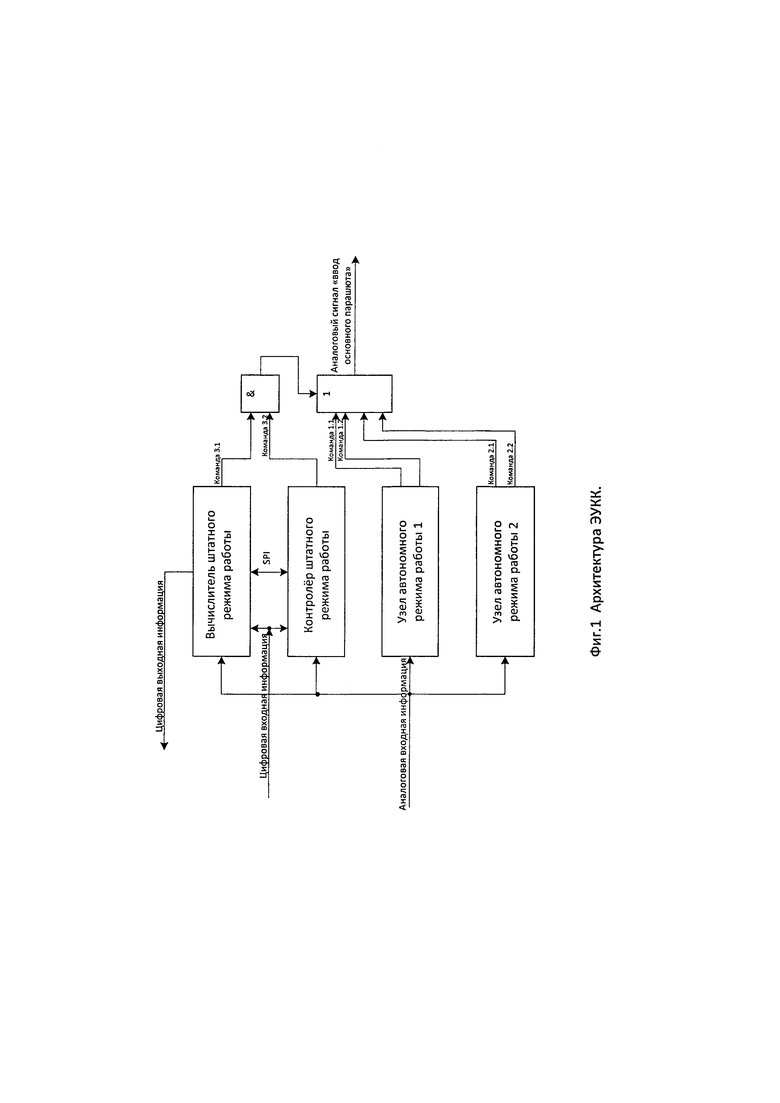

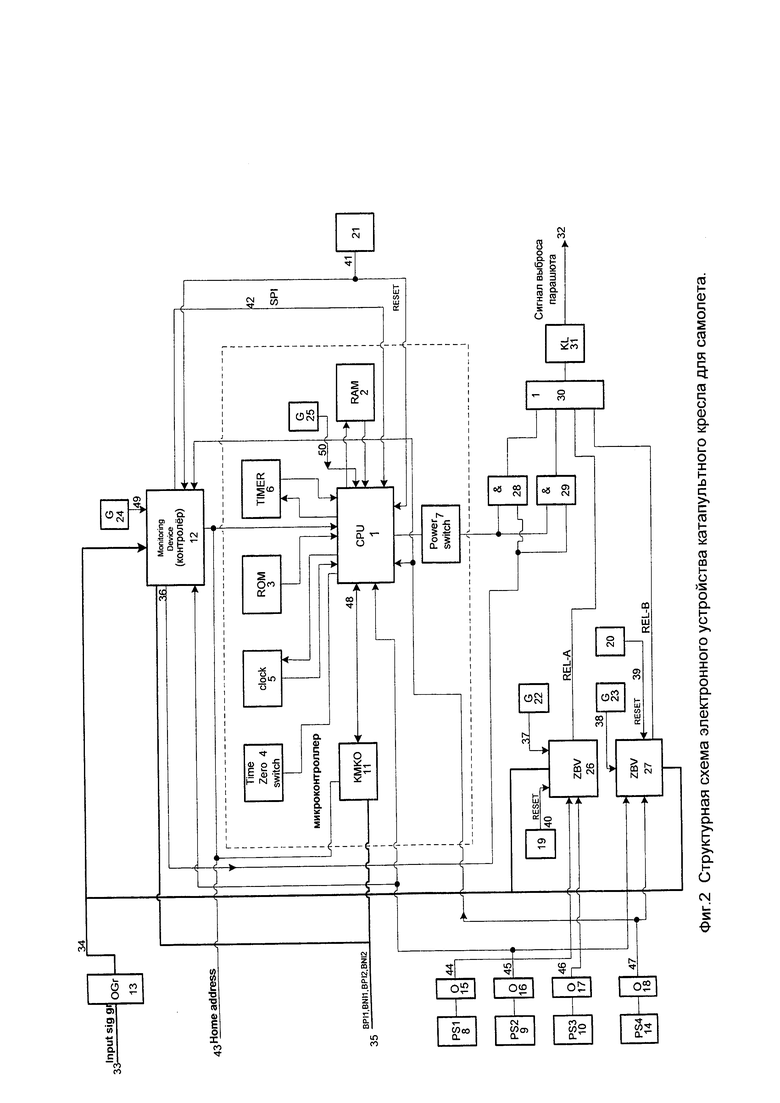

Сигналы длительностью не менее 4 мс «датчик хода 2 (ДХ2) А» и «датчик хода 2 (ДХ2) В», поступающие в узлы ZBV 26 и 27 соответственно, служат началом отчета: времени Т26 выброса основного парашюта в зависимости состояний BR2 и BR6 (от 2 до 6 км) до выдачи команд 1.1 и 2.1; времени Т22 выброса основного парашюта в зависимости от состояний барореле BR2 и BR6 (до 2 км) до выдачи команд 1.2 и 2.2.

Значения защелок «малая масса А» и «малая масса В» узлов ZBV 26, 27 автономного режима работы запоминаются при их включении на основе значений аналоговых сигналов «малая масса А» и «малая масса Б» соответственно.

Значения защелок «большая масса А» и «большая масса В» узлов ZBV 26, 27 автономного режима работы запоминаются при их включении на основе значений аналоговых сигналов «большая масса А» и «большая масса Б» соответственно.