Изобретение относится к радиотехнике и может использоваться в радиолокационных станциях в режимах сопровождения целей для обработки полифазных (р-ичных, р≥1) импульсных фазокодоманипулированных (ФКМ) сигналов с неизвестной частотой Доплера, кодированных ансамблями ортогональных кодов по предварительному целеуказанию в ограниченном доплеровском диапазоне частот.

Известно устройство сжатия полифазных импульсных сигналов, содержащее два одинаковых квадратурных регистра сдвига с числом ячеек, равным числу элементарных дискрет импульсного ФКМ сигнала, причем первым и вторым входами устройства сжатия являются входы квадратурных регистров сдвига, на которые подаются соответственно реальная и мнимая части комплексной огибающей полифазного сигнала с выходов АЦП, соответствующие ячейки квадратурных регистров сдвига каждая соединены с первыми входами двух умножителей, каждый из которых имеет два входа и один выход, на второй вход первого из умножителей подается реальная часть импульсной характеристики ячейки, а на второй вход второго умножителя - мнимая часть импульсной характеристики ячейки, выходы первого и второго умножителя соответственно косинусного и синусного квадратурных каналов, а так же первого и второго умножителя соответственно синусного и косинусного квадратурных каналов соединены попарно с двумя сумматорами, каждый из которых имеет два входа и один выход, выход каждого из этих сумматоров для каждой ячейки квадратурных регистров сдвига соединен с одним из входов одного из двух сумматоров, каждый из которых имеет количество входов по числу элементарных дискрет в полифазном импульсном сигнале и один выход, являющийся одновременно одним из двух выходов устройства сжатия, с одного из выходов устройства сжатия реальная, а со второго - мнимая части комплексной огибающей деманипулированного сигнала подаются на процессор БПФ для определения доплеровского сдвига несущей частоты сигнала [1].

Однако известное устройство обработки полифазных импульсных ФКМ сигналов с числом элементарных дискрет, равным М, имеет большие вычислительные затраты для сжатия (деманипуляции) сигнала: M2 комплексных умножений (4М2 вещественных умножений) и (М2-М) комплексных сложений ((4М2-2М) вещественных сложений), а также после деманипуляции для определения частоты Доплера во всем возможном доплеровском диапазоне частот используется многоточечный процессор БПФ, что затрудняет обработку полифазных импульсных сигналов с большой базой в реальном масштабе времени.

Целью изобретения является уменьшение вычислительных затрат на деманипуляцию полифазных импульсных сигналов и определение частоты Доплера путем использования процессора быстрого преобразования Виленкина-Крестенсона-Фурье (БПВК-Ф), использующего совмещенный алгоритм БПФ в базисах Виленкина-Крестенсона и дискретных экспоненциальных функций (ДЭФ) [2], позволяющий одновременно снимать манипуляцию полифазных импульсных сигналов, кодированных ансамблями ортогональных функций Виленкина-Крестенсона, и определять частоту Доплера в ограниченном доплеровском диапазоне частот по предварительному целеуказанию.

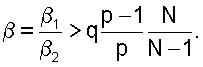

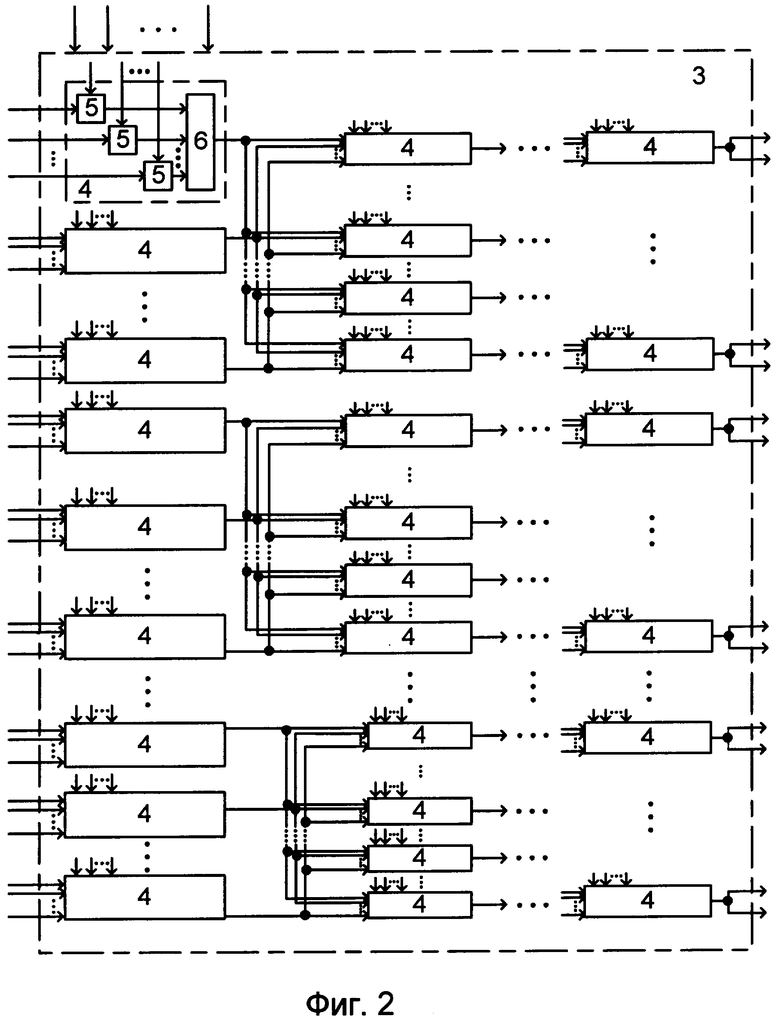

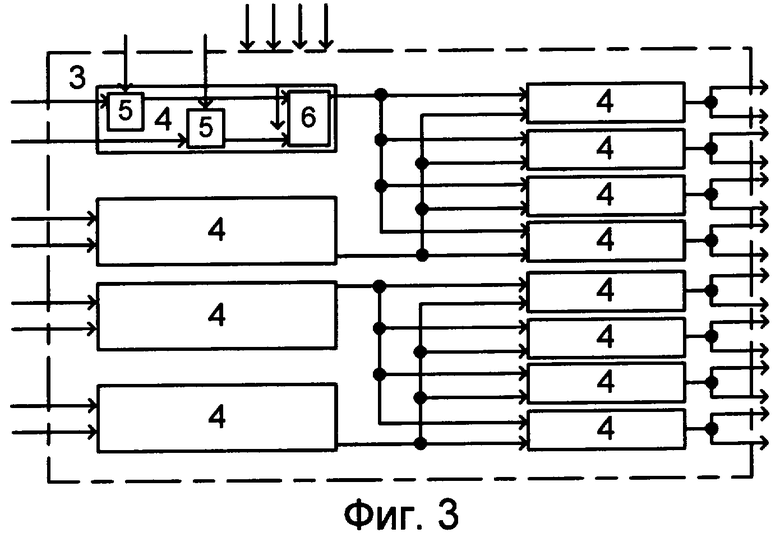

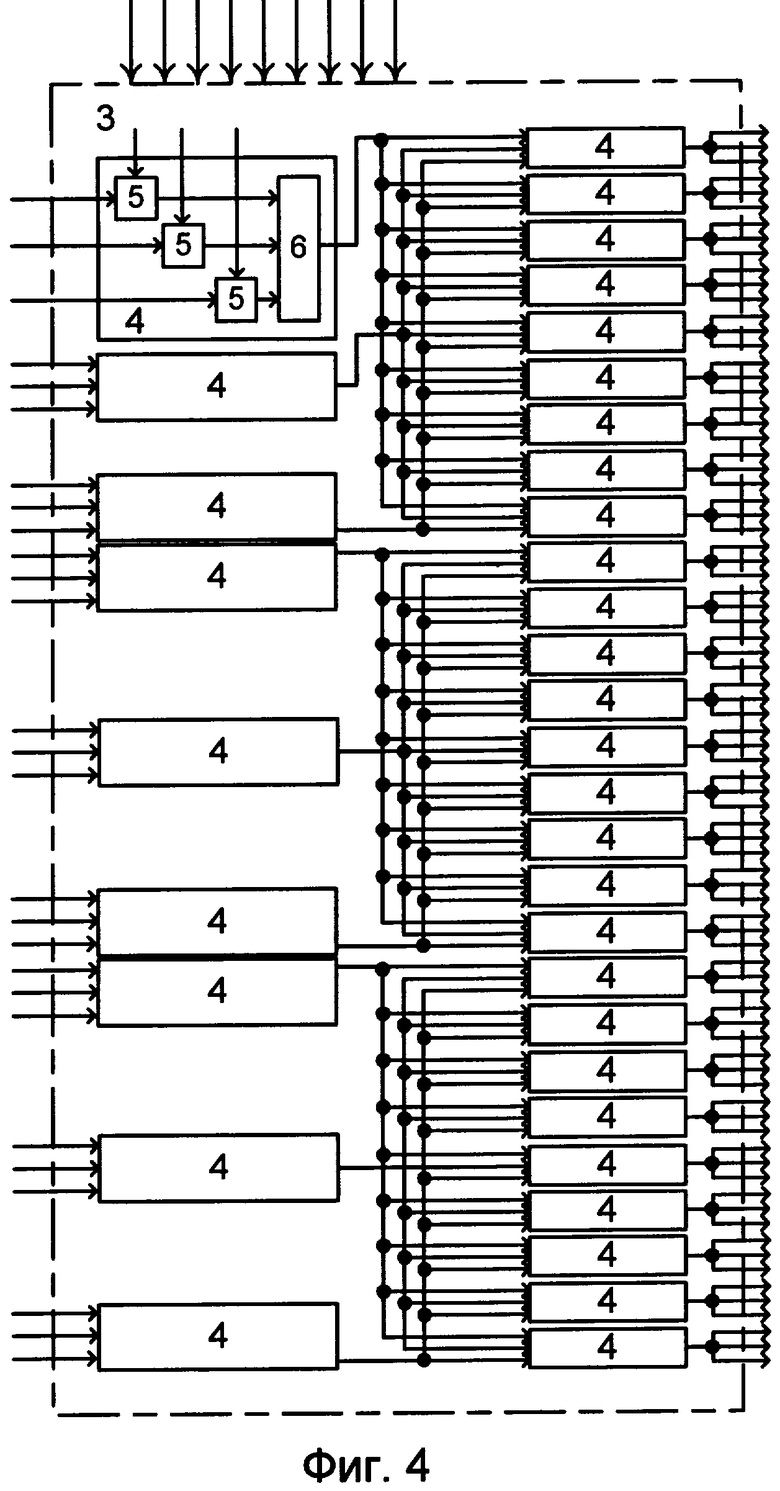

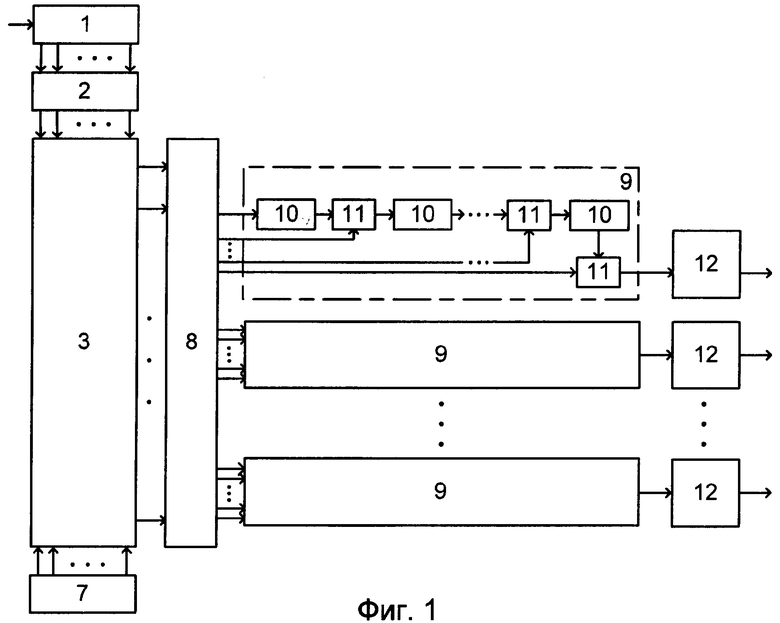

На фиг.1 приведена структурная схема предлагаемого устройства обработки полифазных ортогональных сигналов, на фиг.2 - структурная схема блока 3 процессора БПВК-Ф, на фиг.3 - пример процессора БПВК-Ф устройства обработки полифазного ортогонального сигнала при N=4 и р=2, на фиг.4 - пример процессора БПВК-Ф при N=9 и р=3.

Устройство содержит (фиг.1): регистр 1 сдвига с числом ячеек, равным количеству элементарных дискрет в импульсе, первый блок 2 перекрестных связей, процессор 3 БПВК-Ф, содержащий N(N-1)/(p-1) (N - число элементарных дискрет в одном импульсе, р - число фаз сигнала) блоков 4 перемножения с весовыми коэффициентами (фиг.2), каждый из которых состоит из р умножителей 5 комплексных чисел и одного сумматора 6 комплексных чисел на р входов, блок 7 весовых коэффициентов, второй блок 8 перекрестных связей, N блоков 9 формирования автокорреляционной функции (АКФ) полифазного импульсного сигнала, каждый из которых содержит (N-1) одинаковых регистров 10 сдвига с числом ячеек, равным периоду следования импульсов (qN, где q - скважность импульсного сигнала) и (N-1) одинаковых сумматоров 11 комплексных чисел, N пороговых устройств 12.

Регистр 1 сдвига имеет один вход и N выходов, причем вход регистра является входом устройства, выходы соединены с соответствующими входами первого блока 2 перекрестных связей.

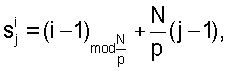

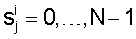

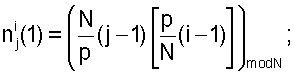

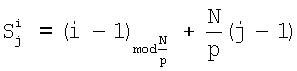

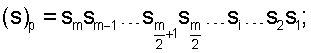

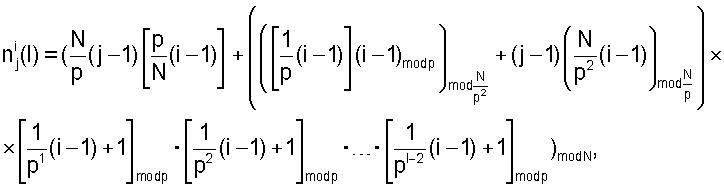

Первый блок 2 перекрестных связей имеет N входов и pN выходов, выходы соединены с соответствующими сигнальными входами процессора 3 БПВК-Ф, который на сигнальном входе имеет N блоков 4 перемножения с весовыми коэффициентами по р входов, с которыми непосредственно соединены выходы блока перекрестных связей, сами перекрестные связи построены согласно выражению

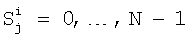

где (a)modb - обозначение числа а по модулю b;

i=1,2,...,N - номер блока перемножения с весовыми коэффициентами в первой итерации процессора БПВК-Ф;

j=1,2,...,p - номер входа i-го блока перемножения с весовыми коэффициентами;

- номер выхода регистра 1 сдвига «минус один», который подключен к j-му входу i-го блока перемножения с весовыми коэффициентами процессора БПВК-Ф.

- номер выхода регистра 1 сдвига «минус один», который подключен к j-му входу i-го блока перемножения с весовыми коэффициентами процессора БПВК-Ф.

Процессор 3 БПВК-Ф имеет pN сигнальных входов по р входов на каждый из N блоков 4 перемножения с весовыми коэффициентами в первой итерации, N входов для весовых коэффициентов и N2 выходов по одному выходу, разветвленному на р выходов с каждого из  блоков перемножения с весовыми коэффициентами в последней итерации, в каждом из N блоков перемножения с весовыми коэффициентами, имеющего р сигнальных входов, р входов для весовых коэффициента и один выход, в первой итерации р сигнальных входов подаются на первые входы соответствующих умножителей 5 комплексных чисел, имеющих каждый по два входа и одному выходу, на вторые входы которых подаются соответствующие весовые коэффициенты, р выходов умножителей комплексных чисел в каждом из блоков перемножения с весовыми коэффициентами подаются на соответствующие входы сумматоров 6 комплексных чисел, имеющих р входов и один выход, выходы сумматоров комплексных чисел являются выходами блоков перемножения с весовыми коэффициентами, выходы с ((j-1)p+1)-го по jp-й

блоков перемножения с весовыми коэффициентами в последней итерации, в каждом из N блоков перемножения с весовыми коэффициентами, имеющего р сигнальных входов, р входов для весовых коэффициента и один выход, в первой итерации р сигнальных входов подаются на первые входы соответствующих умножителей 5 комплексных чисел, имеющих каждый по два входа и одному выходу, на вторые входы которых подаются соответствующие весовые коэффициенты, р выходов умножителей комплексных чисел в каждом из блоков перемножения с весовыми коэффициентами подаются на соответствующие входы сумматоров 6 комплексных чисел, имеющих р входов и один выход, выходы сумматоров комплексных чисел являются выходами блоков перемножения с весовыми коэффициентами, выходы с ((j-1)p+1)-го по jp-й  k-х (k=1,2,...,pl)

k-х (k=1,2,...,pl) - блоков перемножения с весовыми коэффициентами l-ой итерации соединяются с соответствующими «минус один по модулю р плюс один» входами р

- блоков перемножения с весовыми коэффициентами l-ой итерации соединяются с соответствующими «минус один по модулю р плюс один» входами р  (i=0,1,...,p-1) k-х N блоков перемножения с весовыми коэффициентами (l+1)-й итерации, всего процессор БПВК-Ф имеет logp N итераций, количество блоков перемножения с весовыми коэффициентами в l-й итерации равно Npl-1.

(i=0,1,...,p-1) k-х N блоков перемножения с весовыми коэффициентами (l+1)-й итерации, всего процессор БПВК-Ф имеет logp N итераций, количество блоков перемножения с весовыми коэффициентами в l-й итерации равно Npl-1.

Степени весовых коэффициентов  которые перемножаются с сигнальными отсчетами в каждом блоке 4 перемножения с весовыми коэффициентами, распределяются в процессоре БПВК-Ф согласно следующим выражениям.

которые перемножаются с сигнальными отсчетами в каждом блоке 4 перемножения с весовыми коэффициентами, распределяются в процессоре БПВК-Ф согласно следующим выражениям.

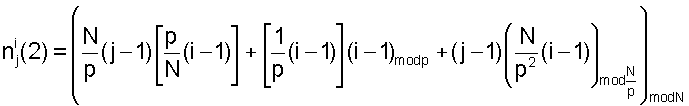

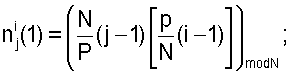

Для первой итерации

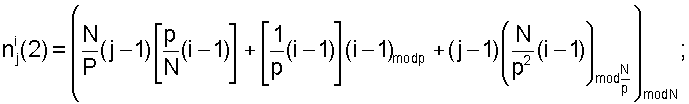

для второй итерации

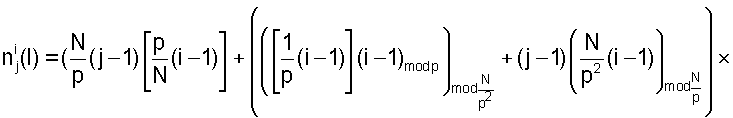

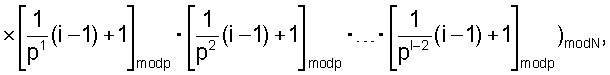

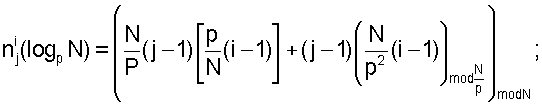

для последней итерации

для промежуточной l-й итерации

где

- обозначение операции выделения целой части числа

- обозначение операции выделения целой части числа

i=1,2,...,N·рl-1 - номер блока перемножения с весовыми коэффициентами в l-й итерации процессора БПВК-Ф;

j=1,2,...,р - номер входа i-го блока перемножения с весовыми коэффициентами.

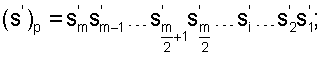

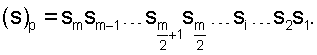

Алгоритм работы процессора БПВК-Ф основан на совмещении алгоритмов БПФ в базисах Виленкина-Крестенсона и ДЭФ путем перемножения матрицы импульсных характеристик размером N×N импульсов сигнала, кодированного ансамблем функций Виленкина-Крестенсона, на каждую строку матрицы ДЭФ размером N×N. При этом получается матрица размером N2×N, представляющая собой набор матриц импульсных характеристик размером N×N на N различных частотах, т.е. строки матрицы ДЭФ играют роль частотных каналов.

Выходы процессора БПВК-Ф соединены с соответствующими входами второго блока 8 перекрестных связей.

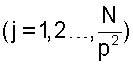

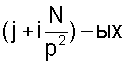

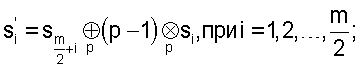

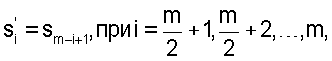

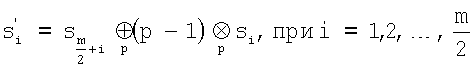

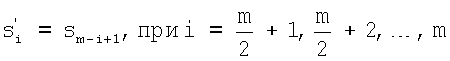

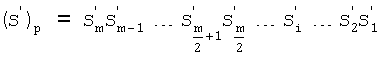

Второй блок 8 перекрестных связей имеет N2 входов и N2 выходов и предназначен для упорядочивания N2 выходных значений процессора БПВК-Ф согласно матрице импульсных характеристик на N различных частотах Доплера; первые N выходов второго блока перекрестных связей представляют собой результат перемножения матрицы импульсных характеристик на отсчеты входного сигнала процессора БПВК-Ф на нулевой частоте, вторые N выходов - на первой частоте, и т.д., последние N выходов - на (N-1)-й частоте. Перекрестные связи N2 выходов с N2 входами второго блока перекрестных связей определяются выражениями:

где

где

и

и  - операции соответственно сложения и умножения по модулю р;

- операции соответственно сложения и умножения по модулю р;

- i-ый разряд (s'+1)-го выхода второго блока перекрестных связей в p-ичном виде

- i-ый разряд (s'+1)-го выхода второго блока перекрестных связей в p-ичном виде

si - i-ый разряд (s+1)-го входа второго блока перекрестных связей в p-ичном виде

N2 выходов блока 8 перекрестных связей соединены с N2 входами N одинаковых блоков формирования АКФ полифазного импульсного сигнала, имеющих по N входов следующим образом: первые N выходов блока перекрестных связей соединены с соответствующими входами первого блока 9 формирования АКФ полифазного импульсного сигнала (нулевая частота), вторые N выходов блока перекрестных связей соединены с соответствующими входами второго блока 9 формирования АКФ полифазного импульсного сигнала (первая частота), и т.д., последние N выходов блока перекрестных связей соединены с соответствующими входами N-го блока 9 формирования АКФ полифазного импульсного сигнала ((N-1)-я частота).

Блок 9 формирования АКФ полифазного импульсного сигнала имеет N входов и один выход, первый вход i-го (i=1,2,...,N) блока формирования АКФ полифазного импульсного сигнала соединен с входом первого регистра сдвига 10, имеющего один вход и один выход, выход первого регистра сдвига соединен с первым входом первого сумматора 11 комплексных чисел, второй вход которого соединен со вторым входом блока формирования АКФ полифазного импульсного сигнала, выход первого сумматора комплексных чисел соединен с входом второго регистра сдвига 10, имеющего один вход и один выход, выход второго регистра сдвига соединен с первым входом второго сумматора 11 комплексных чисел, второй вход которого соединен с третьим входом блока формирования АКФ полифазного импульсного сигнала, выход второго сумматора комплексных чисел соединен с входом третьего регистра сдвига 10, и т.д., выход (N-1)-го регистра сдвига 10 соединен с первым входом (N-1)-го сумматора 11 комплексных чисел, второй вход которого соединен с N-м входом блока формирования АКФ полифазного импульсного сигнала, выход (N-1)-го сумматора комплексных чисел является выходом блока формирования АКФ полифазного импульсного сигнала.

Выход каждого из N блоков формирования АКФ полифазного импульсного сигнала соединен с входом одного из N пороговых устройств 12. Выходы N пороговых устройств являются выходами устройства.

По номеру порогового устройства (i=1,2,...,N), в котором превышен порог, определяется доплеровский сдвиг частоты.

Рассмотрим пример использования устройства обработки полифазных ортогональных сигналов с числом фаз сигнала р=2, числом элементарных дискрет в импульсе N=4 и скважностью q=2. В этом случае полифазные ортогональные ансамбли Виленкина-Крестенсона переходят в бифазные ортогональные ансамбли Уолша, и процессор БПВК-Ф становится процессором быстрого преобразования Уолша-Фурье (БПУ-Ф).

Регистр 1 сдвига имеет один вход, являющийся входом устройства, и 4 выхода, которые соединены с соответствующими входами первого блока 2 перекрестных связей.

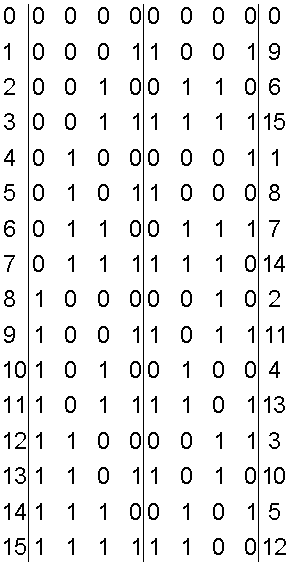

Первый блок 2 перекрестных связей имеет 4 входа и 8 выходов, которые соединены с соответствующими сигнальными входами процессора 3 БПУ-Ф. Перекрестные связи первого блока 2 перекрестных связей представлены в таблице (i - номер блока перемножения с весовыми коэффициентами первой итерации, j - номер входа i - го блока,  - номер ячейки регистра сдвига плюс один).

- номер ячейки регистра сдвига плюс один).

Процессор 3 БПУ-Ф (фиг.3) имеет 8 сигнальных входов по 2 входа на каждый из 4-х блоков 4 перемножения с весовыми коэффициентами в первой итерации, 4 входа для весовых коэффициентов и 16 выходов по одному выходу, разветвленному на 2 выхода с каждого из 8 блоков перемножения с весовыми коэффициентами в последней итерации.

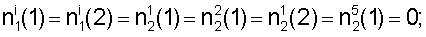

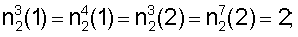

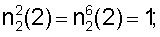

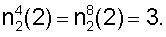

Всего процессор БПУ-Ф имеет log2 N=2 итерации. Выход первого блока перемножения первой итерации соединяется с первыми входами первых 4-х блоков перемножения второй итерации, выход второго блока перемножения первой итерации соединяется со вторыми входами первых 4-х блоков перемножения второй итерации, выход третьего блока перемножения первой итерации соединяется с первыми входами вторых 4-х блоков перемножения второй итерации, выход четвертого блока перемножения первой итерации соединяется со вторыми входами вторых 4-х блоков перемножения второй итерации. Весовые коэффициенты процессора БПУ-Ф имеют следующие показатели степеней:

Выходы процессора БПУ-Ф соединены с соответствующими входами второго блока 8 перекрестных связей.

Второй блок 8 перекрестных связей имеет 16 входов и 16 выходов. Перекрестные связи имеют следующий вид

где левый столбец - это номера входов второго блока перекрестных связей плюс один, а правый столбец - номера выходов второго блока перекрестных связей плюс один, представленных в двоичном виде.

Блок 9 формирования АКФ полифазного импульсного сигнала имеет 4 входа и один выход, первый вход i-го (i=1,2,3,4) блока формирования АКФ полифазного импульсного сигнала соединен с входом первого регистра сдвига 10, имеющего один вход и один выход, выход первого регистра сдвига соединен с первым входом первого сумматора 11 комплексных чисел, второй вход которого соединен со вторым входом блока формирования АКФ полифазного импульсного сигнала, выход первого сумматора комплексных чисел соединен с входом второго регистра сдвига 10, имеющего один вход и один выход, выход второго регистра сдвига соединен с первым входом второго сумматора 11 комплексных чисел, второй вход которого соединен с третьим входом блока формирования АКФ полифазного импульсного сигнала, выход второго сумматора комплексных чисел соединен с входом третьего регистра сдвига 10, выход третьего регистра сдвига соединен с первым входом третьего сумматора 11 комплексных чисел, второй вход которого соединен с четвертым входом блока формирования АКФ. Выход каждого из 4-х блоков формирования АКФ полифазного импульсного сигнала соединен с входом одного из 4 пороговых устройств 12. Выходы 4-х пороговых устройств являются выходами устройства.

На фиг.4 изображен процессор БПВК-Ф устройства обработки полифазного ортогонального сигнала, кодированного ансамблем ортогональных функций Виленкина-Крестенсона с параметрами р=3, N=9. Данный процессор имеет 27 сигнальных входов, 9 входов весовых коэффициентов и 81 выход, содержит две итерации. В первой итерации содержится 9 блоков 4 перемножения с весовыми коэффициентами, во второй итерации - 27 блоков перемножения с весовыми коэффициентами.

Выход первого блока перемножения 4 с весовыми коэффициентами первой итерации соединяется с первыми входами первых 9 блоков перемножения второй итерации, выход второго блока перемножения первой итерации соединяется со вторыми входами первых 9 блоков перемножения второй итерации, выход третьего блока перемножения первой итерации соединяется с третьими входами первых 9 блоков перемножения второй итерации, выход четвертого блока перемножения первой итерации соединяется с первыми входами вторых 9 блоков перемножения второй итерации, выход пятого блока перемножения первой итерации соединяется со вторыми входами вторых 9 блоков перемножения второй итерации, выход шестого блока перемножения первой итерации соединяется с третьими входами вторых 9 блоков перемножения второй итерации, выходы седьмого, восьмого и девятого блоков перемножения соединяются соответственно с первым, вторым и третьим входами последних 9 блоков перемножения второй итерации.

Выше было определено, что прототип для сжатия сигнала использует М2 комплексных умножений и М2-М комплексных сложений, где М - количество элементарных дискрет в сигнале. Полифазный ортогональный сигнал имеет число элементарных дискрет М=qNN=qN2, где N - число элементарных дискрет в импульсе. Таким образом, прототип для деманипуляции полифазного ортогонального сигнала использует q2N4 операций комплексных умножений и q(qN4-N2) операций комплексных сложений. Далее в прототипе деманипулированный сигнал подается на процессор БПФ для определения частоты Доплера. Т.о. прототип использует β1>q2N4 операций комплексных умножений и α1>q(qN4-N2) операций комплексных сложений.

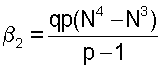

Предлагаемое устройство для деманипуляции полифазного ортогонального сигнала и одновременного определения частоты Доплера использует  операций комплексных умножений и α2=2q(N4-N3) операций комплексных сложений. Выигрыш в количестве операций комплексных умножений как наиболее трудоемких предлагаемого устройства относительно прототипа определяется:

операций комплексных умножений и α2=2q(N4-N3) операций комплексных сложений. Выигрыш в количестве операций комплексных умножений как наиболее трудоемких предлагаемого устройства относительно прототипа определяется:

Из выражения видно, что с увеличением базы полифазного пачечного сигнала выигрыш в количестве операций комплексных умножений предлагаемого устройства относительно прототипа увеличивается.

Литература

1. Применение полифазной модуляции для повышения скрытности работы РЛС. - Радиоэлектроника за рубежом, 1990, №8.

2. A.M.Трахтман, В.А.Трахтман. Основы теории дискретных сигналов на конечных интервалах. - М.: Сов. радио, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой обработки полифазных дополнительных фазокодоманипулированных сигналов | 2017 |

|

RU2647632C1 |

| УСТРОЙСТВО РАЗРЕШЕНИЯ ФАЗОКОДОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2371865C2 |

| Способ формирования множества ансамблей p-ичных D-кодов | 2017 |

|

RU2670773C9 |

| РЕЦИРКУЛЯЦИОННЫЙ КОРРЕЛЯТОР РАЗРЕШЕНИЯ ФАЗОКОДОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2005 |

|

RU2283541C1 |

| ГЕНЕРАТОР СИНГУЛЯРНЫХ АНСАМБЛЕЙ ОПТИМАЛЬНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 2010 |

|

RU2447479C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| СПОСОБ И УСТРОЙСТВО ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ СИГНАЛА | 2005 |

|

RU2303786C2 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для вычисления коэффициентов фурье | 1977 |

|

SU736112A1 |

Изобретение относится к радиотехнике и может использоваться в радиолокационных станциях в режимах сопровождения целей для обработки полифазных импульсных фазокодоманипулированных сигналов с неизвестной частотой Доплера, кодированных ансамблями ортогональных кодов. Достигаемый технический результат - уменьшение вычислительных затрат на деманипуляцию полифазных импульсных сигналов и определение частоты Доплера путем использования процессора быстрого преобразования Виленкина-Крестенсона-Фурье (БПВК-Ф), использующего совмещенный алгоритм БПФ в базисах Виленкина-Крестенсона и дискретных экспоненциальных функций (ДЭФ), что позволяет одновременно снимать манипуляцию полифазных импульсных сигналов, кодированных ансамблями ортогональных функций Виленкина-Крестенсона, и определять частоту Доплера в ограниченном доплеровском диапазоне частот по предварительному целеуказанию. Алгоритм работы процессора БПВК-Ф определяется перемножением матрицы импульсных характеристик размером N×N импульсов сигнала, кодированного ансамблем функций Виленкина-Крестенсона, на каждую строку матрицы ДЭФ размером N×N. Полученная при этом матрица размером N2×N представляет собой набор матриц импульсных характеристик размером N×N на N различных частотах, определяемых матрицей ДЭФ. 1 з.п. ф-лы, 4 ил.

,

,

где (α)modb - обозначение числа α по модулю b;

i=1,2,...,N - номер блока перемножения с весовыми коэффициентами в первой итерации процессора БПВК-Ф;

j=1,2,...,p - номер входа i-го блока перемножения с весовыми коэффициентами;

- номер выхода регистра сдвига «минус один»,

- номер выхода регистра сдвига «минус один»,

выходы первого блока перекрестных связей соединены с соответствующими сигнальными входами процессора БПВК-Ф, имеющего pN сигнальных входов, N входов весовых коэффициентов, соединенных с соответствующими выходами блока весовых коэффициентов, и N2 выходов, которые соединены с соответствующими входами второго блока перекрестных связей, имеющего N2 входов и N2 выходов и предназначенного для упорядочивания N2 выходных значений процессора БПВК-Ф согласно матрице импульсных характеристик на N различных частотах Доплера, порядок соединения (s+1)-го выхода процессора БПВК-Ф с (s'+1)-м выходом второго блока перекрестных связей определяется выражениями

;

;

,

,

где  и

и  - операции соответственно сложения и умножения по модулю p;

- операции соответственно сложения и умножения по модулю p;

- i-й разряд (s'+1)-го выхода второго блока перекрестных связей в p-ичном виде

- i-й разряд (s'+1)-го выхода второго блока перекрестных связей в p-ичном виде  ;

;

si - i-й разряд (s+1)-го выхода второго блока перекрестных связей в p-ичном виде

выходы второго блока перекрестных связей соединены с N2 входами N одинаковых блоков формирования АКФ полифазного импульсного сигнала, каждый из которых при N=4 имеет четыре входа и один выход, первый вход каждого из блоков формирования АКФ полифазного импульсного сигнала соединен с входом первого регистра сдвига, выход первого регистра сдвига соединен с первым входом первого сумматора комплексных чисел, второй вход которого соединен со вторым входом блока формирования АКФ полифазного импульсного сигнала, выход первого сумматора комплексных чисел соединен с входом второго регистра сдвига, выход второго регистра сдвига соединен с первым входом второго сумматора комплексных чисел, второй вход которого соединен с третьим входом блока формирования АКФ полифазного импульсного сигнала, выход второго сумматора комплексных чисел соединен с входом третьего регистра сдвига, выход третьего регистра сдвига соединен с первым входом третьего сумматора комплексных чисел, второй вход которого соединен с четвертым входом блока формирования АКФ полифазного импульсного сигнала, выход третьего сумматора является выходом блока формирования АКФ полифазного импульсного сигнала, выход каждого из N блоков формирования АКФ полифазного импульсного сигнала соединен с одним из входов одного из N пороговых устройств, имеющих по два входа и одному выходу, на вторые входы которых для сравнения подаются пороговые уровни, выходы N пороговых устройств являются выходами устройства.

блоков перемножения с весовыми коэффициентами в последней итерации, в каждом из N блоков перемножения с весовыми коэффициентами, имеющем р сигнальных входов, р входов для весовых коэффициентов и один выход, в первой итерации р сигнальных входов подаются на первые входы соответствующих умножителей комплексных чисел, имеющих каждый по два входа и одному выходу, на вторые входы которых подаются соответствующие весовые коэффициенты, р выходов умножителей комплексных чисел в каждом из блоков перемножения с весовыми коэффициентами подаются на соответствующие входы сумматоров комплексных чисел, имеющих р входов и один выход, выходы сумматоров комплексных чисел являются выходами блоков перемножения с весовыми коэффициентами, при N=4 выход первого блока перемножения с весовыми коэффициентами первой итерации соединяется с первыми входами первых 4-х блоков перемножения с весовыми коэффициентами второй итерации, выход второго блока перемножения первой итерации соединяется со вторыми входами первых 4-х блоков перемножения второй итерации, выход третьего блока перемножения первой итерации соединяется с первыми входами вторых 4-х блоков перемножения второй итерации, выход четвертого блока перемножения первой итерации соединяется со вторыми входами вторых 4-х блоков перемножения второй итерации, всего процессор БПВК-Ф имеет logpN итераций, количество блоков перемножения с весовыми коэффициентами в l-й итерации равно Npl-1, при этом степени весовых коэффициентов

блоков перемножения с весовыми коэффициентами в последней итерации, в каждом из N блоков перемножения с весовыми коэффициентами, имеющем р сигнальных входов, р входов для весовых коэффициентов и один выход, в первой итерации р сигнальных входов подаются на первые входы соответствующих умножителей комплексных чисел, имеющих каждый по два входа и одному выходу, на вторые входы которых подаются соответствующие весовые коэффициенты, р выходов умножителей комплексных чисел в каждом из блоков перемножения с весовыми коэффициентами подаются на соответствующие входы сумматоров комплексных чисел, имеющих р входов и один выход, выходы сумматоров комплексных чисел являются выходами блоков перемножения с весовыми коэффициентами, при N=4 выход первого блока перемножения с весовыми коэффициентами первой итерации соединяется с первыми входами первых 4-х блоков перемножения с весовыми коэффициентами второй итерации, выход второго блока перемножения первой итерации соединяется со вторыми входами первых 4-х блоков перемножения второй итерации, выход третьего блока перемножения первой итерации соединяется с первыми входами вторых 4-х блоков перемножения второй итерации, выход четвертого блока перемножения первой итерации соединяется со вторыми входами вторых 4-х блоков перемножения второй итерации, всего процессор БПВК-Ф имеет logpN итераций, количество блоков перемножения с весовыми коэффициентами в l-й итерации равно Npl-1, при этом степени весовых коэффициентов  , которые перемножаются с сигнальными отсчетами в каждом блоке перемножения с весовыми коэффициентами, распределяются в процессоре БПВК-Ф согласно следующих выражений: для первой итерации

, которые перемножаются с сигнальными отсчетами в каждом блоке перемножения с весовыми коэффициентами, распределяются в процессоре БПВК-Ф согласно следующих выражений: для первой итерации

для второй итерации

для последней итерации

для промежуточной l-й итерации

,

,

где i=1,2,...,N·pl-1 - номер блока перемножения с весовыми коэффициентами в l-й итерации процессора БПВК-Ф;

j=1,2,...,p - номер входа i-го блока перемножения с весовыми коэффициентами.

| РЕЦИРКУЛЯЦИОННЫЙ КОРРЕЛЯТОР РАЗРЕШЕНИЯ ФАЗОКОДОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2005 |

|

RU2283541C1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1987 |

|

SU1509930A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| US 5394349 A, 28.02.1995. | |||

Авторы

Даты

2009-02-10—Публикация

2006-12-20—Подача