Изобретение относится к электронно-вычислительной технике, предназначено для синтеза частот и сигналов и может использоваться в радиолокации, навигации, адаптивных системах связи и телевидения.

Изобретение позволяет синтезировать двухчастотные сигналы.

Известны цифровые синтезаторы частот, содержащие эталонный генератор, блок задержки, два регистра памяти, два цифровых накопителя, делитель с переменным коэффициентом деления, два преобразователя кодов, два цифроаналоговых преобразователя, два фильтра нижних частот [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий последовательно соединенные эталонный генератор и блок задержки, последовательно соединенные первый блок постоянного запоминания, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот; второй блок постоянного запоминания и счетчик с предварительной установкой; входами цифрового синтезатора являются входы первого и второго блоков ПЗУ, а выходом - выход фильтра нижних частот [2].

Однако известные цифровые синтезаторы обладают сравнительно невысоким быстродействием при перестройке с частоты на частоту и не имеют возможности синтезировать на одном выходе двухчастотные сигналы.

Изобретение позволяет расширить функциональные возможности цифровых синтезаторов и повысить их быстродействие.

Положительный эффект - расширение функциональных возможностей цифровых синтезаторов частот и повышение их быстродействия - достигается за счет того, что в цифровой синтезатор частот с коммутацией фазовых отсчетов, содержащий последовательно соединенные эталонный генератор и блок задержки; последовательно соединенные первый регистр памяти, первый цифровой накопитель; второй цифровой накопитель; последовательно соединенные цифроаналоговый преобразователь, фильтр нижних частот, выход которого является выходом цифрового синтезатора частот, выходы блока задержки подключены к тактовым входам цифроаналогового преобразователя, первого и второго цифровых накопителей, причем новым является то, что введены последовательно соединенные второй регистр памяти, третий и четвертый цифровые накопители и мультиплексор, на второй вход которого подключен выход второго цифрового накопителя, а выход мультиплексора подключен к информационному входу цифроаналогового преобразователя; делитель частоты, выход которого подключен к управляющему входу мультиплексора; выходы блока задержки подсоединены к тактовым входам делителя частоты, третьего и четвертого цифровых накопителей; выход первого цифрового накопителя подключен к входу второго цифрового накопителя, а входами цифрового синтезатора частот являются входы первого и второго регистров памяти.

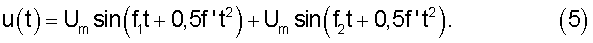

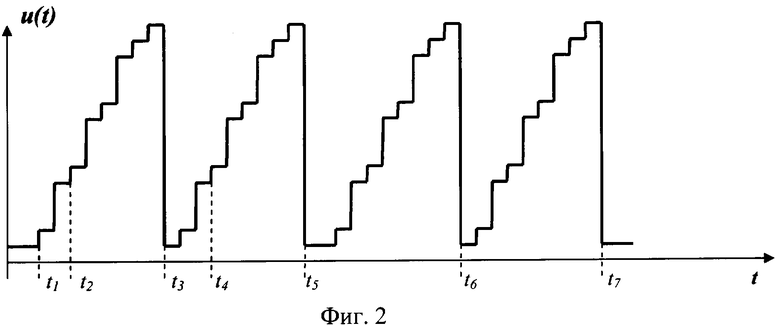

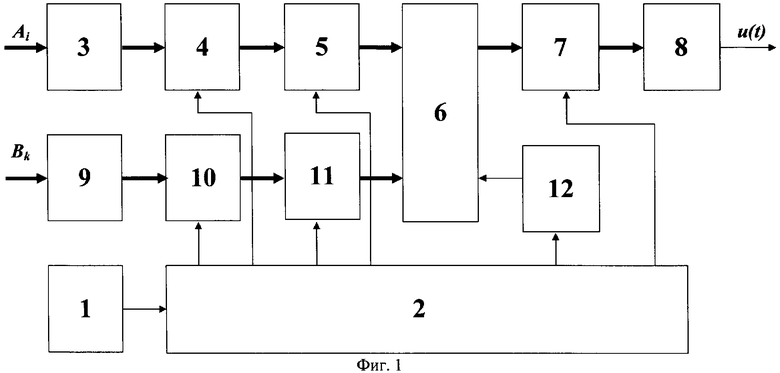

На фиг.1 приведена структурная схема цифрового синтезатора частот с коммутацией фазовых отсчетов, на фиг.2 - графики сигналов на выходе ЦАП цифрового синтезатора.

Цифровой синтезатор частот (фиг.1) содержит эталонный генератор 1, блок задержки 2, первый регистр памяти 3, первый и второй цифровые накопители 4 и 5, мультиплексор 6, цифроаналоговый преобразователь 7, фильтр нижних частот 8, второй регистр памяти 9, третий и четвертый цифровые накопители 10 и 11, делитель частоты 12.

Цифровой синтезатор частот работает следующим образом. На вход первого регистра памяти 3 поступает код первой начальной частоты Аi, а на вход второго регистра памяти 9 - код Вk, определяющий код второй начальной частоты. Эталонный генератор 1 выдает сигнал опорной частоты синусоидальной формы, который поступает на вход блока задержки 2, формирующий разнесенные во времени последовательности прямоугольных импульсов формы «меандр», которые поступают на тактовые входы первого, второго, третьего и четвертого цифровых накопителей 4 и 5, 10 и 11, а также тактовый вход цифроаналогового преобразователя 7, и служат для синхронизации работы цифрового синтезатора частот.

В момент t1 (фиг.2) код первой начальной частоты Аi из первого регистра памяти 3 записывается в первый цифровой накопитель 4, а код второй начальной частоты Bk из второго регистра памяти 9 записывается в третий цифровой накопитель 10.

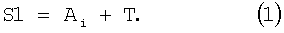

Затем с каждым тактовым импульсом код S1 на выходе первого цифрового накопителя 4 будет изменяться следующим образом:

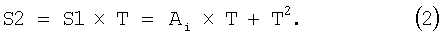

Код S1 поступает на вход второго цифрового накопителя 5, результат суммирования в котором будет изменяться по формуле:

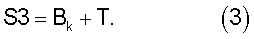

Код Bk из второго регистра памяти поступает на вход третьего цифрового накопителя 9, на выходе которого результат суммирования изменяется по формуле:

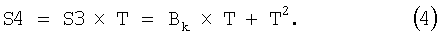

В четвертом цифровом накопителе результат суммирования изменяется по формуле

С выхода мультиплексора 6 отсчеты кодов суммы S2 и S4 поочередно поступают на информационные входы цифроаналогового преобразователя 7.

На выходе ЦАП 7 формируется ступенчатый сигнал «пилообразной» формы, который подается на фильтр нижних частот 8. ФНЧ 8 имеет частоту среза fcp<fm/2, где fm - тактовая частота, и пропускают на выход синтезатора только первую гармонику сформированного сигнала.

Если ввести обозначения, что f1=Аi - первая начальная частота; f2=Bk - вторая начальная частота; 0,5 f' - скорость изменения частоты синтезируемого сигнала, Δt=Т - период следования тактовых импульсов, то на выходе фильтра нижних частот 8 формируется двухчастотный сигнал, амплитуда которого изменяется по формуле:

Таким образом, в цифровом синтезаторе появилась возможность синтезировать двухчастотный сигнал.

Литература

1. Патент №2294054 Российской Федерации МПК H03L 7/18, Цифровой вычислительный синтезатор с квадратурными выходами / Рябов И.В. - Заявл. 25.10.2005. Опубл. 20.02.2007. Бюл. №5.

2. Патент №2058659 Российской Федерации МКИ Н03В 19/00, Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. - Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. №11. (Прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| Цифровой вычислительный синтезатор двухчастотных сигналов | 2019 |

|

RU2710280C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2580444C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ ДЛЯ МНОГОЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2014 |

|

RU2566961C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ДВУХУРОВНЕВЫХ СИГНАЛОВ | 2013 |

|

RU2540796C1 |

| Цифровой вычислительный синтезатор с частотной модуляцией | 2016 |

|

RU2628216C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

Изобретение относится к электронно-вычислительной технике, предназначено для синтеза частот и сигналов и может использоваться в радиолокации, навигации, адаптивных системах связи и телевидения. Достигаемый технический результат - расширение функциональных возможностей путем синтезирования двухчастотных сигналов. Устройство содержит эталонный генератор, блок задержки, первый регистр памяти, первый и второй цифровые накопители, мультиплексор, цифроаналоговый преобразователь, фильтр нижних частот, второй регистр памяти, третий и четвертый цифровые накопители, делитель частоты. 2 ил.

Цифровой синтезатор частот с коммутацией фазовых отсчетов, содержащий последовательно соединенные эталонный генератор и блок задержки; последовательно соединенные первый регистр памяти и первый цифровой накопитель; второй цифровой накопитель; последовательно соединенные цифроаналоговый преобразователь, фильтр нижних частот, выход которого является выходом цифрового синтезатора частот, выходы блока задержки подключены к тактовым входам цифроаналогового преобразователя, первого и второго цифровых накопителей, отличающийся тем, что введены последовательно соединенные второй регистр памяти, третий и четвертый цифровые накопители и мультиплексор, на второй вход которого подключен выход второго цифрового накопителя, а выход мультиплексора подключен к информационному входу цифроаналогового преобразователя; делитель частоты, выход которого подключен к управляющему входу мультиплексора; выходы блока задержки подсоединены к тактовым входам делителя частоты, третьего и четвертого цифровых накопителей; выход первого цифрового накопителя подключен к входу второго цифрового накопителя, а входами цифрового синтезатора частот являются входы первого и второго регистров памяти.

| RU 2058659 C1, 20.04.1996 | |||

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

Авторы

Даты

2009-02-10—Публикация

2007-06-18—Подача