Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза пачек прямоугольных импульсов и может быть использовано в системах радиолокации и навигации.

Известны цифровые синтезаторы частотно-модулированных сигналов, содержащие эталонный генератор, блок задержки, блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, ждущий мультивибратор, реверсивный счетчик и схему сравнения [1].

Наиболее близким техническим решением (прототипом) является цифровой синтезатор частот, содержащий генератор тактовых импульсов, блок задержки, первый и второй регистры памяти, счетчик с предварительной установкой, первый и второй блоки постоянного запоминания, ЦАП, ФНЧ, первый и второй цифровые накопители [2].

Положительный технический результат - возможность формирования пачек прямоугольных импульсов с заданными параметрами частоты следования импульсов, количеством импульсов в пачке и периодом повторения пачки импульсов - достигается тем, что в цифровой синтезатор двухуровневых сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый регистр памяти; цифровой накопитель; последовательно соединенные третий регистр памяти и делитель с переменным коэффициентом деления; входы первого и третьего регистров памяти являются цифровыми входами цифрового синтезатора двухуровневых сигналов; выходы блока формирования и задержки подключены к тактовым входам цифрового накопителя и делителя с переменным коэффициентом деления, введены второй и четвертый регистры памяти; счетчик; первый и второй мультиплексоры; выход первого регистра памяти подключен к входу цифрового накопителя, выход которого подключен к входу первого мультиплексора, выход последнего является цифровым выходом цифрового синтезатора двухуровневых сигналов; входы второго и четвертого регистров памяти являются вторым и четвертым цифровыми входами цифрового синтезатора двухуровневых сигналов; выход второго регистра памяти подключен к входу управления первого мультиплексора; выход делителя с переменным коэффициентом деления подсоединен к тактовому входу счетчика, выход которого подключен к входу второго мультиплексора, выход последнего подключен к входу сброса цифрового накопителя; выход четвертого регистра памяти подключен к входу управления второго мультиплексора; выход блока формирования и задержки подключен к тактовому входу счетчика.

Цифровой синтезатор двухуровневых сигналов содержит эталонный генератор 1 и блок формирования и задержки 2, первый регистр памяти 3, цифровой накопитель 4, первый мультиплексор 5, второй регистр памяти 6, третий регистр памяти 7, делитель с переменным коэффициентом деления 8, счетчик 9, второй мультиплексор 10, четвертый регистр памяти 11; входы первого, второго, третьего и четвертого регистров памяти являются соответственно первым, вторым, третьим и четвертым цифровыми входами цифрового синтезатора двухуровневых сигналов, а выход первого мультиплексора является его цифровым выходом (фиг.1).

Цифровой синтезатор работает следующим образом.

Эталонный генератор 1 вырабатывает синусоидальный сигнал опорной частоты, из которого в блоке формирования и задержки 2 формируются последовательности тактовых импульсов формы «меандр», разнесенные во времени и служащие для синхронизации работы основных узлов цифрового синтезатора двухуровневых сигналов: цифрового накопителя 4, делителя с переменным коэффициентом деления 8 и счетчика 9.

На вход первого регистра памяти 3 поступает код Ai, который будет определять частоту следования прямоугольных импульсов на выходе цифрового накопителя 4. Одновременно на вход второго регистра памяти подается код Bi, который через второй регистр памяти 6 поступает на вход управления первого мультиплексора 5, тогда в зависимости от значения кода Bi на выход первого мультиплексора 5 будет проходить сигнал соответствующего разряда цифрового накопителя 4.

Если Ai=1, Bi=0, то на выходе первого мультиплексора 5 будет присутствовать сигнал первого (младшего) разряда цифрового накопителя 4; он будет иметь прямоугольную форму «меандр» с периодом следования 2 тактовых интервала.

На вход третьего регистра памяти 7 поступает код Dk, который будет определять коэффициент деления делителя с переменным коэффициентом деления 8. Выход делителя с переменным коэффициентом деления 8 подключен к тактовому входу счетчика 9, выход которого подсоединен к входу второго мультиплексора 10.

На вход четвертого регистра памяти 11 поступает код Ck, который через данный регистр поступает на вход управления второго мультиплексора 10. Код Ck будет определять сигнал с какого разряда счетчика 9 пройдет на выход второго мультиплексора 10.

Если задать Dk=5, Ck=0, то на выходе второго мультиплексора 10 будет сформирован импульс «гашения» длительностью 10 тактовых интервалов опорной частоты (tгашен=10×Δt).

Таким образом, задавая коды Ck и Dk, можно сформировать импульсы «гашения» определенной длительности, которые с выхода второго мультиплексора 10 подаются на вход сброса (Reset) цифрового накопителя 4.

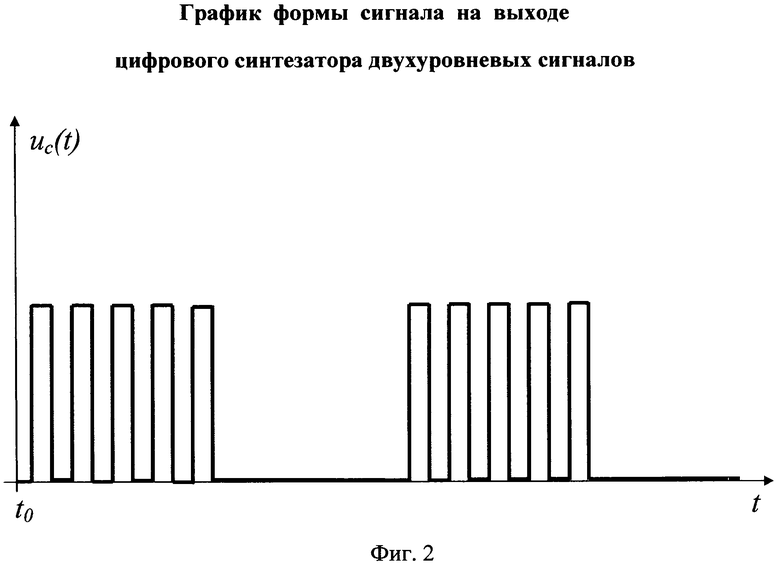

Таким образом, задавая соответствующие значения кодов Ai, Bi, Ck и Dk на входах первого, второго, третьего и четвертого регистров памяти, возможно сформировать сигнал на выходе первого мультиплексора 5, который является цифровым выходом цифрового синтезатора двухуровневых сигналов, в виде формы пачки прямоугольных импульсов с определенным периодом следования и требуемой длительностью импульсов «гашения». Для указанных выше значений кодов Ai=1, Bi=0, Dk=5, Ck=0 форма сигнала на выходе цифрового синтезатора двухуровневых сигналов представлена на фиг.2.

Литература

1. Патент РФ №2204197, МПК H03L 7/18. Цифровой синтезатор частотно-модулированных сигналов / Рябов И.В., Рябов В.И. Заявл. 06.04.2001. Опубл. 10.05.2003. Бюл. №13. - 5 с.

2. Патент РФ №2058659, МПК Н03В 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. №11. - 4 с. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2580444C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С БЫСТРОЙ ПЕРЕСТРОЙКОЙ ЧАСТОТЫ | 2012 |

|

RU2491710C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза пачек прямоугольных импульсов и может быть использовано в системах радиолокации и навигации. Достигаемый технический результат - возможность формирования пачек прямоугольных импульсов с заданными параметрами частоты следования импульсов, количеством импульсов в пачке и периодом повторения пачки импульсов. Цифровой синтезатор двухуровневых сигналов содержит эталонный генератор 1, блок формирования и задержки 2, первый регистр памяти 3, цифровой накопитель 4, первый мультиплексор 5, второй регистр памяти 6, третий регистр памяти 7, делитель с переменным коэффициентом деления 8, счетчик 9, второй мультиплексор 10, четвертый регистр памяти 11. Входы первого, второго, третьего и четвертого регистров памяти являются соответственно первым, вторым, третьим и четвертым цифровыми входами цифрового синтезатора двухуровневых сигналов, а выход первого мультиплексора является его цифровым выходом. 2 ил.

Цифровой синтезатор двухуровневых сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый регистр памяти; цифровой накопитель; последовательно соединенные третий регистр памяти и делитель с переменным коэффициентом деления; входы первого и третьего регистров памяти являются цифровыми входами цифрового синтезатора двухуровневых сигналов; выходы блока формирования и задержки подключены к тактовым входам цифрового накопителя и делителя с переменным коэффициентом деления, отличающийся тем, что введены второй и четвертый регистры памяти; счетчик; первый и второй мультиплексоры; выход первого регистра памяти подключен к входу цифрового накопителя, выход которого подключен к входу первого мультиплексора, выход последнего является цифровым выходом цифрового синтезатора двухуровневых сигналов; входы второго и четвертого регистров памяти являются вторым и четвертым цифровыми входами цифрового синтезатора двухуровневых сигналов; выход второго регистра памяти подключен к входу управления первого мультиплексора; выход делителя с переменным коэффициентом деления подсоединен к тактовому входу счетчика, выход которого подключен к входу второго мультиплексора, выход последнего подключен к входу сброса цифрового накопителя; выход четвертого регистра памяти подключен к входу управления второго мультиплексора; выход блока формирования и задержки подключен к тактовому входу счетчика.

| RU 2058659 C1, 20.04.1996, |

Авторы

Даты

2015-02-10—Публикация

2013-11-07—Подача