Ссылка на родственные заявки

В основу настоящей заявки включены патентная заявка номер (не присвоен), номер поверенного № 200209168-1; патентная заявка номер (не присвоен), номер поверенного № 200208780-1; патентная заявка номер (не присвоен), номер поверенного № 200311485-1, патентная заявка номер (не присвоен), номер поверенного № 200210152-1, патентная заявка номер (не присвоен), номер поверенного № 200209237-1.

Область техники

Настоящее изобретение относится к устройству для эжекции флюида.

Уровень техники

Система струйной печати как один вариант воплощения системы для эжекции флюида может включать в себя печатающую головку, средство подачи чернил, которое обеспечивает подачу жидких чернил для печатающей головки, и электронный контроллер, который управляет печатающей головкой. Печатающая головка как один вариант воплощения устройства для эжекции флюида осуществляет эжекцию капель чернил через множество отверстий или сопел. Чернила эжектируются к печатному носителю, такому как лист бумаги, для печати изображения на печатном носителе. Сопла обычно расположены в одном или более массивах таким образом, чтобы должным образом упорядоченная эжекция чернил из сопел приводила к печати символов или других изображений на печатном носителе по мере того, как печатающая головка и печатный носитель перемещаются друг относительно друга.

В обычной системе термической струйной печати печатающая головка эжектирует капли чернил через сопла посредством быстрого нагревания маленьких объемов чернил, расположенных в камерах испарения. Чернила нагреваются с помощью маленьких электрических нагревателей, таких как тонкопленочные резисторы, называемые здесь нагревательные резисторы. При нагревании чернила испаряются и эжектируются через сопла.

Чтобы эжектировать одну каплю чернил, электронный контроллер, который управляет печатающей головкой, активизирует электрический ток от внешнего источника электропитания. Электрический ток передается через выбранный нагревательный резистор для нагревания чернил в соответствующей выбранной камере испарения и эжекции чернил через соответствующее сопло. Известные генераторы капель включают в себя нагревательный резистор, соответствующую камеру испарения и соответствующее сопло.

По мере развития струйных печатающих головок количество генераторов капель в печатающей головке увеличилось для увеличения скорости и/или улучшения качества печати. Увеличение количества генераторов капель в печатающей головке привело к соответствующему увеличению количества входных контактных площадок, необходимых для размещения на матрице печатающей головки для активизации большего количества нагревательных резисторов. В одном типе печатающей головки каждый нагревательный резистор соединен с соответствующей входной контактной площадкой для подачи энергии для активации нагревательного резистора. Одна входная контактная площадка на нагревательный резистор становится непрактичной по мере увеличения количества нагревательных резисторов.

Количество генераторов капель на входную контактную площадку значительно увеличено в другом типе печатающей головки, имеющей примитивы. Один питающий провод обеспечивает подачу энергии на все нагревательные резисторы в одном примитиве. Каждый нагревательный резистор соединен последовательно с питающим проводом и через сток-исток соответствующего полевого транзистора. Затвор каждого полевого транзистора в примитиве соединен с отдельно питаемым адресным выводом, который совместно используется несколькими примитивами.

Изготовители продолжают уменьшать количество входных контактных площадок и увеличивать количество генераторов капель на матрице печатающей головки. Печатающая головка с меньшим количеством входных контактных площадок обычно стоит меньше, чем печатающая головка с большим количеством входных контактных площадок. Кроме того, печатающая головка с большим количеством генераторов капель обычно обеспечивает более высокое качество печати и/или большую скорость печати. Чтобы при тех же затратах обеспечивать конкретную высоту захвата печати, размер матрицы печатающей головки не может значительно изменяться с увеличенным количеством генераторов капель. По мере того как плотность генераторов капель увеличивается и количество входных контактных площадок уменьшается, компоновка матрицы печатающей головки может становиться все более и более сложной.

По этой и другим причинам имеется потребность в настоящем изобретении.

Краткое описание чертежей

В дальнейшем изобретение поясняется описанием предпочтительных вариантов воплощения со ссылками на сопровождающие чертежи, на которых:

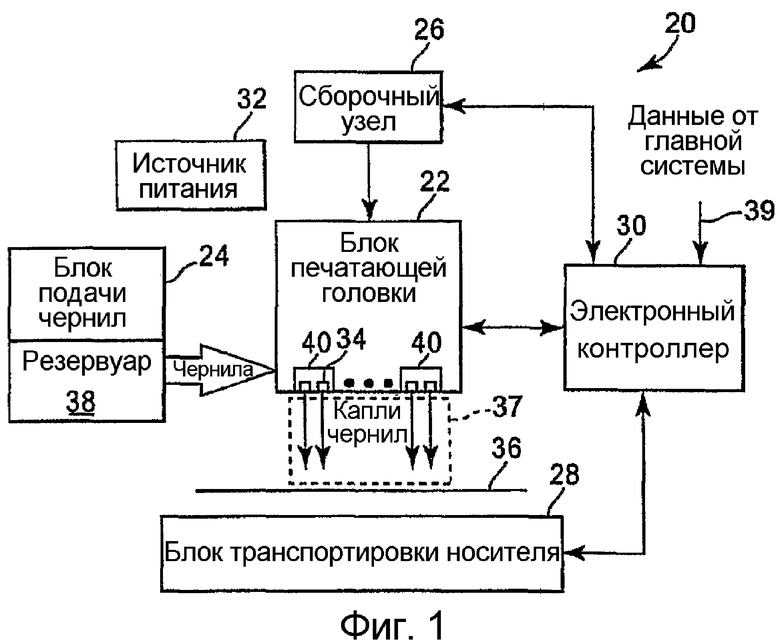

Фиг.1 изображает блок-схему системы струйной печати согласно изобретению;

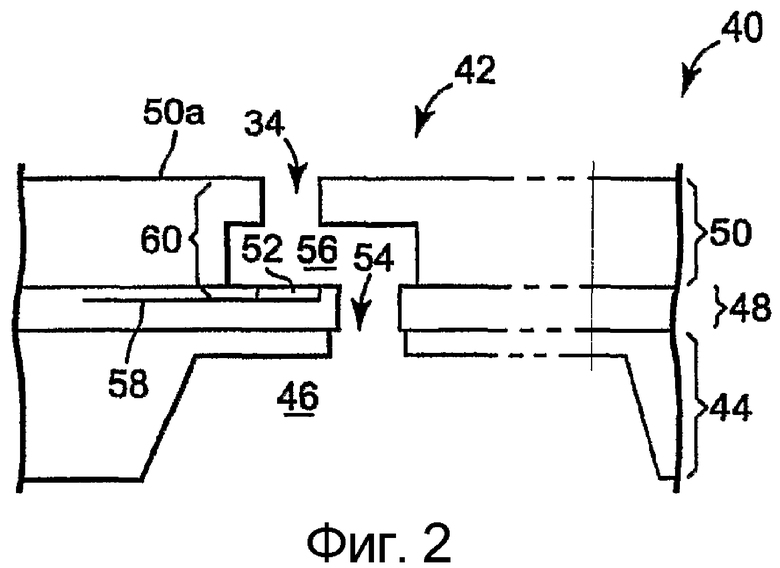

Фиг.2 - схему части варианта воплощения матрицы печатающей головки согласно изобретению;

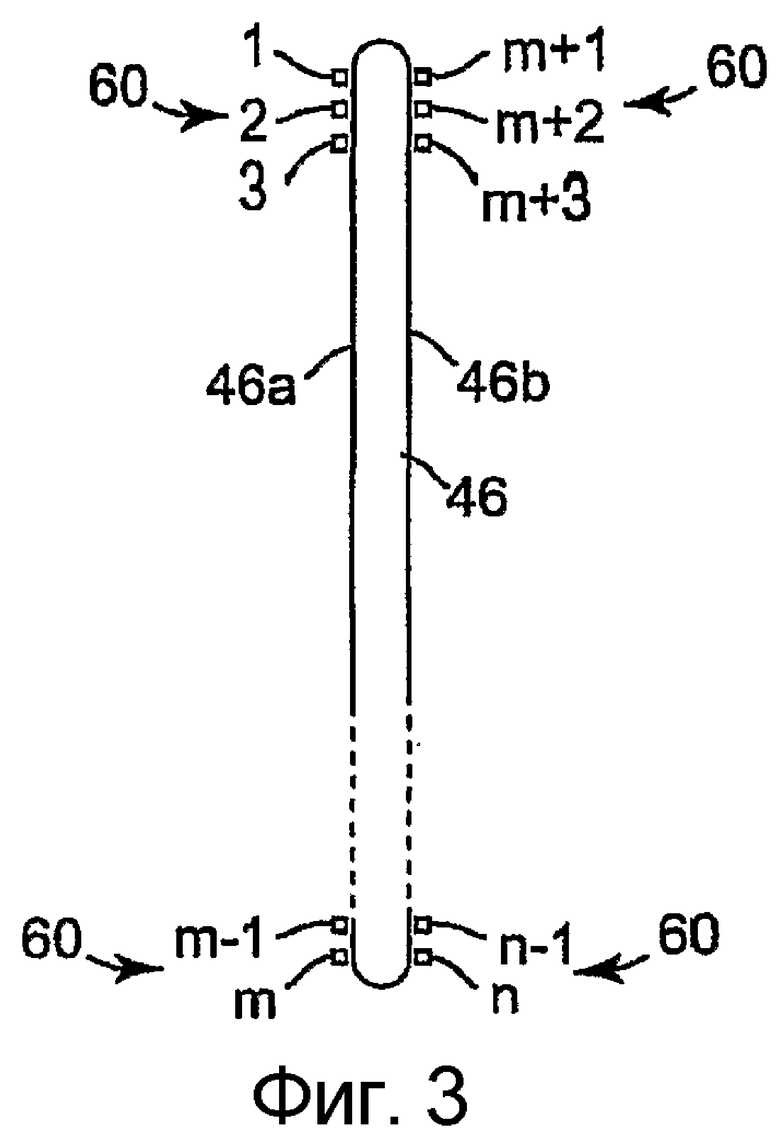

Фиг.3 - схему размещения генераторов капель, расположенных вдоль прорези для подачи чернил в одном варианте воплощения матрицы печатающей головки согласно изобретению;

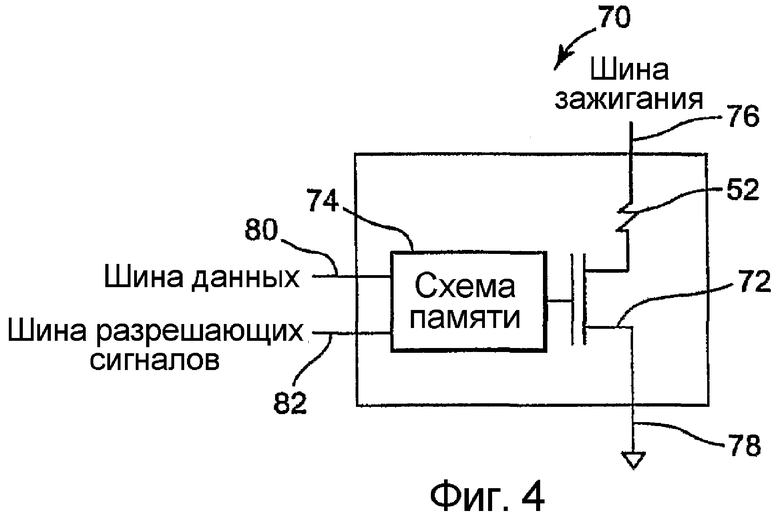

Фиг.4 - схему нагревательной ячейки, используемой в матрице печатающей головки согласно изобретению;

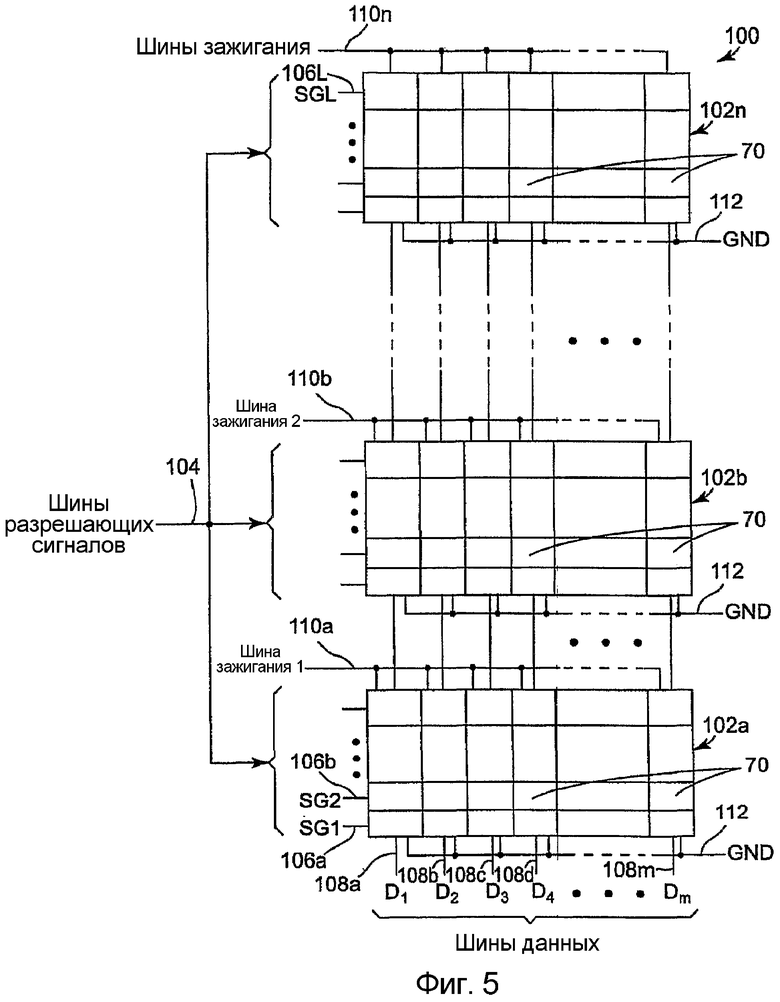

Фиг.5 - схему массива нагревательных ячеек струйной печатающей головки согласно изобретению;

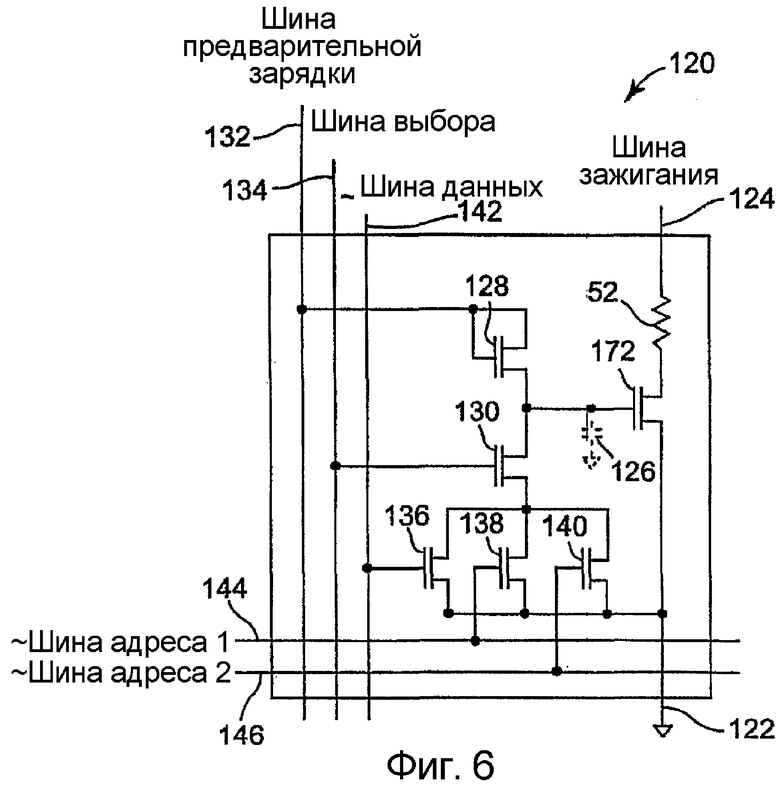

Фиг.6 - электрическую схему предварительно заряженной нагревательной ячейки согласно изобретению;

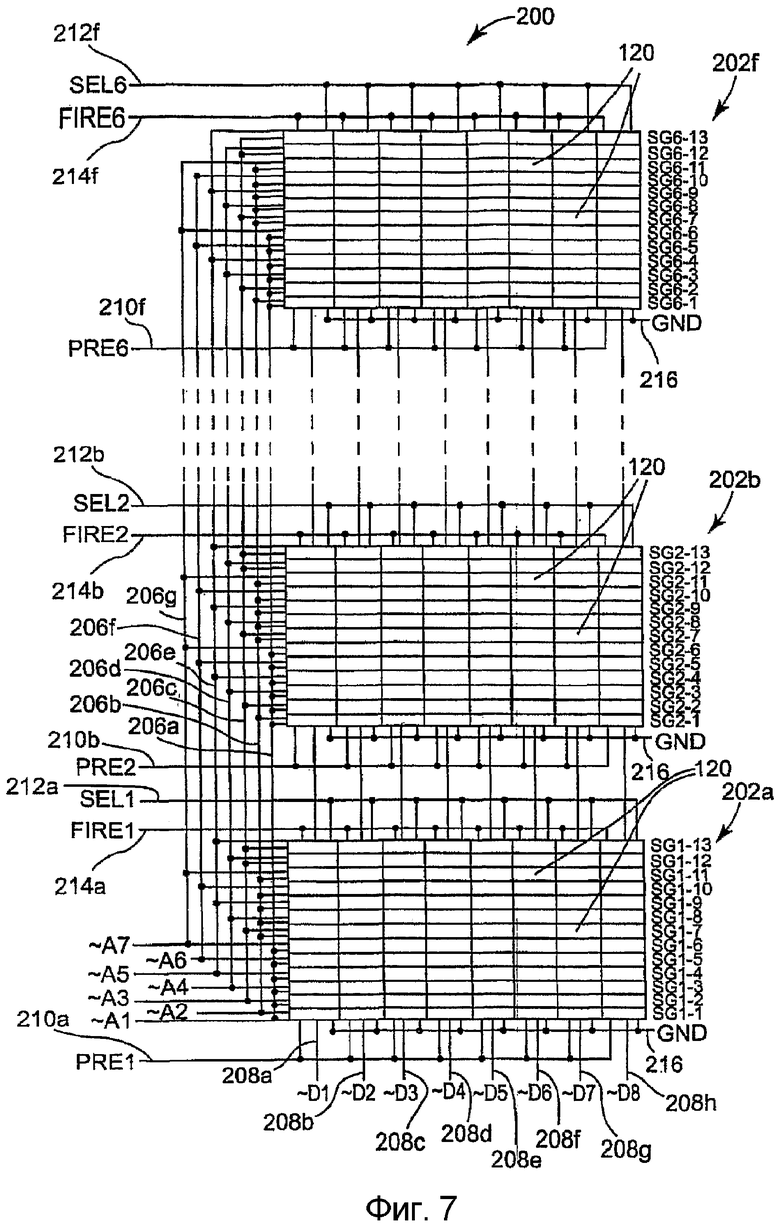

Фиг.7 - схему варианта воплощения массива нагревательных ячеек струйной печатающей головки согласно изобретению;

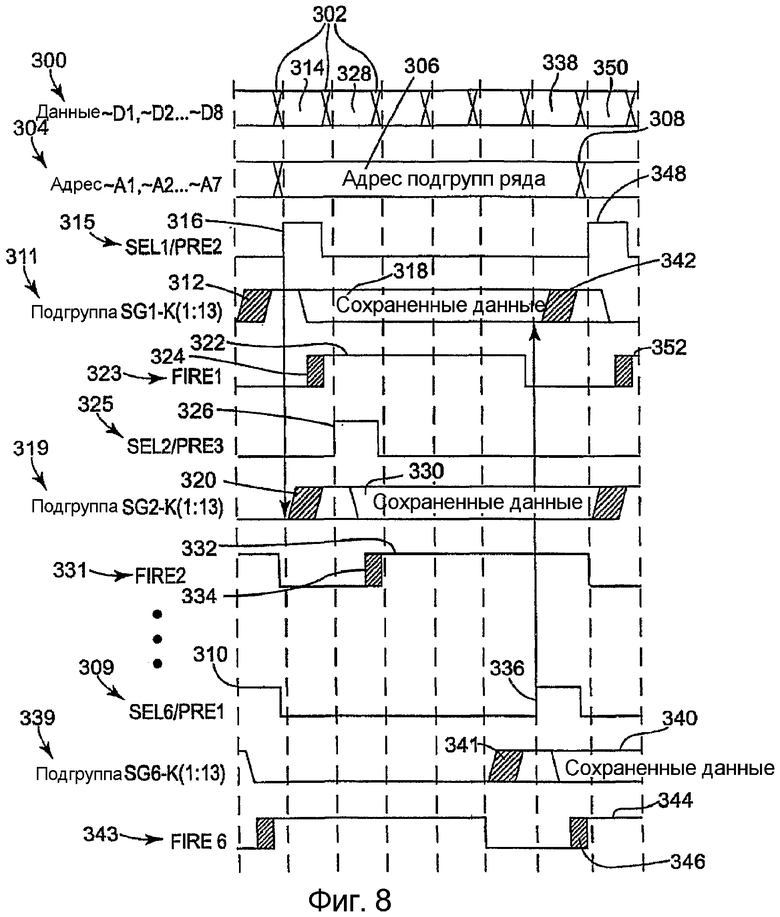

Фиг.8 - временную диаграмму работы массива нагревательных ячеек согласно изобретению;

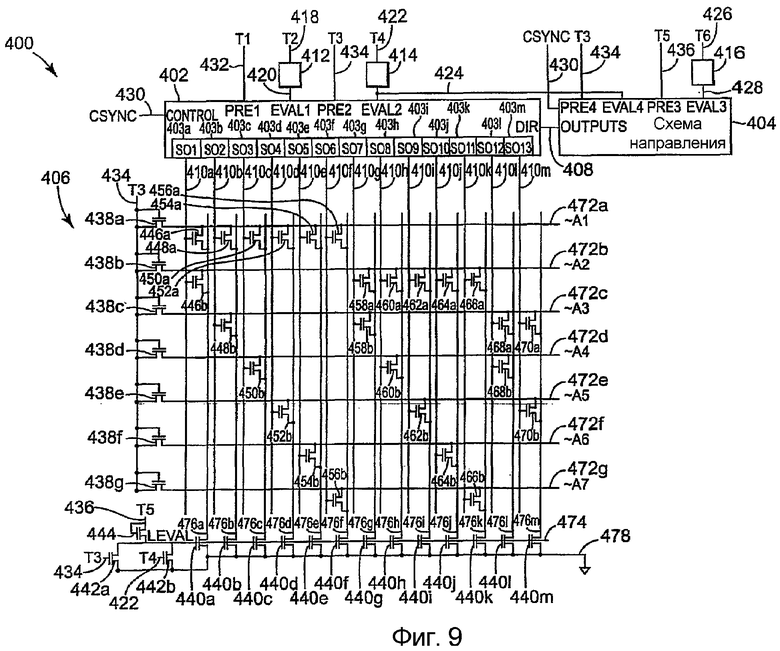

Фиг.9 - схему генератора адреса в матрице печатающей головки согласно изобретению;

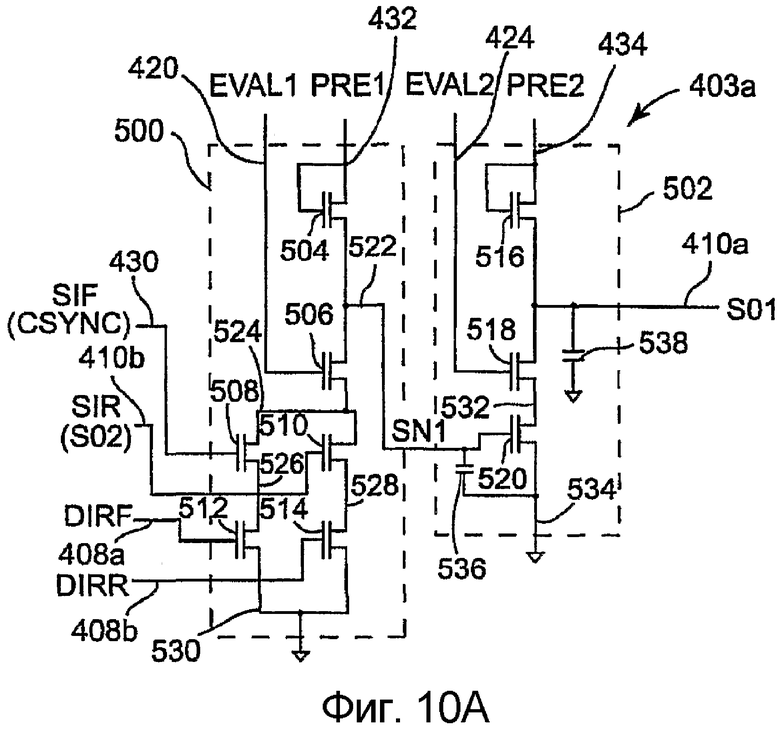

Фиг.10A - электрическую схему одной ячейки сдвигового регистра в сдвиговом регистре согласно изобретению;

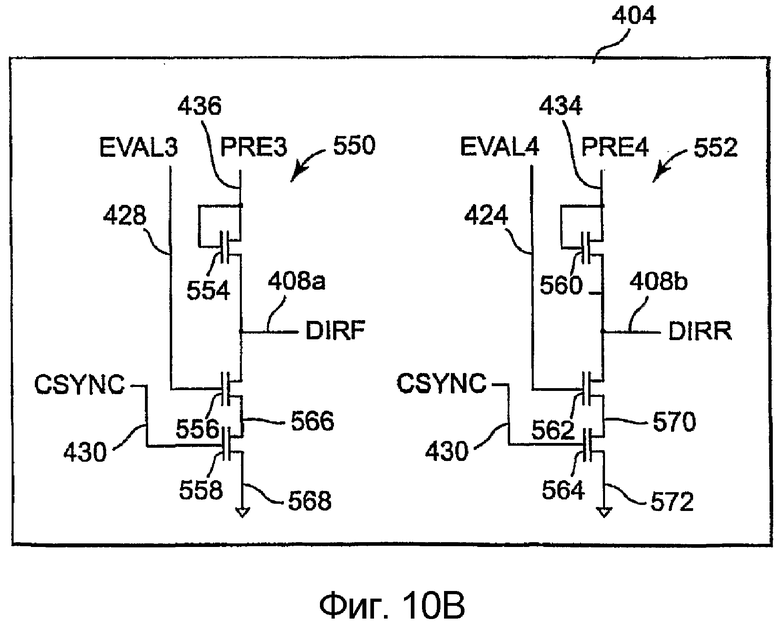

Фиг.10B - схему направления согласно изобретению;

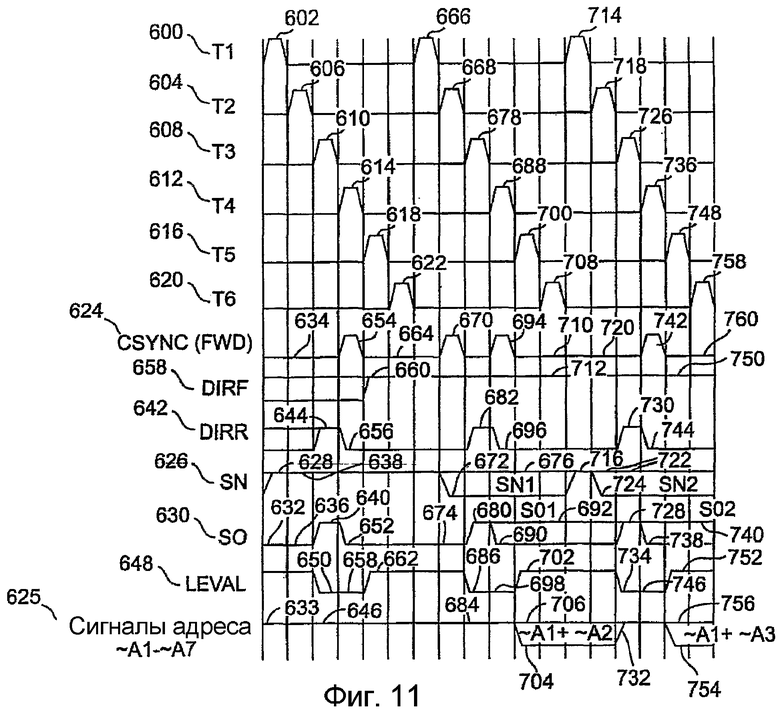

Фиг.11 - временную диаграмму, иллюстрирующую работу генератора адреса в прямом направлении согласно изобретению;

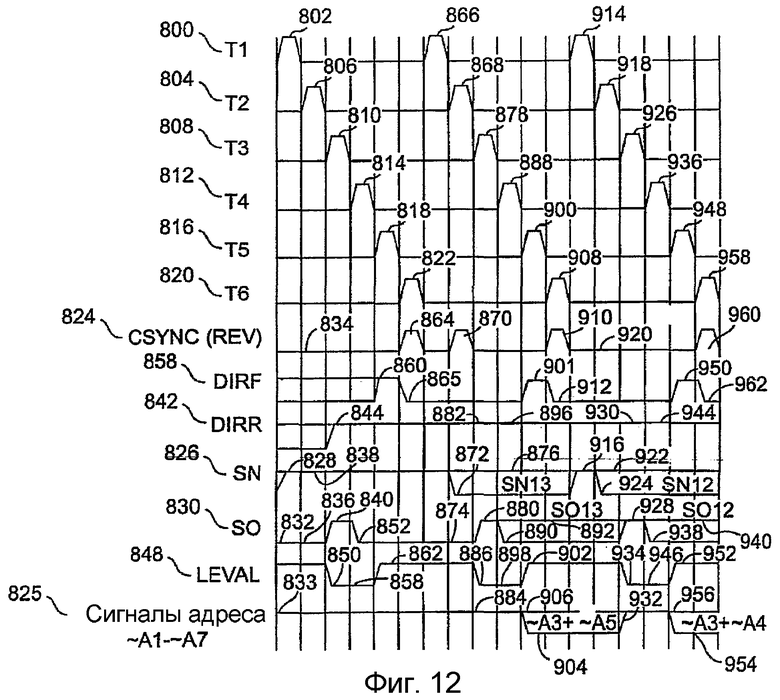

Фиг.12 - временную диаграмму, иллюстрирующую работу генератора адреса в обратном направлении согласно изобретению;

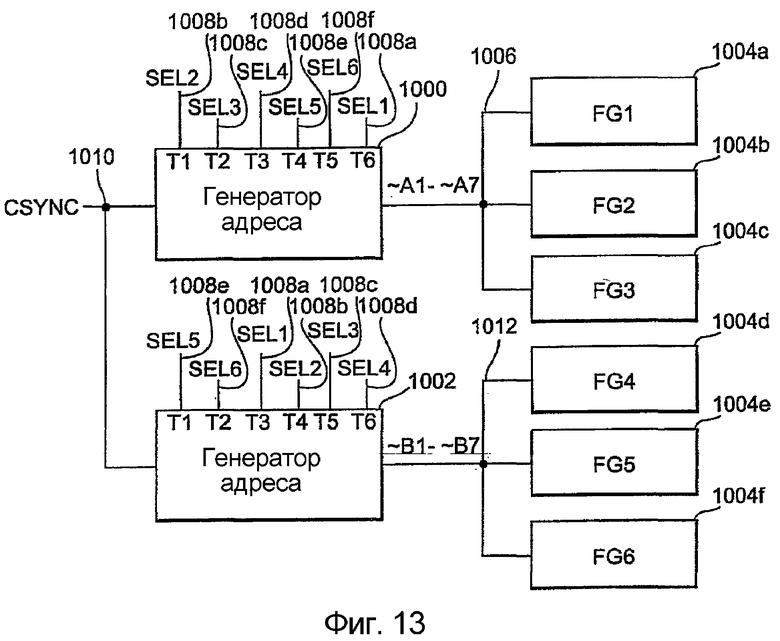

Фиг.13 - блок-схему двух генераторов адреса и шести нагревательных групп в матрице печатающей головки согласно изобретению;

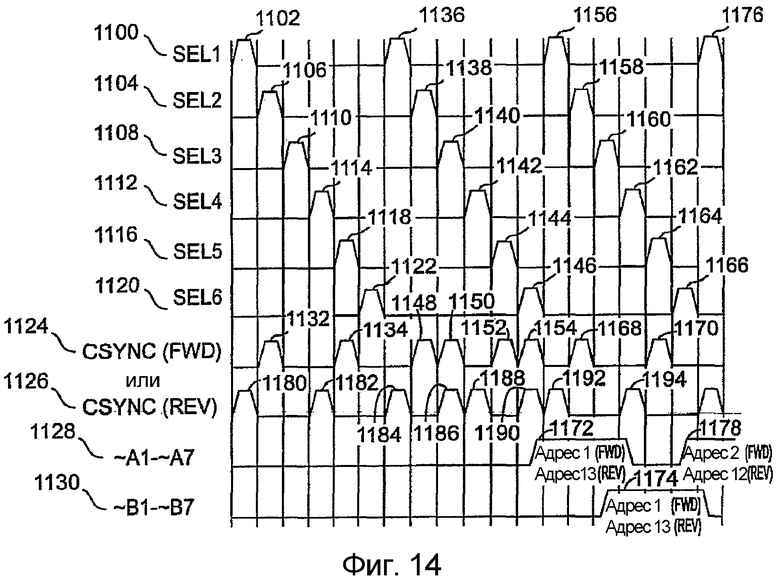

Фиг.14 - временную диаграмму, иллюстрирующую прямое и обратное действие генераторов адреса в матрице печатающей головки согласно изобретению;

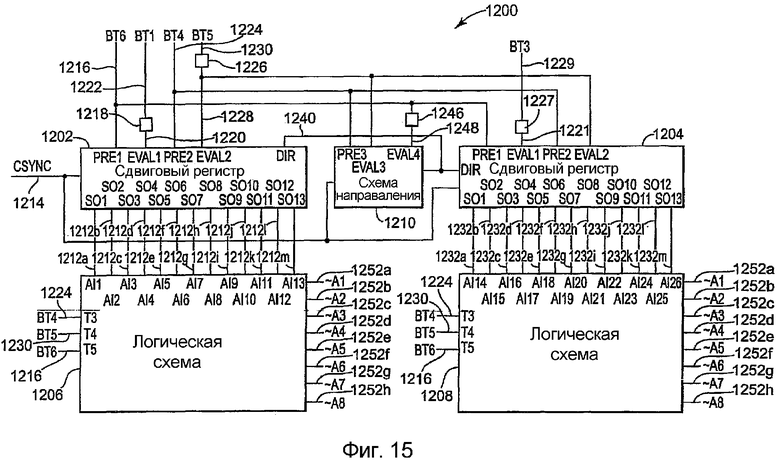

Фиг.15 - схему генератора адреса выбора банка в матрице печатающей головки согласно изобретению;

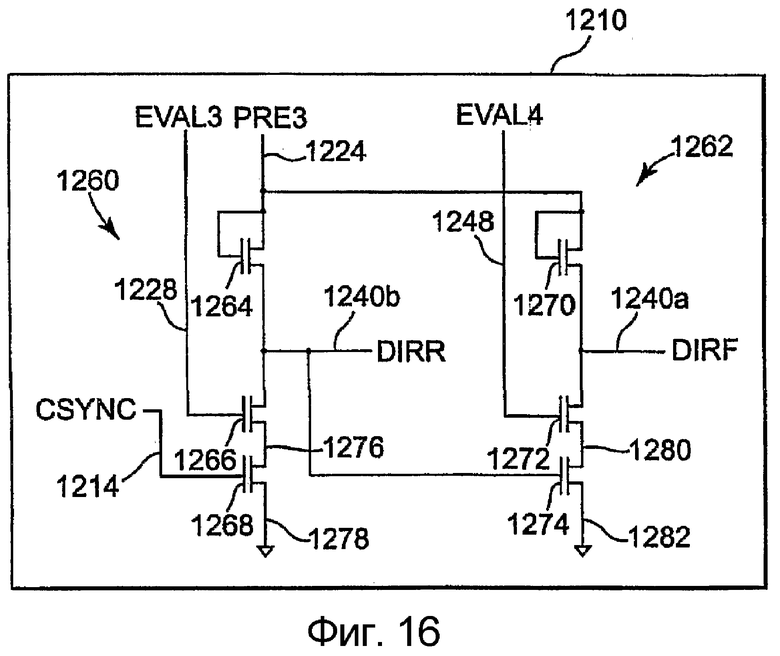

Фиг.16 - схему направления согласно изобретению;

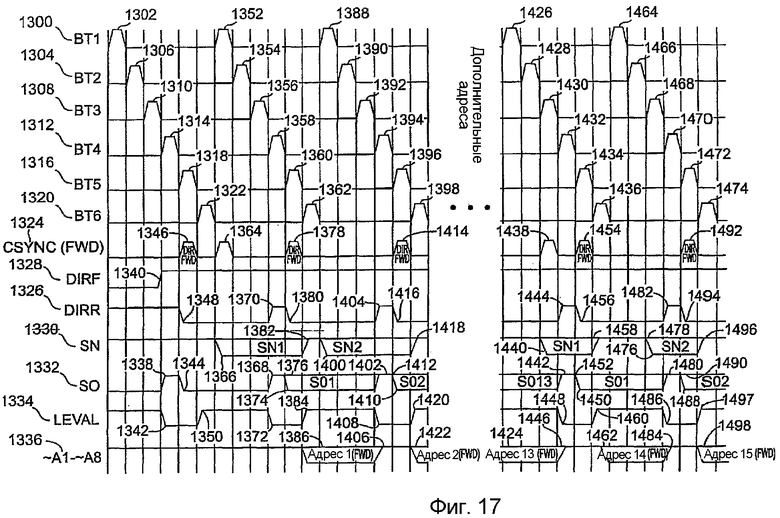

Фиг.17 - временную диаграмму, иллюстрирующую работу генератора адреса выбора банка в прямом направлении согласно изобретению;

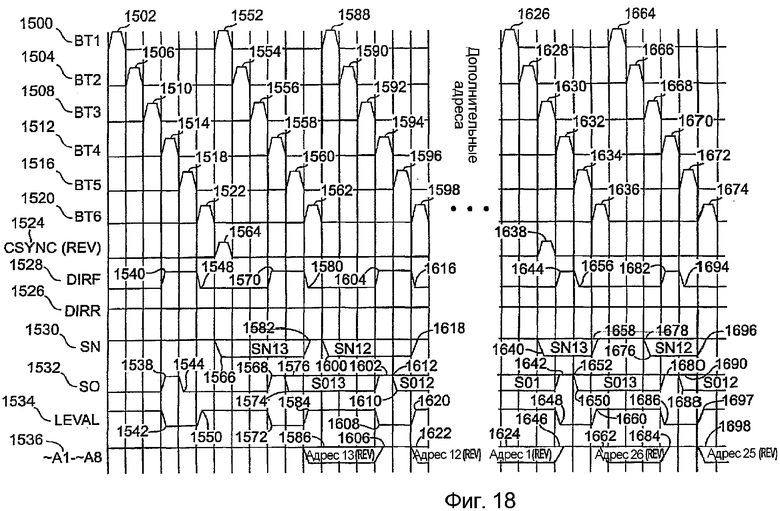

Фиг.18 - временную диаграмму, иллюстрирующую работу генератора адреса выбора банка в обратном направлении согласно изобретению;

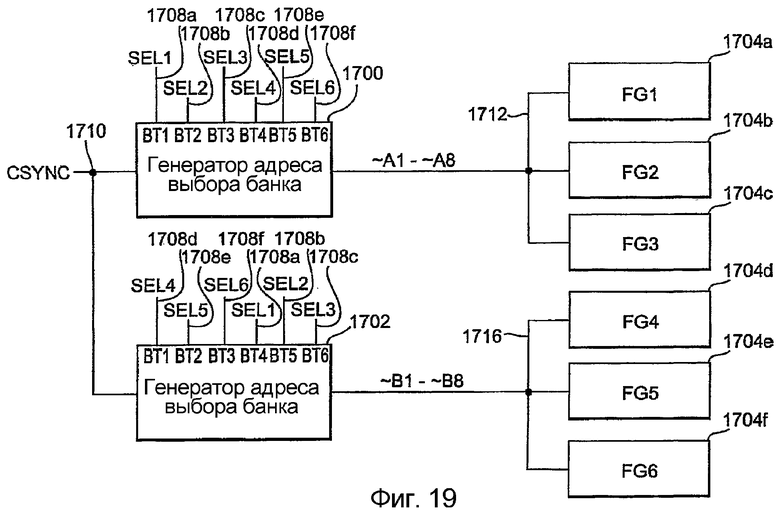

Фиг.19 - схему двух генераторов адреса выбора банка и шести нагревательных групп в матрице печатающей головки согласно изобретению;

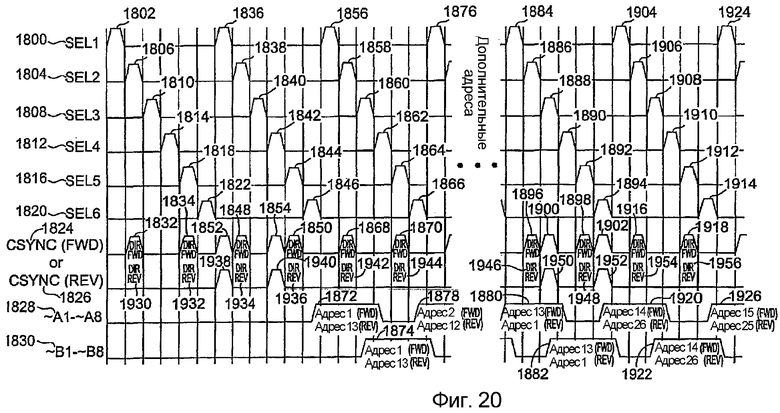

Фиг.20 - временную диаграмму, иллюстрирующую прямое действие и обратное действие одного варианта воплощения двух генераторов адреса выбора банка в матрице печатающей головки согласно изобретению.

Подробное описание предпочтительных вариантов

воплощения изобретения

В данном описании терминология указания направлений, такая как "верх", "низ", "перед", "зад", "передний", "задний" и т.д., используется относительно ориентации описываемых фигур. Поскольку элементы могут быть расположены во множестве других ориентаций, терминология указания направлений используется только для иллюстрации и никоим образом не является ограничивающей. Могут использоваться другие варианты воплощения. Объем настоящего изобретения определяется приложенной формулой изобретения.

На фиг.1 представлен один вариант воплощения системы 20 струйной печати. Система 20 струйной печати является вариантом воплощения системы для эжекции флюида, которая содержит устройство для эжекции флюида, например блок 22 струйной печатающей головки, и блок для подачи флюида, например блок 24 подачи чернил. Система 20 струйной печати также содержит сборочный узел 26, блок 28 транспортировки носителя и электронный контроллер 30. По меньшей мере, один источник 32 питания обеспечивает подачу энергии различным электрическим элементам системы 20 струйной печати.

В одном варианте воплощения блок 22 струйной печатающей головки содержит, по меньшей мере, одну печатающую головку или матрицу 40 печатающей головки, которая эжектирует капли чернил через множество отверстий или сопел 34 к печатному носителю 36, чтобы печатать на печатном носителе 36. Печатающая головка 40 является одним вариантом воплощения устройства для эжекции флюида. Печатный носитель 36 может быть любым типом подходящего листового материала, такого как бумага, стопка карт, прозрачные пленки, майлар, ткань и т.п. Как правило, сопла 34 размещены в одном или более столбцах или массивах таким образом, чтобы осуществлять упорядоченную эжекцию чернил из сопел 34, которая приводит к печати символов и/или другой графики или изображения на печатном носителе 36 по мере того, как блок 22 струйной печатающей головки и печатный носитель 36 перемещаются друг относительно друга. Хотя последующее описание относится к эжекции чернил из блока 22 печатающей головки 22, понятно, что другие жидкости, флюиды (текучие среды) или текучие материалы, включающие в себя чистый флюид, могут эжектироваться из блока 22 печатающей головки.

Блок 24 подачи чернил как один вариант воплощения блока подачи флюида обеспечивает подачу чернил для блока 22 печатающей головки и содержит резервуар 38 для хранения чернил. Чернила текут из резервуара 38 к блоку 22 струйной печатающей головки. Блок 24 подачи чернил и блок 22 струйной печатающей головки могут образовывать либо одностороннюю систему подачи чернил, либо рециркулирующую систему подачи чернил. В односторонней системе подачи чернил главным образом все чернила, поступающие в блок 22 струйной печатающей головки, расходуются во время печати. В рециркулирующей системе подачи чернил только часть чернил, поступающих в блок 22 печатающей головки, расходуется во время печати. Чернила, не употребленные во время печати, возвращаются в блок 24 подачи чернил.

В одном варианте воплощения блок 22 струйной печатающей головки и блок 24 подачи чернил размещены вместе в струйном картридже или пере. Струйный картридж или перо являются одним вариантом воплощения устройства для эжекции флюида. В другом варианте воплощения блок 24 подачи чернил установлен отдельно от блока 22 струйной печатающей головки и обеспечивает подачу чернил для блока 22 струйной печатающей головки через интерфейсное соединение, такое как питающая труба (не показана). В любом варианте воплощения резервуар 38 блока 24 подачи чернил может быть удален, заменен и/или снова наполнен. Если блок 22 струйной печатающей головки и блок 24 подачи чернил размещены вместе в струйном картридже, резервуар 38 содержит локальный резервуар, расположенный в пределах картриджа, и может также включать в себя больший резервуар, расположенный отдельно от картриджа. Отдельный больший резервуар служит для пополнения локального резервуара. В соответствии с этим отдельный больший резервуар и/или локальный резервуар могут быть удалены, заменены и/или снова наполнены.

Сборочный узел 26 обеспечивает размещение блока 22 струйной печатающей головки относительно блока 28 транспортировки носителя, который обеспечивает размещение печатного носителя 36 относительно блока 22 струйной печатающей головки. Таким образом, зона 37 печати определяется примыкающей к соплам 34 в области между блоком 22 струйной печатающей головки и печатным носителем 36. В одном варианте воплощения блок 22 струйной печатающей головки является блоком печатающей головки сканирующего типа. Сборочный узел 26 включает в себя каретку (не показана) для перемещения блока 22 струйной печатающей головки относительно блока 28 транспортировки носителя для сканирования печатного носителя 36. В другом варианте воплощения блок 22 струйной печатающей головки является блоком печатающей головки не сканирующего типа. Сборочный узел 26 обеспечивает закрепление блока 22 струйной печатающей головки в заданном положении относительно блока 28 транспортировки носителя. Таким образом, блок 28 транспортировки носителя обеспечивает расположение печатного носителя 36 относительно блока 22 струйной печатающей головки.

Электронный контроллер 30 или контроллер принтера обычно содержит процессор, встроенное программное обеспечение и другую электронику или любую их комбинацию для взаимодействия и управления блоком 22 струйной печатающей головки, сборочным узлом 26 и блоком 28 транспортировки носителя. Электронный контроллер 30 принимает данные 39 от главной системы, такой как компьютер, и обычно включает в себя память для временного хранения данных 39. Как правило, данные 39 пересылаются системе 20 струйной печати по электронному, инфракрасному, оптическому или другому пути передачи информации. Данные 39 представляют собой, например, документ и/или файл, который должен быть напечатан. Данные 39 образуют задание по выводу на печать для системы 20 струйной печати и включают в себя одну или более команд задания по выводу на печать и/или параметры команды.

В одном варианте воплощения электронный контроллер 30 управляет блоком 22 струйной печатающей головки для эжекции капель чернил из сопел 34. Электронный контроллер 30 определяет шаблон эжектируемых капель чернил, которые формируют символы и/или другую графику или изображения на печатном носителе 36. Шаблон эжектируемых капель чернил определяется командами задания по выводу на печать и/или параметрами команды.

В одном варианте воплощения блок 22 струйной печатающей головки содержит одну печатающую головку 40. В другом варианте воплощения блок 22 струйной печатающей головки является блок печатающей головки с массивом головок или несколькими головками. В варианте с массивом головок блок 22 струйной печатающей головки содержит несущую, на которой размещены матрицы 40 печатающей головки, обеспечивает электрическое соединение между матрицами 40 печатающей головки и электронным контроллером 30 и содержит канал для жидкостного соединения между матрицами 40 печатающей головки и блоком 24 подачи чернил.

На фиг.2 представлен вариант воплощения матрицы 40 печатающей головки. Матрица 40 печатающей головки содержит массив печатающих или эжектирующих флюид элементов 42. Элементы 42 сформированы на подложке 44, которая имеет прорезь 46 для подачи чернил. Через прорезь 46 для подачи чернил осуществляется подача жидких чернил к печатающим элементам 42. Прорезь 46 подачи чернил является одним вариантом воплощения источника подачи флюида. Другие варианты воплощения источников подачи флюида включают в себя, но не ограничиваясь этим, соответствующие индивидуальные отверстия для подачи чернил к соответствующим камерам испарения и нескольким более коротким канавкам для подачи чернил, через каждую из которых осуществляется подача чернил соответствующим группам эжектирующих флюид элементов. Тонкопленочная структура 48 имеет канал 54 подачи чернил, который связан с прорезью 46 для подачи чернил, сформированной в подложке 44. Слой 50 отверстий имеет лицевую сторону 50a и отверстие 34 сопла, сформированное на лицевой стороне 50a. Слой 50 отверстий также имеет камеру сопла или камеру 56 испарения, которая соединена с отверстием 34 сопла и каналом 54 подачи чернил тонкопленочной структуры 48. Нагревательный резистор 52 расположен в пределах камеры 56 испарения, выводы 58 электрически соединяют нагревательный резистор 52 со схемой, управляющей подачей электрического тока к выбранному нагревательному резистору. Генератор 60 капель содержит нагревательный резистор 52, камеру сопла или камеру 56 испарения и отверстие 34 сопла.

Во время печати чернила текут от прорези 46 для подачи чернил к камере 56 испарения через канал 54 для подачи чернил. Отверстие 34 сопла связано с нагревательным резистором 52 таким образом, что капельки чернил в камере 56 испарения эжектируются через отверстие 34 сопла, например, главным образом перпендикулярно плоскости нагревательного резистора 52 к печатному носителю 36 после подачи энергии на нагревательный резистор 52.

В различных вариантах воплощения матрицы 40 печатающей головки содержат термическую печатающую головку, пьезоэлектрическую печатающую головку, электростатическую печатающую головку или любой другой тип устройства эжекции флюида, известного в этой области техники, которое может быть интегрировано в многослойную структуру. Подложка 44 сформирована, например, из кремния, стекла, керамики или устойчивого полимера, а тонкопленочная структура 48 сформирована для включения в себя одного или более слоев пассивирования или изоляции из диоксида кремния, карбида кремния, нитрида кремния, тантала, поликремниевого стекла или другого подходящего материала. Тонкопленочная структура 48 также включает в себя по меньшей мере один проводящий слой, который представляет собой нагревательный резистор 52 и выводы 58. В одном варианте воплощения проводящий слой содержит, например, алюминий, золото, тантал, тантал-алюминий или другой металл или металлический сплав. В одном варианте воплощения схема нагревательных ячеек, такая как описана подробно ниже, реализована в подложке и тонкопленочных слоях, таких как подложка 44 и тонкопленочная структура 48.

В одном варианте воплощения слой 50 отверстий содержит светочувствительную эпоксидную смолу, например эпоксидную смолу, называемую SU8, поставляемую Micro-Chem, Ньютон, штат Массачусетс. Методики изготовления слоя 50 отверстий из SU8 или других полимеров подробно описаны в патенте США №6162589. В одном варианте воплощения слой 50 отверстий сформирован в виде двух отдельных слоев, называемых барьерным слоем (например, барьерный слой сухой пленки фоторезиста) и металлическим слоем отверстий (например, слой никеля, меди, сплава железа/никеля, палладия, золота или родия), сформированным поверх барьерного слоя. Однако могут использоваться другие подходящие материалы для сформирования слоя 50 отверстий.

На фиг.3 представлены генераторы 60 капель, расположенные вдоль прорези 46 для подачи чернил. Прорезь 46 подачи чернил имеет противоположные стороны 46a и 46b. Генераторы 60 капель расположены вдоль каждой из противоположных сторон 46a и 46b прорези подачи чернил. В общей сложности n генераторов 60 капель расположены вдоль прорези 46 подачи чернил, m генераторов 60 капель расположены вдоль стороны 46a прорези подачи чернил, и n - m генераторов 60 капель расположены вдоль стороны 46b прорези подачи чернил. В одном варианте воплощения n равно 200 генераторам 60 капель, расположенных вдоль прорези 46 подачи чернил, и m равно 100 генераторам 60 капель, расположенных вдоль каждой из противоположных сторон 46a и 46b прорези подачи чернил. В других вариантах воплощения любое подходящее количество генераторов 60 капель может быть расположено вдоль прорези 46 подачи чернил.

Прорезь 46 подачи чернил обеспечивает подачу чернил каждому из n генераторов 60 капель, расположенных вдоль прорези 46 подачи чернил. Каждый из n генераторов 60 капель содержит нагревательный резистор 52, камеру 56 испарения и сопло 34. Каждая из n камер 56 испарения соединена посредством жидкой среды с прорезью 46 подачи чернил, по меньшей мере, через один канал 54 подачи чернил. На нагревательные резисторы 52 генераторов 60 капель подается энергия в управляемой последовательности для эжекции флюида из камер 56 испарения через сопла 34 для печати изображения на печатном носителе 36.

На фиг.4 представлен вариант воплощения нагревательной ячейки 70, используемой в матрице 40 печатающей головки. Нагревательная ячейка 70 содержит нагревательный резистор 52, переключатель 72 возбуждения резистора и схему 74 памяти. Нагревательный резистор 52 является частью генератора 60 капель. Переключатель 72 возбуждения и схема 74 памяти являются частью схемы, которая управляет подачей электрического тока к нагревательному резистору 52. Нагревательная ячейка 70 сформирована в тонкопленочной структуре 48 и на подложке 44.

В одном варианте воплощения нагревательный резистор 52 является тонкопленочным резистором, а переключатель 72 возбуждения является полевым транзистором. Нагревательный резистор 52 электрически соединен с шиной 76 зажигания и с линией сток-исток переключателя 72 возбуждения. Сток-исток переключателя 72 возбуждения также электрически соединен с опорной линией 78, которая соединена с опорным напряжением, таким как земля. Затвор переключателя 72 возбуждения электрически соединен со схемой 74 памяти, которая управляет состоянием переключателя 72 возбуждения.

Схема 74 памяти электрически соединена с шиной 80 данных и шинами 82 разрешающих сигналов. Шина 80 данных принимает сигнал данных, который представляет часть изображения, и шины 82 разрешающих сигналов принимают разрешающие сигналы для управления работой схемы 74 памяти. Схема 74 памяти хранит один бит данных, когда он включается разрешающими сигналами. Логический уровень сохраненного бита данных устанавливает состояние (например, включено или выключено, проводящий или непроводящий) переключателя 72 возбуждения. Разрешающие сигналы могут включать в себя один или более сигналов выбора и один или более сигналов адреса.

Шина 76 запуска принимает сигнал энергии, содержащий импульсы энергии, и подает импульс энергии нагревательному резистору 52. В одном варианте воплощения электронный контроллер 30 подает импульсы энергии в заданное по времени время начало и с заданной по времени продолжительностью для обеспечения надлежащего количества энергии для нагревания и испарения жидкости в камере 56 испарения генератора 60 капель. Если переключатель 72 возбуждения включен (проводит ток), импульс энергии нагревает нагревательный резистор 52 для нагревания и эжекции флюида из генератора 60 капель. Если переключатель 72 возбуждения выключен (не проводит ток), импульс энергии не нагревает нагревательный резистор 52 и жидкость остается в генераторе 60 капель.

На фиг.5 представлен вариант воплощения массива 100 нагревательной ячейки струйной печатающей головки. Массив 100 нагревательной ячейки содержит множество нагревательных ячеек 70, размещенных в n группах 102a-102n. В одном варианте воплощения нагревательные ячейки 70 размещены в шести нагревательных группах 102a-102n. В других вариантах воплощения нагревательные ячейки 70 могут быть размещены в любом подходящем количестве нагревательных групп 102a-102n, например четырех или более нагревательных групп 102a-102n.

Нагревательные ячейки 70 в массиве 100 схематически размещены в L рядов и m столбцов. L рядов нагревательных ячеек 70 электрически соединены с шинами 104 разрешающих сигналов, которые принимают разрешающие сигналы. Каждый ряд нагревательных ячеек 70, называемый здесь как подгруппа ряда или подгруппа нагревательных ячеек 70, электрически соединен с одним набором шин 106a-106L разрешающих сигналов подгрупп. Шины 106a-106L разрешающих сигналов подгрупп принимают разрешающие сигналы SG1, SG2... SGL подгрупп, которые активируют соответствующую подгруппу нагревательных ячеек 70.

m столбцов электрически соединены с m шин 108a-108m данных, которые принимают сигналы D1, D2... Dm данных соответственно. Каждый из m столбцов содержит нагревательные ячейки 70 в каждой из n нагревательных групп 102a-102n, и каждый столбец нагревательных ячеек 70, называемый здесь группой шины данных или группой данных, электрически соединен с одной из шин 108a-108m данных. Другими словами, каждая из шин 108a-108m данных электрически соединена с каждой из нагревательных ячеек 70 в одном столбце, в том числе, с нагревательными ячейками 70 в каждой из нагревательных групп 102a-102n. Например, шина 108a данных электрически соединена с каждой из нагревательных ячеек 70 в крайнем левом столбце, в том числе с нагревательными ячейками 70 в каждой из нагревательных групп 102a-102n. Шина 108b данных электрически соединена с каждой из нагревательных ячеек 70 в смежном столбце и так далее до шины 108m данных включительно, которая электрически соединена с каждой из нагревательных ячеек 70 в крайнем правом столбце, в том числе с нагревательными ячейками 70 в каждой из нагревательных групп 102a-102n.

В одном варианте воплощения массив 100 организован в шесть нагревательных групп 102a-102n и каждая из этих шести нагревательных групп 102a-102n содержит 13 подгрупп и восемь групп шины данных. В других вариантах воплощения массив 100 может содержать любое подходящее количество нагревательных групп 102a-102n и любое подходящее количество подгрупп и групп шины данных. В любом варианте воплощения нагревательные группы 102a-102n не ограничены наличием одного и того же количества подгрупп и групп шины данных. Вместо этого каждая из нагревательных групп 102a-102n может иметь различное количество подгрупп и/или групп шины данных по сравнению с любой другой нагревательной группой 102a-102n. Кроме того, каждая подгруппа может иметь различное количество нагревательных ячеек 70 по сравнению с любой другой подгруппой, и каждая группа шины данных может иметь различное количество нагревательных ячеек 70 по сравнению с любой другой группой шины данных.

Нагревательные ячейки 70 в каждой из нагревательных групп 102a-102n электрически соединены с одной из шин 110a-110n зажигания. В нагревательной группе 102a каждая из нагревательных ячеек 70 электрически соединена с шиной 110a зажигания, которая принимает сигнал зажигания или сигнал FIRE1 энергии. В нагревательной группе 102b каждая из нагревательных ячеек 70 электрически соединена с шиной 110b зажигания, которая принимает сигнал зажигания или сигнал FIRE2 энергии и так далее до нагревательной группы 102n включительно, в которой каждая из нагревательных ячеек 70 электрически соединена с шиной 110n зажигания, которая принимает сигнал зажигания или сигнал FIREn энергии. Кроме того, каждая из нагревательных ячеек 70 в каждой из нагревательных групп 102a-102n электрически соединена с общей опорной шиной 112, которая связана с землей.

Во время работы разрешающие сигналы SG1, SG2... SGL подгруппы подаются на шины 106a-106L разрешающих сигналов подгруппы для активирования одной подгруппы нагревательных ячеек 70. Активированные нагревательные ячейки 70 сохраняют сигналы D1, D2... Dm на шинах 108a-108m данных. Сигналы D1, D2... Dm данных сохраняются в схемах 74 памяти активированных нагревательных ячеек 70. Каждый из сохраненных сигналов D1, D2... Dm данных устанавливает состояние переключателя 72 возбуждения в одной из активированных нагревательных ячеек 70. Переключатель 72 возбуждения устанавливается для проведения тока или непроведения тока на основе сохраненного значения сигнала данных.

После того как состояния выбранных переключателей 72 возбуждения установлены, сигнал FIRE1-FIREn энергии подается на шину 110a-110n зажигания, соответствующую нагревательной группе 102a-102n, которая включает в себя выбранную подгруппу нагревательных ячеек 70. Сигнал FIRE1-FIREn энергии содержит импульс энергии. Импульс энергии подается на выбранную шину 110a-110n зажигания для подачи энергии на нагревательные резисторы 52 в нагревательных ячейках 70, которые имеют проводящие переключатели 72 возбуждения. Нагревательные резисторы 52, на которые подана энергия, нагревают и эжектируют чернила на печатный носитель 36 для печати изображения, представленного сигналами D1, D2... Dm данных. Процесс активирования подгруппы нагревательных ячеек 70, хранения сигналов D1, D2... Dm данных в активированной подгруппе и обеспечения сигнала FIRE1-FIREn энергии для подачи энергии на нагревательные резисторы 52 в активированной подгруппе продолжается, пока печать не остановится.

В одном варианте воплощения, когда сигнал FIRE1-FIREn энергии подается к выбранной нагревательной группе 102a-102n, разрешающие сигналы SG1, SG2... SGL подгруппы изменяются для выбора и активирования другой подгруппы в другой нагревательной группе 102a-102n. Новая активированная подгруппа сохраняет сигналы D1, D2... Dm данных на шинах 108a-108m данных, и сигналы FIRE1-FIREn энергии подаются на одну из шин 110a-110n зажигания для подачи энергии на нагревательные резисторы 52 в новых активированных нагревательных ячейках 70. В любой момент только одна подгруппа нагревательных ячеек 70 активируется разрешающими сигналами SG1, SG2... SGL подгруппы для сохранения сигналов D1, D2... Dm данных на шинах 108a-108m данных. В этом случае сигналы D1, D2... Dm данных на шинах 108a-108m данных являются мультиплексированными сигналами данных с разделением по времени. Кроме того, только одна подгруппа в отобранной нагревательной группе 102a-102n включает в себя переключатели 72 возбуждения, которые установлены для проведения тока, когда сигнал FIRE1-FIREn энергии подается к выбранной нагревательной группе 102a-102n. Однако сигналы FIRE1-FIREn энергии, подаваемые различным нагревательным группам 102a-102n, могут накладываться и накладываются.

На фиг.6 представлен вариант воплощения предварительно заряженной нагревательной ячейки 120. Предварительно заряженная нагревательная ячейка 120 является одним вариантом воплощения нагревательной ячейки 70. Предварительно заряженная нагревательная ячейка 120 содержит переключатель 172 возбуждения, электрически соединенный с нагревательным резистором 52. В одном варианте воплощения переключатель 172 возбуждения является полевым транзистором, включающий в себя линию исток-сток, электрически соединенную с одного конца с одним выводом нагревательного резистора 52 и с другого конца с опорной шиной 122. Опорная шина 122 связана с опорным напряжением, таким как земля. Другой вывод нагревательного резистора 52 электрически соединен с шиной 124 зажигания, которая принимает сигнал зажигания или сигнал FIRE энергии, содержащий импульсы энергии. Импульсы энергии активируют нагревательный резистор 52, если переключатель 172 включен (проводит ток).

Затвор переключателя 172 возбуждения образует емкостное сопротивление 126 узла хранения, который функционирует как элемент памяти для хранения данных в соответствии с последовательной активацией транзистора 128 предварительной зарядки 128 и транзистора 130 выбора. Сток-исток и затвор транзистора 128 предварительной зарядки электрически соединены с шиной 132 предварительной зарядки, которая принимает сигнал предварительной зарядки. Затвор переключателя 172 возбуждения электрически соединен с линией исток-сток транзистора 128 предварительной зарядки и исток-сток транзистора 130 выбора. Ворота транзистора 130 выбора электрически соединены с шиной 134 выбора, которая принимает сигнал выбора. Емкостное сопротивление 126 узла хранения показано пунктирными линиями, поскольку оно является частью переключателя 172 возбуждения. В качестве альтернативы конденсатор, отдельный от переключателя 172 возбуждения, может использоваться как элемент памяти.

Транзистор 136 данных, первый транзистор 138 адреса и второй транзистор 140 адреса содержат исток-сток, которые электрически соединены параллельно. Параллельная комбинация транзистора 136 данных, первого транзистора 138 адреса и второго транзистора 140 адреса, электрически соединена между сток-исток транзистора 130 выбора и опорной шиной 122. Последовательная схема, содержащая транзистор 130 выбора, соединенный с параллельной комбинацией транзистора 136 данных, первого транзистора 138 адреса и второго транзистора 140 адреса электрически соединена через емкостное сопротивление 126 узла переключателя 172 возбуждения. Затвор транзистора 136 данных электрически соединен c шиной 142 данных, которая принимает сигналы ˜DATA данных. Затвор первого транзистора 138 адреса электрически соединен с шиной 144 адреса, которая принимает сигналы ˜ADDRESS1 адреса, и затвор второго транзистора 140 адреса электрически соединен со второй шиной 146 адреса, которая принимает сигналы ˜ADDRESS2 адреса. Сигналы ˜DATA данных и сигналы ˜ADDRESS1 и ˜ADDRESS2 являются активными при низком уровне сигнала, как обозначено тильдой (˜) в начале названия сигнала. Емкостное сопротивление 126 узла, транзистор 128 предварительной зарядки, транзистор 130 выбора, транзистор 136 данных и транзисторы 138 и 140 адреса образуют ячейку памяти.

Во время работы емкостное сопротивление 126 узла предварительно заряжается через транзистор 128 предварительной зарядки путем подачи импульса напряжения высокого уровня на шину 132 предварительной зарядки. В одном варианте воплощения после подачи импульса напряжения высокого уровня на шину 132 предварительной зарядки сигнал ˜DATA данных подается на шину 142 данных для установки состояния транзистора 136 данных и сигналы ˜ADDRESS1 и ˜ADDRESS2 адреса подаются на шины 144 и 146 адреса для установки состояния первого транзистора 138 адреса и второго транзистора 140 адреса. Импульс напряжения достаточной величины подается на шину 134 выбора для включения транзистора 130 выбора, и емкостное сопротивление 126 узла разряжается, если транзистор 136 данных, первый транзистор 138 адреса и/или второй транзистор 140 адреса включены. В качестве альтернативы емкостное сопротивление 126 узла остается заряженным, если транзистор 136 данных, первый транзистор 138 адреса и второй транзистор 140 адреса все выключены.

Предварительно заряженная нагревательная ячейка 120 является адресной нагревательной ячейкой, если оба сигнала ˜ADDRESS1 и ˜ADDRESS2 адреса имеют низкий уровень, и емкостное сопротивление 126 узла либо разряжается, если сигнал ˜DATA данных имеет высокий уровень, либо остается заряженным, если сигнал ˜DATA данных имеет низкий уровень. Предварительно заряженная нагревательная ячейка 120 не является адресной нагревательной ячейкой, если, по меньшей мере, один из сигналов ˜ADDRESS1 и-ADDRESS2 адреса имеет высокий уровень, и емкостное сопротивление 126 узла разряжается независимо от уровня напряжения сигнала ˜DATA данных. Первый и второй транзисторы 136 и 138 адреса содержат дешифратор адреса, а транзистор 136 данных управляет уровнем напряжения на емкостном сопротивлении 126 узла, если предварительно заряженная нагревательная ячейка 120 является адресной.

Предварительно заряженная нагревательная ячейка 120 может использовать любое количество других топологий или компоновок, пока поддерживаются описанные выше операционные отношения. Например, вентиль "ИЛИ" может быть соединен с шинами 144 и 146 адреса, вывод которого соединен с одним транзистором.

На фиг.7 представлен один вариант воплощения массива 200 нагревательных ячеек струйной печатающей головки. Массив 200 нагревательных ячеек содержит множество предварительно заряженных нагревательных ячеек 120, скомпонованных в шесть нагревательных групп 202a-202f. Предварительно заряженные нагревательные ячейки 120 в каждой нагревательной группе 202a-202f схематично скомпонованы в 13 рядов и восемь столбцов. Нагревательные группы 202a-202f и предварительно заряженные нагревательные ячейки 120 в массиве 200 схематично скомпонованы в 78 рядов и восемь столбцов, хотя количество предварительно заряженных нагревательных ячеек и их компоновка могут быть изменены.

Восемь столбцов предварительно заряженных нагревательных ячеек 120 электрически соединены с восемью шинами 208a-208h данных, которые принимают сигналы ˜D1, ˜D2... ˜D8 данных соответственно. Каждый из восьми столбцов, называемых здесь группой шины данных или группой данных, включает в себя предварительно заряженные нагревательные ячейки 120 в каждой из шести нагревательных групп 202a-202f. Каждая из нагревательных ячеек 120 в каждом столбце предварительно заряженных нагревательных ячеек 120 электрически соединена с одной из шин 208a-208h данных. Все предварительно заряженные нагревательные ячейки 120 в группе шины данных электрически соединены с той же самой шиной 208a-208-ой данных, которая электрически соединена с затворами транзисторов 136 данных в предварительно заряженных нагревательных ячейках 120 в столбце.

Шина 208a данных электрически соединена с каждой из предварительно заряженных нагревательных ячеек 120 в крайне левом столбце, в том числе с предварительно заряженными нагревательными ячейками в каждой из нагревательных групп 202a-202f. Шина 208b данных электрически соединена с каждой из предварительно заряженных нагревательных ячеек 120 в смежном столбце и так далее до шины 208h данных включительно, которая электрически соединена с каждой из предварительно заряженных нагревательных ячеек 120 в крайнем правом столбце, в том числе с предварительно заряженными нагревательными ячейками 120 в каждой из нагревательных групп 202a-202f.

Ряды предварительно заряженных нагревательных ячеек 120 электрически соединены с шинами 206a-206g адреса, которые принимают сигналы ˜A1, ˜A2... ˜A7 адреса соответственно. Каждая предварительно заряженная нагревательная ячейка 120 в ряду предварительно заряженных нагревательных ячеек 120, называемом здесь подгруппой ряда или подгруппой предварительно заряженных нагревательных ячеек 120, электрически соединена с двумя из шин 206a-206g адреса. Все предварительно заряженные нагревательные ячейки 120 в подгруппе ряда электрически соединены с теми же самыми двумя шинами 206a-206g адреса.

Подгруппы нагревательных групп 202a-202f идентифицированы как подгруппы от SG1-1 до SG1-13 в нагревательной группе 202a один (FG1), подгруппы от SG2-1 до SG2-13 в нагревательной группе 202b два (FG2) и так далее до подгруппы от SG6-1 до SG6-13 включительно в нагревательной группе 202f шесть (FG6). В других вариантах воплощения каждая нагревательная группа 202a-202f может включать в себя любое подходящее количество подгрупп, например 14 или более подгрупп.

Каждая подгруппа предварительно заряженных нагревательных ячеек 120 электрически соединена с двумя шинами 206a-206g адреса. Две шины 206a-206g адреса, соответствующие подгруппе, электрически соединены с первым и вторым транзисторами 138 и 140 адреса во всех предварительно заряженных нагревательных ячейках 120 из подгруппы. Одна шина 206a-206g адреса электрически соединена с затвором одного из первого и второго транзисторов 138 и 140 адреса, и другая шина 206a-206g адреса электрически соединена с затвором другого из первого и второго транзисторов 138 и 140 адреса. Шины 206a-206g адреса принимают сигналы ˜A1, ˜A2... ˜A7 адреса и соединены для подачи сигналов ˜A1, ˜A2... ˜A7 адреса подгруппам массива 200 следующим образом:

К подгруппам предварительно заряженных нагревательных ячеек 120 обращаются путем подачи сигналов ˜A1, ˜A2... ˜A7 адреса на шинах 206a-206g адреса. В одном варианте воплощения шины 206a-206g адреса электрически соединены с одним или более генераторами адреса на матрице 40 печатающей головки.

Шины 210a-210f предварительной зарядки принимают сигналы PRE1, PRE2... PRE6 предварительной зарядки и подают сигналы PRE1, PRE2... PRE6 предварительной зарядки соответствующим нагревательным группам 202a-202f. Шина 210a предварительной зарядки электрически соединена со всеми из предварительно заряженных нагревательных ячеек 120 в FG1 202a. Шина 210b предварительной зарядки электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG2 202b и так далее до шины 210f предварительной зарядки включительно, которая электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG6 202f. Каждая из шин предварительной зарядки 210a-210f электрически соединена с затвором и линией сток-исток всех транзисторов 128 предварительной зарядки в соответствующей нагревательной группе 202a-202f, и все предварительно заряженные нагревательные ячейки 120 в нагревательной группе 202a-202f электрически соединены только с одной шиной 210a-210f предварительной зарядки. Таким образом, емкостные сопротивления 126 узла из всех предварительно заряженных нагревательных ячеек 120 в нагревательной группе 202a-202f заряжаются путем подачи соответствующего сигнала PRE1, PRE2.... PRE6 предварительной зарядки соответствующей шине 210a-210f предварительной зарядки.

Шины 212a-212f выбора принимают сигналы SEL1, SEL2... SEL6 выбора и подают сигналы SEL1, SEL2... SEL6 выбора соответствующим нагревательным группам 202a-202f. Шина 212a выбора электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG1 202a. Шина 212b выбора электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG2 202b и так далее до шины 212f выбора включительно, которая электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG6 202f. Каждая шина 212a-212f выбора электрически соединена с затвором всех транзисторов 130 выбора в соответствующей нагревательной группе 202a-202f, и все предварительно заряженные нагревательные ячейки 120 в нагревательной группе 202a-202f электрически соединены только с одной шиной 212a-212f выбора.

Шины 214a-214f зажигания принимают сигналы зажигания или сигналы FIRE1, FIRE2... FIRE6 энергии и подают сигналы FIRE1, FIRE2... FIRE6 энергии соответствующим нагревательным группам 202a-202f. Шина 214a зажигания электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG1 202a. Шина 214b зажигания электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG2 202b и так далее до шины 214f зажигания включительно, которая электрически соединена со всеми предварительно заряженными нагревательными ячейками 120 в FG6 202f. Каждая из шин 214a-214f зажигания электрически соединена со всеми нагревательными резисторами 52 в соответствующей нагревательной группе 202a-202f, и все предварительно заряженные нагревательные ячейки 120 в нагревательной группе 202a-202f электрически соединены только с одной шиной 214a-214f зажигания. Шины 214a-214f зажигания электрически соединены со схемой внешнего питания соответствующими интерфейсными контактными площадками. Все предварительно заряженные нагревательные ячейки 120 в массиве 200 электрически соединены с опорной шиной 216, на которую подается опорное напряжение. Таким образом, предварительно заряженные нагревательные ячейки 120 в подгруппе ряда предварительно заряженных нагревательных ячеек 120 электрически соединены с одной и той же шиной 206a-206g адреса, шиной 210a-210f предварительной зарядки, шиной 212a-212f выбора и шиной 214a-214f зажигания.

Во время работы в одном варианте воплощения нагревательные группы 202a-202f выбираются для последовательного зажигания. FG1 202a выбирается перед FG2 202b, которая выбирается перед FG3, и так далее до FG6 202f. После FG6 202f цикл нагревательной группы начинается с FG1 202a. Однако могут использоваться другие последовательности и непоследовательные выборы.

Сигналы ˜A1, ˜A2... ˜A7 адреса циклически проходят 13 адресов подгруппы ряда перед повторением адреса подгруппы ряда. Сигналы ˜A1, ˜A2... ˜A7 адреса на шинах 206a-206g адреса установлены в один адрес подгруппы ряда в течение каждого цикла через нагревательные группы 202a-202f. Сигналы ˜A1 ˜A2... ˜A7 адреса выбирают одну подгруппу ряда в каждой из нагревательных групп 202a-202f для одного цикла через нагревательные группы 202a-202f. Для следующего цикла через нагревательные группы 202a-202f сигналы ˜A1, ˜A2... ˜A7 адреса изменяются для выбора другой подгруппы ряда в каждой из нагревательных групп 202a-202f. Это продолжается до того, когда сигналы ˜A1, ˜A2... ˜A7 адреса выбирают последнюю подгруппу ряда в нагревательных группах 202a-202f. После последней подгруппы ряда сигналы ˜A1, ˜A2... ˜A7 адреса выбирают первую подгруппу ряда, чтобы начать цикл адреса снова.

В другом аспекте одной из нагревательных групп 202a-202f управляют путем подачи сигнала PRE1, PRE2... PRE6 предварительной зарядки на шину 210a-210f предварительной зарядки одной нагревательной группы 202a-202f. Сигнал PRE1, PRE2... PRE6 предварительной зарядки определяет интервал времени предварительной зарядки или период, в течение которого емкостное сопротивление узла 126 на каждом переключателе 172 возбуждения в одной нагревательной группе 202a-202f заряжается до высокого уровня напряжения для предварительной зарядки одной нагревательной группы 202a-202f.

Сигналы ˜A1, ˜A2... ˜A7 адреса обеспечиваются на шинах 206a-206g адреса для обращения к одной подгруппе ряда в каждой из нагревательных групп 202a-202f, в том числе к одной подгруппе ряда в предварительно заряженной нагревательной группе 202a-202f. Сигналы ˜D1, ˜D2... ˜D8 данных обеспечиваются на шинах 208a-208h данных для обеспечения данных всем нагревательным группам 202a-202f, в том числе подгруппу ряда, к которой обращаются, в предварительно заряженной нагревательной группе 202a-202f.

Затем сигнал SEL1, SEL2... SEL6 выбора подается на шины 212a-212f выбора предварительно заряженной нагревательной группы 202a-202f для выбора предварительно заряженной нагревательной группы 202a-202f. Сигнал SEL1, SEL2... SEL6 выбора определяет интервал времени разряда для разряда емкостного сопротивления 126 узла на каждом переключателе 172 возбуждения в предварительно заряженной нагревательной ячейке 120, которая либо находится не в подгруппе ряда, к которому обращаются, в отобранной нагревательной группе 202a-202f, либо к ней обращаются в выбранной нагревательной группе 202a-202f, и она принимает сигнал данных ˜D1, ˜D2... ˜D8 высокого уровня. Емкостное сопротивление 126 узла не разряжается в предварительно заряженных нагревательных ячейках 120, к которым обращаются в отобранной нагревательной группе 202a-202f и которые принимают сигнал ˜D1, ˜D2... ˜D8 данных низкого уровня. Высокий уровень напряжения на емкостном сопротивлении 126 узла включает переключатель 172 возбуждения (проводит ток).

После того как переключатели 172 возбуждения в выбранной нагревательной группе 202a-202f установлены в проводящее или непроводящее состояние, импульс энергии или импульс напряжения подается на шину 214a-214f зажигания выбранной нагревательной группы 202a-202f. Предварительно заряженные нагревательные ячейки 120, которые имеют проводящий переключатель 172 возбуждения, проводят ток через нагревательный резистор 52 для нагревания чернил и эжекции чернил из соответствующего генератора 60 капель.

При последовательной работе нагревательных групп 202a-202f сигнал SEL1, SEL2... SEL6 выбора для одной нагревательной группы 202a-202f используется как сигнал PRE1, PRE2... PRE6 предварительной зарядки для следующей нагревательной группы 202a-202f. Сигнал PRE1, PRE2... PRE6 предварительной зарядки для одной нагревательной группы 202a-202f предшествует сигналу SEL1, SEL2... SEL6 выбора и сигналу FIRE1, FIRE2... FIRE6 энергии для одной нагревательной группы 202a-202f. После сигнала PRE1, PRE2... PRE6 предварительной зарядки сигналы ˜D1, ˜D2... ˜D8 данных мультиплексируются по времени и сохраняются в подгруппе ряда, к которой обращаются, одной нагревательной группы 202a-202f с помощью сигнала SEL1, SEL2... SEL6 выбора. Сигнал SEL1, SEL2... SEL6 выбора для выбранной нагревательной группы 202a-202f является также сигналом PRE1, PRE2... PRE6 предварительной зарядки для следующей нагревательной группы 202a-202f. После завершения сигнала SEL1, SEL2... SEL6 выбора для выбранной нагревательной группы 202a-202f сигнал SEL1, SEL2... SEL6 выбора подается для следующей нагревательной группы 202a-202f. Предварительно заряженные нагревательные ячейки 120 в выбранной подгруппе выстреливают или нагревают чернила на основе сохраненного сигнала ˜D1, ˜D2... ˜D8 данных по мере того, как сигнал FIRE1, FIRE2... FIRE6 энергии, содержащий импульс энергии, подается к выбранной нагревательной группе 202a-202f.

На фиг.8 представлена временная диаграмма одного варианта воплощения массива нагревательной ячейки 200. Нагревательные группы 202a-202f выбираются последовательно для подачи энергии на предварительно заряженные нагревательные ячейки 120 на основе сигналов ˜D1, ˜D2... ˜D8 данных, обозначенных 300. Сигналы ˜D1, ˜D2... ˜D8 300 данных изменяются в зависимости от сопел 302, которые должны эжектировать флюид для каждой комбинации адреса подгруппы ряда и нагревательной группы 202a-202f. Сигналы ˜A1, ˜A2... ˜A7 адреса 304 подаются на шины 206a-206g для адресации одной подгруппы ряда из каждой из нагревательных групп 202a-202f. Сигналы ˜A1, ˜A2... ˜A7 адреса в 304 устанавливаются в один адрес 306 для одного цикла через нагревательные группы 202a-202f. После того как цикл завершен, сигналы ˜A1, ˜A2... ˜A7 адреса 304 заменяются на 308 для обращения к другой подгруппе ряда из каждой из нагревательных групп 202a-202f. Сигналы ˜A1, ˜A2.... ˜A7 адреса 304 увеличиваются по подгруппам ряда для обращения к подгруппам ряда в последовательном порядке от одного до 13 и снова к одному. В других вариантах воплощения сигналы ˜A1, ˜A2... ˜A7 адреса 304 могут быть установлены для обращения к подгруппам ряда в любом подходящем порядке.

В течение цикла через нагревательные группы 202a-202f шина 212f выбора, соединенная с FG6 202f, и шина 210a предварительной зарядки, соединенная с FG1 202a, принимают сигнал 309 SEL6/PRE1, содержащий импульс 310 сигнала SEL6/PRE1. В одном варианте воплощения шина 212f выбора и шина 210a предварительной зарядки электрически соединены вместе для принятия одного и того же сигнала. В другом варианте воплощения шина 212f выбора и шина 210a предварительной зарядки электрически не соединены вместе, но принимают сходные сигналы.

Импульс сигнала SEL6/PRE1 в 310 на шине 210a предварительной зарядки предварительно заряжает все нагревательные ячейки 120 в FG1 202a. Емкостное сопротивление 126 узла для каждой из предварительно заряженных нагревательных ячеек 120 в FG1 202a заряжены до высокого уровня напряжения. Емкостное сопротивление 126 узла для предварительно заряженных нагревательных ячеек 120 в одной подгруппе 311 SG1-K ряда предварительно заряжено до высокого уровня напряжения 312. Адрес подгруппы ряда 306 выбирает подгруппу SG1-K, и сигнал данных 314 подается на транзисторы 136 данных во всех предварительно заряженных нагревательных ячейках 120 из всех нагревательных групп 202a-202f, в том числе выбранной адресом подгруппы SG1-K ряда.

Шина 212a выбора для FG1 202a и шина 210b предварительной зарядки для FG2 202b принимают сигнал 315 SEL1/PRE2, содержащий импульс 316 сигнала SEL1/PRE2. Импульс 316 сигнала SEL1/PRE2 на шине 212a выбора включает транзистор 130 выбора в каждой из предварительно заряженных нагревательных ячеек 120 в FG1 202a. Емкостное сопротивление 126 узла разряжается во всех предварительно заряженных нагревательных ячейках 120 в FG1 202a, которые не находятся в выбранной адресом подгруппе SG1-K ряда. В выбранной подгруппе SG1-K ряда 314 сохраняются данные 318 в емкостных сопротивлениях 126 узла переключателей 172 возбуждения в подгруппе SG1-K ряда для включения (проводящее состояние) либо выключения (непроводящее состояние) переключателя возбуждения.

Импульс сигнала SEL1/PRE2 316 на шине 210b предварительной зарядки предварительно заряжает все нагревательные ячейки 120 в FG2 202b. Емкостное сопротивление 126 узла для каждой из предварительно заряженных нагревательных ячеек 120 в FG2 202b заряжается до высокого уровня напряжения. Емкостное сопротивление 126 узла для предварительно заряженных нагревательных ячеек 120 в одной подгруппе 319 SG2-K ряда предварительно заряжается до высокого уровня напряжения в 320. Адрес подгруппы ряда в 306 выбирает подгруппу SG2-K, и сигнал данных 328 подается на транзисторы 136 данных во всех предварительно заряженных нагревательных ячейках 120 из всех нагревательных групп 202a-202f, в том числе выбранной адресом подгруппы SG2-K ряда.

Шина 214a зажигания принимает сигнал FIRE1 энергии 323, содержащий импульс энергии 322 для подачи энергии на нагревательные резисторы 52 в предварительно заряженных нагревательных ячейках 120, которые имеют проводящие переключатели 172 возбуждения в FG1 202a. Импульс FIRE1 энергии 322 идет на высоком уровне, пока импульс 316 сигнала SEL1/PRE2 имеет высокий уровень и пока напряжение на емкостном сопротивлении 126 узла на непроводящих переключателях 172 возбуждения активно понижается 324 на сигнале FIRE1 323 энергии. Переключение импульса 322 энергии на высокий уровень, пока напряжение на емкостных сопротивлениях 126 узла активно понижается, предотвращает непреднамеренную зарядку емкостных сопротивлений 126 узла через переключатель 172 возбуждения, когда импульс 322 энергии идет на высоком уровне. Сигнал 315 SEL1/PRE2 идет на низком уровне, и импульс 322 энергии подается на FG1 202a в течение определенного времени для нагревания чернил и эжекции чернил через сопла 34, соответствующие проводящим предварительно заряженным нагревательным ячейкам 120.

Шина 212b выбора для FG2 202b и шина 210c предварительной зарядки для FG3 202c принимают сигнал 325 SEL2/PRE3, содержащий импульс 326 сигнала SEL2/PRE3. После того как импульс 316 сигнала SEL1/PRE2 идет на низком уровне и пока импульс 322 энергии имеет высокий уровень, импульс 326 сигнала SEL2/PRE3 на шине 212b выбора включает транзистор 130 выбора в каждой из предварительно заряженных нагревательных ячеек 120 в FG2 202b. Емкостное сопротивление 126 узла разряжается на всех предварительно заряженных нагревательных ячейках 120 в FG2 202b, которые не находятся в выбранной адресом подгруппе SG2-K ряда. Сигнал данных, установленный 328 для подгруппы SG2-K, сохраняется в предварительно заряженных нагревательных ячейках 120 подгруппы SG2-K 330 для включения (проводящее состояние) либо выключения (непроводящее состояние) переключателя 172 возбуждения. Импульс сигнала SEL2/PRE3 на шине 210c предварительной зарядки предварительно заряжает все предварительно заряженные нагревательные ячейки 120 в FG3 202c.

Шина 214b зажигания принимает сигнал FIRE2 энергии 331, содержащий импульс 332 энергии для подачи энергии на нагревательные резисторы 52 в предварительно заряженных нагревательных ячейках 120 из FG2 202b, которые имеют проводящие переключатели 172 возбуждения. Импульс 332 энергии FIRE2 идет на высоком уровне, пока импульс 326 сигнала SEL2/PRE3 имеет высокий уровень 334. Импульс 326 сигнала SEL2/PRE3 идет на низком уровне, и импульс FIRE2 332 энергии остается на высоком уровне для нагревания и эжекции чернил из соответствующего генератора 60 капель.

После того как импульс 326 сигнала SEL2/PRE3 идет на низком уровне и пока импульс 332 энергии имеет высокий уровень, сигнал SEL3/PRE4 подается для выбора FG3 202c и предварительной зарядки FG4 202d. Процесс предварительной зарядки, выбора и подачи сигнала энергии, содержащего импульс энергии, продолжается до включительно FG6 202f.

Импульс сигнала SEL5/PRE6 на шине 210f предварительной зарядки предварительно заряжает все нагревательные ячейки 120 в FG6 202f. Емкостное сопротивление 126 узла для каждой из предварительно заряженных нагревательных ячеек 120 в FG6 202f заряжается до высокого уровня напряжения. Емкостные сопротивления 126 узла для предварительно заряженных нагревательных ячеек 120 в одной подгруппе ряда SG6-K 339 предварительно заряжаются до высокого уровня напряжения 341. Адрес подгруппы ряда в 306 выбирает подгруппу SG6-K, и сигнал данных 338 подается на транзисторы 136 данных во всех предварительно заряженных нагревательных ячейках 120 из всех нагревательных групп 202a-202f, в том числе выбранной подгруппы SG6-K ряда.

Шина 212f выбора для FG6 202f и шина 210a предварительной зарядки для FG1 202a принимает второй импульс сигнала SEL6/PRE1 336. Второй импульс 336 сигнала SEL6/PRE1 на шине 212f выбора включает транзистор 130 выбора в каждой из предварительно заряженных нагревательных ячеек 120 в FG6 202f. Емкостное сопротивление 126 узла разряжается во всех предварительно заряженных нагревательных ячейках 120 в FG6 202f, которые не находятся в выбранной адресом подгруппе SG6-K ряда. В выбранной адресом подгруппе SG6-K ряда данные 338 сохраняются 340 в емкостном сопротивлении 126 узла каждого переключателя 172 возбуждения для включения либо выключения переключателя возбуждения.

Сигнал SEL6/PRE1 на шине 210a предварительной зарядки предварительно заряжает емкостные сопротивления 126 узла во всех нагревательных ячейках 120 в FG1 202a, в том числе в нагревательных ячейках 120 в подгруппе SG1-K ряда 342 до высокого уровня напряжения. Нагревательные ячейки 120 в FG1 202a предварительно заряжаются, пока сигналы ˜A1, ˜A2... ˜A7 304 адреса выбирают подгруппы SG1-K, SG2-K и далее до подгруппы SG6-K ряда.

Шина 214f зажигания принимает сигнал FIRE6 энергии 343, содержащий импульс энергии 344, для подачи напряжения на нагревательные резисторы 52 в предварительно заряженных нагревательных ячейках 120, которые имеют проводящие переключатели 172 возбуждения в FG6 202f. Импульс 344 энергии идет на высоком уровне, пока импульс 336 сигнала SEL6/PRE1 имеет высокий уровень, и напряжение на емкостных сопротивлениях 126 узла на непроводящих переключателях 172 возбуждения активно понижается 346. Переключение импульса 344 энергии на высокий уровень, пока напряжение на емкостных сопротивлениях 126 узла активно понижается, предотвращает емкостное сопротивление 126 узла от непреднамеренной зарядки через переключатель 172 возбуждения, когда импульс 344 имеет высокий уровень. Импульс 336 сигнала SEL6/PRE1 идет на низком уровне, и импульс 344 энергии поддерживается на высоком уровне в течение определенного времени для нагревания чернил и эжекции чернил через сопла 34, соответствующие проводящим предварительно заряженным нагревательным ячейкам 120.

После того как импульс 336 сигнала SEL6/PRE1 имеет низкий уровень и пока импульс 344 энергии имеет высокий уровень, сигналы ˜A1, ˜A2... ˜A7 304 адреса изменяются 308 для выбора другого набора подгрупп SG1-K+1, SG2-K+1 и так далее до SG6-K+1. Шина 212a выбора для FG1 202a и шина 210b предварительной зарядки для FG2 202b принимает импульс сигнала SEL1/PRE2 348. Импульс 348 сигнала SEL1/PRE2 на шине 212a выбора включает транзистор 130 выбора в каждой из предварительно заряженных нагревательных ячеек 120 в FG1 202a. Емкостное сопротивление 126 узла разряжается во всех предварительно заряженных нагревательных ячейках 120 в FG1 202a, которые не находятся в выбранной адресом подгруппе SG1-K+1. Сигнал данных 350 для подгруппы SG1-K+1 ряда, сохраняется в предварительно заряженных нагревательных ячейках 120 из подгруппы SG1-K+1 для включения либо выключения переключателей 172 возбуждения. Импульс 348 сигнала SEL1/PRE2 на шине 210b предварительной зарядки предварительно заряжает все нагревательные ячейки 120 в FG2 202b.

Шина 214a зажигания принимает импульс 352 энергии для подачи энергии на нагревательные резисторы 52 и предварительно заряженные нагревательные ячейки 120 из FG1 202a, которые имеют проводящие переключатели 172 возбуждения. Импульс 352 энергии имеет высокий уровень, пока импульс сигнала SEL1/PRE2 348 имеет высокий уровень. Импульс 348 сигнала SEL1/PRE2 имеет низкий уровень, и импульс 352 энергии остается на высоком уровне для нагревания и эжекции чернил из соответствующих генераторов 60 капель. Процесс продолжается, пока печать не завершится.

На фиг.9 представлен вариант воплощения генератора 400 адреса в матрице 40 печатающей головки. Генератор 400 адреса содержит сдвиговый регистр 402, схему 404 направления и логическую матрицу 406. Сдвиговый регистр 402 электрически соединен со схемой 404 направления через шины 408 управления направлением. Кроме того, сдвиговый регистр 402 электрически соединен с логической матрицей 406 через шины 410a-410m вывода сдвигового регистра.

В вариантах воплощения, описанных ниже, генератор 400 адреса обеспечивает сигналы адреса нагревательным ячейкам 120. В одном варианте воплощения генератор 400 адреса принимает внешние сигналы, содержащие управляющий сигнал CSYNC и шесть синхронизирующих сигналов T1-T6, и в ответ формирует семь сигналов ˜A1, ˜A2... ˜A7 адреса. Сигналы ˜A1, ˜A2... ˜A7 адреса активны, когда они находятся на низком уровне напряжения, как обозначено предшествующей тильдой (˜) в каждом названии сигнала. В одном варианте воплощения синхронизирующие сигналы T1-T6 подаются на шины выбора (например, шины 212a-212f выбора на фиг.7). Генератор 400 адреса является одним вариантом воплощения схемы управления, выполненной с возможностью отвечать на управляющий сигнал (например, CSYNC) для инициализации последовательности (например, последовательности адресов ˜A1, ˜A2... ˜A7 в прямом или обратном порядке) для активации нагревательных ячеек 120.

Генератор 400 адреса содержит сети 412, 414 и 416 резисторных делителей, которые принимают синхронизирующие сигналы T2, T4 и T6. Сеть 412 резисторных делителей принимает синхронизирующий сигнал T2 через шину 418 синхронизирующего сигнала и делит уровень напряжения синхронизирующего сигнала T2 для формирования синхронизирующего сигнала T2 с уменьшенным уровнем напряжения на первой шине 420 сигналов оценки. Сеть 414 резисторных делителей принимает синхронизирующий сигнал T4 через шину 422 синхронизирующего сигнала и делит уровень напряжения синхронизирующего сигнала T4 для формирования синхронизирующего сигнала T4 с уменьшенным уровнем напряжения на второй шине 424 сигналов оценки. Сеть 416 резисторных делителей принимает синхронизирующий сигнал T6 через шину 426 синхронизирующего сигнала и делит уровень напряжения синхронизирующего сигнала T6 для формирования синхронизирующего сигнала T6 с уменьшенным уровнем напряжения на третьей шине 428 сигналов оценки.

Сдвиговый регистр 402 принимает управляющий сигнал CSYNC через шину 430 управляющих сигналов и сигналы направления через шины 408 сигналов направления. Кроме того, сдвиговый регистр 402 принимает синхронизирующий сигнал T1 через шину 432 синхронизирующих сигналов как первый сигнал PRE1 предварительной зарядки. Синхронизирующий сигнал T2 с уменьшенным уровнем напряжения принимается через первую шину 420 сигналов оценки как первый сигнал EVAL1 оценки. Синхронизирующий сигнал T3 принимается через шину 434 синхронизирующих сигналов как второй сигнал PRE2 предварительной зарядки, и синхронизирующий сигнал T4 с уменьшенным уровнем напряжения принимается через вторую шину 424 сигналов оценки как второй сигнал EVAL2 оценки. Сдвиговый регистр 402 подает выходные сигналы SO1-SO13 сдвигового регистра на шины 410a-410m выхода сдвигового регистра.

Сдвиговый регистр 402 включает в себя тринадцать ячеек 403a-403m сдвигового регистра, которые обеспечивают тринадцать выходных сигналов SO1-SO13 сдвигового регистра. Каждая ячейка 403a-403m сдвигового регистра обеспечивает один из выходных сигналов SO1-SO13 сдвигового регистра. Тринадцать ячеек 403a-403m сдвигового регистра электрически соединены последовательно для смещения в прямом направлении и в обратном направлении. В других вариантах воплощения сдвиговый регистр 402 может включать в себя любое подходящее количество ячеек 403 сдвигового регистра для обеспечения любого подходящего количества выходных сигналов сдвигового регистра для обеспечения любого количества желаемых сигналов адреса.

Ячейка 403a сдвигового регистра обеспечивает выходной сигнал SO1 сдвигового регистра на шине 410a выхода сдвигового регистра. Ячейка 403b сдвигового регистра обеспечивает выходной сигнал SO2 сдвигового регистра на шине 410b выхода сдвигового регистра. Ячейка 403c сдвигового регистра обеспечивает выходной сигнал SO3 сдвигового регистра на шине 410c выхода сдвигового регистра. Ячейка 403d сдвигового регистра обеспечивает выходной сигнал SO4 сдвигового регистра на шине 410d выхода сдвигового регистра. Ячейка 403e сдвигового регистра обеспечивает выходной сигнал SO5 сдвигового регистра на шине 410e выхода сдвигового регистра. Ячейка 403f сдвигового регистра обеспечивает выходной сигнал SO6 сдвигового регистра на шине 410f выхода сдвигового регистра. Ячейка 403g сдвигового регистра обеспечивает выходной сигнал SO7 сдвигового регистра на шине 410g выхода сдвигового регистра. Ячейка 403h сдвигового регистра обеспечивает выходной сигнал SO8 сдвигового регистра на шине 410h выхода сдвигового регистра. Ячейка 403i сдвигового регистра обеспечивает выходной сигнал SO9 сдвигового регистра на шине 410i выхода сдвигового регистра. Ячейка 403j сдвигового регистра обеспечивает выходной сигнал SO10 сдвигового регистра на шине 410j выхода сдвигового регистра. Ячейка сдвигового регистра 403k обеспечивает выходной сигнал SO11 сдвигового регистра на шине 410k выхода сдвигового регистра. Ячейка 403l сдвигового регистра обеспечивает выходной сигнал SO12 сдвигового регистра на шине 410l выхода сдвигового регистра, и ячейка 403m сдвигового регистра обеспечивает выходной сигнал SO13 сдвигового регистра на шине 410m выхода сдвигового регистра.

Схема 404 направления принимает управляющий сигнал CSYNC на шине 430 управляющих сигналов. Синхронизирующий сигнал T3 принимается на шине 434 синхронизирующих сигналов как четвертый сигнал PRE4 предварительной зарядки. Синхронизирующий сигнал T4 с уменьшенным уровнем напряжения принимается на шине 424 сигналов оценки как четвертый сигнал EVAL4 оценки. Синхронизирующий сигнал T5 принимается на шине 436 синхронизирующих сигналов как третий сигнал PRE3 предварительной зарядки, и синхронизирующий сигнал T6 с уменьшенным уровнем напряжения принимается на шине 428 сигналов оценки как третий сигнал EVAL3 оценки. Схема 404 направления обеспечивает сигналы направления сдвиговому регистру 402 через шину 408 сигналов направления.

Логическая матрица 406 содержит транзисторы 438a-438g предварительной зарядки шины адреса, транзисторы 440a-440m оценки адреса, транзисторы 442a и 442b предотвращения оценки и транзистор 444 предварительной зарядки логической оценки. Кроме того, логическая матрица 406 содержит пары 446, 448... 470 транзисторов адреса, которые декодируют выходные сигналы SO1-SO13 сдвигового регистра на шинах 410a-410m выхода сдвигового регистра для обеспечения сигналов ˜A1, ˜A2... ˜A7 адреса. Логическая матрица 406 содержит транзисторы 446a и 446b адреса один, транзисторы 448a и 448b адреса два, транзисторы 450a и 450b адреса три, транзисторы 452a и 452b адреса четыре, транзисторы 454a и 454b адреса пять, транзисторы 456a и 456b адреса шесть, транзисторы 458a и 458b адреса семь, транзисторы 460a и 460b адреса восемь, транзисторы 462a и 462b адреса девять, транзисторы 464a и 464b адреса десять, транзисторы 466a и 466b адреса одиннадцать, транзисторы 468a и 468b адреса двенадцать и транзисторы 470a и 470b адреса тринадцать.

Транзисторы 438a-438g предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3 и шинами 472a-472g адреса. Затвор и одна сторона линии сток-исток транзистора 438a предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438a предварительной зарядки шины адреса электрически соединена с шиной 472a адреса. Затвор и одна сторона линии сток-исток транзистора 438b предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438b предварительной зарядки шины адреса электрически соединена с шиной 472b адреса. Затвор и одна сторона линии сток-исток транзистора 438c предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438c предварительной зарядки шины адреса электрически соединена с шиной 472c адреса. Затвор и одна сторона линии сток-исток транзистора 438d предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438d предварительной зарядки шины адреса электрически соединена с шиной 472d адреса. Затвор и одна сторона линии сток-исток транзистора 438e предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438e предварительной зарядки шины адреса электрически соединена с шиной 472e адреса. Затвор и одна сторона линии сток-исток транзистора 438f предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438f предварительной зарядки шины адреса электрически соединена с шиной 472f адреса. Затвор и одна сторона линии сток-исток транзистора 438g предварительной зарядки шины адреса электрически соединены с шиной 434 сигнала T3. Другая сторона линии сток-исток транзистора 438g предварительной зарядки шины адреса электрически соединена с шиной 472g адреса. В одном варианте воплощения транзисторы 438a-438g предварительной зарядки шины адреса электрически соединены с шиной 422 сигнала T4 вместо шины 434 сигнала T3. Шина 422 сигнала T4 электрически соединена с затвором и одной стороной линии сток-исток каждого из транзисторов 438a-438g предварительной зарядки шины адреса.

Затвор каждого из транзисторов 440a-440m оценки адреса электрически соединен с шиной 474 сигнала логической оценки. Одна сторона линии сток-исток каждого из транзисторов 440a-440m оценки адреса заземлена. Кроме того, линия сток-исток транзистора 440a оценки адреса электрически соединена с шиной 476a оценки. Линия сток-исток транзистора 440b оценки адреса электрически соединена с шиной 476b оценки. Линия сток-исток транзистора 440с оценки адреса электрически соединена с шиной 476с оценки. Линия сток-исток транзистора 440d оценки адреса электрически соединена с шиной 476d оценки. Линия сток-исток транзистора 440e оценки адреса электрически соединена с шиной 476e оценки. Линия сток-исток транзистора 440f оценки адреса электрически соединена с шиной 476f оценки. Линия сток-исток транзистора 440g оценки адреса электрически соединена с шиной 476g оценки. Линия сток-исток транзистора 440h оценки адреса электрически соединена с шиной 476h оценки. Линия сток-исток транзистора 440i оценки адреса электрически соединена с шиной 476i оценки. Линия сток-исток транзистора 440j оценки адреса электрически соединена с шиной 476j оценки. Линия сток-исток транзистора 440k оценки адреса электрически соединена с шиной 476k оценки. Линия сток-исток транзистора 440l оценки адреса электрически соединена с шиной 476l оценки. Линия сток-исток транзистора 440m оценки адреса электрически соединена с шиной 476m оценки.

Затвор и одна сторона линии сток-исток транзистора 444 предварительной зарядки логической оценки электрически соединены с шиной 436 сигнала T5, и другая сторона линии сток-исток электрически соединена с шиной 474 сигнала логической оценки. Затвор транзистора 442a предотвращения оценки электрически соединен с шиной 434 сигнала T3. Линия сток-исток транзистора 442a предотвращения оценки электрически соединена с одной стороны с шиной 474 сигнала логической оценки и с другой стороны с землей 478. Затвор транзистора 442b предотвращения оценки электрически соединен с шиной 422 сигнала T4. Линия сток-исток транзистора 442b предотвращения оценки электрически соединена с одной стороны с шиной 474 сигнала логической оценки и с другой стороны с землей 478.

Линии сток-исток пар 446, 448... 470 транзисторов адреса электрически соединены между шинами 472a-472g адреса и шинами 476a-476m оценки. Затворы пар 446, 448... 470 транзисторов адреса управляются выходными сигналами SO1-SO13 сдвигового регистра через шины 410a-410m выходного сигнала сдвигового регистра.

Затворы транзисторов 446a и 446b адреса электрически соединены с шиной 410a выходного сигнала сдвигового регистра. Сток-исток транзистора 446a адреса один электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476a оценки. Сток-исток транзистора 446b адреса один электрически соединен на одной стороне с шиной 472b адреса и с другой стороны с шиной 476a оценки. Выходной сигнал SO1 сдвигового регистра с высоким уровнем на шине 410a выходного сигнала сдвигового регистра включает транзисторы 446a и 446b адреса один, в то время как транзистор 440a оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения на шине 474 сигнала логической оценки. Транзистор 446a адреса один и транзистор 440a оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 446b адреса один и транзистор 440a оценки адреса проводят ток для активного снижения напряжения на шине 472b адреса до низкого уровня.

Затворы транзисторов 448a и 448b адреса два электрически соединены с шиной 410b выходного сигнала сдвигового регистра. Сток-исток транзистора 448a адреса два электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476b оценки. Сток-исток транзистора 448b адреса два электрически соединен на одной стороне с шиной 472c адреса и с другой стороны с шиной 476b оценки. Выходной сигнал SO2 сдвигового регистра с высоким уровнем на шине 410b выходного сигнала сдвигового регистра включает транзисторы 448a и 448b адреса два, в то время как транзистор 440b оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения на шине 474 сигнала логической оценки. Транзистор 448a адреса два и транзистор 440b оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 448b адреса два и транзистор 440b оценки адреса проводят ток для активного снижения напряжения на шине 472c адреса до низкого уровня.

Затворы транзисторов 450a и 450b адреса три электрически соединены с шиной 410c выходного сигнала сдвигового регистра. Сток-исток транзистора 450a адреса три электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476c оценки. Сток-исток транзистора 450b адреса один электрически соединен на одной стороне с шиной 472d адреса и с другой стороны с шиной 476c оценки. Выходной сигнал SO3 сдвигового регистра с высоким уровнем на шине 410c выходного сигнала сдвигового регистра включает транзисторы 450a и 450b адреса три, в то время как транзистор 440c оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения на шине 474 сигнала логической оценки. Транзистор 450a адреса три и транзистор 440c оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 450b адреса три и транзистор 440c оценки адреса проводят ток для активного снижения напряжения на шине 472d адреса до низкого уровня.

Затворы транзисторов 452a и 452b адреса четыре электрически соединены с шиной 410d выходного сигнала сдвигового регистра. Сток-исток транзистора 452a адреса четыре электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476d оценки. Сток-исток транзистора 452b адреса четыре электрически соединен на одной стороне с шиной 472e адреса и с другой стороны с шиной 476d оценки. Выходной сигнал SO4 сдвигового регистра с высоким уровнем на шине 410d выходного сигнала сдвигового регистра включает транзисторы 452a и 452b адреса четыре, в то время как транзистор 440d оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения на шине 474 сигнала логической оценки. Транзистор 452a адреса четыре и транзистор 440d оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 452b адреса четыре и транзистор 440d оценки адреса проводят ток для активного снижения напряжения на шине 472e адреса до низкого уровня.

Затворы транзисторов 454a и 454b адреса пять электрически соединены с шиной 410e выходного сигнала сдвигового регистра. Сток-исток транзистора 454a адреса пять электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476e оценки. Сток-исток транзистора 454b адреса пять электрически соединен на одной стороне с шиной 472f адреса и с другой стороны с шиной 476e оценки. Выходной сигнал SO5 сдвигового регистра с высоким уровнем на шине 410e выходного сигнала сдвигового регистра включает транзисторы 454a и 454b адреса пять, в то время как транзистор 440e оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения. Транзистор 454a адреса пять и транзистор 440e оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 454b адреса пять и транзистор 440e оценки адреса проводят ток для активного снижения напряжения на шине 472f адреса до низкого уровня.

Затворы транзисторов 456a и 456b адреса шесть электрически соединены с шиной 410f выходного сигнала сдвигового регистра. Сток-исток транзистора 456a адреса шесть электрически соединен с одной стороны с шиной 472a адреса и с другой стороны с шиной 476f оценки. Сток-исток транзистора 456b адреса шесть электрически соединен на одной стороне с шиной 472g адреса и с другой стороны с шиной 476f оценки. Выходной сигнал SO6 сдвигового регистра с высоким уровнем на шине 410f выходного сигнала сдвигового регистра включает транзисторы 456a и 456b адреса шесть, в то время как транзистор 440f оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения. Транзистор 456a адреса шесть и транзистор 440f оценки адреса проводят ток для активного снижения напряжения на шине 472a адреса до низкого уровня. Транзистор 456b адреса шесть и транзистор 440f оценки адреса проводят ток для активного снижения напряжения на шине 472g адреса до низкого уровня.

Затворы транзисторов 458a и 458b адреса семь электрически соединены с шиной 410g выходного сигнала сдвигового регистра. Сток-исток транзистора 458a адреса семь электрически соединен с одной стороны с шиной 472c адреса и с другой стороны с шиной 476g оценки. Сток-исток транзистора 458b адреса семь электрически соединен на одной стороне с шиной 472c адреса и с другой стороны с шиной 476g оценки. Выходной сигнал SO7 сдвигового регистра с высоким уровнем на шине 410g выходного сигнала сдвигового регистра включает транзисторы 458a и 458b адреса семь, в то время как транзистор 440g оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения. Транзистор 458a адреса семь и транзистор 440g оценки адреса проводят ток для активного снижения напряжения на шине 472b адреса до низкого уровня. Транзистор 458b адреса семь и транзистор 440g оценки адреса проводят ток для активного снижения напряжения на шине 472c адреса до низкого уровня.

Затворы транзисторов 460a и 460b адреса восемь электрически соединены с шиной 410h выходного сигнала сдвигового регистра. Сток-исток транзистора 460a адреса восемь электрически соединен с одной стороны с шиной 472b адреса и с другой стороны с шиной 476h оценки. Сток-исток транзистора 460b адреса восемь электрически соединен на одной стороне с шиной 472d адреса и с другой стороны с шиной 476h оценки. Выходной сигнал SO8 сдвигового регистра с высоким уровнем на шине 410h выходного сигнала сдвигового регистра включает транзисторы 460a и 460b адреса восемь, в то время как транзистор 440h оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения. Транзистор 460a адреса восемь и транзистор 440h оценки адреса проводят ток для активного снижения напряжения на шине 472b адреса до низкого уровня. Транзистор 460b адреса восемь и транзистор 440h оценки адреса проводят ток для активного снижения напряжения на шине 472d адреса до низкого уровня.

Затворы транзисторов 462a и 462b адреса девять электрически соединены с шиной 410i выходного сигнала сдвигового регистра. Сток-исток транзистора 462a адреса девять электрически соединен с одной стороны с шиной 472b адреса и с другой стороны с шиной 476i оценки. Сток-исток транзистора 462b адреса девять электрически соединен на одной стороне с шиной 472e адреса и с другой стороны с шиной 476i оценки. Выходной сигнал SO9 сдвигового регистра с высоким уровнем на шине 410i выходного сигнала сдвигового регистра включает транзисторы 462a и 462b адреса девять, в то время как транзистор 440i оценки адреса включается сигналом LEVAL оценки с высоким уровнем напряжения. Транзистор 462a адреса девять и транзистор 440i оценки адреса проводят ток для активного снижения напряжения на шине 472b адреса до низкого уровня. Транзистор 462b адреса девять и транзистор 440i оценки адреса проводят ток для активного снижения напряжения на шине 472e адреса до низкого уровня.