Изобретение относится к области железнодорожной автоматики и может быть использовано в устройствах многозначной автоматической локомотивной сигнализации (АЛС-ЕН) для обеспечения приема кодовых сигналов АЛС-ЕН.

В качестве ближайшего аналога заявляемого технического решения выбран приемник сигналов АЛС-ЕН, содержащий входной канал, демодулятор и декодер [Системы железнодорожной автоматики и телемеханики. Под ред. Ю.А.Кравцова. М., Транспорт, 1996 г. С.168-180]. Известное устройство работает следующим образом. На вход приемника поступают сигналы АЛС-ЕН, представляющие собой кодовые сигналы с двукратной фазоразностной модуляцией (ДФРМ). После фильтрации сигналы АЛС-ЕН поступают на усилитель-ограничитель, который формирует из них прямоугольные импульсы определенного уровня, поступающие на вход демодулятора. В демодуляторе входной сигнал дифференцируется и формируется последовательность фронтов несущего колебания, а затем - последовательность фронтов данных, временное положение которых соответствует границам посылок информационного сигнала. Схема тактовой синхронизации вырабатывает стробирующий сигнал, в соответствии с которым отсчитывается разность фаз двух соседних элементарных посылок в момент максимального отношения сигнал-помеха. Выделитель измерительного фронта перемножает входной сигнал, представленный последовательностью фронтов несущего колебания, с опорным сигналом, в качестве которого используется стробирующий сигнал. На выходе выделителя измерительного фронта имеет место последовательность измерительных фронтов, несущих информацию о переданной разности фаз. Определитель разности фаз (решающее устройство) преобразует временной интервал в последовательность двоичных символов по двум подканалам. Таймер формирует тактовые сигналы, обеспечивающие синхронную работу всех функциональных узлов демодулятора и декодера.

Недостаток известного приемника сигналов АЛС-ЕН - недостаточная помехоустойчивость.

Задача, решаемая изобретением, - повышение помехоустойчивости приемника сигналов АЛС-ЕН.

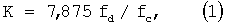

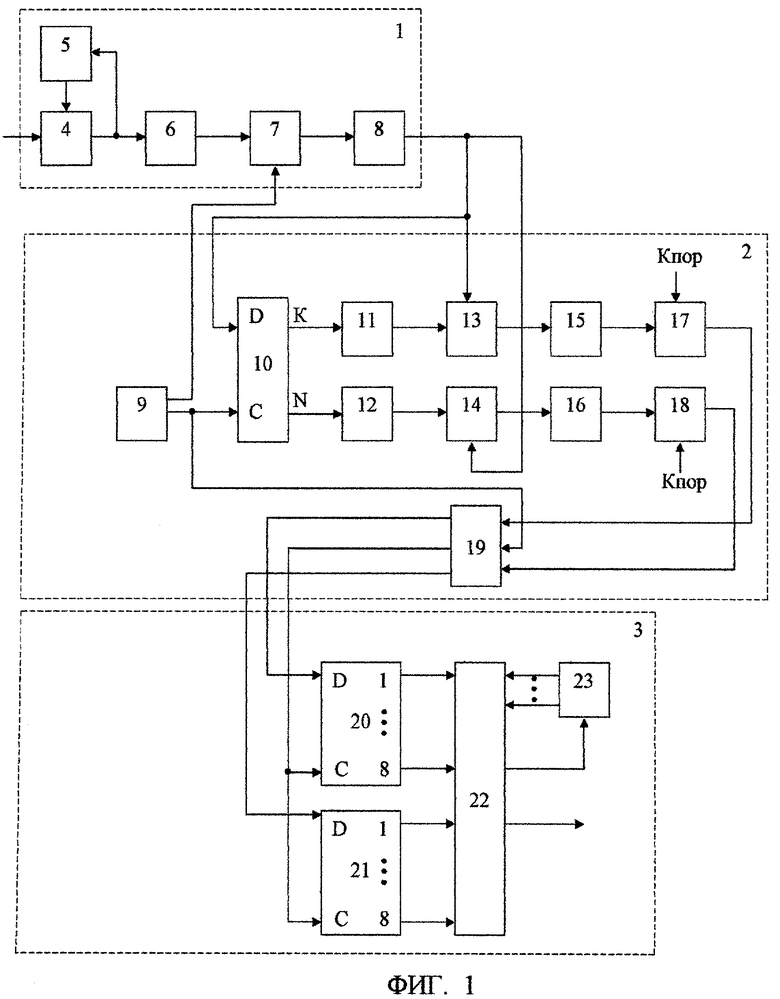

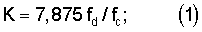

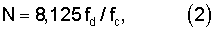

Указанная задача решается тем, что в приемнике сигналов многозначной автоматической локомотивной сигнализации (АЛС-ЕН), включающем входной канал с устройством фильтрации, демодулятор, содержащий генератор тактовых сигналов, и декодер, устройство фильтрации выполнено в виде фильтра нижних частот, соединенного выходом с входом аналого-цифрового преобразователя, тактовый вход которого подключен к первому выходу генератора тактовых сигналов, и цифрового полосового фильтра, вход которого связан с выходом аналого-цифрового преобразователя; демодулятор содержит линию задержки цифровых кодов, вход данных которой подключен к выходу цифрового полосового фильтра, а тактовый вход подсоединен ко второму выходу генератора тактового сигнала, первый и второй фазовращатели, входы которых соединены с К-ым и N-ым выходами линии задержки, порядковые номера которых определяются по формуле

где fd - частота дискретизации аналого-цифрового преобразователя, fc - частота несущей сигнала АЛС-ЕН, причем в качестве значений К и N выбираются целые части выражений (1) и (2); выходы первого и второго фазовращателей подключены, соответственно, к первым входам первого и второго цифровых перемножителей, вторые входы которых соединены с выходом цифрового полосового фильтра; первый и второй цифровые фильтры нижних частот, входы которых подключены, соответственно, к выходам первого и второго цифровых перемножителей, а выходы соединены с входами первого и второго цифровых компараторов, и блок преобразования, содержащий первый и второй логические элементы «НЕ», первый, второй и третий логические элементы «2 И», первый и второй триггеры, таймер, логический элемент «2 ИЛИ» и элемент задержки, при этом выход первого цифрового компаратора соединен с входом первого логического элемента «НЕ» и первым входом третьего логического элемента «2 И», являющихся первым входом блока преобразования; выход второго цифрового компаратора соединен с входом второго логического элемента «НЕ» и вторым входом третьего логического элемента «2 И», являющихся вторым входом блока преобразования, второй выход генератора тактовых сигналов подсоединен к первым входам первого и второго логического элемента «2 И», являющихся тактовым входом блока преобразования, выход первого логического элемента «НЕ» подключен к входу данных первого триггера, тактовый вход которого соединен с выходом первого логического элемента «2 И»; выход второго логического элемента «НЕ» подключен к входу данных второго триггера, тактовый вход которого соединен с выходом второго логического элемента «2 И», выходы данных первого и второго триггеров являются, соответственно, первым и вторым выходом блока преобразования, а инверсные выходы первого и второго триггеров подсоединены, соответственно, ко вторым входам первого и второго логического элемента «2 И», выход третьего логического элемента «2 И» подключен к входу таймера и второму входу логического элемента «2 ИЛИ», первый вход которого соединен с выходом таймера, а выход логического элемента «2 ИЛИ», являющийся третьим выходом блока преобразования, связан с входом элемента задержки, выход которого подключен к входам установки логического нуля первого и второго триггеров; декодер содержит первый и второй регистры сдвига, блок сравнения и постоянное запоминающее устройство, при этом входы данных первого и второго регистров сдвига подсоединены, соответственно, к первому и второму выходам блока преобразования; тактовые входы регистров сдвига подключены к третьему выходу блока преобразования; выходы регистров сдвига подсоединены к первым информационным входам блока сравнения, первый выход которого связан с входом постоянного запоминающего устройства, выходы которого подключены ко вторым информационным входам блока сравнения, второй выход которого является выходом приемника.

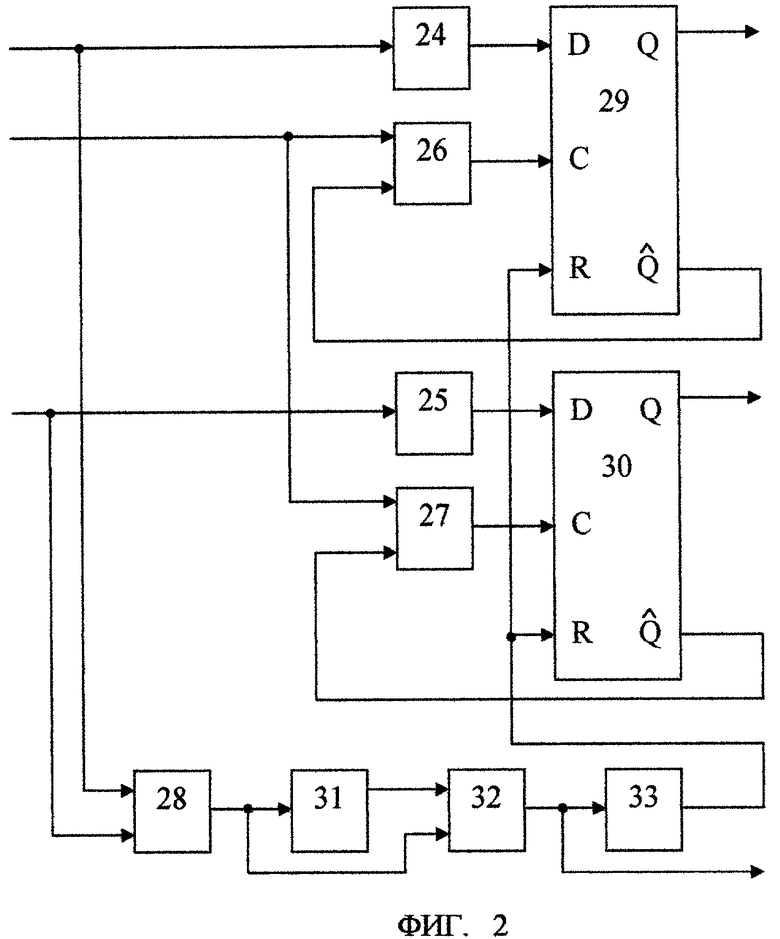

На фиг.1 показана функциональная схема заявляемого приемника, на фиг.2 приведена функциональная схема блока преобразования.

Приемник сигналов АЛС-ЕН включает входной канал 1, демодулятор 2 и декодер 3. В состав входного канала 1 входят усилитель 4, первый вход которого является входом приемника, а выход соединен с входами блока автоматической регулировки усиления (АРУ) 5 и фильтра нижних частот (ФНЧ) 6, выход которого подключен к входу аналого-цифрового преобразователя (АЦП) 7, выход которого связан с входом цифрового полосового фильтра (ЦПФ) 8, при этом выход блока АРУ 5 соединен со вторым входом усилителя 4. В состав демодулятора 2 входят генератор тактовых сигналов 9, первый выход которого подключен к тактовому входу АЦП 7, линия задержки цифровых кодов 10, выполненная в виде набора регистров сдвига, число которых равно числу двоичных разрядов данных, поступающих с выхода ЦПФ 8, при этом вход данных D линии задержки 10 подключен к выходу ЦПФ 8, а вход тактового сигнала С соединен со вторым выходом генератора 9, первый и второй фазовращатели 11 и 12, входы которых подсоединены, соответственно, к К-ому и N-ому выходам линии задержки 10, причем N-ый выход является последним (по порядку) выходом линии задержки 10, выходы фазовращателей 11 и 12 подключены, соответственно, к первым входам первого и второго цифровых перемножителей 13 и 14, вторые входы которых соединены с выходом ЦПФ 8; первый и второй цифровые фильтры нижних частот (ЦФНЧ) 15 и 16, соединенные своими входами с выходами цифровых перемножителей 13 и 14, соответственно, а выходами - с входами первого и второго цифровых компараторов 17 и 18; блок преобразования 19, первый и второй входы которого подключены, соответственно, к выходам компараторов 17 и 18, а тактовый вход связан со вторым выходом генератора 9. Декодер 3 включает первый и второй 8-разрядные регистры сдвига 20 и 21, блок сравнения 22 и постоянное запоминающее устройство (ПЗУ) 23, при этом вход данных D регистра 20 соединен с первым выходом блока 19, вход данных D регистра 21 соединен со вторым выходом блока 19, а входы тактового сигнала С регистров 20 и 21 подключены к третьему выходу блока 19; выходы регистров 20 и 21 связаны с первыми информационными входами блока сравнения 22, первый выход которого связан с входом ПЗУ 23, выходы которого подключены ко вторым информационным входам блока сравнения 22, второй выход которого является выходом приемника.

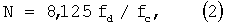

Блок преобразования 19 содержит первый и второй логические элементы «НЕ» 24 и 25, первый, второй и третий логические элементы «2 И» 26, 27 и 28, первый и второй триггеры 29 и 30, таймер 31, логический элемент «2 ИЛИ» 32 и элемент задержки 33. Выход компаратора 17 соединен с входом первого логического элемента «НЕ» 24 и первым входом третьего логического элемента «2 И» 28, являющихся первым входом блока 19; выход компаратора 18 соединен с входом второго логического элемента «НЕ» 25 и вторым входом третьего логического элемента «2 И» 28, являющихся вторым входом блока 19. Второй выход генератора 9 подсоединен к первым входам первого и второго логического элемента «2 И» 26 и 27, являющихся тактовым входом блока 19. Выход первого логического элемента «НЕ» 24 подключен к входу данных D1 триггера 29, тактовый вход которого соединен с выходом первого логического элемента «2 И» 26; выход второго логического элемента «НЕ» 25 подключен к входу данных D триггера 30, тактовый вход которого соединен с выходом второго логического элемента «2 И» 27. Выходы данных Q триггеров 29 и 30, соответственно, являются первым и вторым выходом блока 19, а инверсные выходы  триггеров 29 и 30, соответственно, подсоединены ко вторым входам первого и второго логических элементов «2 И» 26 и 27. Выход третьего логического элемента «2 И» 28 подключен к входу таймера 31 и второму входу логического элемента «2 ИЛИ» 32, первый вход которого соединен с выходом таймера 31. Выход логического элемента «2 ИЛИ» 32, являющийся третьим выходом блока 19, связан с входом элемента задержки 33, выход которого подключен к входам установки логического нуля R триггеров 29 и 30, соответственно.

триггеров 29 и 30, соответственно, подсоединены ко вторым входам первого и второго логических элементов «2 И» 26 и 27. Выход третьего логического элемента «2 И» 28 подключен к входу таймера 31 и второму входу логического элемента «2 ИЛИ» 32, первый вход которого соединен с выходом таймера 31. Выход логического элемента «2 ИЛИ» 32, являющийся третьим выходом блока 19, связан с входом элемента задержки 33, выход которого подключен к входам установки логического нуля R триггеров 29 и 30, соответственно.

Приемник сигналов АЛС-ЕН работает следующим образом. Кодовый сигнал АЛС-ЕН с двукратной фазоразностной модуляцией поступает во входной канал 1 приемника, где производится его усиление, преобразование в цифровую форму и фильтрация. С выхода ЦПФ 8 сигнал в цифровой форме поступает на вход данных линии задержки 10 и на вторые входы цифровых перемножителей 13 и 14. На тактовый вход линии задержки 10 поступает сигнал со второго выхода генератора тактовых сигналов 9, частота которого равна частоте дискретизации АЦП 7. Задержанный по времени сигнал АЛС-ЕН относительно выходного сигнала ЦПФ 8 присутствует на К-ом и N-ом выходах линии задержки 10. Порядковые номера К-ого и N-ого выходов линии задержки 10 выбираются таким образом, чтобы сигналы, снимаемые с этих выходов, были задержаны относительно сигнала с выхода ЦПФ 8 на 7,875 fd/fc и 8,125 fd/fc, соответственно (т.е. на (8-1/8) и (8+1/8) периодов несущей сигнала АЛС-ЕН), где fd - частота дискретизации АЦП 7, fc - частота несущей сигнала АЛС-ЕН. Поскольку К и N могут быть только целыми числами, для определения порядковых номеров выходов линии задержки 10 берутся целые части выражений 7,875 fd/fc и 8,125 fd/fc.

Фазовращатели 11 и 12 обеспечивают относительное фазовое рассогласование между их выходными сигналами, равное ±45°. В цифровых перемножителях 13 и 14 осуществляется перемножение незадержанного сигнала АЛС-ЕН, поступающего с выхода ЦПФ 8, с выходными сигналами фазовращателей 11 и 12. С выходов перемножителей 13 и 14 сигналы поступают на входы цифровых ФНЧ 15 и 16, осуществляющих фильтрацию сигнала. При этом с момента скачкообразного изменения фазы несущего сигнала АЛС-ЕН Δϕ, в течение 8-и периодов несущей сигнала АЛС-ЕН на выходе ЦФНЧ 15 сигнал будет иметь отрицательное значение, когда Δϕ=-90° и +180°, а сигнал на выходе ЦФНЧ 16 будет иметь отрицательное значение при Δϕ=+90° и 180°. Во всех остальных случаях сигналы на выходах ЦФНЧ 15 и 16 будут иметь положительное значение.

В момент изменения полярности выходного сигнала ЦФНЧ 15 и 16 из положительного состояния в отрицательное битовый сигнал на выходе компараторов 17 и 18 изменяет свое состояние с логической «1» на логический «0». Опорный (пороговый) уровень компараторов - Кпор равен нулю.

С выходов компараторов 17 и 18 сигналы подаются, соответственно, на первый и второй входы блока преобразования 19. Блок преобразования 19 работает следующим образом.

Исходное состояние блока 19 (при наличии на выходах компараторов 17 и 18 логической «1»):

- сигналы на входах данных триггеров 29 и 30 равны логическому «0»;

- сигнал на выходе логического элемента «2 И» 28 равен логической «1»;

- сигнал на входах установки логического «0» R триггеров 29 и 30 равен логической «1»;

- сигнал на выходах данных D триггеров 29 и 30 равен логическому «0»;

- сигналы на инверсных выходах триггеров 29 и 30 равны логической «1»;

- тактовый сигнал с выхода генератора 9 поддерживает триггеры 29 и 30 в исходном состоянии.

При появлении на выходе компаратора 17 сигнала логического «0» логический элемент «НЕ» 24 устанавливает на входе данных триггера 29 логическую «1». На выходе логического элемента «2 И» 28 установится сигнал логического «0», который, пройдя через логический элемент «2 ИЛИ» 32 и элемент задержки 33, установит на входах установки логического нуля триггеров 29 и 30 логический «0», снимая тем самым запрет на изменение состояния триггеров 29 и 30.

Первый тактовый сигнал с генератора 9, пришедший после установки на входе установки логического нуля триггера 29 логического «0», пройдя через логический элемент «2 И» 26, установит триггер 29 в единичное состояние, в результате чего на выходе данных триггера 29 появится логическая «1», а на инверсном выходе триггера 29 - логический «0». Логический «0» на инверсном выходе триггера 29 запретит прохождение тактовых сигналов через логический элемент «2 И» 26.

При появлении сигнала логического «0» на выходе компаратора 18 логический элемент «НЕ» 25 устанавливает на входе данных триггера 30 логическую «1». На выходе логического элемента «2 И» 28 установится сигнал логического «0», который, пройдя через логический элемент «2 ИЛИ» 32 и элемент задержки 33, установит на входах установки логического нуля триггеров 29 и 39 логический «0», снимая запрет на изменение состояния триггеров 29 и 30.

Первый тактовый сигнал, пришедший после установки на входе установки логического нуля триггера 30 логического «0», пройдя через логический элемент «2 И» 27, установит триггер 30 в единичное состояние, в результате чего на выходе данных триггера 30 установится логическая «1», a на инверсном выходе триггера 30 - логический «0». Логический «0» на инверсном выходе триггера 30 запретит прохождение тактовых сигналов через логический элемент «2 И» 29.

При появлении на выходах компараторов 17 и 18 сигнала логической «1» на выходе логического элемента «2 И» 28 сигнал логической «0» изменится на сигнал логической «1». В результате формируется сигнал, который является выходным синхросигналом блока 19, снимаемым с его третьего выхода, и который перезапускает и сбрасывает таймер 31.

Когда на выходах компараторов 17 и 18 установлены сигналы логической «1», триггеры 29 и 30 находятся в исходном состоянии. Таймер 31 срабатывает спустя время, равное 16-и периодам несущей сигнала АЛС-ЕН после последнего положительного фронта на выходе логической схемы «2 И» 28 или от последнего срабатывания таймера 31, и через схему «2 ИЛИ» 32 установит на третьем выходе блока 19 выходной синхросигнал блока 19.

Дальнейшая работа приемника осуществляется следующим образом. Логические сигнала с первого и второго выходов блока 19 (с выходов данных триггеров 29 и 30) записываются в ячейки памяти сдвиговых регистров 20 и 21. Синхронизация записи осуществляется с помощью синхросигнала, поступающего с третьего выхода блока 19 на входы тактового сигнала регистров 20 и 21.

В ПЗУ 23 хранится банк кодов эталонных сигналов АЛС-ЕН, содержащий информацию о кодограммах сигналов АЛС-ЕН модифицированных кодов Бауэра [В.И.Сороко, Е.А.Розенберг. Аппаратура железнодорожной автоматики и телемеханики. Справочник, Книга 2. М., НПФ «Планета», 2000 г., С.794-797]. По запросам, поступающим с первого выхода блока сравнения 22 на вход ПЗУ 23, ПЗУ 23 поочередно выдает на вторые информационные выходы блока сравнения 22 коды эталонных сигналов.

Блок сравнения 22 анализирует поступающие с выходов регистров 20 и 21 на его первые информационные входы сигналы (принятые коды) и сравнивает их с кодами эталонных сигналов из банка кодов эталонных сигналов АЛС-ЕН. В блоке 22 по результатам сравнения принимается решение о коде сигнала АЛС-ЕН и достоверности процедуры его декодирования. Выходной сигнал блока 22 - код сигнала АЛС-ЕН.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИГНАЛОВ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ | 2004 |

|

RU2278795C2 |

| СИСТЕМА АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ АЛС | 2023 |

|

RU2815588C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМНИК С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ ДЛЯ ПРИЕМА КВАДРАТУРНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПОВЫШЕННОЙ СТРУКТУРНОЙ СКРЫТНОСТИ | 2013 |

|

RU2544767C1 |

| Приемник многочастотных сигналов | 1987 |

|

SU1478368A1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1984 |

|

SU1252964A1 |

| Устройство для передачи информации с вращающегося объекта | 1986 |

|

SU1334173A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ ЛИНИИ СВЯЗИ КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2304847C2 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ ВЗАИМНОГО ВЛИЯНИЯ СИГНАЛОВ | 2022 |

|

RU2785898C1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

Изобретение относится к области железнодорожной автоматики и может быть использовано в устройствах многозначной автоматической локомотивной сигнализации (АЛС-ЕН) для обеспечения приема кодовых сигналов АЛС-ЕН. Приемник сигналов многозначной автоматической локомотивной сигнализации (АЛС-ЕН) включает входной канал (1), содержащий усилитель (4), блок автоматической регулировки усиления (5), фильтр нижних частот (6), аналого-цифровой преобразователь и цифровой полосовой фильтр (8), демодулятор (2), содержащий генератор тактовых сигналов (9), линию задержки (10), фазовращатели (11) и (12), фазовые детекторы (13) и (14), цифровые фильтры нижних частот (15) и (16), цифровые компараторы (17) и (18), блок преобразования (19), и декодер (3), содержащий регистры сдвига (20) и (21), блок сравнения (22) и постоянное запоминающее устройство (23). В состав блока преобразования (19) входят логические элементы (24) и (25), логические элементы «2 И» (26), (27) и (28), триггеры (29) и (30), таймер (31), логический элемент «2 ИЛИ» (32) и элемент задержки (33). Техническим результатом изобретения является повышение помехозащищенности приемника сигналов АЛС-ЕН. 2 ил.

Приемник сигналов многозначной автоматической локомотивной сигнализации (АЛС-ЕН), включающий входной канал с устройством фильтрации, демодулятор, содержащий генератор тактовых сигналов, и декодер, отличающийся тем, что устройство фильтрации выполнено в виде фильтра нижних частот, соединенного выходом с входом аналого-цифрового преобразователя, тактовый вход которого подключен к первому выходу генератора тактовых сигналов, и цифрового полосового фильтра, вход которого связан с выходом аналого-цифрового преобразователя; демодулятор содержит линию задержки цифровых кодов, вход данных которой подключен к выходу цифрового полосового фильтра, а тактовый вход подсоединен ко второму выходу генератора тактового сигнала, первый и второй фазовращатели, входы которых соединены с К-м и N-м выходами линии задержки, порядковые номера которых определяются по формуле

где fd - частота дискретизации аналого-цифрового преобразователя, fc - частота несущей сигнала АЛС-ЕН, причем в качестве значений К и N выбираются целые части выражений (1) и (2),

выходы первого и второго фазовращателей подключены соответственно к первым входам первого и второго цифровых перемножителей, вторые входы которых соединены с выходом цифрового полосового фильтра; первый и второй цифровые фильтры нижних частот, входы которых подключены соответственно к выходам первого и второго цифровых перемножителей, а выходы соединены с входами первого и второго цифровых компараторов, и блок преобразования, содержащий первый и второй логические элементы «НЕ», первый, второй и третий логические элементы «2И», первый и второй триггеры, таймер, логический элемент «2ИЛИ» и элемент задержки, при этом выход первого цифрового компаратора соединен с входом первого логического элемента «НЕ» и первым входом третьего логического элемента «2И», являющихся первым входом блока преобразования; выход второго цифрового компаратора соединен с входом второго логического элемента «НЕ» и вторым входом третьего логического элемента «2И», являющихся вторым входом блока преобразования, второй выход генератора тактовых сигналов подсоединен к первым входам первого и второго логических элементов «2И», являющихся тактовым входом блока преобразования, выход первого логического элемента «НЕ» подключен к входу данных первого триггера, тактовый вход которого соединен с выходом первого логического элемента «2И»; выход второго логического элемента «НЕ» подключен к входу данных второго триггера, тактовый вход которого соединен с выходом второго логического элемента «2И», выходы данных первого и второго триггеров являются соответственно первым и вторым выходами блока преобразования, а инверсные выходы первого и второго триггеров подсоединены соответственно ко вторым входам первого и второго логических элементов «2И», выход третьего логического элемента «2И» подключен к входу таймера и второму входу логического элемента «2ИЛИ», первый вход которого соединен с выходом таймера, а выход логического элемента «2ИЛИ», являющийся третьим выходом блока преобразования, связан с входом элемента задержки, выход которого подключен к входам установки логического нуля первого и второго триггеров; декодер содержит первый и второй регистры сдвига, блок сравнения и постоянное запоминающее устройство, при этом входы данных первого и второго регистров сдвига подсоединены соответственно к первому и второму выходам блока преобразования; тактовые входы регистров сдвига подключены к третьему выходу блока преобразования; выходы регистров сдвига подсоединены к первым информационным входам блока сравнения, первый выход которого связан с входом постоянного запоминающего устройства, выходы которого подключены ко вторым информационным входам блока сравнения, второй выход которого является выходом приемника.

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИГНАЛОВ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ | 2004 |

|

RU2278795C2 |

| Следящее устройство | 1936 |

|

SU59010A1 |

| Приемник для устройств железнодорожной автоматики | 1990 |

|

SU1787855A1 |

| Устройство для автоматической локомотивной сигнализации | 1990 |

|

SU1776596A1 |

Авторы

Даты

2009-02-27—Публикация

2007-04-09—Подача