Зь 1

00

со

ОЭ

00

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| УСТРОЙСТВО ДИСКРЕТНО-ВЕСОВОГО СЛОЖЕНИЯ РАЗНЕСЕННЫХ СИГНАЛОВ | 2002 |

|

RU2220504C1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| СПОСОБ ФОРМИРОВАНИЯ КВАДРАТУРНЫХ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2168281C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Цифровой анализатор энергетического спектра | 1978 |

|

SU769443A1 |

Изобретение относится к радиосвязи и может быть использовано в системах передачи дискретной информации. Цель изобретения - повышение помехоустойчивости. Устройство содержит анализатор 1 энергетического спектра, коммутатор 2, накопитель 5, логический блок 6, блок 10 управления, г-р 11 тактовых импульсов. Поставленная цель достигается введением в устройство решающего блока 3, двух компенсаторов 4,9, блока 7 выбора данных, блока 8 вычисления ошибки синхронизации, формирователя 12 управляющего сигнала, коммутатора 13 и демодулятора 14. Компенсатор 4 предназначен для подавления узкополосных помех. Блок 7 из всех сформированных оценок разностей выбирает ту, величина которой пропорциональна задержке сигнала. По вычисленному значению ошибки синхронизации в блоке 8 компенсатор 9 осуществляет задержку импульсов г-ра 11, поступающих на компенсатор 9 через формирователь 12, чем компенсируется ошибка по задержке. 11 з.п. ф-лы, 12 ил.

Фиг.1

Изобретение относится к радиосвязи и может быть использовано в системах передачи дискретной информации.

Цель изобретения - повышение помехоустойчивости .

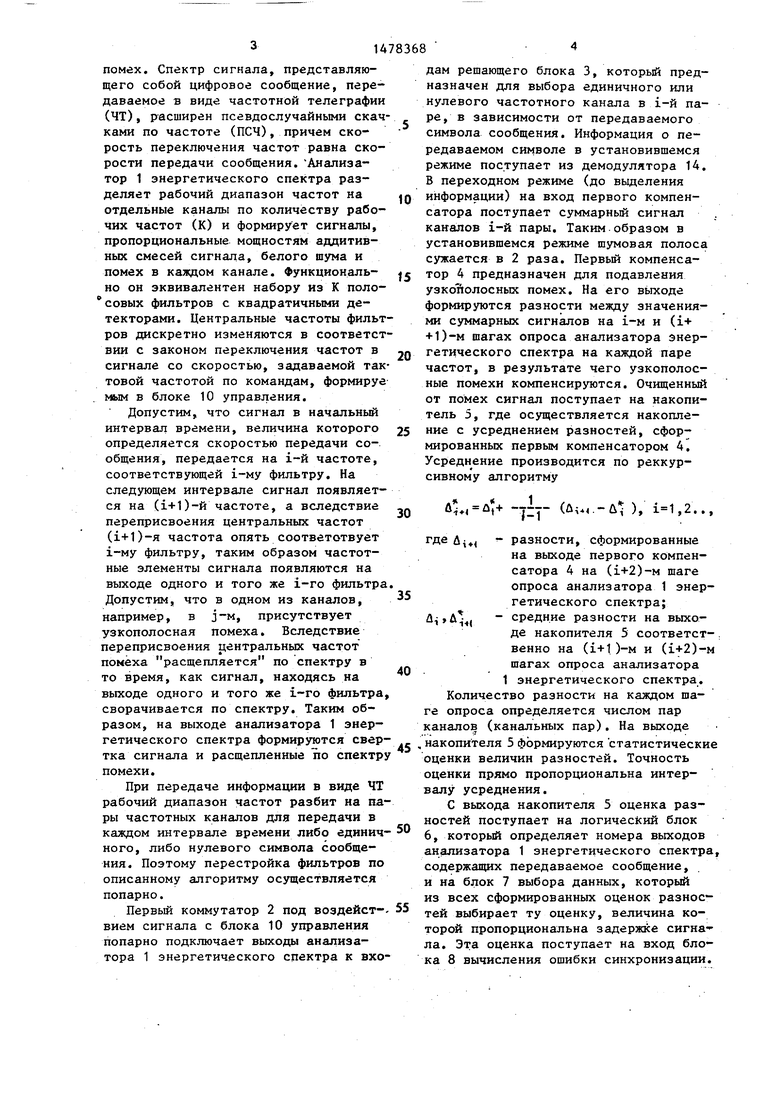

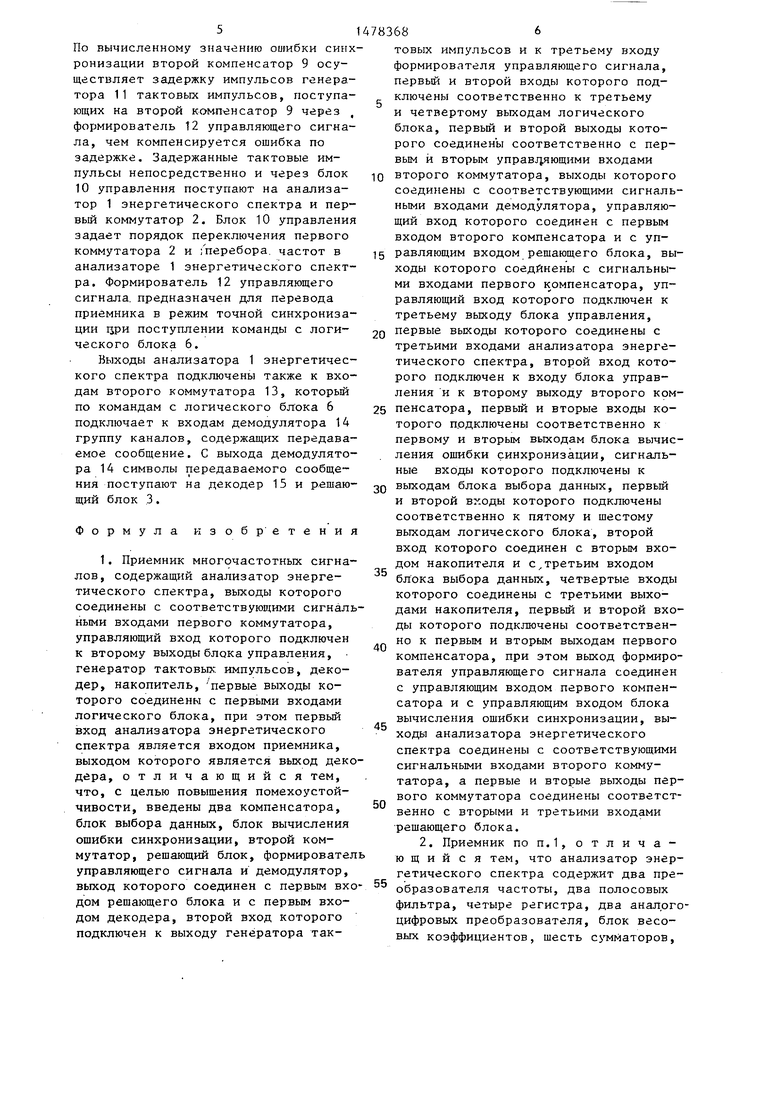

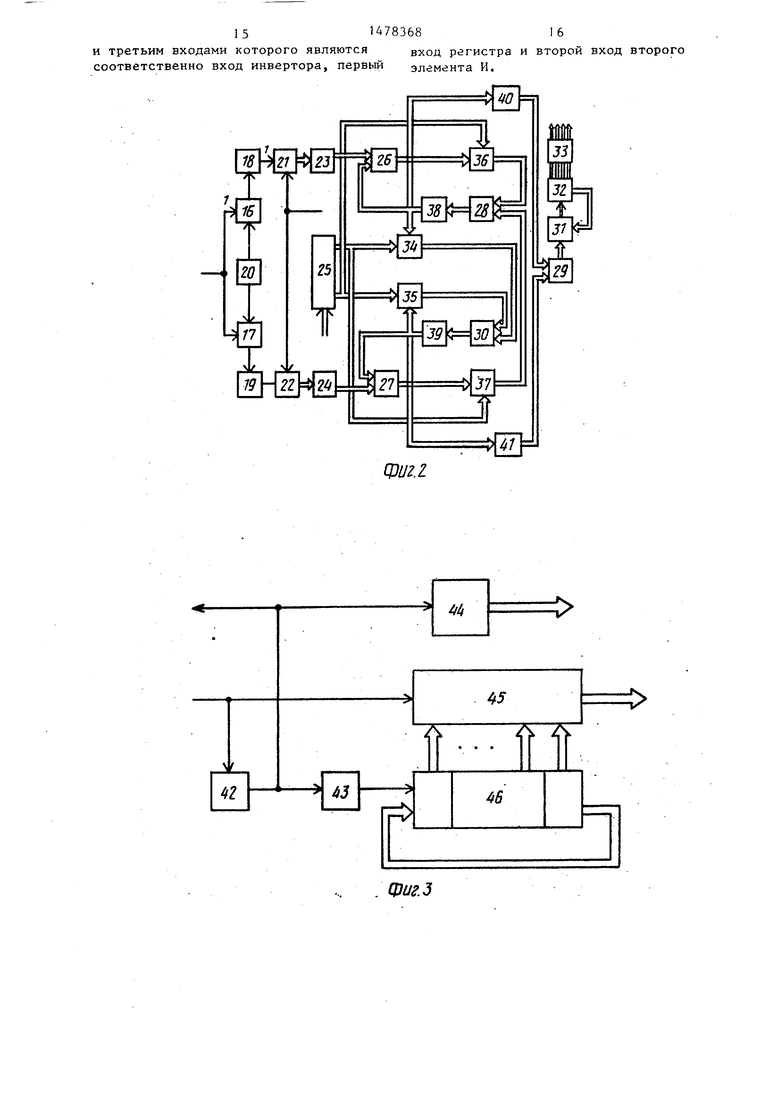

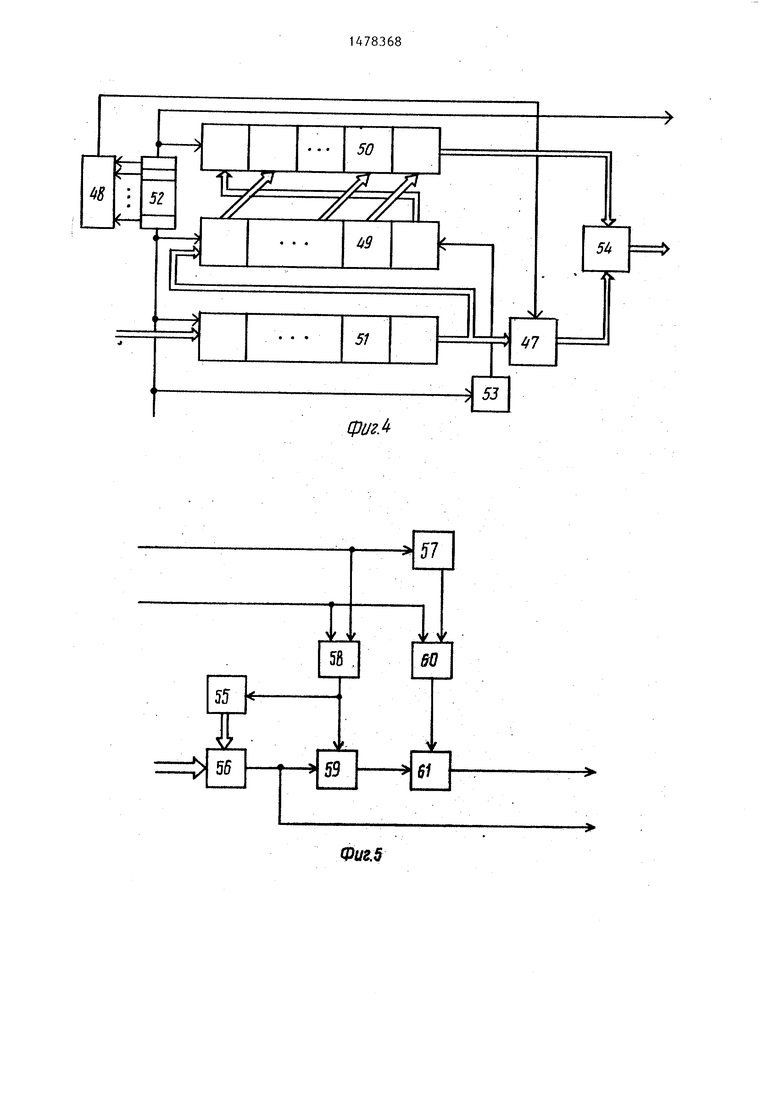

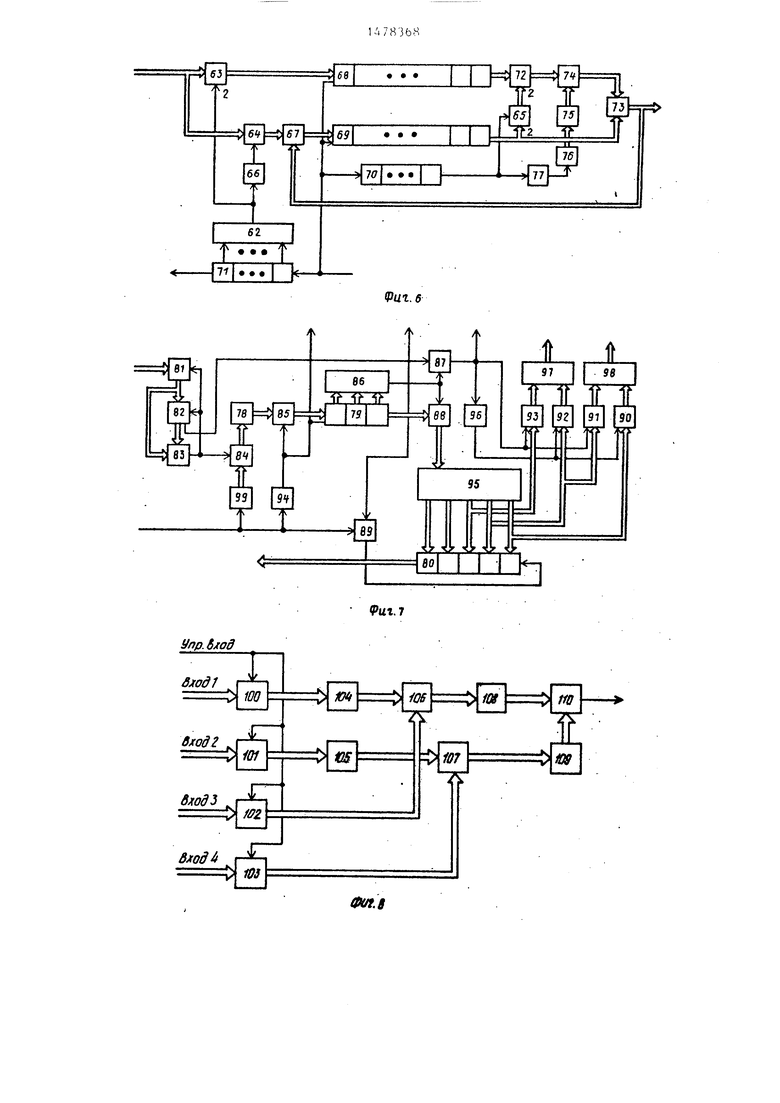

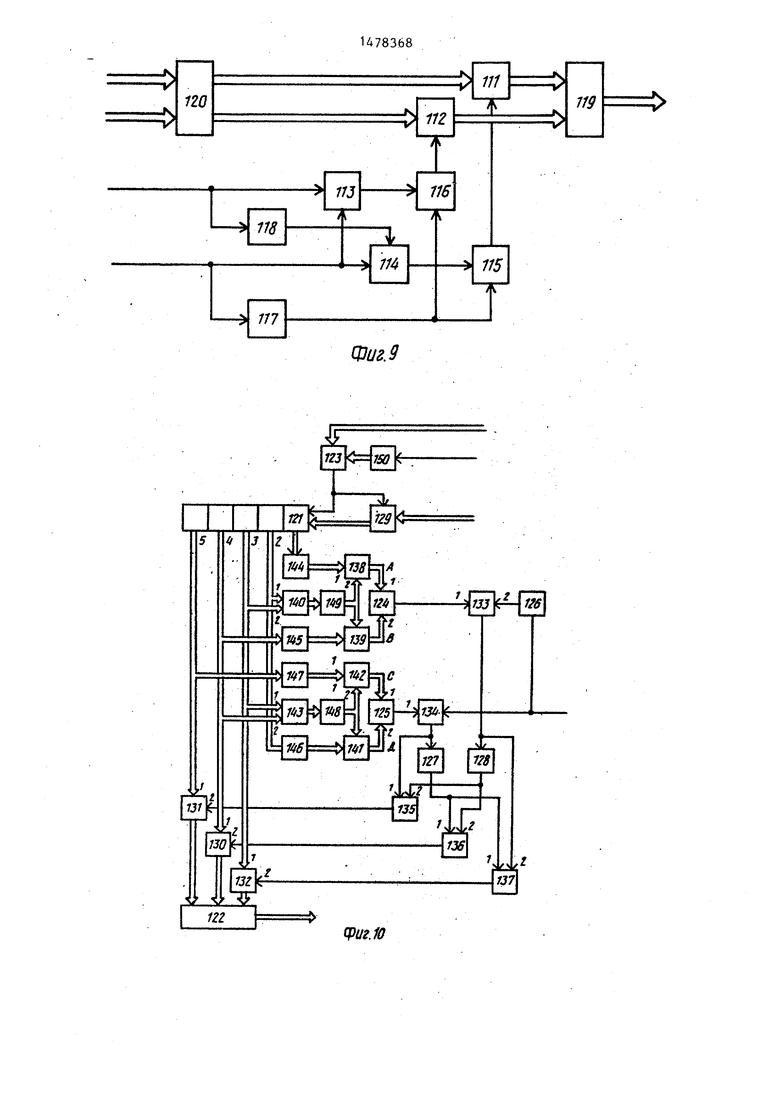

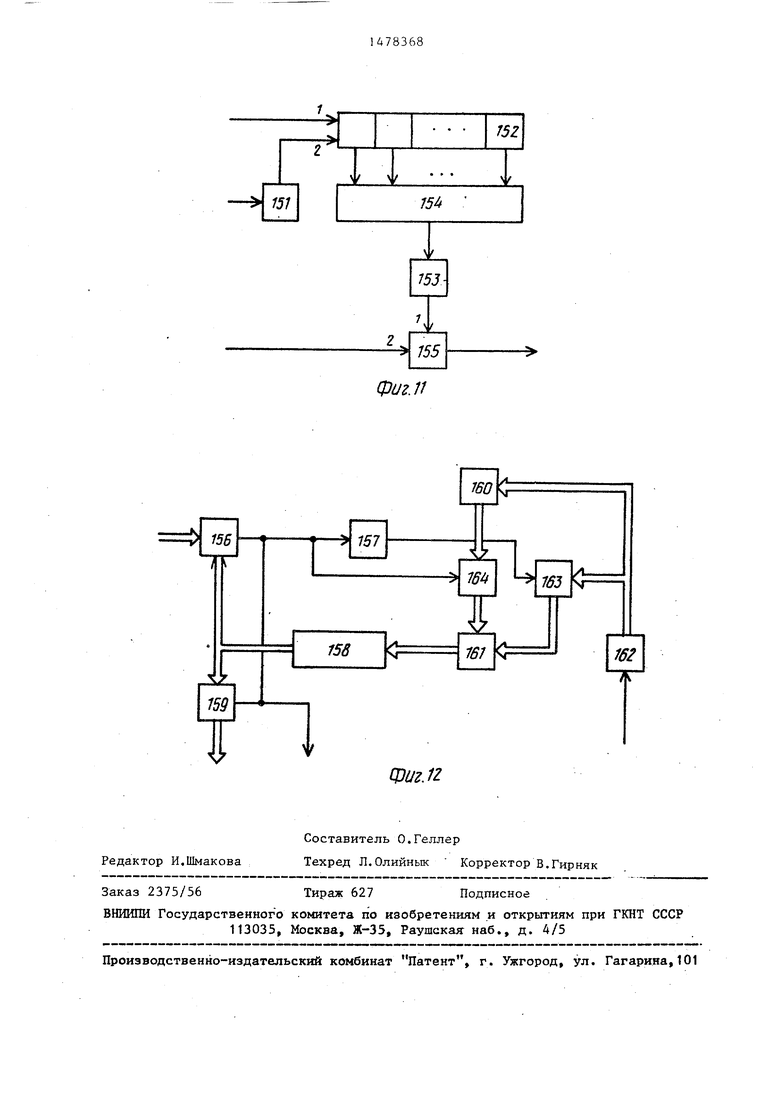

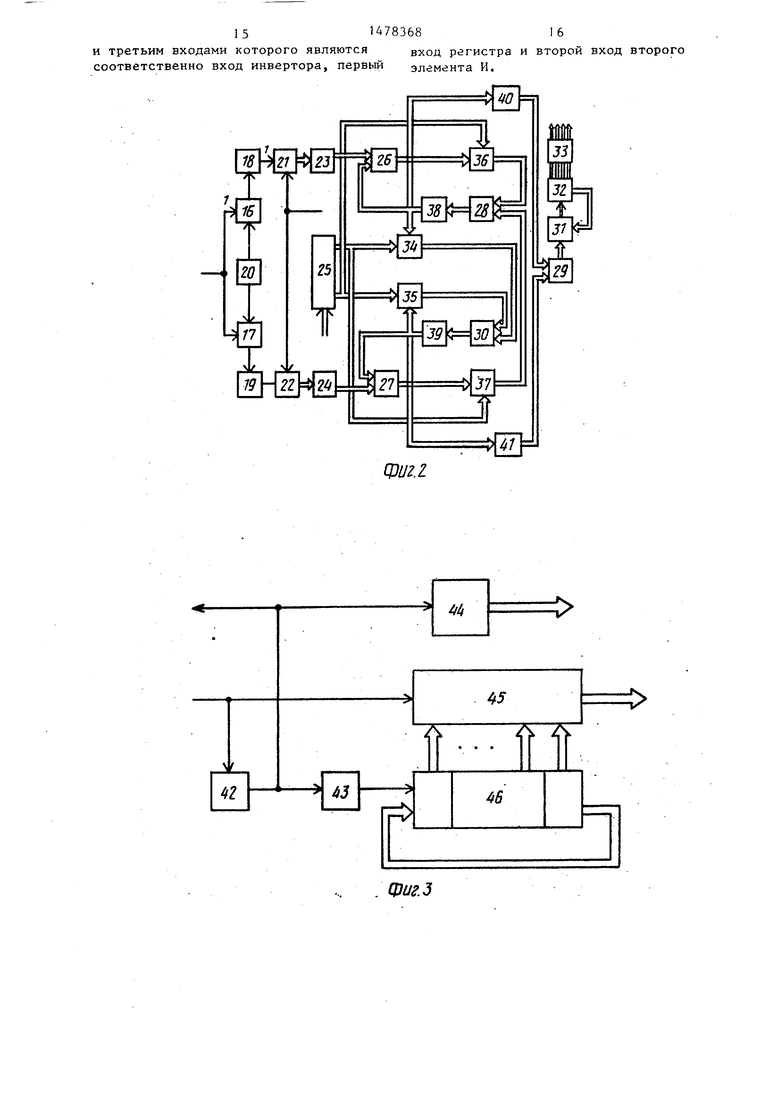

На фиг.1 изображена структурная электрическая схема предложенного приемника; на фиг.2 - структурная электрическая схема анализатора энергетического спектра; на фиг.З - структурная электрическая схема блока управления; на фиг.4 - структурная электрическая схема первого компен- сатора; на фиг.З - структурная электрическая схема второго компенсатора на фиг.6 - структурная электрическая схема накопителя; на фиг.7 - структурная электрическая схема логичес- кого блока; на фиг.8 - структурная электрическая схема демодулятора; на фиг.9 - структурная электрическая схема решающего блока; на фиг.10 - структурная электрическая схема бло- ка выбора данных; на фиг.11 - структурная электрическая схема формирователя управляющего сигнала; на фиг.12 - структурная электрическая схема блока вычисления ошибки синхро- низации.

Приемник многочастотных сигналов содержит анализатор 1 энергетического спектра, первый коммутатор 2, решающий блок 3, первый компенсатор 4, накопитель 5, логический блок 6, бло 7 выбора данных, блок 8 вычисления ошибки синхронизации, второй компенсатор 9, блок 10 управления, генератор 11 тактовых импульсов, формиро- ватель 12 управляющего сигнала, второй коммутатор 13, демодулятор 14 и декодер 15.

Анализатор 1 энергетического спектра содержит первый 16 и второй 17 преобразователи частоты, первый 18 и второй 19 полосовые фильтры, генератор 20 опорного сигнала, первый 21 и второй 22 аналого-цифровые преобразователи, первый 23 и второй 24 регистры, блок 25 весовых коэффициентов, первый - шестой сумматоры 26- 31, третий 32 и четвертый 33 регистр первый - четвертый перемножители 34- 37, первый 38 и второй 39 запоминающие блоки и первый 40 и второй 41 квадраторы.

Блок 10 управления содержит первый 42 и второй 43 делители частоты,

,

Q $ 0 5 0

5 0

5

счетчик 44, коммутатор 45 и регистр 46.

Первый компенсатор 4 содержит первый 47 и второй 48 элементы И, первый - четвертый регистры 49-52, де- литель 53 частоты и сумматор 54.

Второй компенсатор 9 содержит счетчик 55, блок 56 сравнения, инвертор 57, первый - третий элементы И 58-60 и элемент ИЛИ 61.

Накопитель 5 содержит первый - четвертый элементы И 62-65, инвертор 66, элемент ИЛИ 67, первый - четвертый регистры 68-71, первый 72 и второй 73 сумматоры, перемножитель 74, постоянный запоминающий блок 75, счетчик 76 и делитель 77 частоты.

Логический блок 6 содержит первый- пятый регистры 78-82, узел 83 сравнения, первый - десятый элементы И 84-93, делитель 94 частоты, арифметический узел 95, инвертор 96, первый 97 и второй 98 элементы ИЛИ и счетчик 99.

Демодулятор 14 содержит первый - четвертый элементы И 100-103, первьТй 104ф и второй 105 блоки задержки, первый 106 и второй 107 сумматоры, первый 108 и второй 109 двухполупериод- ные выпрямители и блок 110 сравнения.

Решающий блок 3 содержит лервый - четвертый элементы И 111-114, первый 115 и второй 116 элементы ИЛИ, первый 117 и второй 118 инверторы, сумматор 119 и узел 120 задержки.

Блок 7 выбора данных содержит регистр 121, элемент ИЛИ 122; первый - третий узлы 123-125 сравнения, пер- вый-третий инверторы 126-128, первый- девятый элементы И 129-137, первый- шестой сумматоры 138-143, первый - шестой двухполупериодные выпрямители 144-149 и счетчик 150.

Формирователь 12 управляющего сигнала содержит инвертор 151, регистр 152, триггер 153, первый 154 и второй 155 элементы И.

Блок 8 вычисления ошибки синхронизации содержит узел 156 сравнения, инвертор 157, постоянный запоминающий узел 158, элемент И 159, сумматор 160, элемент ИЛИ 161,счетчик 162, первый 163 и второй 164 элементы И.

Приемник работает следующим образом.

На вход приемника многочастотных сигналов поступает аддитивная смесь сигнала, белого шума и узкополосных

омех. Спектр сигнала, представляюего собой цифровое сообщение, переаваемое в виде частотной телеграфии (ЧТ), расширен псевдослучайными скачками по частоте (ПСЧ), причем скорость переключения частот равна скорости передачи сообщения. Анализатор 1 энергетического спектра разделяет рабочий диапазон частот на отдельные каналы по количеству рабочих частот (К) и формирует сигналы, пропорциональные мощностям аддитивных смесей сигнала, белого шума и помех в каждом канале. Функционально он эквивалентен набору из К поло- совых фильтров с квадратичными детекторами. Центральные частоты фильтров дискретно изменяются в соответствии с законом переключения частот в сигнале со скоростью, задаваемой тактовой частотой по командам, формируе мым в блоке 10 управления.

Допустим, что сигнал в начальный интервал времени, величина которого определяется скоростью передачи сообщения, передается на i-й частоте, соответствующей i-му фильтру. На следующем интервале сигнал появляется на (1+1)-й частоте, а вследствие переприсвоения центральных частот (1+1)-я частота опять соответствует i-му фильтру, таким образом частотные элементы сигнала появляются на выходе одного и того же 1-го фильтра. Допустим, что в одном из каналов, апример, в j-м, присутствует зкополосная помеха. Вследствие ереприсвоения центральных частот

помеха расщепляется по спектру в то время, как сигнал, находясь на выходе одного и того же 1-го фильтра, сворачивается по спектру. Таким образом, на выходе анализатора 1 энергетического спектра формируются свертка сигнала и расщепленные по спектру помехи.

При передаче информации в виде ЧТ рабочий диапазон частот разбит на пары частотных каналов для передачи в каждом интервале времени либо единичного, либо нулевого символа сообщения. Поэтому перестройка фильтров по описанному алгоритму осуществляется попарно.

Первый коммутатор 2 под возденет-- вием сигнала с блока 10 управления попарно подключает выходы анализатора 1 энергетического спектра к вхо0

5

0

5

дам решающего блока 3, который предназначен для выбора единичного или нулевого частотного канала в i-й паре, в зависимости от передаваемого символа сообщения. Информация о передаваемом символе в установившемся режиме поступает из демодулятора 14. В переходном режиме (до выделения информации) на вход первого компенсатора поступает суммарный сигнал каналов i-й пары. Таким образом в установившемся режиме шумовая полоса сужается в 2 раза. Первый компенсатор 4 предназначен для подавления узкогюлосных помех. На его выходе формируются разности между значениями суммарных сигналов на i-м и (i+ +1)-м шагах опроса анализатора энергетического спектра на каждой паре частот, в результате чего узкополосные помехи компенсируются. Очищенный от помех сигнал поступает на накопитель 5, где осуществляется накопление с усреднением разностей, сформированных первым компенсатором 4. Усреднение производится по реккур- сивному алгоритму

А,

Л,+

1

1-1

( -Ь ), ,2..,

5

0

5

0

5

и

где ui+1 - разности, сформированные на выходе первого компенсатора 4 на (1+2)-м шаге опроса анализатора 1 энергетического спектра; средние разности на выходе накопителя 5 соответственно на (i+1)-м и (1+2)-м шагах опроса анализатора 1 энергетического спектра. Количество разности на каждом шаге опроса определяется числом пар каналов (канальных пар). На выходе . накопителя 5 формируются статистические оценки величин разностей. Точность оценки прямо пропорциональна интервалу усреднения.

С выхода накопителя 5 оценка разностей поступает на логический блок 6, который определяет номера выходов анализатора 1 энергетического спектра, содержащих передаваемое сообщение, и на блок 7 выбора данных, который из всех сформированных оценок разностей выбирает ту оценку, величина которой пропорциональна задержке сигнала. Эта оценка поступает на вход блока 8 вычисления ошибки синхронизации.

51

По вычисленному значению ошибки синхронизации второй компенсатор 9 осуществляет задержку импульсов генератора 11 тактовых импульсов, поступающих на второй компенсатор 9 через , формирователь 12 управляющего сигнала, чем компенсируется ошибка по задержке. Задержанные тактовые импульсы непосредственно и через блок 10 управления поступают на анализатор 1 энергетического спектра и первый коммутатор 2. Блок 10 управления задает порядок переключения первого коммутатора 2 и Гперебора частот в анализаторе 1 энергетического спектра. Формирователь 12 управляющего сигнала предназначен для перевода приемника в режим точной синхронизации цри поступлении команды с логического блока 6.

Выходы анализатора 1 энергетического спектра подключены также к входам второго коммутатора 13, который по командам с логического блока 6 подключает к входам демодулятора 14 группу каналов, содержащих передаваемое сообщение. С выхода демодулятора 14 символы передаваемого сообщения поступают на декодер 15 и решающий блок 3.

Формула изобретения

товых импульсов и к третьему входу формирователя управляющего сигнала, первый и второй входы которого подключены соответственно к третьему и четвертому выходам логического блока, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами

0 второго коммутатора, выходы которого соединены с соответствующими сигнальными входами демодулятора, управляющий вход которого соединен с первым входом второго компенсатора и с уп5 равляющим входом решающего блока, выходы которого соединены с сигнальными входами первого компенсатора, управляющий вход которого подключен к третьему выходу блока управления,

0 первые выходы которого соединены с третьими входами анализатора энергетического спектра, второй вход которого подключен к входу блока управления и к второму выходу второго ком5 пенсатора, первый и вторые входы которого подключены соответственно к первому и вторым выходам блока вычисления ошибки синхронизации, сигнальные входы которого подключены к

о выходам блока выбора данных, первый и второй входы которого подключены соответственно к пятому и шестому выходам логического блока, второй вход которого соединен с вторым входом накопителя и с,третьим входом блока выбора данных, четвертые входы которого соединены с третьими выходами накопителя, первый и второй входы которого подключены соответственно к первым и вторым выходам первого компенсатора, при этом выход формирователя управляющего сигнала соединен с управляющим входом первого компенсатора и с управляющим входом блока вычисления ошибки синхронизации, выходы анализатора энергетического спектра соединены с соответствующими сигнальными входами второго коммутатора, а первые и вторые выходы первого коммутатора соединены соответственно с вторыми и третьими входами решающего блока.

5

0

5

0

5

четыре перемножителя, два запоминающих блока, два квадратора и генератор опорного сигнала, первый и второ выходы которого соединены с вторыми входами соответственно первого и второго преобразователей частоты, выходы которых соединены с входами соответственно первого и второго полосовых фильтров, выходы которых соединены с первыми входами соответственно первого и второго аналого-цифровых преобразователей, выходы которых соединены с входами соответственно первого и второго регистров, выходы которых подключены к первым входам соответственно первого и второго сумматоров, выходы которых подключены к первым входам соответственно третьего и четвертого перемножителей, выходы которых соединены соответственно с первым и вторым входами третьего сумматора, выходы которого соединены с входами первого запоминающего блока, выходы которого соединены с вторыми входами первого сумматора, с первыми входами первого перемножителя и с входами первого квадратора, выходы которого соединены с первыми входами четвертого сумматора вторые входы которого соединены с выходами второго квадратора, входы которого подключены- к первым входам второго перемножителя, к вторым входам второго сумматора и к выходам второго запоминающего блока, входы которого подключены к выходам пятого сумматора, первый и второй входы которого соединены с выходами соответственно первого и второго перемножителей, вторые входы которых соединены с вторыми входами соответственно четвертого и третьего перемножителей, выходы четвертого сумматора соединены с первыми входами шестого сумматора, выходы которого подключены к входам третьего регистра, первые выходы которого соединены с вторыми входами шестого сумматора, первые и вторые выходы блока весовых коэффициентов соединены с вторыми входами соответственно первого и второго перемножителей, вторые выходы третьего регистра соединены с входами четвертого регистра, выходы которого являются выходами анализатора энергетического спектра, первым входом которого являются объединенные первые входы первого и второго преобразователей частоты, вторые объединенные входы первого и второго знало- го-цифровых преобразователей являются вторым входом анализатора энергетического спектра, третьими входами которого являются входы блока весовых коэффициентов.

5 первыми, вторыми и третьим выходами которого являются соответственно выходы коммутатора, выходы счетчика и выход первого делителя частоты.

с вторыми входами перемножителя, первые входы которого подключены к выходам первого сумматора, первые входы которого подключены к выходам первого регистра, первый вход которого соединен с пеовым входом второго регистра, с входом третьего регистра и с входом четвертого регистра, параллельные выходы которого соединены с входами первого элемента И, выход которого соединен с вторым входом второго элемента-И и с входом инвертора, выход которого соединен с вторым входом третьего элемента И, выходы которого соединены с первыми входами элемента ИЛИ, выходы которого соединены с вторыми входами второго регистра, выходы которого соединены с вторыми входами четвертого 5 элемента И и с вторыми входами второго сумматора, первые входы которого подключены к выходам перемножителя, выход третьего регистра соепи0

5

0

5

0

пен с входом делителя частоты и с первым входом четвертого элемента И, выходы которого соединены с вторыми входами первого сумматора, выход делителя частоты соедшнаи с вкояом счетчика, выходы второго сумма ера сое- динены с вторыми входами элеме-ита ИЛИ, вторые входы первого регистра подключены к выходам второго элемента И, первые входы которого соединены с первыми входами третьего элемента И и являются входами накопителя, управляющим входом которого является первый вход первого регистра, выходы второго сумматора являются первыми выходами накопителя, вторым выходом которого является выход четвертого регистра.

10

15

20

25

78368Ю

арифметического узла, четвертые и пятые выходы которого соединены соответственно с четвертыми и пятыми входами третьего регистра, вход управления которого подключен к выходу шестого элемента И, выходы четвертого регистра соединены с соответствующими входами пятого регистра и с вто рыми входами узла сравнения, первые входы которого подключены к первым выходам пятого регистра, второй выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом инвертора, с первым входом десятого элемента И и с первым входом восьмого элемента И, выходы которого соединены с первыми входами второго элемента ИЛИ, вторые входы которого подключены к выходам седьмого элемента И, первый вход которого подключен к первому входу девятого элемента И и к выходу инвертора, первый вход первого элемента И соединен

0

5

5

0

5

0

с выходом узла сравнения, с управляющим входом пятого регистра и с управляющим входом четвертого регистра, входы которого являются первыми входами логического блока, вторым входом которого является вход счетчика, первыми, вторыми, третьим, четвертым, пятым и шестыми выходами логического блока являются соответственно выходы второго элемента ИЛИ, выходы первого элемента ИЛИ, выход третьего элемента И, выход делителя частоты, выход четвертого элемента И и выходы третьего регистра.

ход блока сравнения является выходом демодулятора, первыми, вторыми, третьими и четвертыми входами которого являются соответственно вторые входы первого элемента И, вторые входы второго элемента И, вторые входы третьего элемента И и вторые входы четвертого элемента И, первый вход которого является управляющим входом демодулятора.

и узел задержки, первые и вторые выходы которого соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с выходами, соответственно первого и второго элементов ИЛИ, первые входы которых подключены к выходу первого инвертора, вход которого соединен с вторыми входами третьего и четвертого элементов И, выходы которых соединены с вторыми входами соответственно второго и первого элементов ИЛИ, первый вход третьего элемента И соединен с входом второго инвертора, выход которого соединен с первым входом четвертого элемента И, выходы первого и второго элементов И соединены соответственно с первыми и вторыми входами сумматора, выходы которого являются выходами решающего блока,первым, вторыми и третьими входами которого являются соответственно вход второго инвертора, вторые и третьи входы узла задержки, управляющим входам решающего блока является вход первого инвертора.

1 2

5

0

5

с входом делителя частоты, параллельные выходы четвертого регистра подключены к входам второго элемента И, выход которого соединен с вторым входом первого элемента И, последовательный выход четвертого регистра соединен с управляющим входом второго регистра, выходы сумматора и последовательный выход четвертого регистра являются соответственно первыми и вторыми выходами первого компенсатора, вход делителя частоты является управляющим входом первого компенсатора.

9v Приемник поп.1,отлича- ю щ и и с я тем, что второй компенсатор содержит три элемента И, элемент ИЛИ, инвертор, блок сравнения и счетчик, вход которого подключен к выходу первого элемента И и к первому входу второго элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, первый вход которого соединен с первым входом первого элемента И, второй вход которого подключен к входу инвертора, выход которого сое0 динен с вторым входом третьего элемента И, выходы счетчика соединены с первыми входами блока сравнения, выход которого соединен с вторым входом второго элемента И и является первым выходом второго компенсатора, вторым выходом которого является выход элемента ИЛИ, первый вход первого элемента И является управляющим входом второго компенсатора, первым и вторым входами которого являются соответственно вход инвертора и вторые входы блока сравнения.

0

0

5

131

рым входом третьего элемента И и с выходом узла сравнения, вторые входы которого соединены с первыми входами третьего элемента И и с выходами постоянного запоминающего узла, входы которого подключены к выходам элемента ИЛИ, при этом выход узла сравнения является первым выходом блока вычисления ошибки синхронизации, вто рыми выходами которого являются выходы третьего элемента И, вход счетчика является управляющим входом блока вычисления ошибки синхронизации, входами которого являются первы входы узла сравнения.

ю щ и и с я тем, что блок выбора данных содержит регистр, элемент ИЛИ, три узяа сравнения, три инвертора, девять элементов И, шесть сумматоров, шесть двухполупериодных выпрямителей и счетчик, выходы которого соединены с вторыми входами первого узла сравнения, выход которого соединен с управляющим входом регистра и с первым входом первого элемента И, выходы которого соединены с входами регистра, первые выходы которого соединены через первый двухполупериодный выпрямитель с первыми входами первого сумматора, выходы которого соединены с первыми входами второго узла сравнения , вторые входы которого подключены к выходам второго двухполупери- одного выпрямителя, входы которого соединены с первыми входами второго элемента И, с вторыми входами шестого сумматора и с четвертыми выходами регистра, вторые выходы которого соединены с первыми входами третьего сумматора и с входами третьего двух- полупериодного выпрямителя, выходы которого соединены с первыми входами четвертого сумматора, выходы которого соединены с вторыми входами третьего узла сравнения, первые входы которого подключены к выходам пятого сумматора, первые входы которого подключены к выходам четвертого двухпо- лупериодного выпрямителя, входы которого соединены с первыми входами третьего элемента И и с пятыми выходами регистра, третьи выходы которого соединены с первыми входами четвертого элемента И, с вторыми входами третьего сумматора и с первыми входами шестого сумматора, выходы которого соединены с входами пятого двухполу14

Q

5

периодного выпрямителя, выходы которого соединены с вторыми входами четвертого и пятого сумматоров, выходы третьего сумматора соединены с входами шестого двухполупериодного выпрямителя, выходы которого соединены с вторыми входами первого и второго сумматоров, выход второго узла сравнения соединен с первым входом пятого элемента И, второй вход которого подключен к выходу первого инвертора, вход которого соединен с вторым входом шестого элемента И, выход которого соединен с входом второго инвертора и с первым входом седьмого элемента И, второй вход которого соединен с вторым входом восьмого элемента И и с выходом третьего ино вертора, вход которого подключен к выходу пятого элемента И и к второму входу девятого элемента И, первый вход которого соединен с первым входом восьмого элемента И и с выходом

5 второго инвертора, выход третьего узла сравнения соединен с первым входом шестого элемента И, выход седьмого элемента И соединен с вторым входом третьего элемента И, вы0 ходы которого соединены с первыми входами элемента ИЛИ, вторые входы которого подключены к выходам второго элемента И, второй вход которого соединен с выходом восьмого элемента И, выход девятого элемента И соединен с вторым входом четвертого элемента И, выходы которого соединены с третьими входами элемента ИЛИ, выходы которого являются выходаQ ми блока выбора данных, первым, вторыми, третьим и четвертым входами которого являются соответственно вход первого инвертора, первые входы первого узла сравнения, вход счетчика и вторые входы первого элемента И.

5 элемента И, выход которого через триггер соединен с первым входом второго элемента И, выход которого- является выходом формирователя управляющего сигнала, первым, вторым

5

5

4J

Фиг. 2.

44

:

45

i

ft-If If

46

. Фиг.З

f f

t

59

60

Фиг.5

b QftfZVt

$

/54

фиг. 11

| Патент США N 4271524, кл | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

Авторы

Даты

1989-05-07—Публикация

1987-08-10—Подача