Изобретение относится к области электрорадиотехники и может быть использовано в качестве функционального узла различных аналоговых микросхем для стабилизации их статического режима.

Основное назначение двуполярных стабилизаторов тока - обеспечить идентичный заданный статический режим транзисторных каскадов относительно шины положительного и отрицательного источников питания, например комплементарных дифференциальных усилителей, различных входных, промежуточных и выходных подсхем на р-n-р и n-р-n транзисторах. Двуполярный стабилизатор тока является одним из наиболее распространенных функциональных узлов аналоговой микроэлектроники.

Известны стабилизаторы двуполярных токов (СДТ) на базе токовых зеркал, которые стали основой построения современных аналоговых микросхем (AM) различного назначения [1-4]. Проблемы повышения стабильности и идентичности их выходных токов, которые оказывают существенное влияние на качественные показатели AM, относятся к числу одной из задач современной аналоговой микросхемотехники.

Ближайшим прототипом (фиг.1) заявляемого устройства является классический стабилизатор двуполярных токов, описанный в структуре усилителя по патенту США №5.557.238 (фиг.6), содержащий первый 1 и второй 2 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине первого 3 источника питания, причем коллектор второго 2 р-n-р транзистора связан с первым выходом 4 стабилизатора двуполярных токов, первый 5 и второй 6 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине второго 7 источника питания, причем коллектор второго n-p-n транзистора 6 соединен со вторым выходом 8 стабилизатора двуполярных токов, токозадающий резистор 9, включенный между коллекторами первого 1 р-n-р и первого 5 n-p-n транзисторов.

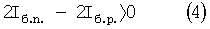

Существенный недостаток известного устройства (фиг.1) состоит в том, что оно имеет сравнительно высокие значения нестабильности выходных токов (I4, I8) при изменении напряжений питания E1, E2.

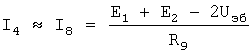

Действительно, выходные токи I4, I8 СДТ в нагрузках Rн1 и Rн2 схемы-прототипа (фиг.1) определяются резистором 9:

,

,

где Uэб=0,7 В - напряжение эмиттер-база транзисторов схемы;

R9 - сопротивление токозадающего резистора 9.

Таким образом, приращение напряжений E1, E2 на А% вызывает такое же изменение токов I4 и I8 (на А%). Это существенный недостаток СДТ-прототипа.

Основная цель предполагаемого изобретения состоит в повышении стабильности выходных токов СДТ при их высокой идентичности в широком диапазоне изменения напряжений питания.

Поставленная цель достигается тем, что в стабилизаторе двуполярных токов, содержащем первый 1 и второй 2 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине первого 3 источника питания, причем коллектор второго 2 р-n-р транзистора связан с первым выходом 4 стабилизатора двуполярных токов, первый 5 и второй 6 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине второго 7 источника питания, причем коллектор второго n-p-n транзистора 6 соединен со вторым выходом 8 стабилизатора двуполярных токов, токозадающий резистор 9, включенный между коллекторами первого 1 р-n-р и первого 5 n-р-n транзисторов, предусмотрены новые элементы и связи - в схему введены дополнительные n-p-n 10 и р-n-р 11 транзисторы, эмиттер n-p-n 10 дополнительного транзистора соединен с коллектором первого n-p-n транзистора 5, его коллектор подключен к объединенным базам первого 1 и второго 2 р-n-р транзисторов, а база связана с первым источником напряжения смещения 12, эмиттер дополнительного р-n-р транзистора 11 соединен с коллектором первого р-n-р 1 транзистора, его коллектор подключен к объединенным базам первого 5 р-n-р и второго 6 n-p-n транзисторов, а база связана со вторым источником напряжения смещения 13.

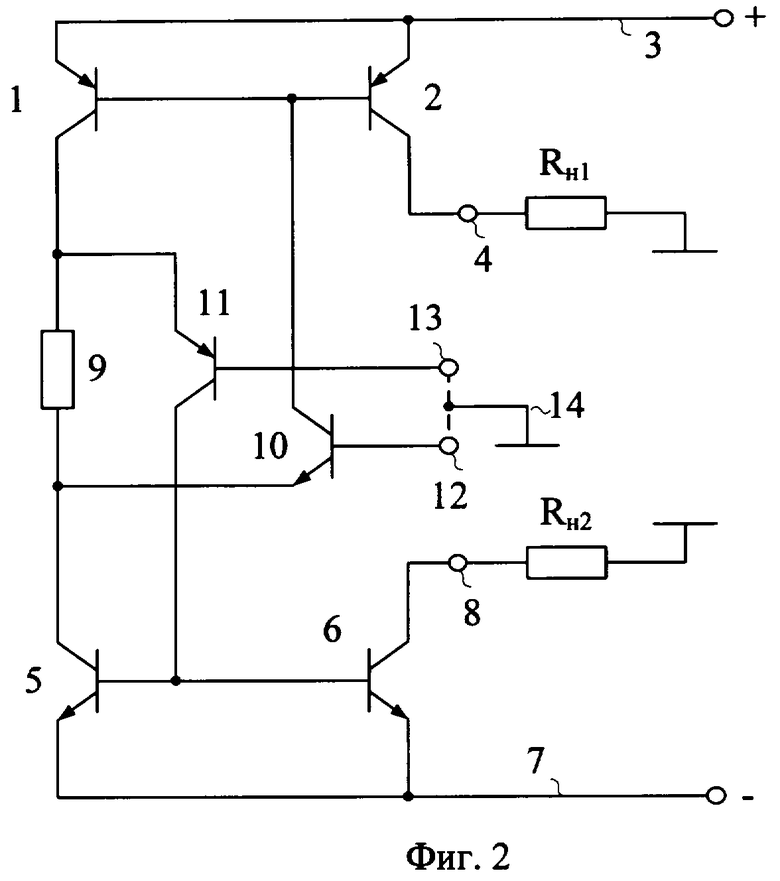

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

На фиг.3 показаны токи в транзисторах схемы фиг.2. Эта схема используется для анализа свойств заявляемого СДТ.

На фиг.4 представлен стабилизатор двуполярных токов, соответствующий п.2, п.3 и п.4 формулы изобретения, в котором потенциал базы транзисторов 12 и 13 равен потенциалу общей шины 14.

Схема стабилизатора двуполярных токов, соответствующая п.1, п.3, п.4 формулы изобретения, в которой показан другой вариант выполнения первого 12 и второго 13 источников напряжения смещения, представлена на фиг.5.

На фиг.6 приведена схема СДТ, соответствующая п.5 формулы изобретения. Здесь напряжения Е12 и E13 устанавливаются двухполюсниками 23 и 24.

Пример применения предлагаемого устройства для установления статического режима классического комплементарного дифференциального усилителя показан на фиг.7.

На фиг.8 представлена схема предлагаемого устройства фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.9 и фиг.10 - результаты ее компьютерного моделирования - зависимость выходных токов СДТ I4=I(R1), I8=I(R2) от изменения напряжений питания E1=V1 и E2=V2. Эти графики показывают, что выходные токи ДСТ изменяются не более чем на 1% при изменении E1 (E2) в 4 раза.

На фиг.11 показана схема СДТ фиг.2 с цепью запуска статического режима в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», соответствующая п.6 формулы изобретения, а на фиг.12, фиг.13, фиг.14 и фиг.15 - результаты ее компьютерного моделирования - зависимость выходных токов СДТ I4=I(R13), I8=(R14) от изменения напряжений питания E1=V1 и Е2=V2. Эти графики показывают, что выходные токи СДТ изменяются не более чем на 1% при изменении E1(Е2) в 3 раза.

Фиг.14 и фиг.15 соответствуют чертежам фиг.12 и фиг.13 в укрупненном масштабе. Последние графики показывают, что предлагаемый СДТ обеспечивает высокую стабильность выходных токов при изменении V1 и V2 в диапазоне 0,86В - 15В.

Схема СДТ с одним из вариантов цепи запуска статического режима, соответствующая п.6 формулы изобретения, приведена на фиг.16. Результаты ее компьютерного моделирования (фиг.11) представлены на фиг.12 - фиг.15.

Предлагаемый стабилизатор двуполярных токов (фиг.2, фиг.3) содержит первый 1 и второй 2 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине первого 3 источника питания, причем коллектор второго 2 р-n-р транзистора связан с первым выходом 4 стабилизатора двуполярных токов, первый 5 и второй 6 n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине второго 7 источника питания, причем коллектор второго n-p-n транзистора 6 соединен со вторым выходом 8 стабилизатора двуполярных токов, токозадающий резистор 9, включенный между коллекторами первого 1 р-n-р и первого 5 n-р-n транзисторов. В схему введены дополнительные n-p-n 10 и р-n-р 11 транзисторы, эмиттер n-p-n 10 дополнительного транзистора соединен с коллектором первого n-p-n транзистора 5, его коллектор подключен к объединенным базам первого 1 и второго 2 р-n-р транзисторов, а база связана с первым источником напряжения смещения 12, эмиттер дополнительного р-n-р транзистора 11 соединен с коллектором первого р-n-р 1 транзистора, его коллектор подключен к объединенным базам первого 5 р-n-р и второго 6 n-p-n транзисторов, а база связана со вторым источником напряжения смещения 13.

В схеме фиг.3, соответствующей п.1 и п.2 формулы изобретения, в качестве первого 12 и второго 13 источников напряжения смещения используется общая шина 14 первого 3 и второго 7 источников питания.

В схеме фиг.4, соответствующей п.2, п.3 и п.4 формулы изобретения, параллельно эмиттерно-базовому переходу второго 2 р-n-р транзистора включены эмиттерно-базовые переходы n (n≥1) вспомогательных р-n-р транзисторов 15, коллекторы которых являются токовыми выходами 16 первой группы выходов стабилизатора двуполярных токов. Кроме этого, в данной схеме параллельно эмиттерно-базовому переходу второго n-p-n 6 транзистора включены эмиттерно-базовые переходы m (m≥l) вспомогательных n-р-n транзисторов 17, коллекторы которых являются токовыми выходами 18 второй группы выходов стабилизатора двуполярных токов.

Схема стабилизатора двуполярных токов (п.1, п.3, п.4 формулы изобретения), в котором показано конкретное выполнение первого 12 и второго 13 источников напряжения смещения (элементы 19, 20, 21), представлена на фиг.5. Здесь за счет выбора отношения резисторов 20 и 21 устанавливается заданный уровень напряжений в узлах 12 (Е12) и 13 (Е13).

В схеме фиг.6 источники напряжения смещения 12 и 13 реализуются в виде элементов 22, 23, 24, а нагрузка Rн (25) включена в цепь шины 3 первого источника питания. Аналогично нагрузка Rн может включаться в эмиттерную цепь транзисторов 5 и 6 (п.5 формулы изобретения).

Пример применения предлагаемого устройства для установления статического режима классических комплементарных дифференциальных усилителей (транзисторы 26-29) показан на фиг.7.

Описание фиг.8÷15 даны на стр.5÷6.

В схеме фиг.16, соответствующей п.6 формулы изобретения, токостабилизирующий резистор 9 выполнен в виде двух последовательно соединенных вспомогательных резисторов 30 и 31, общая точка которых подключена к базе согласующего транзистора 32, коллектор которого связан с коллектором первого 1 р-n-р транзистора, а эмиттер подключен к коллектору первого 5 n-p-n транзистора. Необходимость применения такой схемы возникает в тех редких случаях, когда все элементы схемы фиг.2 имеют высокую симметрию. Возможны и другие варианты построения цепей запуска статического режима СДТ.

Рассмотрим работу заявляемого устройства (фиг.3).

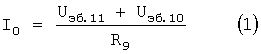

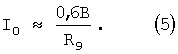

Статический режим всех транзисторов схемы фиг.3 устанавливается резистором 9:

где Uэб.11, Uэб.10≈0,6В - напряжение эмиттер-база транзисторов 11 и 10.

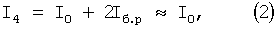

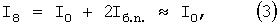

Так как Uэб.11, Uэб.10 слабо зависят от напряжений питания E1 и Е2 - это обуславливает высокую стабильность выходных токов СДТ:

где Iб.р, Iб.n - значения токов базы транзисторов n-р-n и р-n-р типов. Выходные токи заявляемого СДТ отличаются друг от друга на величину, которая определяется разностью

и зависит от абсолютных значений коэффициента усиления по току базы (β) n-р-n и р-n-р транзисторов.

В схемах фиг.4, фиг.5 за счет параллельного включения транзисторов 15 и 2, а также 17 и 6 образуются дополнительные токовые выходы 16 и 18, число которых определяется числом транзисторов 15 и числом транзисторов 17 в схеме СДТ. Эти выходы могут использоваться для установления статического режима в различных элементах аналоговых микросхем.

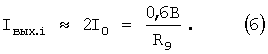

Особенность схемы фиг.5 состоит в том, что здесь статический ток I0, устанавливающий режим всех транзисторов, определяется по формуле

Элементы 19, 20 и 21, 22 создают заданные напряжения Е12 и E13, которые, в зависимости от решаемой задачи, могут изменяться в широких пределах.

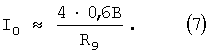

В схеме фиг.6 заданный статический потенциал в узле 13 обеспечивается резисторами 23 и 24, а ток в нагрузке Rн (25)

Численные значения статического тока I0 в схеме комплементарного дифференциального усилителя фиг.7

Одна из особенностей рассматриваемых схем СДТ - проблема запуска статического режима при включении питания, которая решается введением асимметрии элементов схемы, например подключением разного числа транзисторов 15 и 17 и др., а также использованием специальных элементов, предустанавливающих начальный статический режим (фиг.11, фиг.16).

Таким образом, введение в СДТ новых элементов и связей в соответствии с формулой изобретения обеспечивает:

- уменьшение на два порядка влияния нестабильности источников питания на выходные токи СДТ.

- работу СДТ при малых напряжения питания;

- широкий допустимый диапазон изменения выходных напряжений СДТ (E1-0,6В, E2-0,6В);

Компьютерное моделирование частных вариантов заявляемого устройства (фиг.8, фиг.11), выполненное в среде PSpice, подтверждает (фиг.9, фиг.10 и фиг.12, фиг.13, фиг.14, фиг.15) эффективность рассмотренных схемотехнических решений - нестабильность выходных токов СДТ (в сравнении с прототипом) существенно снижается.

Литература

1. Патент США № 5.557.238.

2. Патент США № 5.786.729.

3. Патент США № 4.122.403.

4. Патент США № 3.644.638.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СТАБИЛИЗАЦИИ СТАТИЧЕСКОГО РЕЖИМА ЭМИТТЕРНЫХ ЦЕПЕЙ НИЗКОВОЛЬТНЫХ ТРАНЗИСТОРНЫХ КАСКАДОВ | 2009 |

|

RU2386205C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2595927C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2439781C1 |

| УПРАВЛЯЕМЫЙ ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2307386C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615071C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2383053C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374756C1 |

Изобретение относится к области электрорадиотехники и может быть использовано в качестве функционального узла различных аналоговых микросхем для стабилизации их статического режима.

Стабилизатор двуполярных токов содержит первый (1) и второй (2) n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине первого (3) источника питания, причем коллектор второго (2) р-n-р транзистора связан с первым выходом (4) стабилизатора двуполярных токов, первый (5) и второй (6) n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине второго (7) источника питания, причем коллектор второго n-p-n транзистора (6) соединен со вторым выходом (8) стабилизатора двуполярных токов, токозадающий резистор (9), включенный между коллекторами первого (1) р-n-р и первого (5) n-p-n транзисторов. В схему введены дополнительные n-p-n (10) и р-n-р (11) транзисторы, эмиттер n-p-n дополнительного транзистора 10 соединен с коллектором первого n-p-n транзистора (5), его коллектор - подключен к объединенным базам первого (1) и второго (2) р-n-р транзисторов, а база связана с первым источником напряжения смещения (12), эмиттер дополнительного р-n-р транзистора (11) соединен с коллектором первого р-n-р (1) транзистора, его коллектор - подключен к объединенным базам первого (5) р-n-р и второго (6) n-p-n транзисторов, а база связана со вторым источником напряжения смещения (13). Технический результат - повышение стабильности выходных токов. 5 з.п. ф-лы, 16 ил.

1. Стабилизатор двуполярных токов, содержащий первый (1) и второй (2) p-n-p транзисторы с объединенными базами, эмиттеры которых подключены к шине первого (3) источника питания, причем коллектор второго (2) р-n-р транзистора связан с первым выходом (4) стабилизатора двуполярных токов, первый (5) и второй (6) n-p-n транзисторы с объединенными базами, эмиттеры которых подключены к шине второго (7) источника питания, причем коллектор второго (6) n-p-n транзистора соединен со вторым выходом (8) стабилизатора двуполярных токов, токозадающий резистор (9), включенный между коллекторами первого (1) р-n-р и первого (5) n-p-n транзисторов, отличающийся тем, что в схему введены дополнительные n-p-n (10) и р-n-р (11) транзисторы, эмиттер n-p-n дополнительного транзистора (10) соединен с коллектором первого (5) n-p-n транзистора, его коллектор - подключен к объединенным базам первого (1) и второго (2) р-n-р транзисторов, а база - связана с первым источником напряжения смещения (12), эмиттер дополнительного р-n-р транзистора (11) соединен с коллектором первого р-n-р (1) транзистора, его коллектор - подключен к объединенным базам первого (5) и второго (6) n-p-n транзисторов, а база - связана со вторым источником напряжения смещения (13).

2. Стабилизатор по п.1, отличающийся тем, что в качестве первого (12) и второго (13) источников напряжения смещения используется общая шина (14) первого (3) и второго (7) источников питания.

3. Стабилизатор по п.1, отличающийся тем, что параллельно эмиттерно-базовому переходу второго (2) р-n-р транзистора включены эмиттерно-базовые переходы n (n≥1) вспомогательных р-n-р транзисторов (15), коллекторы которых являются токовыми выходами (16) первой группы выходов стабилизатора двуполярных токов.

4. Стабилизатор по п.1, отличающийся тем, что параллельно эмиттерно-базовому переходу второго (6) n-р-n транзистора включены эмиттерно-базовые переходы m (m≥1) вспомогательных n-p-n транзисторов (17), коллекторы которых являются токовыми выходами (18) второй группы выходов стабилизатора двуполярных токов.

5. Стабилизатор по п.1, отличающийся тем, что в качестве токовых выходов стабилизатора двуполярного тока используются шины первого (3) и/или второго (7) источников питания.

6. Стабилизатор по п.1, отличающийся тем, что токостабилизирующий резистор (9) выполнен в виде двух последовательно соединенных вспомогательных резисторов (30) и (31), общая точка которых подключена к базе согласующего транзистора (32), коллектор которого связан с коллектором первого (1) р-n-р транзистора, а эмиттер подключен к коллектору первого (5) n-p-n транзистора.

| Двуполярный стабилизатор тока | 1976 |

|

SU633004A1 |

| US 5557238 A, 17.09.1996 | |||

| US 5786729 A, 28.07.1998. | |||

Авторы

Даты

2009-04-27—Публикация

2008-03-13—Подача