Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе дифференциального каскада с симметричной активной нагрузкой в виде источников опорного тока [1-8]. Их основное достоинство - повышенный коэффициент усиления по напряжению, который обеспечивается двумя каскадами усиления.

Для работы в условиях космического пространства в экспериментальной физике необходимы радиационно-стойкие ОУ с повышенным коэффициентом усиления по напряжению и максимальными амплитудами выходного напряжения  , близкими к напряжению питания. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [9], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [9-13].

, близкими к напряжению питания. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [9], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [9-13].

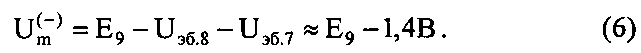

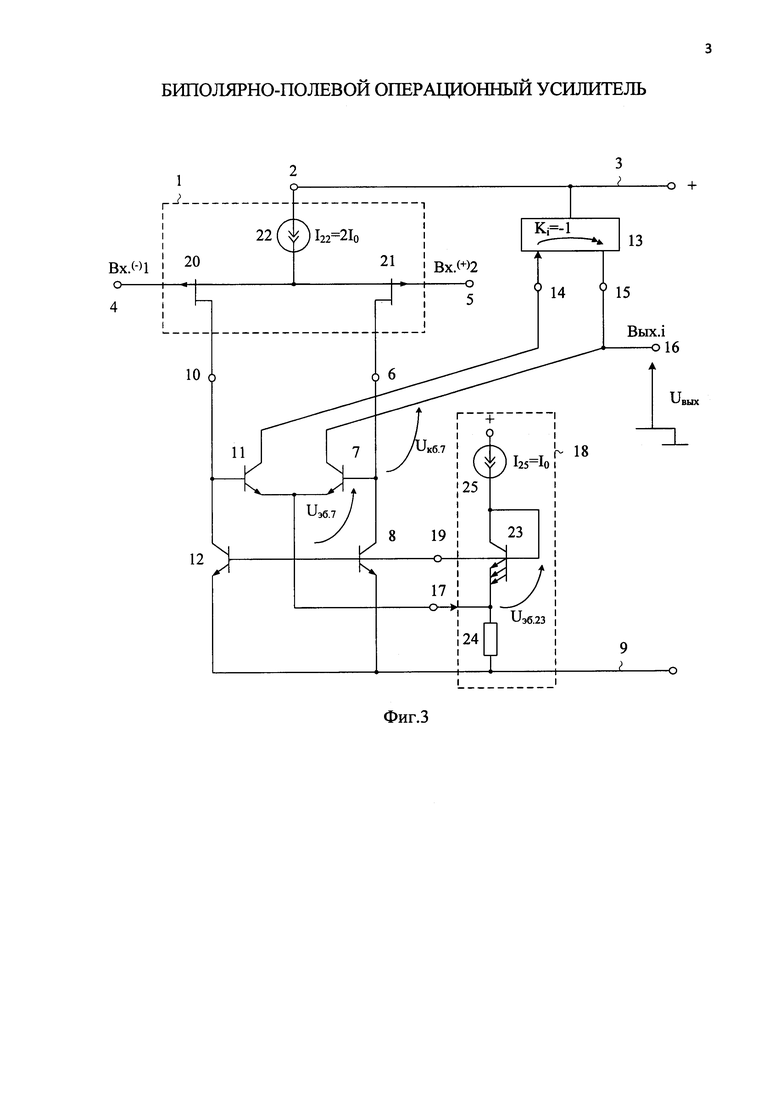

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 7.411.451, fig. 2. Он содержит (фиг. 1) входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 выходного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 выходного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, цепь динамической нагрузки 13, согласованную с первой 3 шиной источника питания, вход которой 14 соединен с коллектором второго 11 выходного транзистора, а выход 15 связан с выходом устройства 16 и коллектором первого 7 выходного транзистора, причем базы первого 8 и второго 12 транзисторов первого и второго источников опорного тока соединены друг с другом, а эмиттеры первого 7 и второго 11 выходных транзисторов объединены друг с другом.

Существенный недостаток известного ОУ состоит в том, что в нем не обеспечивается широкий диапазон изменения выходного напряжения, что особенно проявляется при низковольтном питании (2,5÷5 В). Кроме этого, в диапазоне рабочих, прежде всего низких температур, а также при воздействии потока нейтронов он имеет повышенные значения напряжения смещения нуля (Uсм) (единицы-десятки милливольт). В конечном итоге это снижает прецизионность известного ОУ.

Основная задача предлагаемого изобретения состоит в расширении диапазона изменения выходного напряжения до уровней, близких к напряжениям на положительной (3) и отрицательной (9) шинах питания.

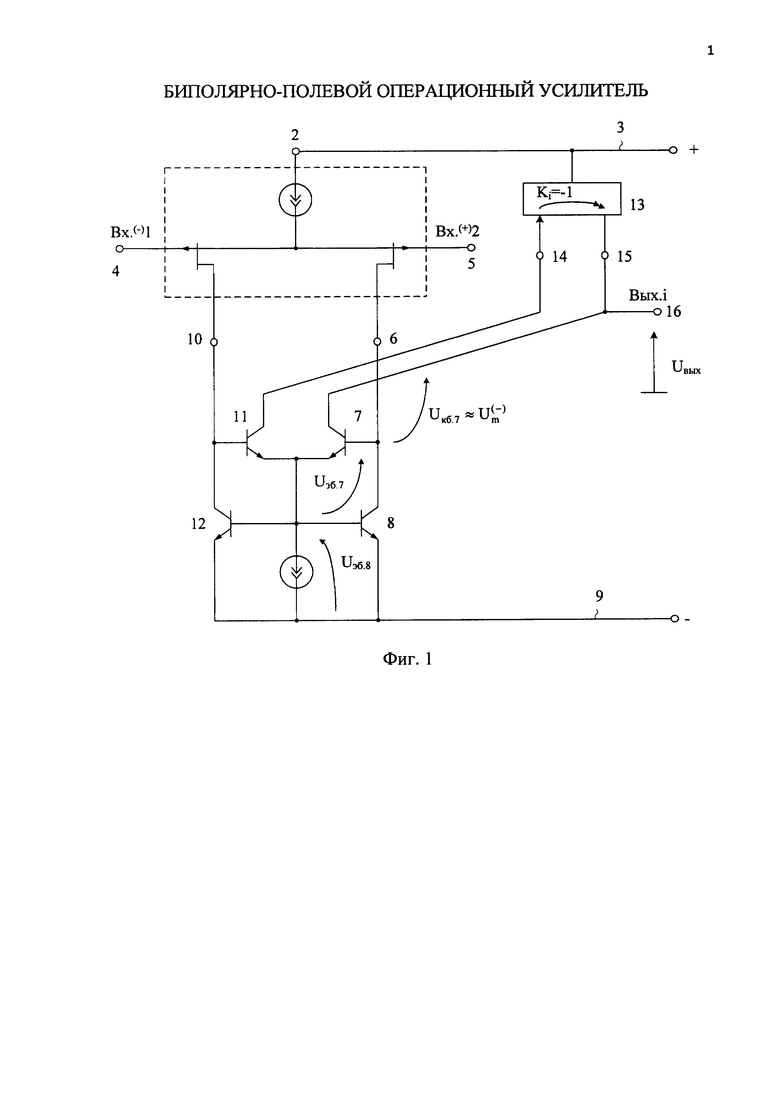

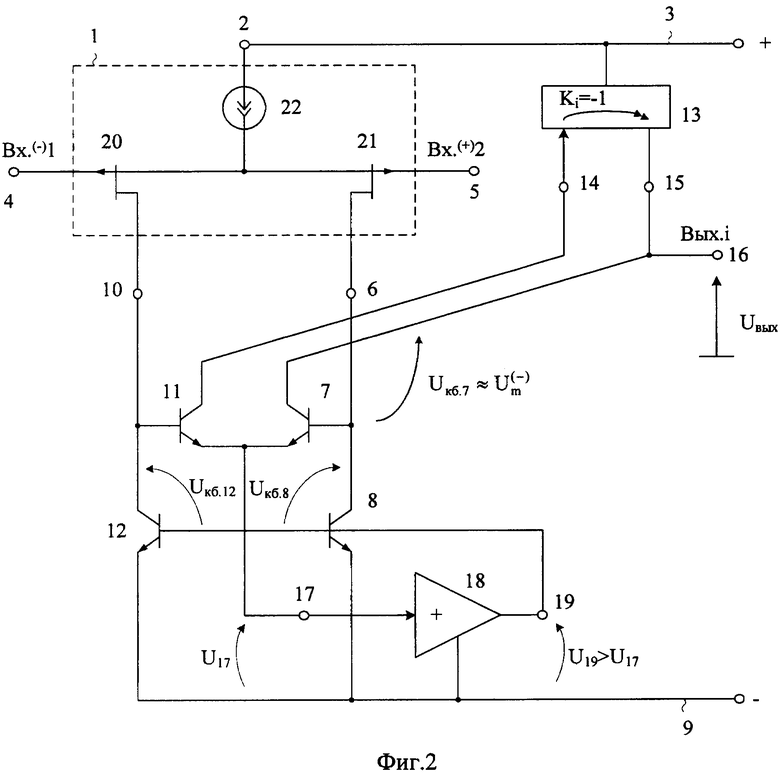

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 выходного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 выходного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, цепь динамической нагрузки 13, согласованную с первой 3 шиной источника питания, вход которой 14 соединен с коллектором второго 11 выходного транзистора, а выход 15 связан с выходом устройства 16 и коллектором первого 7 выходного транзистора, причем базы первого 8 и второго 12 транзисторов первого и второго источников опорного тока соединены друг с другом, а эмиттеры первого 7 и второго 11 выходных транзисторов объединены друг с другом, предусмотрены новые элементы и связи - объединенные эмиттеры первого 7 и второго 11 выходных транзисторов подключены ко входу 17 дополнительного неинвертирующего усилителя 18, выход которого 19 связан с базами первого 8 и второго 12 транзисторов первого и второго источников опорного тока, причем выходное статическое напряжение дополнительного неинвертирующего усилителя 18 превышает его входное статическое напряжение, измеренное относительно второй 9 шины источника питания.

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

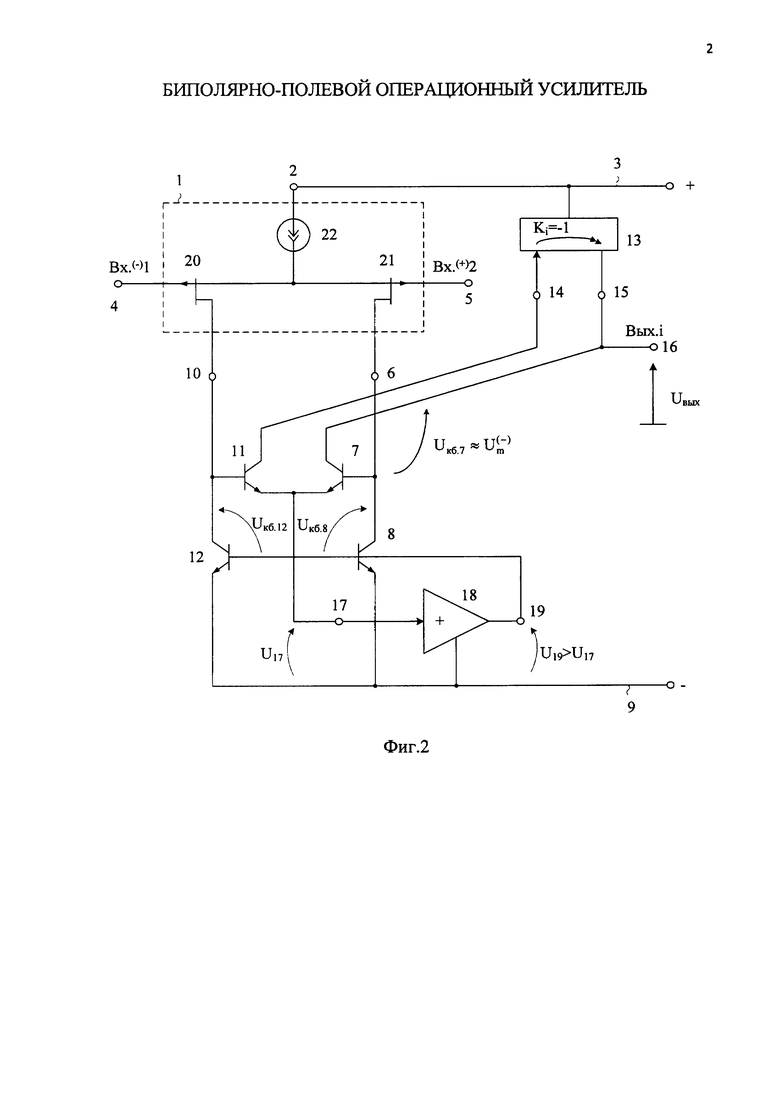

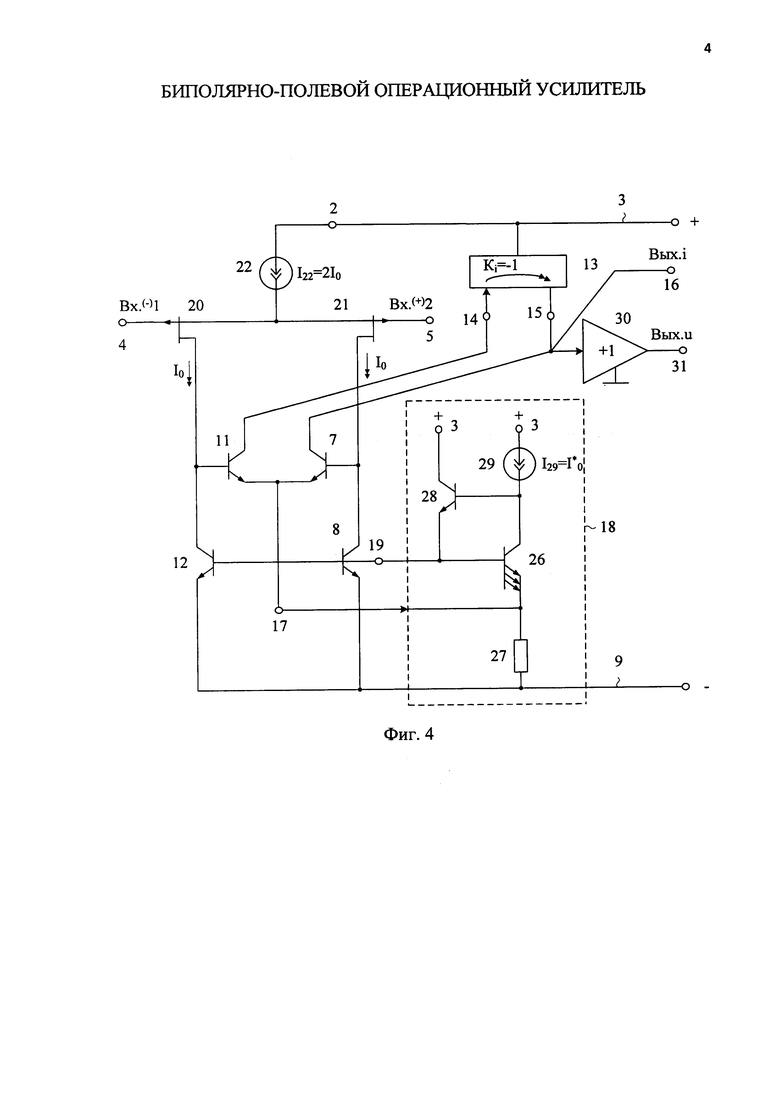

На чертеже фиг. 3 приведена схема заявляемого устройства в соответствии с п. 2, а на чертеже фиг. 4 - п. 3 формулы изобретения.

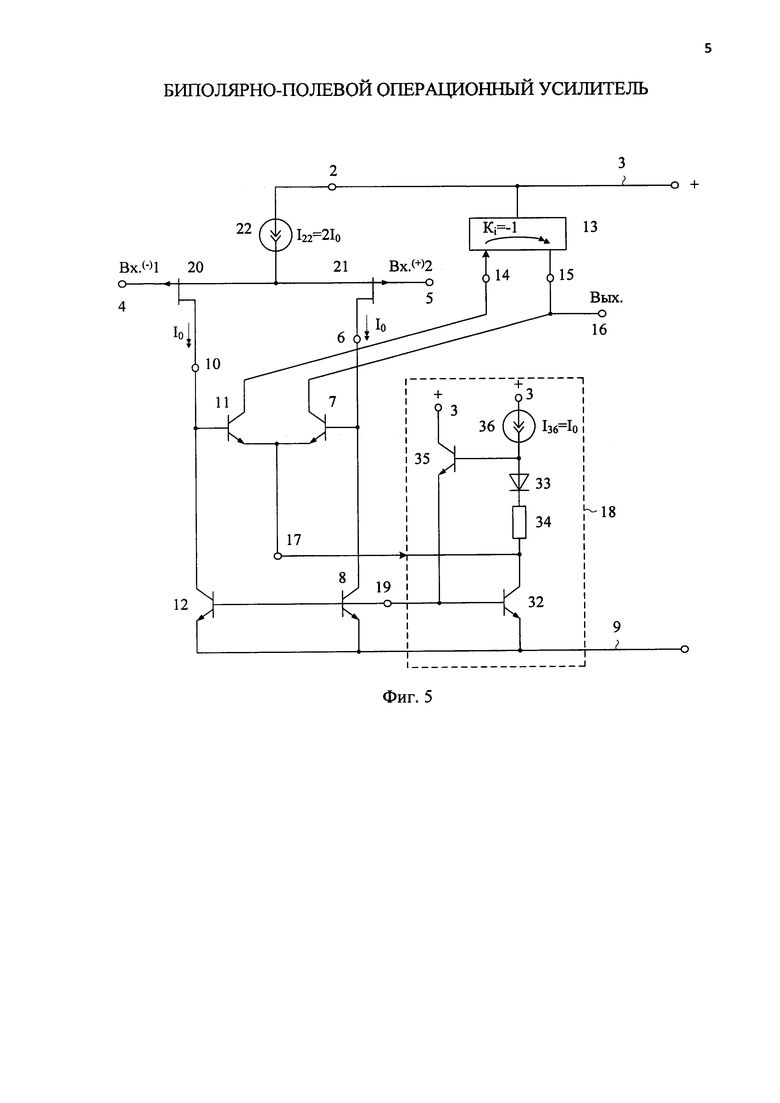

На чертеже фиг. 5 представлена схема заявляемого устройства в соответствии с п. 4 формулы изобретения.

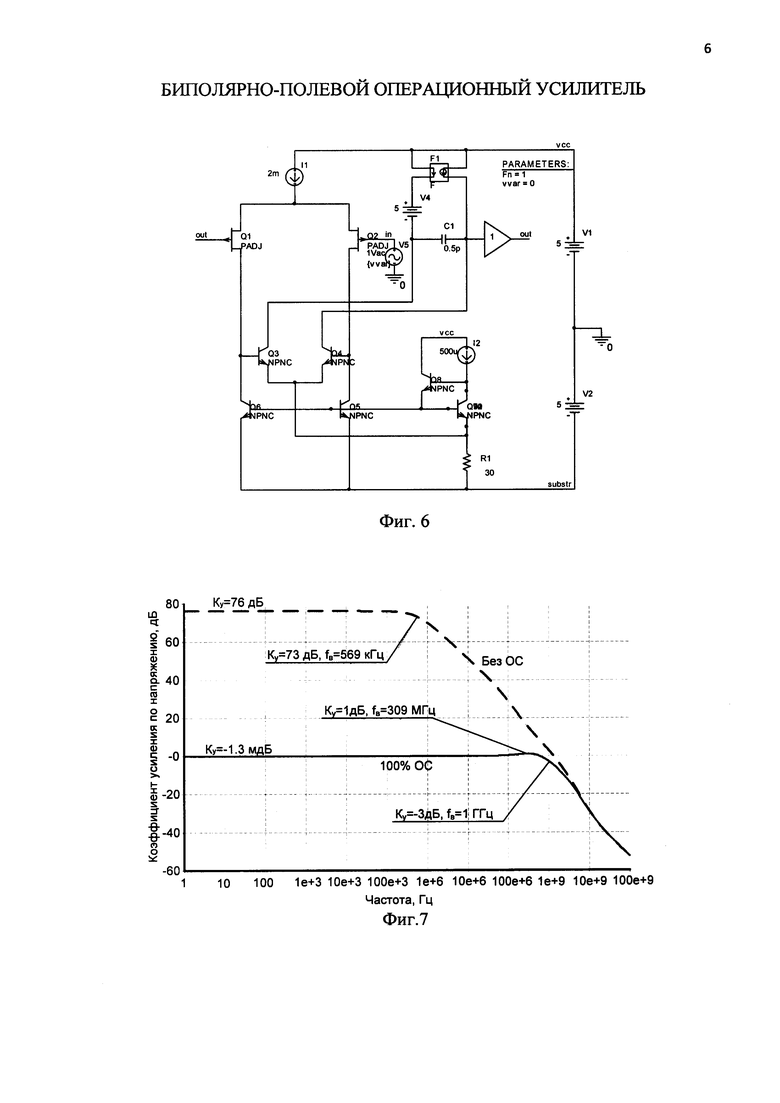

На чертеже фиг. 6 приведена схема заявляемого устройства фиг. 4 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск).

На чертеже фиг. 7 показаны амплитудно-частотные характеристики операционного усилителя фиг. 6 без отрицательной обратной связи и со 100% отрицательной обратной связью.

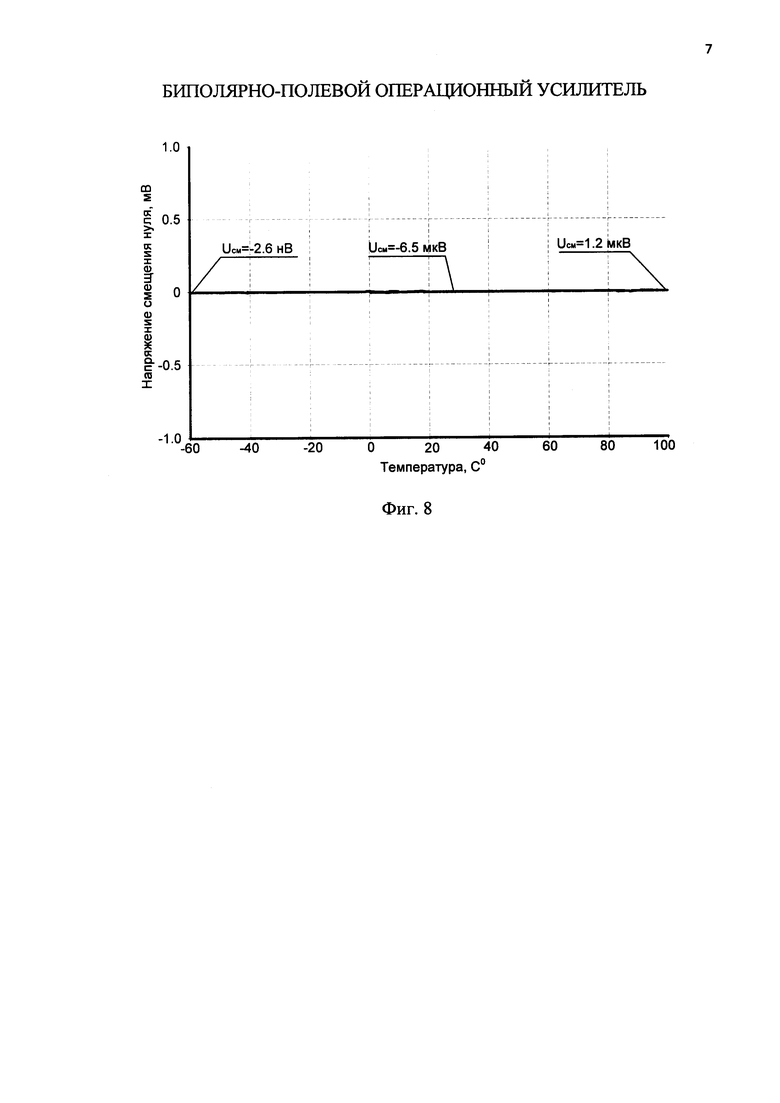

На чертеже фиг. 8 приведена зависимость напряжения смещения нуля ОУ фиг. 6 от температуры.

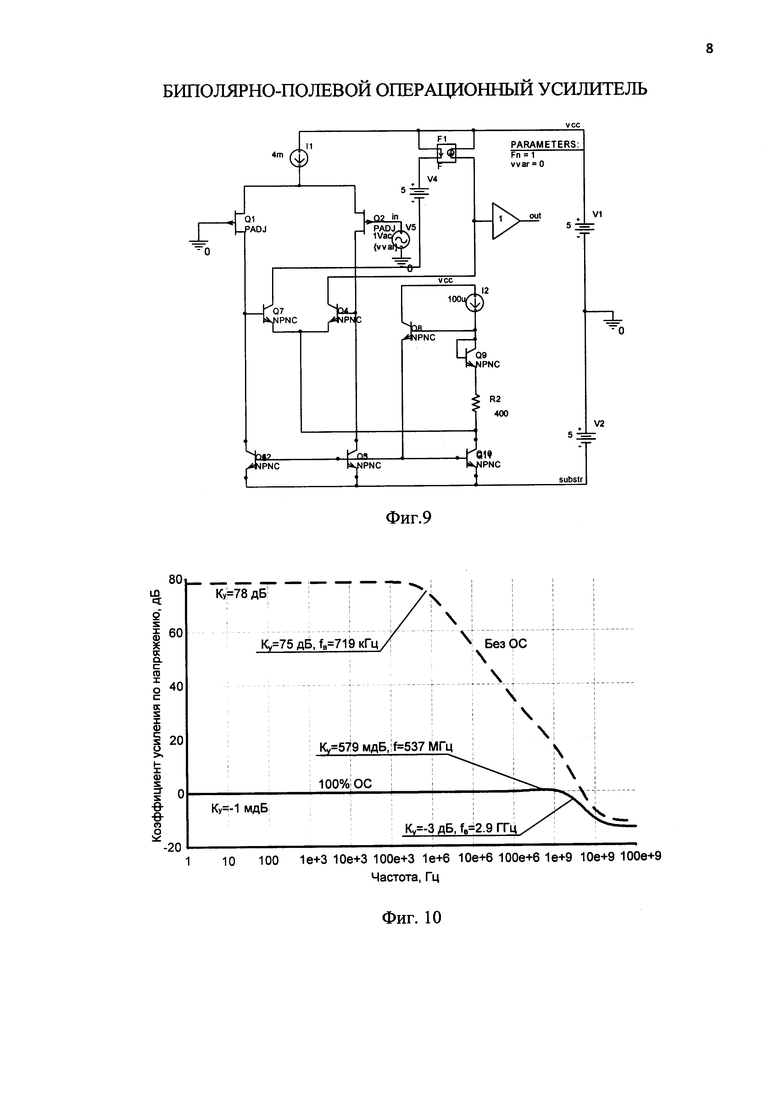

На чертеже фиг. 9 представлена схема заявляемого устройства фиг. 5 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск).

На чертеже фиг. 10 представлены амплитудно-частотные характеристики замкнутого и разомкнутого ОУ фиг. 9.

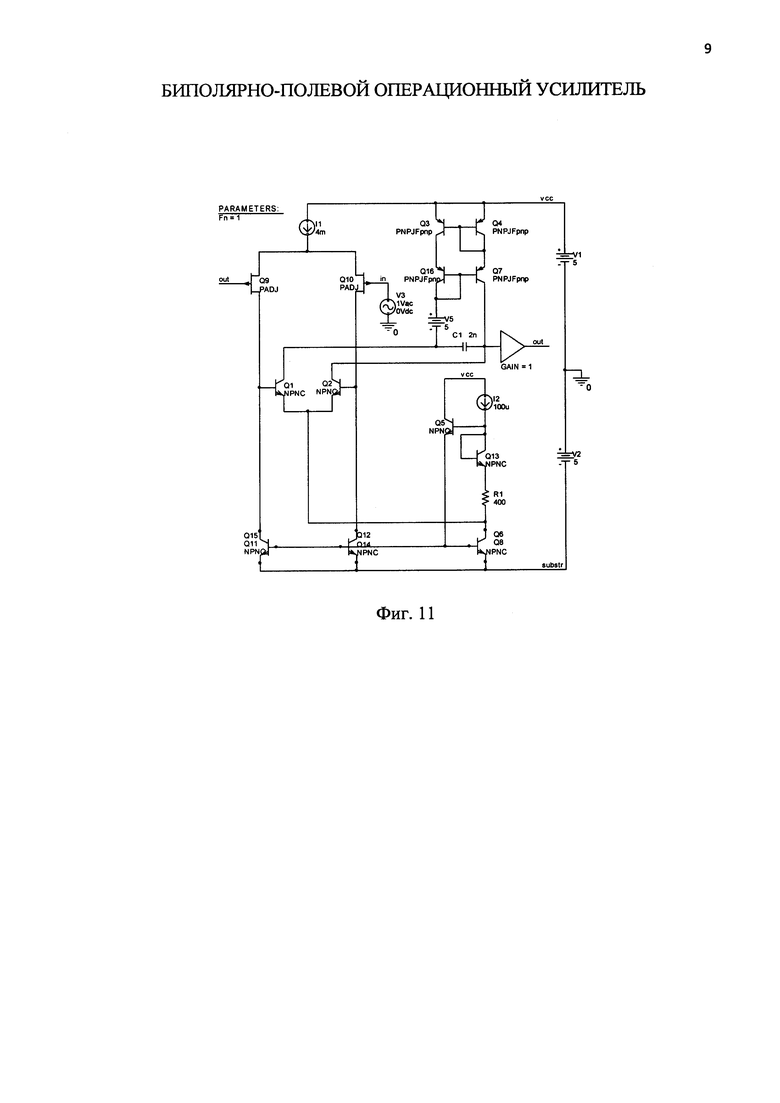

На чертеже фиг. 11 показана схема заявляемого устройства фиг. 5 в среде PSpice при выполнении токового зеркала 13 на основе р-n-р транзисторов АБМК_1_3, которые не отличаются высокой радиационной стойкостью [9].

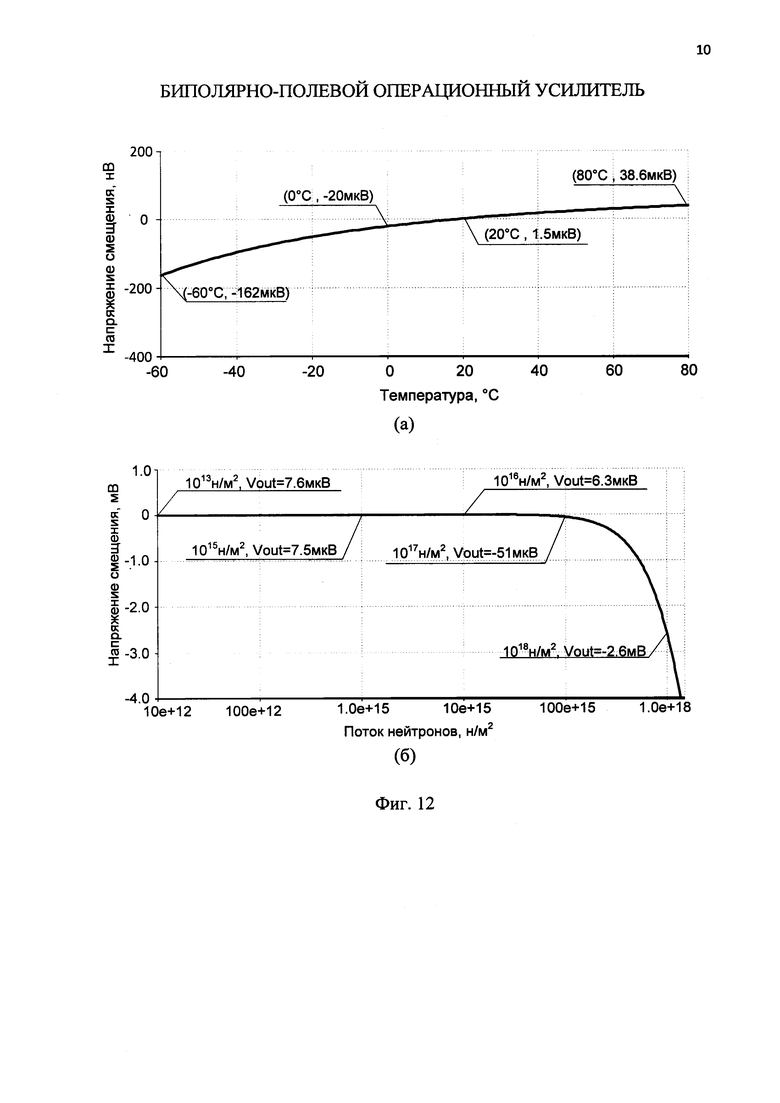

На чертеже фиг. 12 приведена зависимость напряжения смещения нуля ОУ фиг. 11 от температуры в диапазоне минус 60-80°С (а) и потока нейтронов (б).

Биполярно-полевой операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 выходного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 выходного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, цепь динамической нагрузки 13, согласованную с первой 3 шиной источника питания, вход которой 14 соединен с коллектором второго 11 выходного транзистора, а выход 15 связан с выходом устройства 16 и коллектором первого 7 выходного транзистора, причем базы первого 8 и второго 12 транзисторов первого и второго источников опорного тока соединены друг с другом, а эмиттеры первого 7 и второго 11 выходных транзисторов объединены друг с другом. Объединенные эмиттеры первого 7 и второго 11 выходных транзисторов подключены ко входу 17 дополнительного неинвертирующего усилителя 18, выход которого 19 связан с базами первого 8 и второго 12 транзисторов первого и второго источников опорного тока, причем выходное статическое напряжение дополнительного неинвертирующего усилителя 18 превышает его входное статическое напряжение, измеренное относительно второй 9 шины источника питания. В данной схеме входной дифференциальный каскад 1 выполнен на полевых транзисторах 20 и 21 и источнике опорного тока 22.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, вход 17 дополнительного неинвертирующего усилителя 18 подключен к эмиттеру первого 23 вспомогательного транзистора и через первый 24 вспомогательный резистор соединен со второй 9 шиной источника питания, база и коллектор первого 23 вспомогательного транзистора соединены с выходом 19 дополнительного неинвертирующего усилителя 18 и подключены к первому 25 вспомогательному источнику опорного тока, причем площадь эмиттерного перехода первого 23 вспомогательного транзистора значительно превышает площадь эмиттерных переходов первого 8 и второго 12 транзисторов первого и второго источников опорного тока.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, вход 17 дополнительного неинвертирующего усилителя 18 подключен к эмиттеру второго 26 вспомогательного транзистора и через второй 27 вспомогательный резистор соединен со второй 9 шиной источника питания, база второго 26 вспомогательного транзистора соединена с выходом 19 дополнительного неинвертирующего усилителя 18 и эмиттером третьего 28 вспомогательного транзистора, коллектор которого соединен с первой 3 шиной источника питания, коллектор второго 26 вспомогательного транзистора соединен с базой третьего 28 вспомогательного транзистора и подключен ко второму 29 источнику опорного тока, причем площадь эмиттерного перехода второго 26 вспомогательного транзистора значительно превышает площадь эмиттерных переходов первого 8 и второго 12 транзисторов первого и второго источников опорного тока.

В схеме фиг. 4 для уменьшения выходного сопротивления может использоваться буферный усилитель 30, у которого выходное сопротивление относительно выхода 31 мало.

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, вход 17 дополнительного неинвертирующего усилителя 18 соединен с коллектором четвертого 32 вспомогательного транзистора и через последовательно соединенные прямосмещенный р-n-переход 33 и третий 34 вспомогательный резистор подключен к базе пятого 35 вспомогательного транзистора, эмиттер которого подключен к базе четвертого 32 вспомогательного транзистора и выходу 19 дополнительного неинвертирующего усилителя 18, коллектор пятого 35 вспомогательного транзистора соединен с первой 3 шиной источника питания, а его база связана с третьим 36 источником опорного тока, причем эмиттер четвертого 32 вспомогательного транзистора подключен ко второй 9 шине источника питания.

Рассмотрим работу ОУ, фиг. 3.

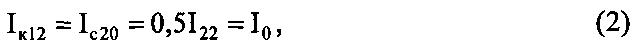

Статический режим транзисторов схемы (фиг. 3) устанавливается источником опорного тока 22 и первым 25 вспомогательным источником опорного тока. При этом токи стока (Ici) и токи коллекторов (Iкi) транзисторов схемы определяются уравнениями:

где Iс20, Ic21 - токи стока полевых транзисторов 20 и 21;

I0 - некоторый заданный опорный ток, например I0=1 мА;

Iк8, Iк12 - токи коллекторов первого 8 и второго 12 транзисторов первого и второго источников опорного тока.

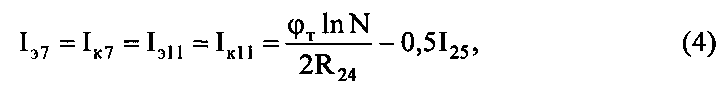

Если выбрать I25=I0, а отношение площадей эмиттерных переходов первого 23 вспомогательного транзистора и первого 8 (второго 12) транзистора первого (второго) источника опорного тока обозначить как N=S23/S8, то можно получить, что токи эмиттеров первого 7 и второго 11 выходных транзисторов зависят от N и сопротивления R24 первого 24 вспомогательного резистора:

где φт≈26 мВ - температурный потенциал.

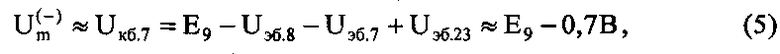

Амплитуда отрицательного выходного напряжения ОУ (фиг. 3)  определяется напряжением коллектор-база (Uкб.7) первого 7 выходного транзистора в статическом режиме:

определяется напряжением коллектор-база (Uкб.7) первого 7 выходного транзистора в статическом режиме:

где иэб.8 - напряжение эмиттер-база первого 8 транзистора первого источника опорного тока;

Uэб.7 - напряжение эмиттер-база первого 7 выходного транзистора;

Uэб.23 - напряжение эмиттер-база первого 23 вспомогательного транзистора;

Е9 - напряжение на второй 9 шине источника питания.

В схеме ОУ-прототипа (фиг. 1) этот параметр

Таким образом, заявляемое устройство имеет на 0,7 В более широкий диапазон изменения отрицательного выходного напряжения  , что достаточно актуально при низковольтном электропитании [Е9=(1.5÷3) В].

, что достаточно актуально при низковольтном электропитании [Е9=(1.5÷3) В].

Аналогичные улучшения по амплитуде  реализуются в схемах фиг. 4, фиг. 5.

реализуются в схемах фиг. 4, фиг. 5.

Предлагаемые схемотехнические решения обеспечивают высокую стабильность напряжения смещения нуля ОУ (фиг. 8, фиг. 12).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7.411.451, fig. 2.

2. Патент US 4.607.232.

3. Патент US 3.614.645, fig. 1, fig. 2.

4. Патент US 5.963.085, fig. 3.

5. Патент US 4.271.394, fig. 3.

6. Патент US 4.069.460, fig. 1.

7. Патент US 4.359.693, fig. 1.

8. Патент US 4.348.602, fig. 1.

9. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

10. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 1 / О. Дворников // Компоненты и технологии, №6, 200.5, http:/kit-e.ru/articles/device/2005_6_218.php

11. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 2 / О. Дворников // Компоненты и технологии, №7, 2005, http.7/kit-e.ru/articles/device/2005_7_216.php

12. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 3 / О. Дворников // Компоненты и технологии, №8, 2005, http://kit-e.ru/articles/device/2005_8_184.php

13. Схемотехника биполярно-полевых аналоговых микросхем. Часть 4. Источники тока для особых применений / О. Дворников // Chip News, №3(96), 2005. - С. 66-68.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| СИММЕТРИЧНАЯ АКТИВНАЯ НАГРУЗКА ДИФФЕРЕНЦИАЛЬНЫХ УСИЛИТЕЛЕЙ ДЛЯ БИПОЛЯРНО-ПОЛЕВЫХ РАДИАЦИОННО-СТОЙКИХ ТЕХНОЛОГИЧЕСКИХ ПРОЦЕССОВ | 2014 |

|

RU2572380C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592455C1 |

Изобретение относится к области радиоэлектроники. Технический результат заключается в расширении диапазона изменения выходного напряжения до уровней, близких к напряжениям на положительной и отрицательной шинах питания. Устройство содержит: входной дифференциальный каскад, общая истоковая цепь которого связана с первой шиной источника питания, первый и второй входы входного дифференциального каскада, первый токовый выход входного дифференциального каскада, связанный с базой первого выходного транзистора и коллектором первого транзистора первого источника опорного тока, эмиттер которого связан со второй шиной источника питания, второй токовый выход входного дифференциального каскада, связанный с базой второго выходного транзистора и коллектором второго транзистора второго источника опорного тока, эмиттер которого связан со второй шиной источника питания, цепь динамической нагрузки, согласованную с первой шиной источника питания, вход которой соединен с коллектором второго выходного транзистора, а выход связан с выходом устройства и коллектором первого выходного транзистора, причем базы первого и второго транзисторов первого и второго источников опорного тока соединены друг с другом, а эмиттеры первого и второго выходных транзисторов объединены друг с другом. 3 з.п. ф-лы, 12 ил.

1. Биполярно-полевой операционный усилитель, содержащий входной дифференциальный каскад (1), общая истоковая цепь которого (2) связана с первой (3) шиной источника питания, первый (4) и второй (5) входы входного дифференциального каскада (1), первый (6) токовый выход входного дифференциального каскада (1), связанный с базой первого (7) выходного транзистора и коллектором первого (8) транзистора первого источника опорного тока, эмиттер которого связан со второй (9) шиной источника питания, второй (10) токовый выход входного дифференциального каскада (1), связанный с базой второго (11) выходного транзистора и коллектором второго (12) транзистора второго источника опорного тока, эмиттер которого связан со второй (9) шиной источника питания, цепь динамической нагрузки (13), согласованную с первой (3) шиной источника питания, вход которой (14) соединен с коллектором второго (11) выходного транзистора, а выход (15) связан с выходом устройства (16) и коллектором первого (7) выходного транзистора, причем базы первого (8) и второго (12) транзисторов первого и второго источников опорного тока соединены друг с другом, а эмиттеры первого (7) и второго (11) выходных транзисторов объединены друг с другом, отличающийся тем, что объединенные эмиттеры первого (7) и второго (11) выходных транзисторов подключены к входу (17) дополнительного неинвертирующего усилителя (18), выход которого (19) связан с базами первого (8) и второго (12) транзисторов первого и второго источников опорного тока, причем выходное статическое напряжение дополнительного неинвертирующего усилителя (18) превышает его входное статическое напряжение, измеренное относительно второй (9) шины источника питания.

2. Биполярно-полевой операционный усилитель по п. 1, отличающийся тем, что вход (17) дополнительного неинвертирующего усилителя (18) подключен к эмиттеру первого (23) вспомогательного транзистора и через первый (24) вспомогательный резистор соединен со второй (9) шиной источника питания, база и коллектор первого (23) вспомогательного транзистора соединены с выходом (19) дополнительного неинвертирующего усилителя (18) и подключены к первому (25) вспомогательному источнику опорного тока, причем площадь эмиттерного перехода первого (23) вспомогательного транзистора значительно превышает площадь эмиттерных переходов первого (8) и второго (12) транзисторов первого и второго источников опорного тока.

3. Биполярно-полевой операционный усилитель по п. 1, отличающийся тем, что вход (17) дополнительного неинвертирующего усилителя (18) подключен к эмиттеру второго (26) вспомогательного транзистора и через второй (27) вспомогательный резистор соединен со второй (9) шиной источника питания, база второго (26) вспомогательного транзистора соединена с выходом (19) дополнительного неинвертирующего усилителя (18) и эмиттером третьего (28) вспомогательного транзистора, коллектор которого соединен с первой (3) шиной источника питания, коллектор второго (26) вспомогательного транзистора соединен с базой третьего (28) вспомогательного транзистора и подключен ко второму (29) источнику опорного тока, причем площадь эмиттерного перехода второго (26) вспомогательного транзистора значительно превышает площадь эмиттерных переходов первого (8) и второго (12) транзисторов первого и второго источников опорного тока.

4. Биполярно-полевой операционный усилитель по п. 1, отличающийся тем, что вход (17) дополнительного неинвертирующего усилителя (18) соединен с коллектором четвертого (32) вспомогательного транзистора и через последовательно соединенные прямосмещенный p-n-переход (33) и третий (34) вспомогательный резистор подключен к базе пятого (35) вспомогательного транзистора, эмиттер которого подключен к базе четвертого (32) вспомогательного транзистора и выходу (19) дополнительного неинвертирующего усилителя (18), коллектор пятого (35) вспомогательного транзистора соединен с первой (3) шиной источника питания, а его база связана с третьим (36) источником опорного тока, причем эмиттер четвертого (32) вспомогательного транзистора подключен ко второй (9) шине источника питания.

| US 7411451 B2, 12.08.2008 | |||

| US 6542030 B2, 01.04.2003 | |||

| US 6801087 B2, 05.09.2004. |

Авторы

Даты

2016-08-27—Публикация

2015-07-23—Подача