Предлагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла многих устройств автоматики, вычислительной техники, систем связи и приборостроения, в т.ч. работающих при высоких температурах.

В современной микроэлектронике получили широкое распространение операционные усилители (ОУ), которые включают входной дифференциальный каскад на полевых (или биполярных) транзисторах с источником опорного тока в общей истоковой (эмиттерной) цепи и промежуточный каскад, выполненный на основе схемы так называемого «перегнутого» каскода [1-54]. Операционные усилители данного класса имеют широкий диапазон рабочих частот, а при использовании JFet входных транзисторов – экстремально низкий уровень шумов. Кроме этого, у них эффективно используется напряжение питания. Предполагаемое изобретение относится к данному классу ОУ.

В практических схемах ОУ входной дифференциальный каскад реализуется как на биполярных, так и на полевых транзисторах, что определяется используемыми технологическими процессами. Однако, перспективный арсенид-галлиевый техпроцесс [55,56], осваиваемый Минским НИИ радиоматериалов (https://mniirm.by/) и рядом зарубежных фирм, обеспечивает создание только nJFet и биполярных p-n-p транзисторов. Отсутствие n-p-n транзисторов создает схемотехнические проблемы построения GaAs ОУ. Это не позволяет создать высокотемпературные GaAs изделия, а также высокотемпературные ОУ на других широкозонных полупроводниках (SiC, GaN и др.) с аналогичным сочетанием доступных активных элементов, востребованные в ряде важных отраслей науки и техники - космическом приборостроении, нефтегазовой, автомобильной и авиационной промышленности.

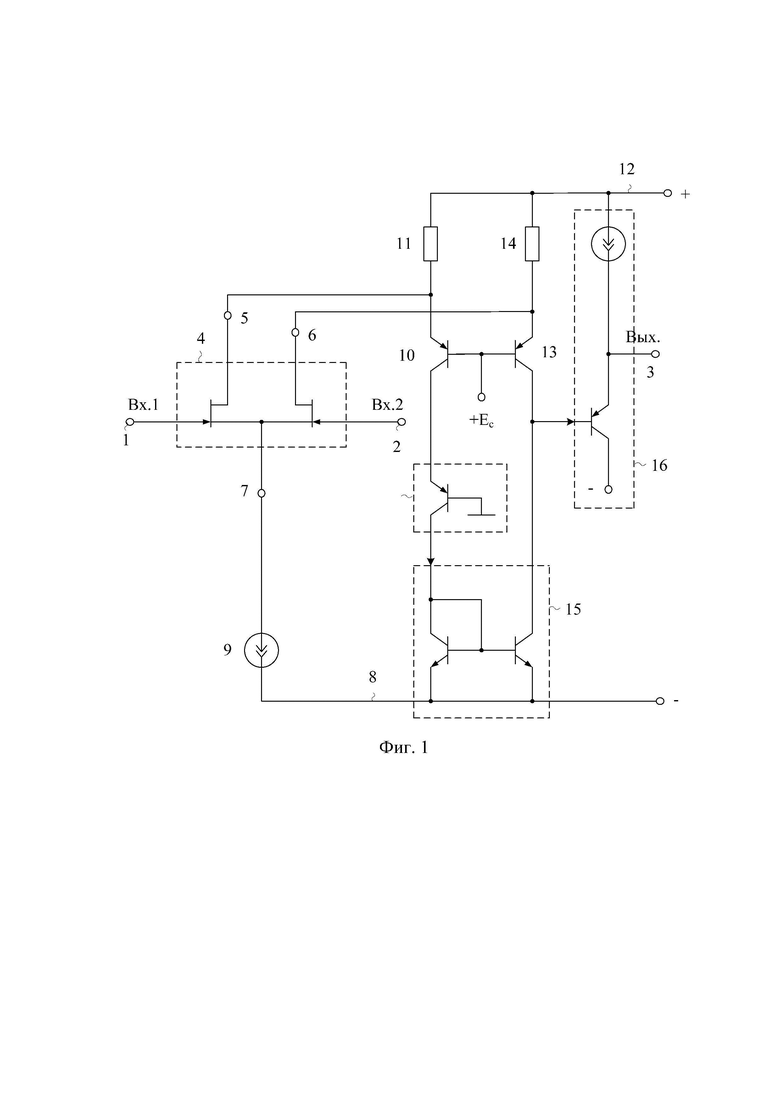

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в публикации «Bob Cordell. LSK489 Application Note. Low Noise Dual Monolithic JFET. URL: https://www.cordellaudio.com/JFETs/LSK489appnote.pdf. 16 p., fig. 10». Данная схема ОУ представлена также в патенте US 4.406.990, fig. 6 1983 г. Он содержит первый 1 и второй 2 входы устройства, а также потенциальный выход 3 устройства, входной дифференциальный каскад 4 с первым 5 и вторым 6 токовыми выходами и токовым входом 7 для установления статического режима, который связан с первой 8 шиной источника питания через первый 9 источник опорного тока, причем первый 1 и второй 2 входы устройства соединены с затворами соответствующих входных полевых транзисторов входного дифференциального каскада 4, первый 10 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен с первым 5 токовым выходом входного дифференциального каскада 4 и через первый 11 токостабилизирующий резистор подключен ко второй 12 шине источника питания, второй 13 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен со вторым 6 токовым выходом входного дифференциального каскада 4 и через второй 14 токостабилизирующий резистор связан со второй 12 шиной источника питания, причем база первого 10 выходного биполярного транзистора промежуточного каскада соединена с базой второго 13 выходного биполярного транзистора промежуточного каскада, второй 15 источник опорного тока, включенный между коллектором второго 13 выходного биполярного транзистора промежуточного каскада и первой 8 шиной источника питания, буферный усилитель 16, выход которого связан с выходом устройства 3.

Существенный недостаток ОУ – прототипа состоит в том, что он не реализуется в рамках перспективного арсенид-галлиевого технологического процесса [55,56] из-за отсутствия n-p-n арсенид-галлиевых биполярных транзисторов. Кроме этого, известный ОУ характеризуется повышенным уровнем систематической составляющей напряжения смещения нуля Uсм, что обусловлено применяемой в нем схемой установления статического режима на базах первого 10 и второго 13 выходных биполярных транзисторов промежуточного каскада.

Основная задача предполагаемого изобретения состоит в создании схемы прецизионного операционного усилителя с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления по напряжению в рамках совмещенного GaAs технологического процесса, разрешающего использовать только p-n-p биполярные и nJFet полевые транзисторы.

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, а также потенциальный выход 3 устройства, входной дифференциальный каскад 4 с первым 5 и вторым 6 токовыми выходами и токовым входом 7 для установления статического режима, который связан с первой 8 шиной источника питания через первый 9 источник опорного тока, причем первый 1 и второй 2 входы устройства соединены с затворами соответствующих входных полевых транзисторов входного дифференциального каскада 4, первый 10 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен с первым 5 токовым выходом входного дифференциального каскада 4 и через первый 11 токостабилизирующий резистор подключен ко второй 12 шине источника питания, второй 13 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен со вторым 6 токовым выходом входного дифференциального каскада 4 и через второй 14 токостабилизирующий резистор связан со второй 12 шиной источника питания, причем база первого 10 выходного биполярного транзистора промежуточного каскада соединена с базой второго 13 выходного биполярного транзистора промежуточного каскада, второй 15 источник опорного тока, включенный между коллектором второго 13 выходного биполярного транзистора промежуточного каскада и первой 8 шиной источника питания, буферный усилитель 16, выход которого связан с выходом устройства 3, предусмотрены новые элементы и связи между ними - в схему введены третий 17 и четвертый 18 источники опорного тока, а также первый 19 и второй 20 дополнительные биполярные транзисторы, причем база первого 19 дополнительного биполярного транзистора соединена с коллектором первого 10 выходного биполярного транзистора промежуточного каскада и через третий 17 источник опорного тока подключена к первой 8 шине источника питания, база второго 20 дополнительного биполярного транзистора соединена с коллектором второго 13 выходного биполярного транзистора промежуточного каскада, коллектор второго 20 дополнительного биполярного транзистора соединен со входом буферного усилителя 16 и связан с первой 8 шиной через четвертый 18 источник опорного тока, коллектор первого 19 дополнительного биполярного транзистора согласован с общей шиной источников питания, объединенные эмиттеры первого 19 и второго 20 дополнительных биполярных транзисторов соединены с базами первого 10 и второго 13 выходных биполярных транзисторов промежуточного каскада и связаны со второй 12 шиной источника питания через последовательно соединенные дополнительный резистор 21 и два параллельно включенных p-n перехода 22, реализованных на биполярных транзисторах, у которых коллекторы соединены с базой.

На чертеже фиг. 1 показана схема операционного усилителя – прототипа.

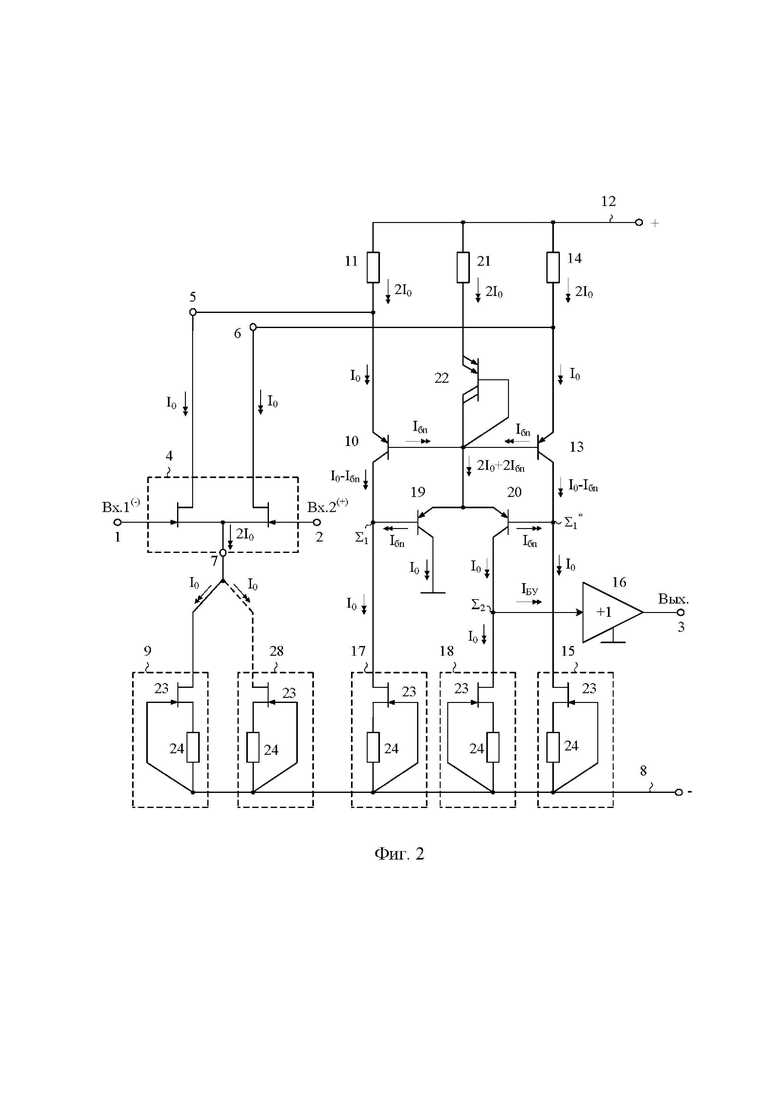

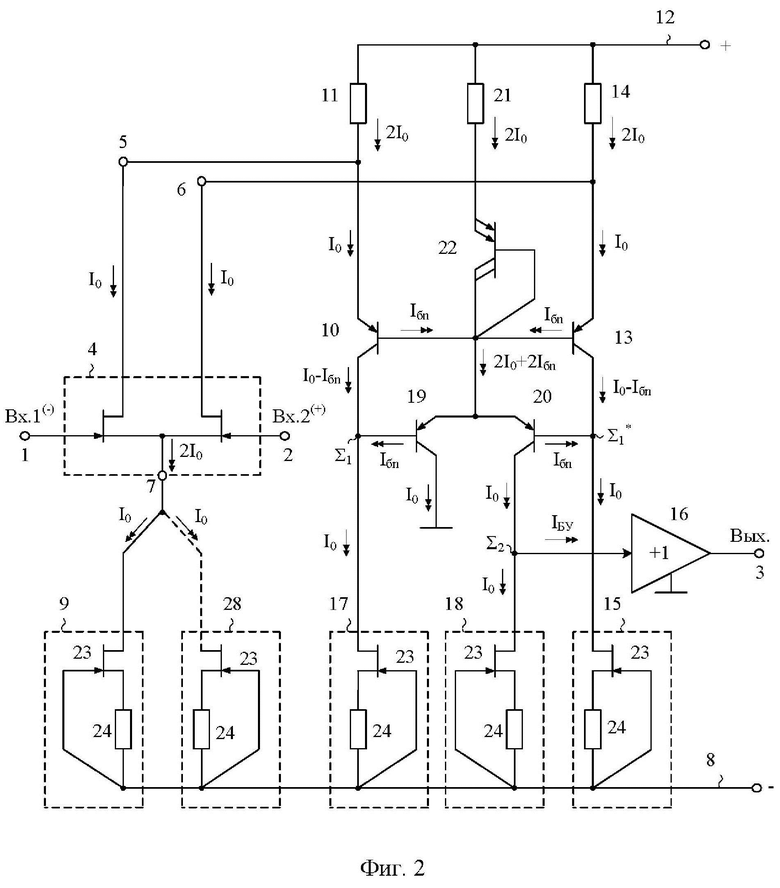

На чертеже фиг. 2 приведена схема заявляемого ОУ по п. 1 формулы изобретения, в котором первый 9, второй 15, третий 17 и четвертый 18 источники опорного тока выполнены в соответствии с п. 2 формулы изобретения (фиг. 3), а параллельно первому 9 источнику опорного тока включен дополнительный источник опорного тока 28, что соответствует п. 4 формулы изобретения.

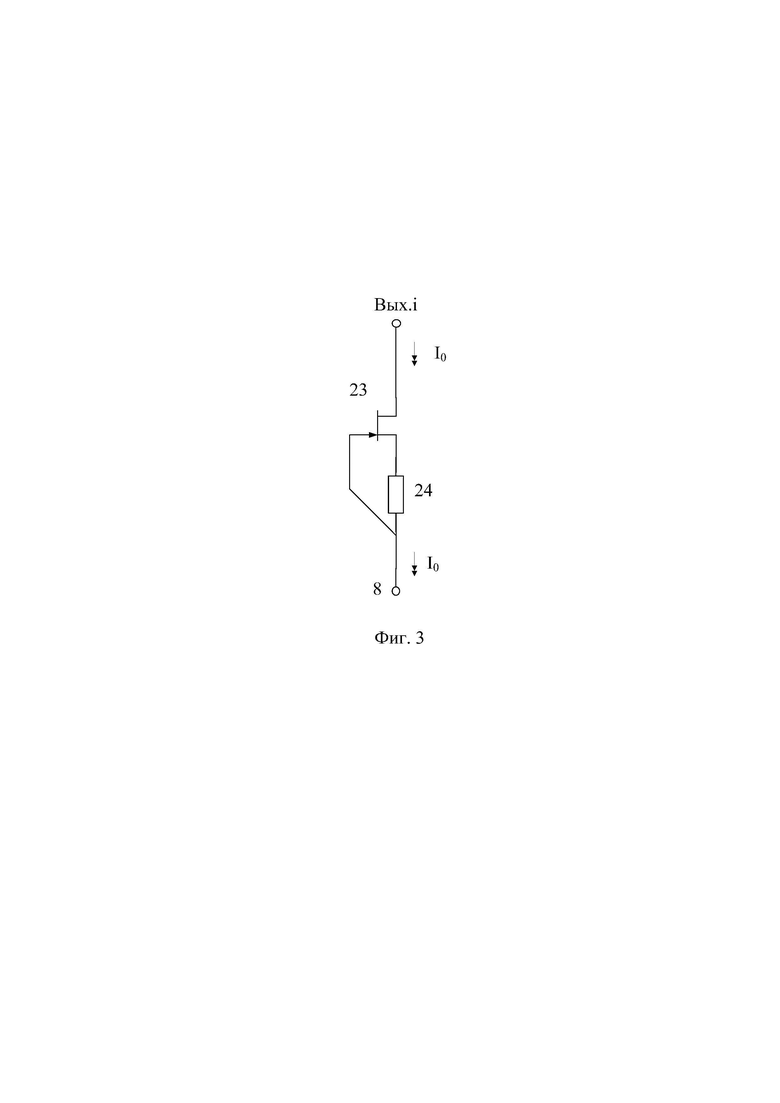

На чертеже фиг. 3 представлен частный случай выполнения первого 9, второго 15, третьего 17 и четвертого 18 источников опорного тока в ОУ фиг. 2, схема которого соответствует п. 2 формулы изобретения.

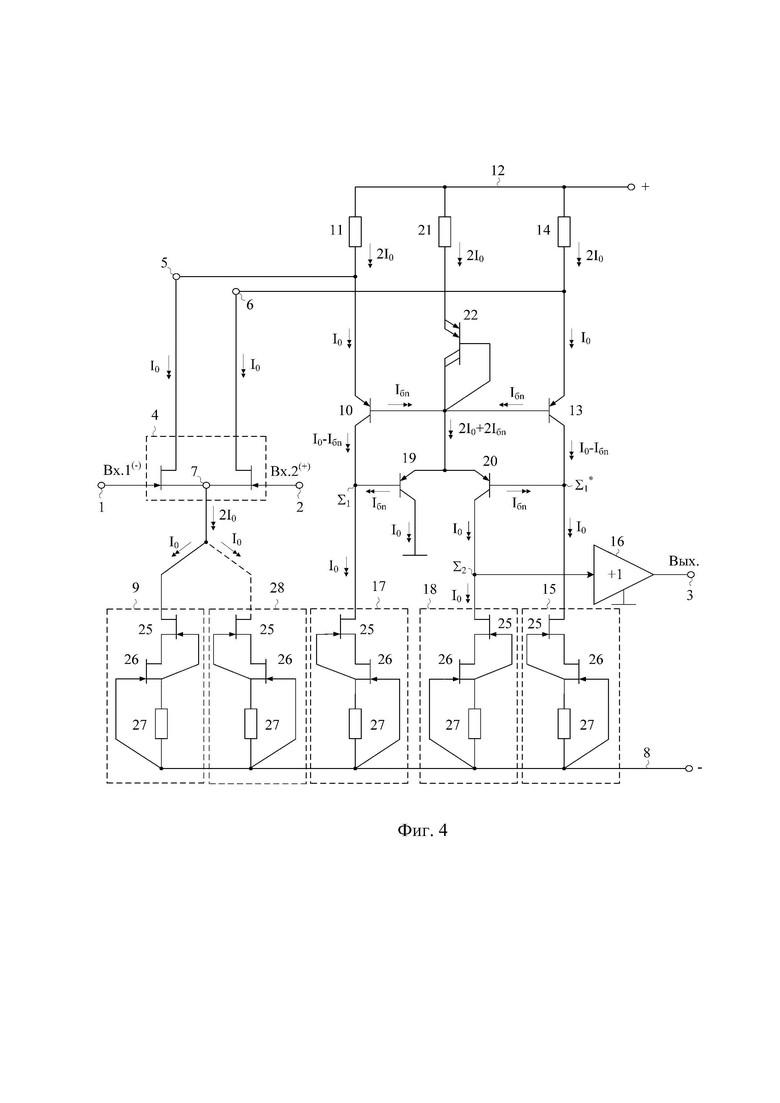

На чертеже фиг. 4 показана схема ОУ, в котором первый 9, второй 15, третий 17 и четвертый 18 источники опорного тока, а также дополнительный источник опорного тока 28 выполнены по идентичным схемам, соответствующим п. 3 формулы изобретения (чертеж фиг. 5).

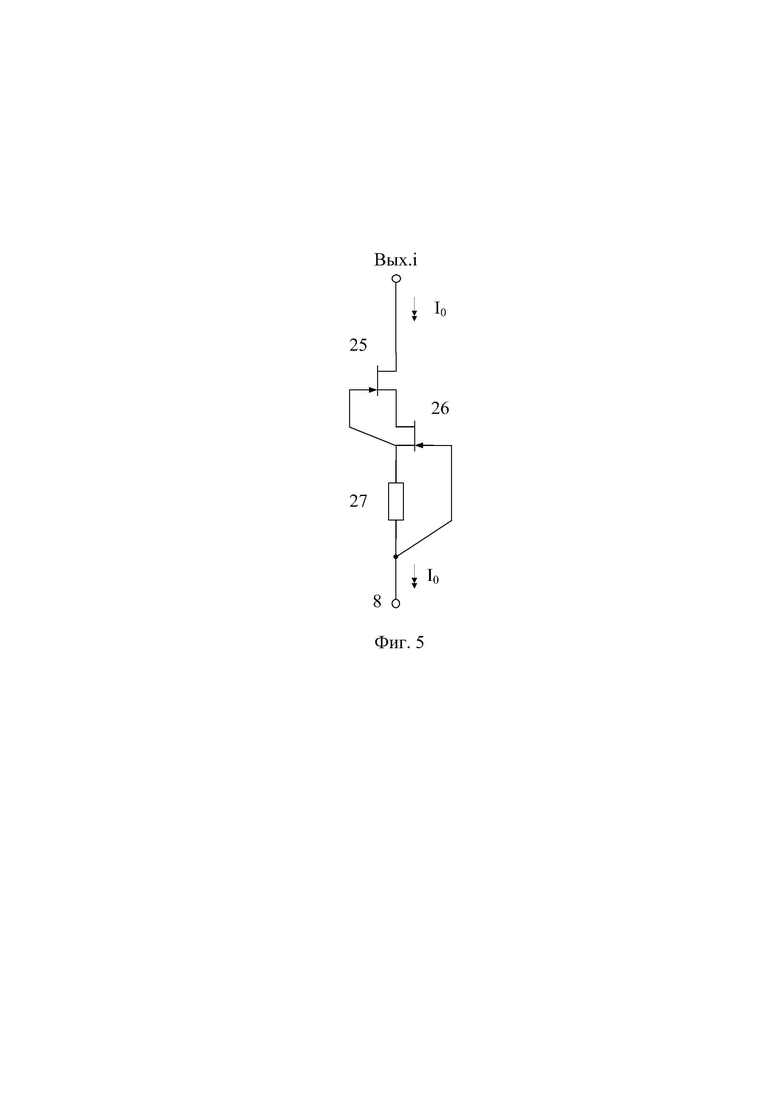

На чертеже фиг. 5 приведена схема первого 9, второго 15, третьего 17, четвертого 18 идентичных источников опорного тока на арсенид-галлиевых полевых транзисторах 23 и 24, включенных по каскодной схеме в ОУ, соответствующем п. 3 формулы изобретения.

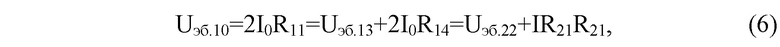

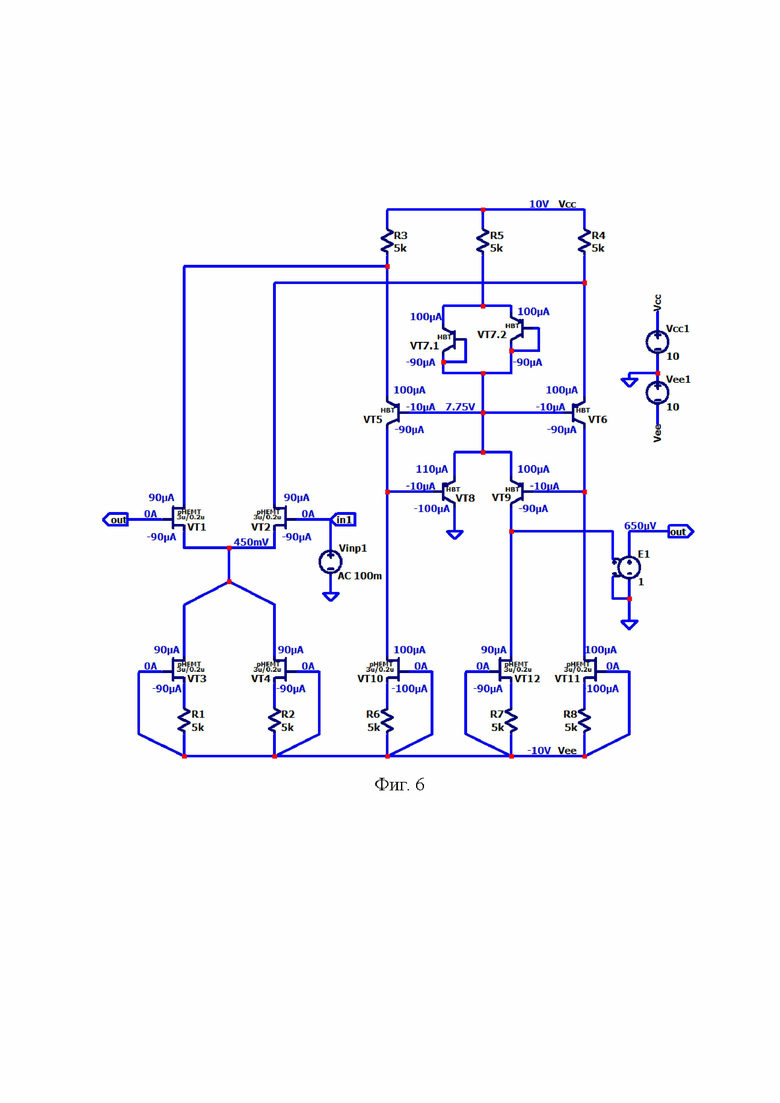

На чертеже фиг. 6 представлен статический режим схемы GaAs ОУ фиг. 2 в среде LTspice при t= 27°C, R1÷R8=5кОм, транзисторы VT1-VT4 и VT10-VT12 с шириной/длиной канала 3мкм/0.2мкм. Здесь Uсм=650 мкВ

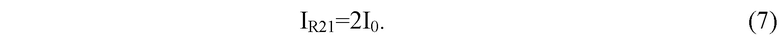

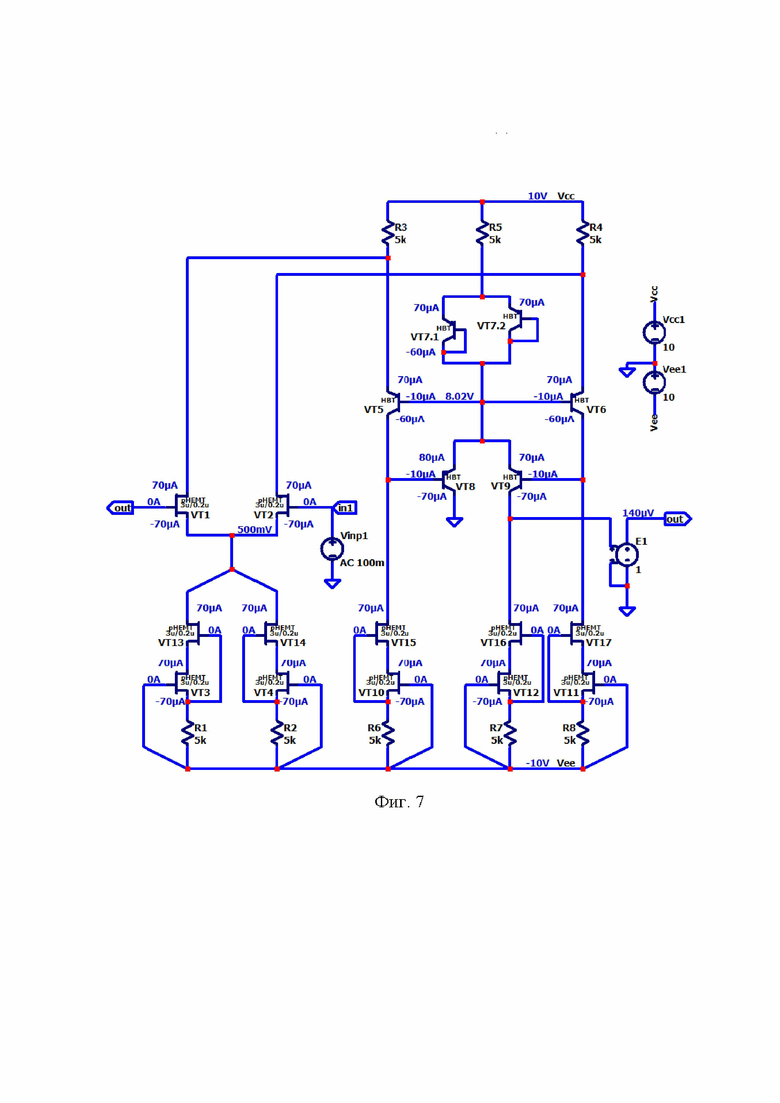

На чертеже фиг. 7 показан статический режим схемы ОУ фиг. 4 в среде LTspice при t= 27°C, R1÷R8=5кОм, транзисторы VT1-VT4 и VT10-VT17 с шириной/длиной канала 3мкм/0.2мкм. Здесь Uсм=140 мкВ.

Арсенид-галлиевый операционный усилитель на основе «перегнутого» каскода фиг. 2 содержит первый 1 и второй 2 входы устройства, а также потенциальный выход 3 устройства, входной дифференциальный каскад 4 с первым 5 и вторым 6 токовыми выходами и токовым входом 7 для установления статического режима, который связан с первой 8 шиной источника питания через первый 9 источник опорного тока, причем первый 1 и второй 2 входы устройства соединены с затворами соответствующих входных полевых транзисторов входного дифференциального каскада 4, первый 10 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен с первым 5 токовым выходом входного дифференциального каскада 4 и через первый 11 токостабилизирующий резистор подключен ко второй 12 шине источника питания, второй 13 выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен со вторым 6 токовым выходом входного дифференциального каскада 4 и через второй 14 токостабилизирующий резистор связан со второй 12 шиной источника питания, причем база первого 10 выходного биполярного транзистора промежуточного каскада соединена с базой второго 13 выходного биполярного транзистора промежуточного каскада, второй 15 источник опорного тока, включенный между коллектором второго 13 выходного биполярного транзистора промежуточного каскада и первой 8 шиной источника питания, буферный усилитель 16, выход которого связан с выходом устройства 3. В схему введены третий 17 и четвертый 18 источники опорного тока, а также первый 19 и второй 20 дополнительные биполярные транзисторы, причем база первого 19 дополнительного биполярного транзистора соединена с коллектором первого 10 выходного биполярного транзистора промежуточного каскада и через третий 17 источник опорного тока подключена к первой 8 шине источника питания, база второго 20 дополнительного биполярного транзистора соединена с коллектором второго 13 выходного биполярного транзистора промежуточного каскада, коллектор второго 20 дополнительного биполярного транзистора соединен со входом буферного усилителя 16 и связан с первой 8 шиной через четвертый 18 источник опорного тока, коллектор первого 19 дополнительного биполярного транзистора согласован с общей шиной источников питания, объединенные эмиттеры первого 19 и второго 20 дополнительных биполярных транзисторов соединены с базами первого 10 и второго 13 выходных биполярных транзисторов промежуточного каскада и связаны со второй 12 шиной источника питания через последовательно соединенные дополнительный резистор 21 и два параллельно включенных p-n перехода 22, реализованных на биполярных транзисторах, у которых коллекторы соединены с базой.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, первый 9, второй 15, третий 17, четвертый 18 источники опорного тока выполнены по идентичным схемам (фиг. 3) на основе выходного полевого транзистора 23, затвор которого связан с первой 8 шиной источника питания и через токостабилизирующий резистор 24 соединен с истоком выходного полевого транзистора 23.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, первый 9, второй 15, третий 17, четвертый 18 источники опорного тока выполнены по идентичным схемам (фиг. 5), каждый из которых содержит выходной транзистор 25, затвор которого соединен с истоком согласующего транзистора 26 и связан с первой 8 шиной источника питания через вспомогательный резистор 27, причем затвор согласующего транзистора 26 соединен с истоком согласующего транзистора 26 через вспомогательный резистор 27, а сток согласующего транзистора 26 подключен к истоку выходного транзистора 25.

Кроме этого, на чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, параллельно первому 9 источнику опорного тока включен идентичный ему дополнительный источник опорного тока 28, выполненный по идентичной ему схеме.

Рассмотрим работу заявляемого ОУ фиг. 2.

Статический режим схемы ОУ на чертеже фиг. 2 устанавливается четырьмя идентичными источниками опорного тока (9, 15, 17, 18), схемы которых представлены на чертеже фиг. 3. Это является принципиально важным условием получения малых уровней систематической составляющей напряжения смещения нуля для схемы ОУ фиг. 2, т.к. позволяет обеспечить взаимную компенсацию статических токов в высокоимпедансном узле Σ2, при которых систематическая составляющая Uсм, будет близка к нулю.

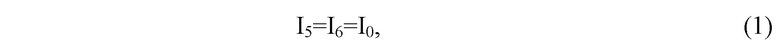

Если суммарный ток токового входа 7 для установления статического режима входного дифференциального каскада 4 равен I7=2I0, то токи первого 5 и второго 6 выходов:

где I0 – заданное разработчиком значение тока, определяющее токи источников опорного тока 9, 15, 17, 18, 28.

Поэтому коллекторные (Iк) и эмиттерные (Iэ) токи первого 10 и второго 13 выходных биполярных транзисторов промежуточного каскада

где Iбn – ток базы p-n-p арсенид-галлиевых транзисторов 10, 13, 19, 20 при токе эмиттера Iэi=I0.

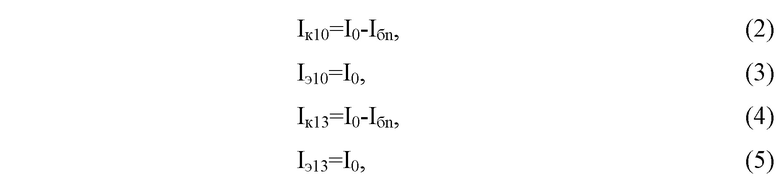

На основе второго закона Кирхгофа можно найти, что

где Uэб.10, Uэб.13, Uэб.22 – напряжение эмиттер-база транзисторов 10, 13, 22.

Учитывая, что R11=R14=R21, Uэб.10=Uэб.13=Uэб.22, из последнего уравнения можно найти ток в дополнительном резисторе 21

Как следствие, токи эмиттеров (Iэ) и коллекторов (Iк) первого 19 и второго 20 дополнительных биполярных транзисторов:

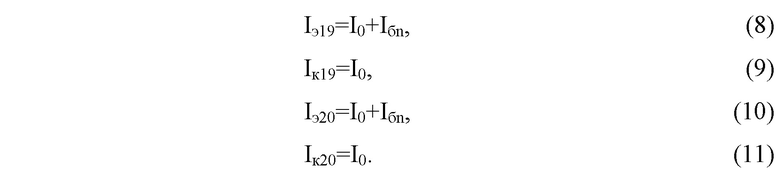

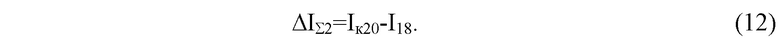

Поэтому разностный ток ΔIΣ2 в высокоимпедансном узле Σ2 (при нулевом входном токе буферного усилителя 16), определяющий систематическую составляющую напряжения смещения нуля (Uсм)

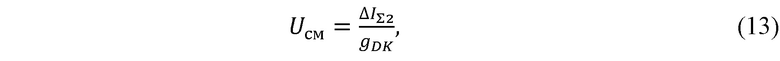

Причем

где gDK – крутизна усиления подсхемы, расположенной между входами 1 и 2 устройства и высокоимпедансным узлом Σ2.

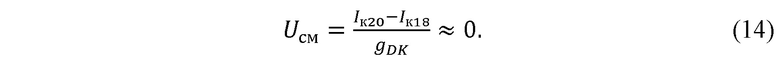

Подставляя в формулу (13) уравнения для токов Iк20 и I18 (12), находим, что

Уравнение (14) позволяет объяснить эффект уменьшения систематической составляющей напряжения смещения нуля в заявляемой схеме ОУ.

Таким образом, в предлагаемом ОУ обеспечиваются малые значения систематической составляющей напряжения смещения нуля.

В частных случаях источники опорного тока 9, 15, 17, 18 в схеме фиг. 2 могут быть выполнены в соответствии с чертежом фиг. 3 на полевом транзисторе 23 и резисторе 24. Кроме этого, возможно построение данных источников опорного тока в соответствии с чертежом фиг. 5, которые содержат транзисторы 25 и 26 и резистор 27.

Дополнительный источник опорного тока 28 в схеме фиг. 4 может быть выполнен на основе каскодного включения полевых транзисторов (фиг. 5), которое содержит выходной транзистор 25, затвор которого соединен с истоком согласующего транзистора 26 и связан с первой 8 шиной источника питания через вспомогательный резистор 27, причем затвор согласующего транзистора 26 соединен с истоком согласующего транзистора 26 через вспомогательный резистор 27, а сток согласующего транзистора 26 подключен к истоку выходного транзистора 25.

Таким образом, предлагаемая схема арсенид-галлиевого ОУ характеризуется экстремально низкой чувствительностью напряжения смещения нуля к абсолютным значениям идентичных сопротивлений применяемых первого 11 и второго 14 токостабилизирующих резисторов. Данный эффект, подтвержденный компьютерным моделированием, обеспечивается предлагаемой нетрадиционной схемой установления статического режима на базах первого 10 и второго 13 выходных транзисторов промежуточного каскада, которая использует первый 19 и второй 20 дополнительные биполярные транзисторы и два параллельно включенных p-n перехода 22.

Следовательно, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

Операционные усилители на «перегнутом» каскоде и входным ДК на pnp транзисторах

1. Патент US 6448583, fig.4, fig.5, fig.6, 2002 г.

2. Патент US 5091701, fig.1, 1992 г.

3. Патент US 5420542, fig.1A, 1995 г.

4. Патент US 5389894, fig.1, 1995 г.

5. Патент US 7545213, fig. 2, 2009 г.

6. Патент US 5282242, fig.2, 1994 г.

7. Патент US 6696888, fig.17, 2004 г .

8. Патент US 4293824, fig.2, 1981 г.

9. Патент US 7411451, fig. 1, 2008 г.

10. Патент RU 2354041, fig.2, 2009 г.

11. Патент US 6501333, fig.1, 2002 г.

12. Патент US 6456162, fig. 3, 2002 г.

13. Патент US 6542030, fig.2, 2003 г.

14. Патент US 3979069, fig.2, 1976 г.

15. Патент RU 2331969, fig.1, 2008 г.

16. Патент EP 0 586251, fig.2, 1994 г.

17. Патент US 3979689, fig.2, 1976 г.

18. Патент US 4600893, fig.7, 1986 г.

19. Патент US 5418491, fig.2, 1995 г.

20. Патент US 4406990, fig.4, 1983 г.

21. Патент US 5422600, fig.2, 1995 г.

22. Патент US 6218900, fig.1, 2001 г.

23. Патентная заявка US 2006/0202762, fig.2, 2006 г.

Операционные усилители на «перегнутом» каскоде с входным ДК на npn транзисторах

24. Патент РФ 2310268, fig.1, fig.2, 2007 г.

25. Патент US 6529076, 2001 г.

26. Патент US 4600893, fig.6,1986 г.

27. Патент US 2009/0256634, fig.1, 2009 г.

28. Патент US 6734737, fig.7, 2004 г.

29. Патент US 6483382, fig.1, fig.2, 2002 г.

30. Патент US 6304143, fig.1, 2001 г.

31. Патент JP 2009201119 A, fig.1, fig.2, 2009 г.

32. Патент US 5786729, fig.1, fig.2, 1998 г.

33. Патент RU 2421884, fig.1, 2011 г.

34. Патент US 7005921, fig.1B, 2006 г.

35. Патент US 6965266, fig. 1, 2005 г.

36. Патентная заявка US 2008/0024224, fig.1, 2008 г.

37. Патент US 6300831, fig.1, fig. 2, 2001 г.

38. Патент US 6788143, fig. 2, 2004 г.

39. Патент US 4959622, fig.18, 1990 г.

40. Патент US 5327100, fig.2, 1994 г.

Операционные усилители на «перегнутом» каскоде и входным ДК на полевых транзисторах

41. Патент US 5734296, fig.3, 2008 г.

42. Патент US 4406990, fig.6, 1983 г.

43. Патент US 6580325, fig.35, fig.36, 2003 г.

44. Патент US 6788143, fig.1, fig.4, 2004 г.

45. Патент US 4829266, fig. 10, 1989 г.

46. Патент US 7898330, fig. 1, 2011 г.

47. Патент US 4387309, 1983 г.

48. Патент US 6084475, fig.1, 2000 г.

49. Патентная заявка US 2005/0001682, fig.3, 2005 г.

50. Патент US 6717474, fig.4, 2004 г.

51. Патент US 6018268, fig.1, 2000 г.

52. Патент US 6714076, fig.2, 2004 г.

53. Патент EP 1227580, fig. 1, 2002 г.

Серийные ОУ на «перегнутых» каскодах

54. 154УД3, HA2520, HA5190, OP90, AD797, AD8631, AD8632, AD817, HA-2500, 140УД30, OPA42, LT1226.

Статья по арсенид-галлиевым микросхемам

55. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475–488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488.

56. Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. Арсенид-галлиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 47-54. doi:10.31114/2078-7707-2021-2-47-54.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

Изобретение относится к области радиотехники. Технический результат: создание схемы прецизионного операционного усилителя с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления по напряжению в рамках совмещенного GaAs технологического процесса, разрешающего использовать только p-n-p-биполярные и nJFet полевые транзисторы. Такой результат обеспечивается за счет введения в схему арсенид-галлиевого операционного усилителя третьего и четвертого источников опорного тока, а также дополнительных биполярных транзисторов, причем база первого дополнительного биполярного транзистора соединена с коллектором первого выходного биполярного транзистора промежуточного каскада и с третьим источником опорного тока, база второго дополнительного биполярного транзистора соединена с коллектором второго выходного биполярного транзистора промежуточного каскада, коллектор второго дополнительного биполярного транзистора соединен со входом буферного усилителя и с четвертым источником опорного тока, объединенные эмиттеры дополнительных транзисторов соединены с базами первого и второго выходных транзисторов промежуточного каскада и связаны с дополнительным резистором и параллельно включенными p-n-переходами. 3 з.п. ф-лы, 7 ил.

1. Арсенид-галлиевый операционный усилитель на основе «перегнутого» каскода, содержащий первый (1) и второй (2) входы устройства, а также потенциальный выход (3) устройства, входной дифференциальный каскад (4) с первым (5) и вторым (6) токовыми выходами и токовым входом (7) для установления статического режима, который связан с первой (8) шиной источника питания через первый (9) источник опорного тока, причем первый (1) и второй (2) входы устройства соединены с затворами соответствующих входных полевых транзисторов входного дифференциального каскада (4), первый (10) выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен с первым (5) токовым выходом входного дифференциального каскада (4) и через первый (11) токостабилизирующий резистор подключен ко второй (12) шине источника питания, второй (13) выходной биполярный транзистор промежуточного каскада, эмиттер которого соединен со вторым (6) токовым выходом входного дифференциального каскада (4) и через второй (14) токостабилизирующий резистор связан со второй (12) шиной источника питания, причем база первого (10) выходного биполярного транзистора промежуточного каскада соединена с базой второго (13) выходного биполярного транзистора промежуточного каскада, второй (15) источник опорного тока, включенный между коллектором второго (13) выходного биполярного транзистора промежуточного каскада и первой (8) шиной источника питания, буферный усилитель (16), выход которого связан с выходом устройства (3), отличающийся тем, что в схему введены третий (17) и четвертый (18) источники опорного тока, а также первый (19) и второй (20) дополнительные биполярные транзисторы, причем база первого (19) дополнительного биполярного транзистора соединена с коллектором первого (10) выходного биполярного транзистора промежуточного каскада и через третий (17) источник опорного тока подключена к первой (8) шине источника питания, база второго (20) дополнительного биполярного транзистора соединена с коллектором второго (13) выходного биполярного транзистора промежуточного каскада, коллектор второго (20) дополнительного биполярного транзистора соединен со входом буферного усилителя (16) и связан с первой (8) шиной через четвертый (18) источник опорного тока, коллектор первого (19) дополнительного биполярного транзистора согласован с общей шиной источников питания, объединенные эмиттеры первого (19) и второго (20) дополнительных биполярных транзисторов соединены с базами первого (10) и второго (13) выходных биполярных транзисторов промежуточного каскада и связаны со второй (12) шиной источника питания через последовательно соединенные дополнительный резистор (21) и два параллельно включенных p-n-перехода (22), реализованных на биполярных транзисторах, у которых коллекторы соединены с базой.

2. Арсенид-галлиевый операционный усилитель на основе «перегнутого» каскода по п.1, отличающийся тем, что первый (9), второй (15), третий (17), четвертый (18) источники опорного тока выполнены по идентичным схемам на основе выходного полевого транзистора (23), затвор которого связан с первой (8) шиной источника питания и через токостабилизирующий резистор (24) соединен с истоком выходного полевого транзистора (23).

3. Арсенид-галлиевый операционный усилитель на основе «перегнутого» каскода по п.1, отличающийся тем, что первый (9), второй (15), третий (17), четвертый (18) источники опорного тока выполнены по идентичным схемам на основе каскодного включения полевых транзисторов, каждый из которых содержит выходной транзистор (25), затвор которого соединен с истоком согласующего транзистора (26) и связан с первой (8) шиной источника питания через вспомогательный резистор (27), причем затвор согласующего транзистора (26) соединен с истоком согласующего транзистора (26) через вспомогательный резистор (27), а сток согласующего транзистора (26) подключен к истоку выходного транзистора (25).

4. Арсенид-галлиевый операционный усилитель на основе «перегнутого» каскода по п.1, отличающийся тем, что параллельно первому (9) источнику опорного тока включен идентичный ему дополнительный источник опорного тока (28), выполненный по идентичной ему схеме.

| US 4406990 A, 27.09.1983 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| US 8604878 B2, 10.12.2013. | |||

Авторы

Даты

2024-06-03—Публикация

2023-12-26—Подача