Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей и в криптографических приложениях.

Известно устройство для формирования остатка по произвольному модулю от числа, содержащее регистр, блок ключей, блок сумматоров и элемент задержки, соединенные между собой функционально (см. АС СССР №1633495, кл. Н03М 7/18, 1989).

Недостатком данного устройства является низкая надежность его функционирования и небольшая область функциональных возможностей.

Наиболее близким по технической сущности к заявляемому изобретению является рекуррентный формирователь остатков по произвольному модулю, содержащий блок сумматоров, блок формирования частичных остатков, инвертор, элемент задержки и регистр, соединенные между собой функционально (см. патент РФ №2007037, кл. Н03М 7/18, 30.01.1994, бюл. №2).

Недостатком данного устройства являются его ограниченные функциональные возможности, а именно отсутствие возможности формирования неполного частного.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения формирования неполного частного.

Для достижения поставленной цели в вычислительное устройство, содержащее элемент задержки и регистр, причем вход начала вычисления устройства соединен со входом записи регистра и со входом элемента задержки, выход которого является выходом окончания процесса вычисления, вход числа устройства соединен с информационными входами регистра, введены (n-k+1) сумматоров и (n-k+1) мультиплексоров, причем на входы переноса всех сумматоров подается логическая единица, выход переноса i-го сумматора соединен с управляющим входом i-го мультиплексора и является выходом (n-k-i+1)-го разряда неполного частного устройства, где i=1,…,(n-k+1) номер ступени преобразования, на первый информационный вход i-го сумматора подается инверсный код модуля, сдвинутый на (n-k-i+1) разрядов в сторону старших, причем выход (i-1)-го, где i=2,…,(n-k+1), мультиплексора соединен с первым входом i-го мультиплексора и со вторым информационным входом i-го сумматора, выход (i-1)-го сумматора соединен со вторым информационным входом (i-1)-го мультиплексора, причем выход регистра соединен с первым информационным входом первого мультиплексора и со вторым информационным входом первого сумматора, выход (n-k+1)-го сумматора является выходом вычислительного устройства.

Сущность изобретения заключается в реализации следующего способа формирования остатка по произвольному модулю.

Пусть требуется сформировать остаток r от числа а по модулю р и вычислить частное q, то есть решить уравнение a=qp+r.

При проведении вычислений по модулю р значение числа а сравнивается со значением числа z=p×2n-k, где n количество разрядов числа а, a k количество разрядов модуля р. Если значение a≥z, то из числа а вычитается значение числа z, то есть a1=a-z, при этом формируется ненулевой старший (n-k+1)-й разряд неполного частного q. Если a<z, то число а остается без изменений а1=а, а значение старшего (n-k+1)-го разряда неполного частного q принимается равным нулю. Полученное в результате значение а1 сравнивается со значением z1=p×2n-k-1. Если значение a1≥z1, то из а1 вычитается значение модуля z1, то есть а2=а1-z1, при этом формируется ненулевой (n-k)-й разряд неполного частного q. Если a1<z1, то число а1 остается без изменений а2=а1, а значение (n-k)-го разряда неполного частного q принимается равным нулю. Полученное в результате значение а2 сравнивается со значением z2=p×2n-k-2 и т.д. На последнем (n-k+1)-м шаге число an-k сравнивается с модулем p. Если значение an-k≥p, то из an-k вычитается значение числа р, то есть an-k+1=an-k - Р, при этом формируется ненулевой младший разряд неполного частного q. Если аn-k<р, то число аn-k остается без изменений an-k+1=an-k, а значение младшего разряда неполного частного q принимается равным нулю. Полученное в результате значение r=an-k+1 является остатком от деления числа а на число р.

Предлагаемое вычислительное устройство осуществляет данный метод путем последовательного выполнения (n-k+1) операций, в ходе i-й операции значение аi сравнивается со значением р×2n-k-i путем вычисления разности ai-p×2n-k-i, где i=1,…,(n-k), и формируется (n-k-i)-й разряд неполного частного q. При выполнении (n-k+1)-й операции результатом вычисления числа а по модулю р будет являться значение разности, полученное на последнем (n-k+1)-м шаге.

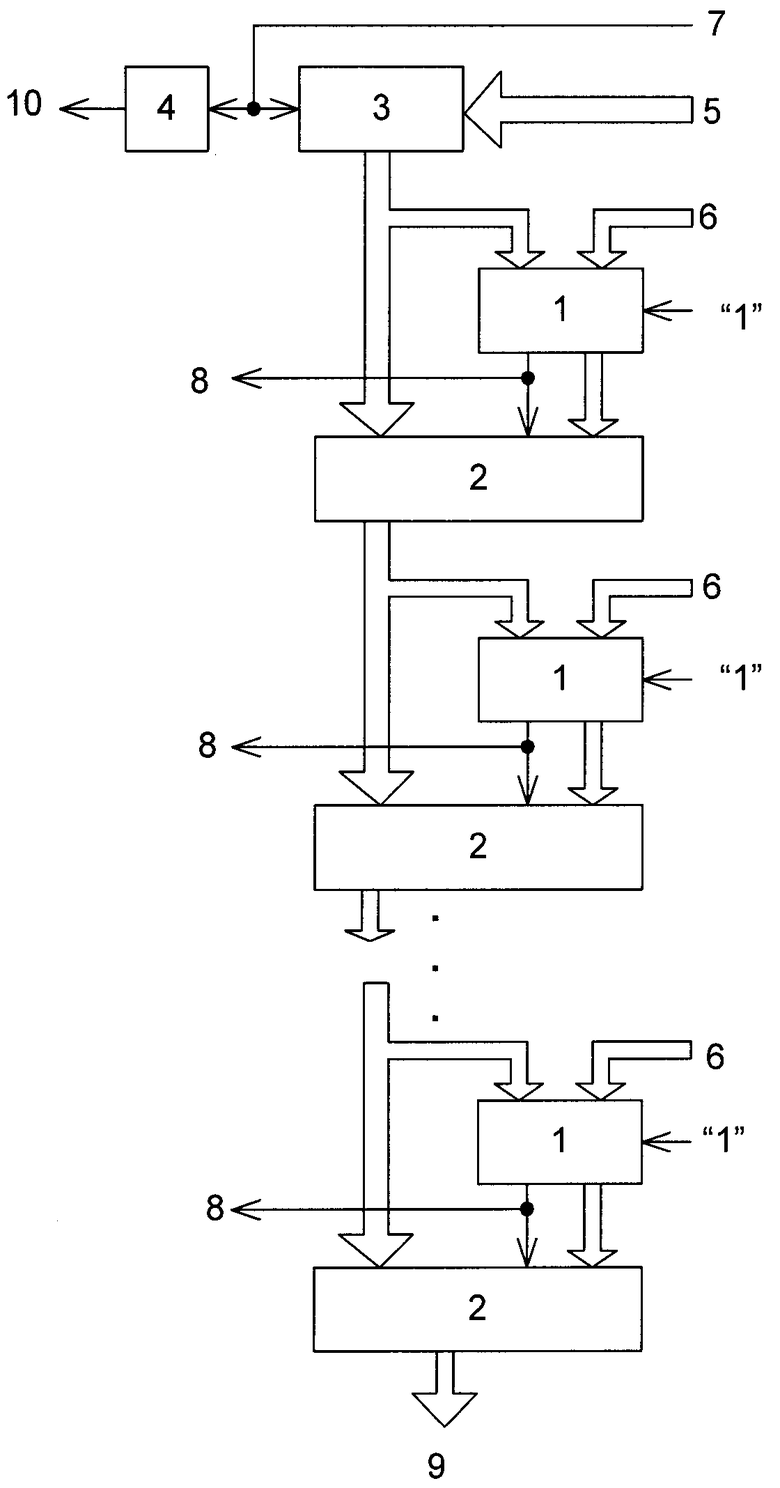

На чертеже представлена схема вычислительного устройства.

Вычислительное устройство содержит (n-k+1) сумматоров 1, (n-k+1) мультиплексоров 2, регистр 3 и элемент 4 задержки. Вход 5 служит для подачи двоичного кода числа а, вход 6 - для подачи двоичного кода модуля р. Вход 7 начала вычисления соединен со входом записи регистра 3 и входом элемента 4 задержки. На вход 6 подается двоичный инверсный код числа р×2n-k-i, где i=1, …, (n-k) порядковый номер ступени преобразования, a (n-k) количество ступеней преобразования, n равно количеству разрядов двоичного представления числа a, k равно количеству разрядов двоичного представления модуля p. Инверсный код числа p×2n-k-i может быть получен путем сдвига двоичного кода числа р на i разрядов в сторону старшего с последующей его инверсией. Выход 9 является выходом двоичного кода остатка r, а выход 8 является выходом двоичного кода неполного частного q. Выход 10 элемента 4 задержки - выходом окончания процесса вычисления.

Вычислительное устройство работает следующим образом.

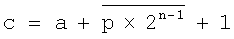

На вход 3 подается двоичный код числа а, который далее поступает на информационные входы регистра 3. Одновременно на вход 7 начала вычисления подается импульс, который поступает на вход элемента 4 задержки и на вход записи регистра 3. При этом код числа а записывается в регистр 3, появляется на его информационных выходах и поступает на второй вход сумматора 1 и первый вход мультиплексора 2 первой ступени преобразования. На первый вход сумматора 1 подается инверсный код p×2n-1 со входа 4 устройства. На вход переноса всех сумматоров 1 подается логическая единица. Сумматор 1 выполняет операцию, описываемую выражением:  , где с - результат суммирования, а - входное число, р - модуль, n - количество разрядов числа а. Старший n+1 разряд полученного значения с поступает на выход переноса сумматора 1. Остальные разряды представляют собой разность

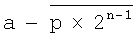

, где с - результат суммирования, а - входное число, р - модуль, n - количество разрядов числа а. Старший n+1 разряд полученного значения с поступает на выход переноса сумматора 1. Остальные разряды представляют собой разность  . На первый вход мультиплексора 2 поступает код числа а, на второй вход мультиплексора 2 поступает разность

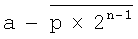

. На первый вход мультиплексора 2 поступает код числа а, на второй вход мультиплексора 2 поступает разность  . Если сигнал на выходе переноса сумматора 1 равен "1", то на второй вход сумматора 1 второй ступени преобразования и на первый вход мультиплексора 2 второй ступени преобразования поступает разность

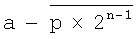

. Если сигнал на выходе переноса сумматора 1 равен "1", то на второй вход сумматора 1 второй ступени преобразования и на первый вход мультиплексора 2 второй ступени преобразования поступает разность  , если же он равен "0", то на второй вход сумматора 1 и на первый вход мультиплексора 2 поступает само число а. На первый вход сумматора 1 второй ступени преобразования поступает инверсный код р×2n-2. Далее выполняются те же действия, что и на первой ступени преобразования. После проведения n таких операций на выходе 4 окажется результат вычисления числа а по модулю р, а на выходах 6 - код неполного частного q. Одновременно с выхода элемента 4, время задержки которого равно времени работы (n-k+1) сумматоров 1 и (n-k+1) мультиплексоров 2, на выход 10 поступает импульс, сигнализирующий об окончании процесса формирования остатка и неполного частного.

, если же он равен "0", то на второй вход сумматора 1 и на первый вход мультиплексора 2 поступает само число а. На первый вход сумматора 1 второй ступени преобразования поступает инверсный код р×2n-2. Далее выполняются те же действия, что и на первой ступени преобразования. После проведения n таких операций на выходе 4 окажется результат вычисления числа а по модулю р, а на выходах 6 - код неполного частного q. Одновременно с выхода элемента 4, время задержки которого равно времени работы (n-k+1) сумматоров 1 и (n-k+1) мультиплексоров 2, на выход 10 поступает импульс, сигнализирующий об окончании процесса формирования остатка и неполного частного.

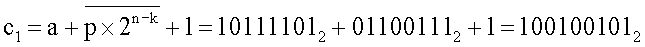

Рассмотрим работу вычислительного устройства на примере.

Пусть a=18910=101111012, модуль р=1910=100112,  , n=8, k=5. Первый сумматор формирует значение

, n=8, k=5. Первый сумматор формирует значение  . Старший разряд c1 равен 1, следовательно, мультиплексор 2 переводит на второй сумматор код числа а1=а-p×2n-k=001001012 и 3-й разряд неполного частного q принимает значение 1. Второй сумматор 1 формирует значение

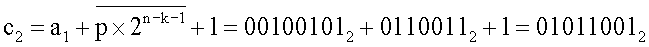

. Старший разряд c1 равен 1, следовательно, мультиплексор 2 переводит на второй сумматор код числа а1=а-p×2n-k=001001012 и 3-й разряд неполного частного q принимает значение 1. Второй сумматор 1 формирует значение  . Старший разряд с2 равен 0, следовательно, мультиплексор 2 переводит на третий сумматор 1 код числа а1 и 2-й разряд неполного частного q принимает значение 0. Третий сумматор 1 формирует значение

. Старший разряд с2 равен 0, следовательно, мультиплексор 2 переводит на третий сумматор 1 код числа а1 и 2-й разряд неполного частного q принимает значение 0. Третий сумматор 1 формирует значение  . Старший разряд с3 равен 0, следовательно, мультиплексор 2 переводит на четвертый сумматор 1 код числа а1 и 1-й разряд неполного частного q принимает значение 0. Четвертый сумматор 1 формирует значение

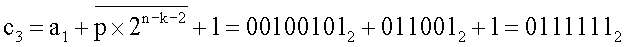

. Старший разряд с3 равен 0, следовательно, мультиплексор 2 переводит на четвертый сумматор 1 код числа а1 и 1-й разряд неполного частного q принимает значение 0. Четвертый сумматор 1 формирует значение  . Старший разряд с4 равен 1, следовательно, мультиплексор 2 переводит на выход код числа

. Старший разряд с4 равен 1, следовательно, мультиплексор 2 переводит на выход код числа

a2=a1-p×2n-k-3=100102=1810 и 0-й разряд неполного частного q принимает значение 1. В результате неполное частное имеет значение q=10012=910

189=19×9+18

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 2007 |

|

RU2348965C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 2020 |

|

RU2739338C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 2020 |

|

RU2756408C1 |

| КОНВЕЙЕРНЫЙ ВЫЧИСЛИТЕЛЬ | 2023 |

|

RU2804380C1 |

| Вычислительное устройство | 2017 |

|

RU2661797C1 |

| КОНВЕЙЕРНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2022 |

|

RU2791440C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 2019 |

|

RU2717915C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| Конвейерный вычислитель | 2023 |

|

RU2797163C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 2018 |

|

RU2696223C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей и в криптографических приложениях. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения формирования неполного частного. Устройство содержит (n-k+1) сумматоров, (n-k+1) мультиплексоров, регистр и элемент задержки. 1 ил.

Вычислительное устройство, содержащее элемент задержки и регистр, причем вход начала вычисления устройства соединен со входом записи регистра и со входом элемента задержки, выход которого является выходом окончания процесса вычисления, вход числа устройства соединен с информационными входами регистра, отличающееся тем, что в него введены (n-k+1) сумматоров и (n-k+1) мультиплексоров, где n - количество разрядов двоичного представления числа a, k - количество разрядов модуля р, причем на входы переноса всех сумматоров подается логическая единица, выход переноса i-го сумматора соединен с управляющим входом i-го мультиплексора и является выходом (n-k-i+1)-го разряда неполного частного устройства, где i=1,…,(n-k+1) номер ступени преобразования, на первый информационный вход i-го сумматора подается инверсный код модуля, сдвинутый на (n-k-i+1) разрядов в сторону старших, причем выход (i-1)-го, где i=2,…,(n-k+1), мультиплексора соединен с первым входом i-го мультиплексора и со вторым информационным входом i-го сумматора, выход (i-1)-го сумматора соединен со вторым информационным входом (i-1)-го мультиплексора, причем выход регистра соединен с первым информационным входом первого мультиплексора и со вторым информационным входом первого сумматора, выход (n-k+1)-ого сумматора является выходом вычислительного устройства.

| РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 1991 |

|

RU2007037C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| Устройство для формирования остатка по произвольному модулю от числа | 1989 |

|

SU1633495A1 |

| Вычислительное устройство по произвольному модулю | 1990 |

|

SU1737442A1 |

| JP 11282349 A, 15.10.1999 | |||

| УСТРОЙСТВО ДЛЯ ЗАГРУЗКИ СКИПОВ | 0 |

|

SU308963A1 |

Авторы

Даты

2009-05-20—Публикация

2007-05-11—Подача